锁相技术第8章

锁相技术复习要求

锁相技术复习要求锁相技术复习要点第1章锁相环路的基本工作原理一、考核知识点(一)锁相环路的基本工作原理;(二)锁相环路的相位数字模型及其微分方程;(三)锁相环路的基本性能。

二、考核要求(一)锁定与跟踪的概念1、识记:(1)相位的概念;(2)锁相环路的定义;(3)环路的捕获带(4)环路的同步带。

2、领会:(1)锁相环路是一个相位跟踪系统,它建立了输出信号瞬时相位与输入信号瞬时相位的控制关系(2)几个重要参数:载波相位、瞬时相位、自由振荡角频率、瞬时相差、移稳态相差;(3)环路的两种基本工作状态:捕获过程、锁定状态。

3、应用:(1)环路是处于锁定状态的判定依据;(2)一阶环稳态相差的计算。

(二)环路组成1、识记:(1)环路的基本部件;(2)鉴相器的作用与数学模型;(3)鉴相器的分类:模拟乘法器鉴相器、序列电路(数字鉴相器);(4)环路滤波器的作用与数学模型;(5)压控振荡器的作用与数学模型;(6)压控灵敏度;(7)压控振荡器的种类。

2、领会:(1)锁相环路的组成及框图;(2)正弦鉴相器及数学模型;(3)几种常用的环路滤波器及传递函数;(4)锁相环路的相位数学模型。

3、应用;(1)理想积分滤波器分析;(2)非常用环路滤波器的传递函数求解。

(三)环路的动态方程1、识记:(1)瞬时频差;(2)控制频差;(3)固有频差;(4)环路增益K。

2、领会:(1)锁相环路动态方程3、应用:(1)锁相环路动态方程的含意;(2)稳态相差的求解。

(四)一阶环路的捕获、锁定与失锁。

1、识记:(1)一阶环路;(2)相点;(3)相轨迹(4)相平面。

2、领会:(1)一阶环路的非线性微分方程;(2)相轨迹上相点的含义。

3、应用:(1)频率牵引现象;(2)一阶环路的捕获带、同步带、快捕带。

第二章环路跟踪性能一、考核知识点(一)锁相环路的线性相位模型及传递函数;(二)锁相环路的性能指标;(三)二阶环路在典型输入下的响应;(四)环路的频率响应。

锁相技术概括

锁相技术原理及应用学号:0808224030姓名:吕社钦第一章 锁相环路的基本工作原理第一节 锁定与跟踪的概念 一、相位关系描述锁相环路(PLL)是一个相位跟踪系统,方框表示如图1-1(a)。

图1-1 相位跟踪系统框图设输入信号 (1-1) 式中U i 是输入信号的幅度;ωi 是载波角频率;θi(t)是以载波相位ωit 为参考的瞬时相位。

若输入信号是未调载波,θi(t) 即为常数,是ui(t)的初始相位;若输入信号是角调制信号(包括调频调相),θi(t)即为时间的函数。

设输出信号 (1-2) 式中Uo 是输出信号的幅度;ωo 是环内被控振荡器的自由振荡角频率,它是环路的一个重要参数;θo(t)是以自由振荡的载波相位ωot 为参考的瞬时相位,在未受控制以前它是常数,在输入信号的控制之下,θo(t)即为时间的函数。

(注: 锁相环路是一个相位反馈控制系统,输入信号ui(t)对环路起作用的是它的瞬时相位,幅度通常是固定的.输出信号u0(t)的幅度Uo 通常也是固定的,只是其瞬时相位受输入信号瞬时相位的控制.因此,我们希望直接建立输出信号瞬时相位与输入信号瞬时相位之间的控制关系.我们先讨论两个不同频率信号之间的相位关系.)图1-2 输入信号和输出信号的相位关系图1-2(a)所示。

从图上可以得到两个信号的瞬时相位之差 (1-3)前面已经说到,被控振荡器的自由振荡角频率ωo 是系统的一个重要参数,它的载波相位ωot 可以作为一个参考相位。

这样一来,输入信号的瞬时相位可以改写为(1-4)令 (1-5)()sin[()]i i i i u t U t t ωθ=+()cos[()]o oo o u t U t t ωθ=+()[()][()]()()()e i i o o i o i o t t t t t t t t θωθωθωωθθ=+-+=-+-()()()i i o i o i o i o t t t t t ωθωωωθωωω+=+-+∆=-为输入信号频率与环路自由振荡频率之差,称为环路的固有频差。

锁相技术课件

一、概述

§6.3 频率合成

1. 概念

频率合成器是将一个高精确度和高稳定度的标准

参考频率,经过混频、倍频与分频等对它进行加、

减、乘、除的四则运算,最终产生大量的具有同样

精确度和稳定度的频率源。

2. 应用 频率合成器在雷达、通信、遥控遥测、电视广

播和电子测量仪器等方面得到了广泛的应用。

《锁相技术》

第6章 锁相环路的应用

于He (s)具有高通特性,只要在He (s) 的通带之内,

输出信号频偏正比于调制信号的幅度。----调频波

调相波:

2

(s)

He (s)

Ko s

sU F

(s)

对调制信号先 微分再调频

2 (s) He (s)KoUF (s)

输出信号相位正比于调制信号的幅度。----调相波

《锁相技术》

第6章 锁相环路的应用

音频信号调频,则输入瞬时频率为:

载频

i (t) c sin t

Δω为峰 值频偏

当 0 时,i c ,所以 实际是叠加到c 上的。

做出 H ( ji ) i 的关系图,就是环路对输入信号 瞬时频率i 的振幅频率响应:

《锁相技术》

第6章 锁相环路的应用

-3dB点

2c

① 具有带通滤波特性。带宽为 2c 。 ② 由于锁相环的跟踪性能,其中心频率可以跟踪输

fd

fo N V

fo N Vfr

①增加前置分频器,解决了输出频率高于程序分频

器的工作频率的问题,提高了输出频率范围。

《锁相技术》

第6章 锁相环路的应用

②输出频率增量为Vfr ,频率分辨率降低了。

③如果保持原有的频率分辨率 fr ,需要使参考频率

第八章锁相技术5-3(捕获) 射频通信电路.

因此,捕捉带 P 一定小于同步带

捕捉时间与环路参数的关系

TP

i 2

2

3 n

与输入固有频差 i 的平方成正比

与环路的带宽 n的立方成正比

缩短捕捉时间的思路:

(1)扩展环路带宽( n

A

1 2 )

改变增益 改变时间常数

(2)减小输入频差——方法?

缩短捕捉时间实例 1:

vc Ud AF () sine vc 0 ,对应 e 为0 ~ ,

由于

e

de

dt

e 小,e (0 ~ ) 间变化速率慢

反之对应 e为 ~ 2 ,e 大

e变化速率快

结果:vd 、 vc 是不对称的正弦波

e 在 0~ 和 ~ 2 间

变化速率不同

频率合成器原理图

锁定时进入鉴相器 两信号频率相等:

fo N

fi

当N变化时,环路失锁——需重新捕获——锁定

改进方法: 将反映分频比N的频率控制值 D/A变换,得模拟电压

粗调VCO,使VCO频率向减小频差方向移动 锁相环的细调和外电路粗调相结合

频率合成 将两个输入信号 的频率差变为电压

v 鉴相器的输出 变为正半周长, d

负半周短的不对称正弦波

不 谐波——被LF滤除

对 称

基波——被LF衰减

波 正平均分量——通过LF

使VCO频率向 i 牵引 i i r( AV ) i

新频差

初始频差

由于频差减小,LF(低通)对 vd 的通过能力增大,即

AF (i) > AF (i )

vc (t)

0 ,不能捕捉

(2) i 较小

正弦鉴相器输出:vd (t) Ud sin it

第八章锁相技术5-1(原理)

频率是频差 (i o ),称差拍正弦 ~ ② 鉴相范围是: 2 2 ③ 鉴相特性为非线性,

当 e

vd (t ) Ud sin e (t ) Ude (t )

④ 正弦鉴相器的鉴相灵敏度为: Ad

6

时 ,正弦鉴相可以近似为线性

dvd d e

Ud

e 0

e (t ) i (t ) o (t )

该方程表示了环路中动态角频率的平衡关系: 瞬时频差 = 输入固有频差 — 控制频差

从以下几点加深对环路方程的理解:

vi

vi Vim sin[r t i (t )]

U d sin()

vd

vc

vo Vom cos[r t o (t )]

vc (t )

VCO

vo (t )

o (t ) r Ao vc (t )

r —— 控制电压 vc =0 时的自由振荡角频率

Ao 压控灵敏度,其单位是(弧度/秒)/伏

锁相环中VCO 数学模型

vi

vd

vc

vo

注意:VCO电压输入鉴相器,起作用的是其相位

U d sin e

求VCO受控相位: o ( )d r t A v ( )d

常用的环路滤波器三种环路滤波器的传递函数时间常数rc无源比例积分滤波器分子引入一个零点低通特性与简单rc滤波器不同趋于比例常数而不是环路滤波器的主要指标相频特性比例积分滤波器的传递函数中引入了一个零点使相频特性在频率较高处有相位超前校正作用这利于增加环路的稳定性直流增益有源滤波器直流增益很大利于环路同步带宽由滤波器的时间常数决定高频增益比例积分滤波器不为0利于环路的捕捉幅频特性低通特性压控振荡器vcovco功能电压控制频率振荡器频率受控特性理想的应为线性

锁相环基本概念PPT课件

ui(t)

PD ud(t) LF

uc(t) VCO

uo(t)

uf(t)

PLL

图1.2.1 基本锁相环组成

实际使用的锁相环还可能包含放大器、混频器、分 频器、滤波器等部件,但这些部件不影响锁相环的工 作原理,可不予考虑。

u(t) VCO

uf(t)

PLL

uo(t)

图1.2.1 基本锁相环组成

ui(t)

PD

ud(t) LF

uc(t) VCO

uo(t)

uf(t)

PLL

图1.2.1 基本锁相环组成

在锁相环中,PD是控制器,VCO是控制对象,LF是校 正网络,基本锁相环中反馈网络的传递函数为1。反 馈网络的传递函数为1 的环路称为单位反馈环,它的 反馈信号等于输出信号,反馈量等于输出量。在本 书中,无特殊说明的锁相环皆是单位反馈环。

由图可见,锁相环是一个反馈系统(闭环控制系统) 。 基本锁相环是一个全反馈系统,因为uf(t)=uo(t) 。

PD对输入信号ui(t)和反馈信号uf(t)的相位作比较, 其输出信号可表示为

ud(t)=f[θe(t)]

(1.2.1)

式中θe(t)是输入信号和反馈信号的相位差,f[·]表 示运算关系。

2021/6/19

12

LF是一个线性低通网络,用来滤除ud(t)中的高频成分 和调整环路参数,它对环路的性能指标有重要影响。 它的输出uc(t)被用来控制VCO的频率和相位。常 称ud(t)为误差信号,uc(t)为控制信号,它们之间的关 系为 uc(t)=F(p)ud(t)…(1.2.2)

式中p为微分算子,F(p)为LF的传输算子。

到70年代,随着集成电路技术的发展,逐渐出现了集成 的环路部件、通用单片集成锁相环路以及多种专用 集成锁相环路,这就为锁相技术在更广泛的领域应用 提供了条件,从而使锁相技术得到了广泛的应用。

锁相技术

设输出信号为:uo (t) Uo cos[ot o (t)]

PLL内部VCO的 自由振荡角频率

是在输入信号控制下,

相对于 ot的瞬时相位,

是时间 t 的函数。

锁相环路中,输入信号 ui (t) 对环路的作用是 在它的瞬时相位 i (t) i (t) 的作用下,改变输出 信号 uo (t) 的瞬时相位 o (t) o (t) ,所以对于锁相 环路来说,更关心的是它的输入和输出信号的相

不为零

数值很小 的量,但

不为零

这一过程所用的时间为捕获时间 TP

《 锁相技术》

第1章 锁相环路的基本工作原理

捕获过程中瞬时相差与瞬时频差的典型时间图分析

.

《 锁相技术》

第1章 锁相环路的基本工作原理

三、锁定状态

环路锁定状态(同步状态)的条件:

e((tt))

(t) 2n e

K0 p

整理得到:pe (t) p1(t) KoUd F ( p)sine(t)

uc (t)

环路的动态方程:

K KoUd

pe (t) p1(t) KF ( p)sine(t)

K K0Ud 为环路增益

《 锁相技术》

第1章 锁相环路的基本工作原理

锁相环路动态方程的物理概念解释:

第1章 锁相环路的基本工作原理

环路的瞬时相位差:(矢量表示方法如图所示)

e (t) 1(t) 2(t)

输入信号的 瞬时角频率

输出信号的 瞬时角频率

环路瞬时频差:

de (t)

dt

1(t)2 (t)

(t)

e (t)

16、锁相技术

锁相技术一、引言锁相,就是实现两个电信号相位同步的自动控制。

锁定放人器(LIA —L0ck —in AmDlmer)是锁相技术在微弱信号检测中的应用,本实验将研究锁定放大器的原理和应用。

实验的目的要求是:l 了解锁定放大器的工作原理,着重掌握相关器的原理。

2学会使用锁定放大器,并用它测量p .n 结势垒电容。

二、原理(一)锁定放大器的基本原理本实验采用NL 一1锁定放大器,其原理框图见图12.k 锁定放大器是一种交流电压表,它能精确地测定深埋在噪声之中的周期重复信号的幅值及相位,这种抑制噪声的作用主要是通过相关器实现的,使用时,除要输入待测信号外,还要输入参考信号。

图12—1 NL 一1锁定放大器原理框图1、相关器 锁定放大器中的相关器如图12—2所示。

它由相乘电路和低通滤波器组成,相乘电路有许多形式,如开关型、电流控制型等等,NL 一1锁定放大器采用开关型。

低通滤波器具有压缩噪声带宽,让直流信号通过的作用,它抑制噪声的能力可以用“等效噪声带宽”图12—2相关器这一参数来描述,可以求出,图12—2中的低通滤波器的等效噪声带宽f n=1144RC T= 低通滤波器的时间常数T=Rc ,T 越长则f n 越小,但实际上由于漂移等问题,T 是不能太长的。

下面是相关器的工作原理。

相关器采用的是所谓相关接收技术。

设输入信号为()Vi t ,参考信号为()Vr t ,由于低通滤波器实际上是一个积分器,因此相关器的输出0V 是()Vi t 和()Vr t 乘积,再对时间积分,并取平均值有0V = ()1lim ()2T i t T V t Vr t dt T τ→∞--⎰ (12-1)式中t 是参考信号相对于输入信号的延迟时间,积分时间上限T 即低通滤波器的时间常数,通常把式(12.1)所表示的0V 称为()Vi t 和()Vr t 的相关函数,实现求相关函数的电子线路称为相关器或相关接收器。

下面的讨论会更清楚相关器的作用。

《锁相技术第章》课件

优化方法

通过调整环路带宽和相位裕量 ,可以提高线性范围和降低失

真性能。

04

锁相环路的设计与实现

设计步骤与注意事项

设计步骤 确定系统性能指标:包括锁定时间、跟踪精度、噪声抑制等。

选择合适的鉴相器、环路滤波器和压控振荡器。

ቤተ መጻሕፍቲ ባይዱ

设计步骤与注意事项

计算相关参数:如环路带宽、滤波器阶数等。 搭建电路并测试性能。

仿真验证法

利用仿真软件模拟环路行为,验证环路设计 的正确性。

测试系统搭建与性能评估

测试系统搭建

性能评估指标

根据锁相环路的特性,搭建相应的测试系 统,包括信号源、示波器、频谱分析仪等 。

设定环路性能评估指标,如锁定时间、跟 踪精度、噪声性能等。

测试步骤

性能评估

按照设定的测试步骤,对环路进行测试, 记录测试数据。

数字化与软件化

01

随着技术的发展,锁相技术正朝着数字化和软件化的方向发展

,提高集成度和灵活性。

高性能与低成本

02

追求高性能的同时降低成本是锁相技术的重要发展趋势,以满

足更广泛的应用需求。

多功能与智能化

03

未来的锁相技术将具备更多的功能和智能化特性,如自适应滤

波、自动校准等。

THANKS

感谢观看

跟踪范围与动态响应

跟踪范围

指锁相环路能够跟踪的 输入信号频率范围。

动态响应

指锁相环路对输入信号 频率变化的响应速度。

影响因素

跟踪范围和动态响应受 到环路带宽、相位裕量

和阻尼系数的影响。

优化方法

通过调整环路带宽和相 位裕量,可以提高跟踪

范围和动态响应。

噪声性能

锁相技术 郑继禹 西电

第一章 锁相环路的基本工作原理1-3 已知一阶环的 U =2V , K =15KHz/V , / 2 =2MHz ,问当输入频率分别为 d 0 0 1.98MHz 和 2.04MHz 的载波信号时,环路能否锁定?稳定相差多大? 解:U 2V , K 0 d15k rad s V 2 , 2 2M rad/s2 1.98M rad/s , 2 2.04M rad/s1 2 环路能够锁定的条件是 K固有频差 1: 2 ( 0.02)M 2 20k rad/s 01 1 0 固有频差 2: 2 0.04M 2 40k rad/s 02 2 0 环路增益: K U K 2 2 15k 2 30k rad/s d 0 对 处于同步带内,即 K ,环路锁定。

01 01 对 处于同步带外,即 K ,环路失锁。

02 02 01 arcsin 2 41.8 稳态相差 arc sine42。

K 3 1-4 已知一阶环的U =0.63V , K =20kHz/V , f =2.5MHz ,在输入载波信号作用下环 d 0 0 路锁定,控制频差等于 10KHz 。

问:输入信号频率 为多大?环路控制电压u (t ) =?稳态 i c 相差 ( ) =?e解: K 0220k rad/ s V , 控制 2 10k rad/s ,环路增益 K U K 0.63 2 20K 2 12.6k rad/s d 0环路锁定时,固有频差等于控制频差,即 = 控制 2 10 k rad/s =f 0 2.5MHz , = 2 2500K rad/s固有频差 0 0 i= 2 2500k+2 10K = 2 2510k =5.02 10 6rad/si 0 0f 2.51MHzi2 10K 0.5V2 20K因为 控制 u t K 0 控制电压u t Kc c 02 10k 10sin e 2 12.6k 0.790 K 12.6 稳态相差earcsin 0.79 52.5 1-5 一阶环,设开环时u i (t ) 0.2sin 2 10 t (V ),u (t ) cos 2 10 t (V )3 4 i 0式中 、 为常数。

锁相技术课程实践

《锁相技术》课程结业论文题目:4PSK信号的解调电路设计院系名称:信息科学与工程学院专业班级:电子信息工程10级1班学生姓名:学号:授课教师:朱春华2013年7月2日摘要在数字信号的调制方式中4PSK是目前最常用的一种数字信号调制方式,它具有较高的频谱利用率、较强的抗干扰性、在电路上实现也较为简单。

本次设计在理解4PSK解调原理的基础上采用四相Costas环完成4PSK的解调并应用SystemView软件来完成电路的仿真,仿真结果包括已调信号的波形、解调后的基带信号波形以及4PSK信号波形,并通过比较仿真模型与理论计算的性能,证明了仿真模型的可行性。

关键词 4PSK 四相costas环 SystemView 解调电路目录1引言 (4)1.1课题目的和意义 (4)1.2 课题研究内容 (4)2 4PSK解调电路的工作原理 (4)2.1 锁相环简介 (4)2.2 4PSK解调电路的工作原理 (5)2.2.1 Costas环原理 (5)2.2.2 4PSK简介 (5)2.2.3 4PSK解调电路原理 (6)3 4PSK解调电路的具体设计及systemview仿真 (6)3.1 4PSK解调电路原理框图 (6)3.2 4PSK解调电路具体设计及仿真图 (6)3.2.1 4PSK解调电路整体设计图 (7)3.2.2 4PSK信号的产生 (7)3.2.3 4PSK信号的解调 (8)4 结论 (11)5 参考文献 (12)1引言1.1课题目的和意义通过课程设计,加强学生对锁相技术的理解,进一步提高分析解决实际问题的能力,创造一个独立开展电路实验的机会,真正实现由课本知识向实际能力的转化;通过具体电路的设计制作与仿真,加深对基本原理的了解,增强学生的实际动手操作能力。

1.2 、课题研究内容1、理解锁相环和costas环的工作原理。

2、掌握4PSK解调电路的设计原理,以及costas环在解调电路中的作用。

3、会使用SystemView软件进行电路仿真。

矢量网络分析仪中的系统锁相技术-易迪拓培训

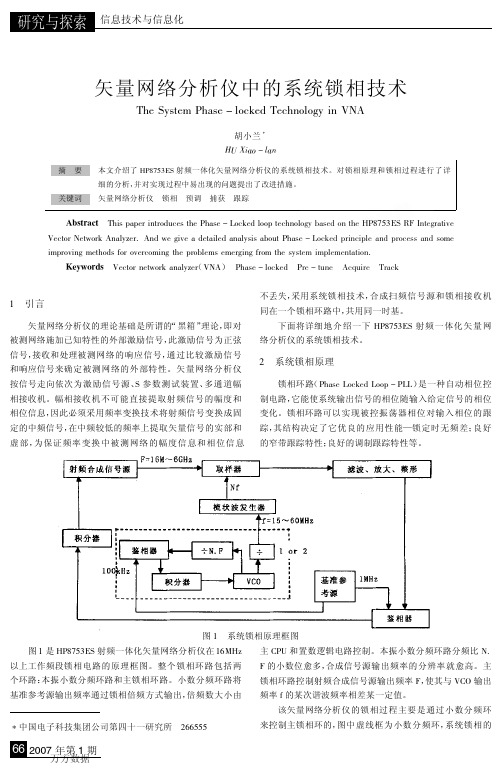

图 N7 系统锁相原理框图 7 7 图 N 是 8)9:;<=$ 射频一体化矢量网络分析仪在 NMO8H 以上工作频段锁相电路的原理框图。整个锁相环路包括两 个环路: 本振小数分频环路和主锁相环路。小数分频环路将 基准参考源输出频率通过锁相倍频方式输出, 倍频数大小由 主 P)Q 和置数逻辑电路控制。本振小数分频环路分频比 5I D 的小数位愈多, 合成信号源输出频率的分辨率就愈高。主 锁相环路控制射频合成信号源输出频率 D, 使其与 4PR 输出 频率 J 的某次谐波频率相差某一定值。 该矢量网络分析仪的锁相过程主要是通过小数分频环 $中国电子科技集团公司第四十一研究所7 LMM;;; 来控制主锁相环的, 图中虚线框为小数分频环, 系统锁相的

7 7 !"#$%&’$7 !"3& >*>#? 31’?-0@.#& ’"# )"*&# + A-./#0 ,--> ’#."1-,-2% B*� -1 ’"# 8)9:;<=$ CD E1’#2?*’3F# 4#.’-? 5#’G-?/ 61*,%H#?I 610 G# 23F# * 0#’*3,#0 *1*,%&3& *B-@’ )"*&# + A-./#0 >?31.3>,# *10 >?-.#&& *10 &-(# 3(>?-F312 (#’"-0& J-? -F#?.-(312 ’"# >?-B,#(& #(#?2312 J?-( ’"# &%&’#( 3(>,#(#1’*’3-1I ()*+,%-#7 4#.’-? 1#’G-?/ *1*,%H#? ( 456) 7 )"*&# + ,-./#07 )?# + ’@1#7 6.K@3?#7 !?*./ 不丢失, 采用系统锁相技术, 合成扫频信号源和锁相接收机 同在一个锁相环路中, 共用同一时基。 下面将详细地介绍一下 8)9:;<=$ 射频一体化矢量网 络分析仪的系统锁相技术。

锁相技术复习要求

锁相技术复习要点第1章 锁相环路的基本工作原理一、考核知识点(一)锁相环路的基本工作原理;(二)锁相环路的相位数字模型及其微分方程;(三)锁相环路的基本性能。

二、考核要求(一)锁定与跟踪的概念1、识记:(1)相位的概念;(2)锁相环路的定义;(3)环路的捕获带(4)环路的同步带。

2、领会:(1)锁相环路是一个相位跟踪系统,它建立了输出信号瞬时相位与输入信号瞬时相位的控制关系(2)几个重要参数:载波相位、瞬时相位、自由振荡角频率、瞬时相差、移稳态相差;(3)环路的两种基本工作状态:捕获过程、锁定状态。

3、应用:(1)环路是处于锁定状态的判定依据;(2)一阶环稳态相差的计算。

(二)环路组成1、识记:(1)环路的基本部件;(2)鉴相器的作用与数学模型;(3)鉴相器的分类:模拟乘法器鉴相器、序列电路(数字鉴相器);(4)环路滤波器的作用与数学模型;(5)压控振荡器的作用与数学模型;(6)压控灵敏度;(7)压控振荡器的种类。

2、领会:(1)锁相环路的组成及框图;(2)正弦鉴相器及数学模型;(3)几种常用的环路滤波器及传递函数;(4)锁相环路的相位数学模型。

3、应用;(1)理想积分滤波器分析;(2)非常用环路滤波器的传递函数求解。

(三)环路的动态方程1、 识记:(1)瞬时频差;(2)控制频差;(3)固有频差;(4)环路增益K。

2、 领会:(1)锁相环路动态方程3、应用:(1)锁相环路动态方程的含意;(2)稳态相差的求解。

(四)一阶环路的捕获、锁定与失锁。

1、识记:(1)一阶环路;(2)相点;(3)相轨迹(4)相平面。

2、领会:(1)一阶环路的非线性微分方程;(2)相轨迹上相点的含义。

3、应用:(1)频率牵引现象;(2)一阶环路的捕获带、同步带、快捕带。

第二章 环路跟踪性能一、考核知识点(一)锁相环路的线性相位模型及传递函数;(二)锁相环路的性能指标;(三)二阶环路在典型输入下的响应;(四)环路的频率响应。

锁相技术频率合成PPT课件

(7-19)

21

第21页/共32页

2. 频率间隔

频率合成器的输出频率是不连续的,以点频方式出现,两相邻点频之间的间隔称为频率间隔,又称为 频率分辨率。在锁相频率合成中,整数分频的频率间隔由参考频率fr决定,而小数分频的频率间隔由分频系 数N.F中小数.F决定。由频率范围与频率间隔可以确定频率合成器的工作频率点数(波道数)。

下变频PLL频率合成器产生本振信号,且混频频率为

90MHZ。 FM收音机本振频率范围:98.7----118.7MHZ

fr 10KHz; fM 90MHz fo Nfr fM N 8702870

合成器 需产生 的信号 fo 频率 范围。

调谐时,只需改变N,就可以搜索到频段内所有的 电台信号。

④电台接收状态产生第一本机振荡信号 fL1和第二本机振

荡信号 fL2 。

混频1、

26.965— 27.405MHZ

混频1

第一中频 10.695MHZ

混频2

第二中频 455KHZ

2采用低 本振方

f L1

fL1 16.270 16.710MHZ

式

fL2 fL2 10.24MHZ

26

第26页/共32页

关键指标

计算 第10及步n1, 2

根据已知 公式计算

第5步

考虑噪声时的电 路类型选择和参

数确定

第6步

选择PD类型 计算Ud

第5步

第11步 求出LF的元件参数

结束

计算电 路参数

30

第30页/共32页

本章小结

➢鉴相器的电路实现 ➢VCO的电路实现 ➢典型通用集成锁相环的构成及工作原理 ➢典型集成频率合成器的构成及工作原理

fo 和 fr 有相同的频率稳定度。由于N是可编程

锁相

摘要随着现代通信、雷达、电子侦察和对抗技术的飞速的发展,对作为核心部件的频率合成器的性能指标提出了越来越高的要求,宽频带、高频率分辨、低捷变时间、高频率稳定度、低相位噪声、低杂散、能程控等。

这些技术要求用普通的模拟电路技术是很难达到的,频率合成技术是产生大量高精度、高稳定度频率信号的主要技术。

小数分频频率合成器则是近年来出现的一种新技术,它与传统的整数分频频率合成器相比具有频率分辨率高、相位噪声低等优点。

本文介绍了锁相环和频率合成技术的基础理论,并对小数分频锁相环频率合成器及其实现技术进行了探讨。

ABSTRACTToday, as the electronic technology is developing fantastically fast, the request for higher performance of synthesizers is put forward, wide frequency range, high frequency resolution, low jump time, low phase noise, high spurious restraining and controlled by program. These requirements are too hard to be reached by using normal analog circuit. Frequency synthesizer is the key technology to produce a great deal of high resolution, high stabilization frequency signal.Fraction-N phase locked loop (FNPLL) frequency synthesizer has been appeared in recent years. It has the advantage of high frequency resolution and low phase noise when compared with traditional Integer-N phase locked loop (NPLL) frequency synthesizer.In this paper the basic theory of phase locked loop (PLL) and frequency synthesizer technology were introduced, the theory and implement of FNPLL frequency synthesizer were discussed too.目录一、锁相环基本原理 (4)1.1锁相环原理及组成 (4)1.2 锁相环路的相位模型及其基本方程 (4)二、频率合成基本原理 (5)2.1频率合成概念 (5)2.2频率合成器及其技术指标 (5)2.2.1频率范围 (5)2.2.2频率间隔(频率分辨率) (6)2.2.3频率转换时间 (6)2.2.4准确度与频率稳定度 (6)2.3频率合成器的类型 (6)2.3.1直接式频率合成器(DS) (6)2.3.2间接式频率合成器(IS) (6)2.3.3直接数字式频率合成器(DDS) (7)三、Σ-△小数分频锁相环频率合成器 (7)3.1锁相环频率合成器的发展 (7)3.2 Σ-△小数分频锁相环频率合成器工作原理 (7)四、结束语 (9)一锁相环基本原理1.1 锁相环原理及组成PLL是一种反馈控制电路,其特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

eight

主 讲 教 师: 赵 仕 良

第8章 通信系统

Communication Systems

信号与系统

主 讲 教 师: 赵 仕 良

本章主要内容

作为傅立叶分析在工程实际中的应用,本章将 讨论通信系统中的某些基本技术及其分析方法。 1. 正弦幅度调制——DSB调制与AM调制。 2. 同步解调与包络解调;频分复用(FDM)。 3. 单边带(SSB)幅度调制。 4. 脉冲串载波调制与时分复用(TDM)。 5. 脉冲幅度调制(PAM)与脉冲编码调制(PCM)。

讨论的解调系统实现解调。

信号与系统

主 讲 教 师: 赵 仕 良

当 c c

实现解调。

2

时,由于 cos(c c ) 0 不能

可见,必须要求调制和解调时所使用的载波 不仅要严格同频,而且要相位同步(以保证相位 差 c c 与时间无关)。因此这种解调方法称为 同步解调(Synchronous Demodulation)。

SSB信号的产生: 1 .滤波法: 利用边带滤波器,滤除一个边带。

信号与系统

主 讲 教 师: 赵 仕 良

2 . 移相法:

(2)

SSB下 SSB上

+

(1) (4) (3)

(5)

其中:

sin ct ( c ) ( c ) j

c

( ) j

( ) j

信号与系统

主 讲 教 师: 赵 仕 良

表明: 对基带信号进行正弦幅度调制,就等于 在频域将基带信号的频谱搬移到载频的位置。 为了在接收端能从 y(t ) 恢复成 x(t ) ,要求频

谱搬移过程中不发生频谱重叠。

为此,应满足: 1. x(t )必须带限于 M。 2.

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(8-5)

6

第八章 数字通信中的锁相同步环路

它与压控振荡器输出电压

相乘, 经环路滤波器滤除4ωo的分量, 得到误差电压 式中

(8-6) (8-7)

7

第八章 数字通信中的锁相同步环路

其中Km为相乘器的系数;

为等效噪声电压。

(8-11)

13

第八章 数字通信中的锁相同步环路

二、同相-正交环 图8-4同相-正交环中, 除VCO和LF之外的所有部分的作用

是, 在接收信号

和VCO输出信号

(8-12)

(8-13)

14

第八章 数字通信中的锁相同步环路

共同作用之下, 产生一个误差电压ud(t), 所以它完全等效为 一个鉴相器。不难证明, 误差电压

[ui(t)+n(t)]2=U2im2(t) sin2[ωo(t)+θ1(t)] +2Uim(t)sin[ω ot+θ1(t)]n(t)+n2(t)

(8-2) 式中第一项展开即可得到2ωo的分量。应用锁相环路提取出这 个2ωo 成分, 再经二分频即可获得BPSK信号的相干载波成分ωo。 由此即可构成提取BPSK信号相干载波的平方环, 如图8-1所示。

(8-26)

31

第八章 数字通信中的锁相同步环路

前面讨论的情况即为ζ=1。另一种常用的情况是ζ=1/2, 此 时的归一化等效鉴相特性变为图8-9所示。同步误差的方 差为

(8-27)

32

第八章 数字通信中的锁相同步环路

图8-9 同相-中相位同步环的归一化等效鉴相特性 (ζ=1/2)

33

第八章 数字通信中的锁相同步环路

42

第八章 数字通信中的锁相同步环路

式中, 为传输时延τ的估值,c1(t)和c2(t)分别与输入信号x(t) 相乘,并经中频滤波后,形成上、下两支路的中频信号y1(t)与 y2(t),且

(8-33)

式中,km为相乘系数,ni(t)为窄带的白高斯噪声,由噪声经中 频窄带滤波器滤波后形成,可表示为

ni(t)=nc(t) cosωct-ns(t) sinωct

几种情况的积分波形如图8-7所示。

24

第八章 数字通信中的锁相同步环路

图8-7 三种情况下的同相和中相积分

25

第八章 数字通信中的锁相同步环路

判决器的输出为

转换判别器的输出为

(8-20) (8-21)

26

第八章 数字通信中的锁相同步环路

相乘器输出

(8-22)

它的作用是对反映定时误差大小的中相积分清除输出模拟量Jk, 按码元转换的不同情况进行处理。无码元转换时, 使ud(t)为零; 码元由正转换到负时, 维持Jk极性不变; 码元由负转换到正时, Jk极性反转。这样就得到准确反映环路定时误差的闭环误差信 号ud(t)。

三、早-迟积分清除位同步环 早-迟积分清除位同步环是一种较易实现的亚最佳同步环。

具体电路有几种形式, 图8-10 为绝对值型早-迟积分清除位同步 环, 信号与噪声同时进入早、迟积分器。它们的积分区间都等 于一个码元持续时间。早积分器的积分起始时刻相对于VCO的 相位中心(对信号码元转换时刻tk的估值tk′ )超前T-Δ, 而迟积分 器则超前Δ, 两者之间覆盖等于2Δ, 如图8-11所示。

(8-24)

30

第八章 数字通信中的锁相同步环路

在线性化条件下, 用等效鉴相特性代入一般环路方程, 在输 入信噪比较大的条件下, 可以算得同步误差τe/T的方差为

(8-25)

以上讨论的是中相积分区间正好等于码元宽度T的情况。 实际应用中可以取积分区间(或称积分“窗口”)小于T, 同样可 以得到误差信号。一般情况下, 中相积分可表示为

(8-30)

39

第八章 数字通信中的锁相同步环路

式中,A为信号振幅,θi可取0°与180°,与数据“1”码及“0” 码相对应,表示信息数据的BPSK调制,cr(u, t-τ)代表扩频码 序列,cr(u, t-τ)为可取±1的二值序列。在二值序列下, cr(u, t-τ)可用cr(t-τ)表示,τ表示传输时延。加上信道的高斯 噪声n(t),则输入信号为

第八章 数字通信中的锁相同步环路

第八章 数字通信中的锁相同步环路

第一节 第二节 第三节 习题

载波同步 码位同步 扩频码的同步跟踪

1

第八章 数字通信中的锁相同步环路

第一节 载 波 同 步

一、平方环

接收信号本身虽然没有载波的频谱分量, 但其中含有载频

的信息, 只要经过非线性变换即可产生载波的倍频分量, 例如

图8-14 延迟锁定环的等效鉴相特性

46

第八章 数字通信中的锁相同步环路

对于噪声,包络检波结果为nc(t)与ns(t)。它们是双边功率 谱密度均为No/2(W/Hz)且相互独立的低频噪声分量。假设低通 滤波器的带宽为B,且有理想矩形特性,则低通滤波器输出噪 声功率为NoB。上、下两支路的噪声功率和为2NoB。这样等效 鉴相器输出噪声可视为双边功率谱密度为

27

第八章 数字通信中的锁相同步环路

由于输入码元序列出现数据转换的概率为1/2, 故平均误差 电压为

此等效误差鉴相特性如图8-8中直线所示。

(8-23)

28

第八章 数字通信中的锁相同步环路

图8-8 同相-中相位同步环的归一化等效鉴相特性 (ζ=1)

29

第八章 数字通信中的锁相同步环路

在有噪情况下, 根据能量比E/No的不同(其中E=PsT是一码 元的能量), 特性变为图8-8中的曲线, 由图可见, 只要输入信噪比 较高(E/No>6 dB), 且误差τe/T较小时, 可以认为是一等效鉴相特 性, 其曲线的斜率为

34

第八章 数字通信中的锁相同步环路

图8-10 绝对值型早 -迟积分清除位同步环

35

第八章 数字通信中的锁相同步环路

图8-11 早-迟积分器的积分区域

36

第八章 数字通信中的锁相同步环路

同样, 早-迟积分清除位同步环中, 除了VCO和LF之外的全 部电路可等效为一个鉴相器, 其等效鉴相特性为

式中, Dn(τe/T)为归一化等效鉴相特性,

BPSK信号

ui(t)=Uim(t) sin[ωot+θ1(t)]

(8-1)

式中Ui为未调载波振幅, m(t)为信号调制, 当m(t)不包含直流分

量时, ui(t)中就不含有载频ωo的频谱分量。

2

第八章 数字通信中的锁相同步环路

当ui(t)与噪声n(t)同时进入接收机之后, 只要经过平方律的 非线性变换, 即可产生2ωo的频谱分量, 即

第八章 数字通信中的锁相同步环路

经过线性近似, 即当θe(t)比较小时

则方程(8-9)式简化为

(8-10)

11

第八章 数字通信中的锁相同步环路

图8-3 平方环线性化噪声相位模型

12

第八章 数字通信中的锁相同步环路

利用这个模型, 可在已知输入信号功率Ps、输入噪声单边 功率谱密度No等条件下, 求得环路的输

图8-1 平方环

4

第八章 数字通信中的锁相同步环路

设输入带通滤波器的带宽Bi足够宽, 可以不失真地传输原 始数据信号m(t), 而Bi与中心频率ωo相比又小得多, 故输出n(t)为 带限白高斯噪声, 可表示为

式中

(8-3)

(8-4)

5

第八章 数字通信中的锁相同步环路

支路增益不平衡,就会有偏移电压叠加到误差电压中,给同步 跟踪性能带来不利影响。显然,只用一个相关器的电路就不存 在增益不平衡的问题。抖动跟踪环只用一条相关器支路,用分 时方式获得本地超前或滞后的PN码序列。抖动跟踪环的原理 组成如图8-15所示。

51

第八章 数字通信中的锁相同步环路

图8-15 抖动跟踪环原理框图

17

第八章 数字通信中的锁相同步环路

图8-5 非归零码的位同步

18

第八章 数字通信中的锁相同步环路

二、同相-中相位同步环 与同作载波同步的同相-正交环相类比, 可以构成用于位同

步的同相-中相环, 如图8-6 所示。

19

第八章 数字通信中的锁相同步环路

图8-6 同相-中相位同步环

20

第八章 数字通信中的锁相同步环路

式中

(8-14)

(8-15)

15

第八章 数字通信中的锁相同步环路

是这个等效鉴相器的灵敏度;

是等效噪声电压。

(8-16)

16

第八章 数字通信中的锁相同步环路

第二节 码 位 同 步

一、非线性变换-滤波法 归零码中含有码元速率的频谱谱线, 可以用锁相环路直接

提取位同步信号。归零码所需的带宽约为非归零码的一倍, 因 此更为常用的数据信号是非归零码。因为非归零码中没有码元 速率的谱线, 码元同步的提取需先对码序列进行非线性变换, 恢复其位信号之后才能用锁相环路来提取, 方法如图8-5所示。

52

第八章 数字通信中的锁相同步环路

设环路输入为

x(t)=s(t)+n(t) =Acr(u, t-τ)cos(ωot+θ+θi)

式中ωc为中频角频率。

(8-45)

53

第八章 数字通信中的锁相同步环路

本地PN码序列产生器提供码序列 加到相乘器之前乘以门控分时信号g(t)。如图8-16所示,g(t)是 一个周期为Tg的方波信号,其中Tg/2时间对应相位超前序列, 取+1值,用g1(t)表示,另Tg/2时间对应相位滞后序列,取-1值, 用g2(t)表示。

(8-34)

43

第八章 数字通信中的锁相同步环路

y1(t)与y2(t)经包络检波,再经低通滤波,对信号而言就是 对载波的幅度部分去统计平均,令检波系数为KD,有