单片机基础考试考点(第3版)

单片机原理及接口技术(第3版)复习题

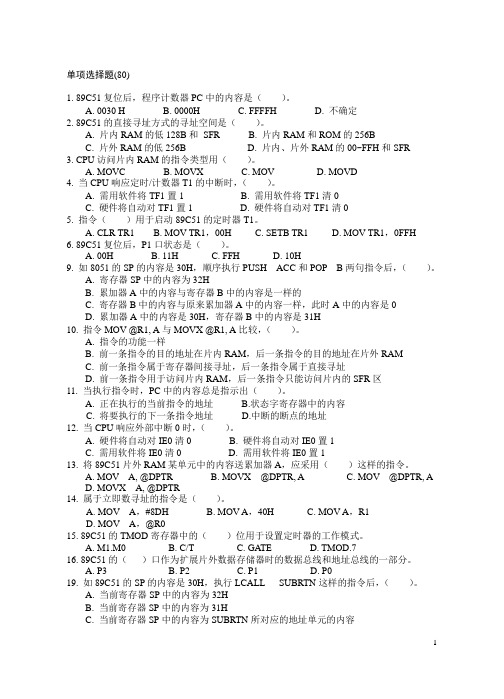

单项选择题(80)1. 89C51复位后,程序计数器PC中的内容是()。

A. 0030 HB. 0000HC. FFFFHD. 不确定2. 89C51的直接寻址方式的寻址空间是()。

A. 片内RAM的低128B和SFRB. 片内RAM和ROM的256BC. 片外RAM的低256BD. 片内、片外RAM的00~FFH和SFR3. CPU访问片内RAM的指令类型用()。

A. MOVCB. MOVXC. MOVD. MOVD4. 当CPU响应定时/计数器T1的中断时,()。

A. 需用软件将TF1置1B. 需用软件将TF1清0C. 硬件将自动对TF1置1D. 硬件将自动对TF1清05. 指令()用于启动89C51的定时器T1。

A. CLR TR1B. MOV TR1,00HC. SETB TR1D. MOV TR1,0FFH6. 89C51复位后,P1口状态是()。

A. 00HB. 11HC. FFHD. 10H9. 如8051的SP的内容是30H,顺序执行PUSH ACC和POP B两句指令后,()。

A. 寄存器SP中的内容为32HB. 累加器A中的内容与寄存器B中的内容是一样的C. 寄存器B中的内容与原来累加器A中的内容一样,此时A中的内容是0D. 累加器A中的内容是30H,寄存器B中的内容是31H10. 指令MOV @R1, A与MOVX @R1, A比较,()。

A. 指令的功能一样B. 前一条指令的目的地址在片内RAM,后一条指令的目的地址在片外RAMC. 前一条指令属于寄存器间接寻址,后一条指令属于直接寻址D. 前一条指令用于访问片内RAM,后一条指令只能访问片内的SFR区11. 当执行指令时,PC中的内容总是指示出()。

A. 正在执行的当前指令的地址B.状态字寄存器中的内容C. 将要执行的下一条指令地址D.中断的断点的地址12. 当CPU响应外部中断0时,()。

A. 硬件将自动对IE0清0B. 硬件将自动对IE0置1C. 需用软件将IE0清0D. 需用软件将IE0置113. 将89C51片外RAM某单元中的内容送累加器A,应采用()这样的指令。

单片机基础(第3版)

1.2.6 实验及实验环境

目标: 1,理解课程讲述的原理、思路 2,应用 3,学习单片机开发、调试的方法、工具 方式 示教 实验课

开发资源

编译器(集成开发环境),Keil 烧写器(仿真器) C语言/汇编语言 原理图 用户手册,用户经验 供货商、论坛

单片机开发的两个思路:

[X+Y]补 = [X]补 + [Y]补 [X-Y]补 = [X]补 - [Y]补 = [X]补 + [-Y]补

1.1.5 计算机中使用的编码

1. 二一十进制编码 在二一十进制编码中最常用的是BCD码。 BCD码共有10个编码,即二进制数0000~1001,分别对应十进制0~9。 2. ASCⅡ码 ASCⅡ码是“美国信息交换标准代码”的简称。是一个16行×8列的矩阵。常用十进制数或十

六进制数来表示ASCⅡ码。如:字符A的ASCⅡ码用十进制数表示为65,用十六进制 数表示为41H。

1.2 单片机概述

1.2.1

什么是单片机

1.2.2

单片机的基本构成

1.2.3

单片机是怎样工作的

1.2.4

单片机的历史及使用情况

1.2.5

课程安排

1.2.6 实验及实验环境

1.2.1 什么是单片机

1.2.2 单片机的基本构成 微 型 计 算 机 系 统

用,主流系列,软、硬件设计资料丰富齐全。

单片机的应用领域

在下述的各个领域广泛的应用: 1. 工业自动化 2. 智能仪器仪表 3.消费类电子产品 4. 通讯 5.武器装备 6.终端及外部设备控制 7.汽车电子

应用领域对单片机的性能要求 使用温度: 民品:0°— +70°C 工业品:-40 — +85°C 汽车:-40— +105°C 军品: -55 — +125°C

单片机基础(第3版)——第3章

3.3 80C51 单片机指令分类介绍 80C51单片机的指令共有111条。这些指令按功 能分成5大类: ——数据传送类(29条) ——算术运算类(24条) ——逻辑运算及移位类(24条) ——控制转移类(17条) ——位操作类(17条)

3.3.1 数据传送类指令 1. 内部RAM数据传送指令组

(4)通过累加器的数据传送指令

MOV A ,direct(直接寻址数据送累加器) MOV A, @Ri ( Ri间接寻址数据送累加器) MOV A, Rn(寄存器内容送累加器) MOV direct, A (累加器内容送直接寻址单元) MOV @Ri , A (累加器内容送Ri间接寻址单元) MOV Rn , A (累加器内容送寄存器)

5. 减1指令组 DEC A (累加器减1) DEC direct (直接寻址单元减1) DEC @Ri ( 间接寻址单元减1) DEC Rn (寄存器减1) 6. 乘法指令组 (1)乘法指令 MUL AB(乘法) (2)除法指令 DIV AB(除法) 7. 十进制调整指令 DA A(十进制调整)

bit:内部RAM(包括专用寄存器)中的直接寻址位。

A:累加器 ACC:直接寻址方式的累加器。 B:寄存器B C :进位标志位。也称为累加位。 / :加在位地址的前面,表示对该位状态取反。 @:间接寻址寄存器的前缀标志。 (X):某寄存器或某单元中的内容。 ((X)):由“X”间接寻址单元中的内容。 ←:箭头左边的内容被箭头右边的内容所取代。

(二)堆栈操作指令 堆栈是在内部RAM中开辟的一个先进后出(后进 先出)的区域,用来保护CPU执行程序的现场 1.入栈指令 PUSH direct; CPU操作:(SP)+1 (SP),修改堆栈指针; (direct) [(SP)],入栈: 例如:MOV SP, #70H 片内RAM 60 A8 PUSH 60H

单片机基础(第3版)——第9章

2. I2C总线器件接入 I2C总线的两条线SCL和SDA都是通过上拉电阻(一般为 10 kΩ)以漏极开路或集电极开路输出的形式接入I2C总线的。

I2C总线如此连接,产生如下硬件关系: 总线系统中各器 件对SCL线是逻辑“与”的关系,对SDA线也是逻辑“与” 关系。反之,对于低电平是逻辑“或”的关系,即系统中任 一器件输出低电平都会使与之相连的总线变低。这种关系使 得I2C总线具有一大优点,即器件可以随时接入或移出,而不 会对系统产生任何不良影响。此外,从图中还可以看出SCL 和SDA均为双向传输线,因为各器件中都有输入和输出控制。 I2C总线通过上拉电阻接正电源。当总线空闲时,两根线均 为高电平。连到总线上的任一器件输出的低电平,都将使总 线的信号变低,即各器件的SDA及SCL都是线“与”关系。

请求访问总线的主机发出起始信号后,发送起始字节 (0000 0001),另一个单片机可以用一个比较低的速率采 样SDA线,直到检测到起始字节中的7个“0”中的一个为止。 在检测到SDA线上的高电平后,单片机就可以用较高的采样 速率,以便寻找作为同步信号使用的第二个起始信号Sr。 在起始信号后的应答时钟脉冲仅仅是为了和总线所使用的 格式一致,并不要求器件在这个脉冲期间作应答。

如果第二字节的方向位B为“1”,则这两个字节命令称 为硬件通用呼叫命令。 在这第二字节的高7位说明自己的地址。接在总线上的智 能器件,如单片机或其他微处理器能识别这个地址,并与 之传送数据。硬件主器件作为从机使用时,也用这个地址 作为从机地址。格式为:

在系统中另一种选择可能是系统复位时硬件主机器件工 作在从机接收器方式,这时由系统中的主机先告诉硬件主机 器件数据应送往的从机器件地址,当硬件主机器件要发送数 据时就可以直接向指定从机器件发送数据了。

单片机基础(第3版)-第4章

定时器函数

用于产生定时器中断或延时。

串口通信函数

用于单片机之间的数据传输。

04

CATALOGUE

单片机应用实例

单片机在智能家居中的应用

智能照明系统

利用单片机控制LED灯的亮度和色温 ,实现节能和舒适的照明环境。

智能安防系统

单片机可以用于监控家庭安全,如门 窗传感器、烟雾报警器等。

智能环境监测

单片机可以监测室内温度、湿度、空 气质量等参数,并通过网络实时上传 数据。

用于连接可编程外设,如定时器、中断控制器等。

03

CATALOGUE

单片机软件编程

单片机编程语言概述

01

02

03

汇编语言

直接与硬件交互,代码效 率高,但可读性差,开发 难度大。

C语言

高效、易读、易维护,适 用于复杂程序开发。

其他语言

如Basic、Pascal等,应用 较少。

C语言在单片机编程中的应用

单片机可以用于控制机器人的运动轨迹和 姿态,实现自动化作业。

单片机在智能仪表中的应用

智能电表

单片机可以用于测量和记录电能消耗,支持 远程抄表和费率控制等功能。

智能水表

单片机可以用于测量和记录水的使用情况, 支持远程抄表和报警等功能。

智能气表

单片机可以用于测量和记录天然气的使用情 况,支持远程抄表和报警等功能。

02

CATALOGUE

单片机硬件结构

单片机的基本组成

01

02

03

04

运算器

用于执行算术和逻辑运算的部 件。

控制单元

负责控制单片机各部件的协调 工作。

存储器

用于存储程序和数据。

输入/输出接口

单片机基础(第3版)——第4章

CJNE A, 55H, LOOP1 ;若Ta≠T55,则转向LOOP1 AJMP FH ;若Ta=T55,则返回 LOOP1:JNC JW ;若(CY)=0,表明Ta>T55,转降温处理程序 CJNE A, 54H, LOOP2 ;若Ta≠T54,则转向LOOP2 AJMP FH ;若Ta=T54,则返回 LOOP2:JC SW FH: RET ;若(CY)=1,表明Ta<T54,转升温处理程序 ;若T55≥Ta≥T54,则返回主程序

4.1.2 单片机使用的高级语言

对于8051单片机,现有4种语言支持,即汇编、 PL/M、C和BASIC。 C语言最终得到广泛应用。 可以大大提高单片机应用系统研制的开发效率。 移植性好。 高级语言的不足:生成的目标代码较长,导致应 用程序运行速度较慢。

4.1.3 80C51 单片机汇编语言的语句格式

4.2.3 循环程序结构

循环结构是重复执行某个程序段。使用条件转移指令通 过条件判断来实现和控制循环。

举例:通过查找结束标志(回车符)以统计字符串长度的循环程序。 设计方法:假定字符串存放在内部RAM从40H单元开始的连续存储 单元中。为找到结束标志,应采用逐个字符依次与回车符(ASCII 码0DH)比较的方法。同时在程序中还应设置一个字符串指针以 顺序定位字符,设置一个字符长度计数器以累计字符个数。

XCH A, R6 ;A←R6,R6←R3R6L+R4(在R6中得 到乘积的第3字节) XCH A, B;A←R3R6H,B←R6 ADDC A, R5 ;R3R6H+R5+(R3R6L+R4时产生的进 位) MOV R5, A;R5←和 MOV F0, C;F0←进位 MOV A, R2 MUL AB;R2×R6(得第4次部分积) ADD A, R5;R2R6L+(R3R6H+R5时 产生的进位) MOV R5, A;在R5中得到乘积的第2字 节 CLR A MOV ACC.0, C;累加器最高位←进位 MOV C, F0 ADDC A, B;R2R6H+F0+ACC.0 MOV R4, A;在R4中得到乘积的第1字 节 RET

单片机基础(第3版)_第3章

内部RAM的40H ~ 4FH单元置初值 单元置初值#A0H ~ #AFH。 例2:将8031内部 : 内部 的 单元置初值 。 解: MOV R0,#40H MOV R2,#10H MOV A,#0A0H LOOP: MOV @R0,A INC R0 INC A DJNZ R2,LOOP ………

1) ORG 1000H MOV A,20H A, MOV 21H,A 21H, RET … ORG 3000H ;取X ;取X(偏移量) ;查表求Y=X ;查表求Y=X2 ;保存Y ;保存Y ;子程序结束 ;其它程序段 ;常数表格首地址 ;平方表 SQU: MOV DPTR,#TAB ;确定表首地址(基地址) DPTR, MOVC A,@A+DPTR A,

0011 1011 + 0011 1011 0111 0110

Cy

ACBiblioteka F0RS1RS0

OV

—

P

例2:A= 9AH,R2= E3H,PSW= 00H,执行指令 : , , , ADDC A,R2 后 , 求: A= ,Cy= ,OV= ,AC= ,P= ,PSW= ?

+ 1

Cy AC F0

1001 1010 1110 0011 0 0111 1101

单片机基础( 单片机基础(第3 版)第三章

80C51 单片机指令系统

3.1 单片机指令系统概述

[标号:] 操作码助记符 [第一操作数 [,第二操作数 [;注释 标号: 第一操作数] 标号 第一操作数 ,第二操作数] ;注释] LOOP: MOV A,#40H ;取参数 : ,

Rn —— 工作寄存器R0 ~ R7 Ri —— 间接寻址寄存器R0、R1 Direct —— 直接地址,包括内部128B RAM单元地址、21个SFR地址 #data —— 8位常数 #data 16 —— 16位常数 addr 16 —— 16位目的地址 addr 11 —— 11位目的地址 rel —— 8位带符号的偏移地址 DPTR —— 16位外部数据指针寄存器 bit —— 可直接位寻址的位 A —— 累加器 B —— 寄存器B C —— 进、借位标志位,或位累加器 @ —— 间接寄存器或基址寄存器的前缀 / —— 指定位求反 (x) —— x中的内容 ((x))—— x中的地址中的内容 $ —— 当前指令存放的地址

单片机基础(第3版)_第5章

(2)设定所用中断源的中断优先级;

(3)若为外部中断,则应确定低电平还是下降沿触发方式。

以设置外部中断0为例: ORG AJMP ORG AJMP MAIN: MOV MOV MOV MOV … EXINT0: … 0000H MAIN 0003H EXINT0 TCON, #01H IE, #81H IP, #01H SP, #3FH

5.3.4 定时器工作方式1 5.3.5 定时器工作方式2

5.3.6 定时器工作方式3

IE TCON

EA

— —

TR1

— —

ES

TR0

ET1 EX1 ET0 EX0

TF1

TF0

IE1

IT1

IE0 TI

IT0 RI

SCON SM0 SM1 SM2 REN

TB8 RB8

IP

—— —— ——

PS

PT1 PX1 PT0 PX0

例5-1 假设允许片内定时器/计数器0中断,禁止其他中断。 试根据假设条件设置IE的相应值。

解:(IE)=10000010B=82H

(a)用字节操作指令

MOV IE,#82H;或 MOV A8H,#82H;

(b)用位操作指令

SETB

SETB

ET0;定时器/计数器0允许中断

EA ;CPU开中断

5.2.3 中断优先级控制

1、优先级排列顺序 中断源 同级内的中断优先级

外部中断0中断 定时器/计数器T0溢出中断 外部中断1 定时器/计数器T1溢出中断 串行口中断

K

K+1

N 保护现场 为外设服务 恢复现场 N+m 返回

单片机基础(第3版)_第7章

方式2(仅用于A口) 方式2(仅用于A 输入 I/O I/O I/O INTRA STBA IBFA × × 输出 I/O I/O I/O INTRA × × ACKA OBFA

联络线用于输入时含义如下: 联络线用于输入时含义如下: 选通信号输入端, (1)STB(Strobe)——选通信号输入端,低电平有 ) ( ) 选通信号输入端 它由外设输入, 效。它由外设输入,当STB=0时,8255接收外设送来 时 接收外设送来 位数据。 的8位数据。 位数据 输入缓冲器满, (2)IBF(Input Buffer Full)——输入缓冲器满,高 ) ( ) 输入缓冲器满 电平有效。 电平有效。当IBF=1时,表示当前有一个新数据在输 时 入缓冲器中,可作为状态信号, 查询用。 入缓冲器中,可作为状态信号,供CPU查询用。 查询用 它是8255送往 ( 3) INTR( Interrupt Request) ——它是 ) ( ) 它是 送往 CPU的中断请求信号,高电平有效。 在STB=IBF=1时, 的中断请求信号, 的中断请求信号 高电平有效。 时 INTR=1。也就是说,当选通信号 结束, 。也就是说,当选通信号STB结束,已将一个 结束 数据送入输入缓冲器中, 并且输入缓冲器满信号IBF 数据送入输入缓冲器中 , 并且输入缓冲器满信号 已经为高电平时, 会向CPU发出中断请求信号 已经为高电平时 , 8255会向 会向 发出中断请求信号 INTR=1。在CPU响应中断后读取缓冲器的数据时,由 响应中断后读取缓冲器的数据时, 。 响应中断后读取缓冲器的数据时 单片机RD的下降沿将 的下降沿将INTR降为 , 使 IBF无效, 通知 降为0, 无效, 单片机 的下降沿将 降为 无效 外设再一次输入数据。 外设再一次输入数据。

单片机基础(第3版)_第4章

(2)多重单分支结构举例 2. 多分支程序结构

图4.1 多分支程序结构

(1)通过数据表实现程序多分支 (2)通过转移指令表实现程序多分支 (3)其他实现程序多分支的方法 4.2.3 循环程序结构 4.3 80C51 单片机汇编语言程序设计举例 4.3.1 算术运算程序 1. 加减法运算 (1)多个不带符号的单字节数相加 (2)两个不带符号的多字节数相减 2. 乘法运算

图4.2

两个双字节无符号数乘法示意图

3. 除法运算 4.3.2 定时程序 1. 单循环定时程序 2. 较长时间的定时程序 3. 调整定时时间程序 4. 通过一个基本延时程序产生不同的定时 4.3.3 查表程序 1. 查表指令 2. 查表程序举例 4.4 单片机汇编语言源程序的编辑和汇编 4.4.1 手工编程与汇编 4.4.2 机器编辑与交叉汇编

李广弟等编著北京航空航天大学出版社2007年680c51单片机汇编语言程序设计41单片机程序设计语言概述411机器语言和汇编语言412单片机使用的高级语言41380c51单片机汇编语言的语句格式分界符分隔符42汇编语言程序的基本结构形式421顺序程序结构422分支程序结构单分支程序结构1单分支结构举例2多重单分支结构举例多分支程序结构图41多分支程序结构1通过数据表实现程序多分支2通过转移指令表实现程序多分支3其他实现程序多分支的方法423循环程序结构4380c51单片机汇编语言程序设计举例431算术运算程序加减法运算1多个不带符号的单字节数相加2两个不带符号的多字节数相减乘法运算图42两个双字节无符号数乘法示意图除法运算432定时程序通过一个基本延时程序产生不同的定时433查表程序查表程序举例44单片机汇编语言源程序的编辑和汇编441手工编程与汇编442机器编辑与交叉汇编图43单片机汇编语言程序生成过程4580c51单片机汇编语言伪指令汇编起始地址命令orgorigin定义字节命令dbdefinebyte定义数据字命令dwdefineword定义存储区命令dsddfinestonage

李朝青 单片机原理及接口技术(第3版)期末考试必考重点

2.3 存储器组织

2.3.1 MCS-51储存器特点

FFFFH 外部

FFFFH 外部 RAM

ROM

1000H 0FFFH 内部 ROM (EA=1) 0FFFH 外部 ROM

7FH

特殊功能寄存器 (21个SFR ) FFH 80H 内部 128BRAM 00H (b) 0000H

(64KB)

0000H

Vcc

Vcc P1R1

8051

R* D C Q Q P10

R1 D1 K1

写数据

D0 P1W P1R2

P10 P11

读端口 图2、P1口内部结构

MOV P1, #0FFH JNB P1.1, $ CLR P1.0

图2.1、P1口应用

2.4.3 P2口内部结构

说明:

1、P2可以作为通用的I/O,

也可以作为高8位地址输出。 2、当控制信号为1时

单片机原理及接口技术

第三版 李朝青

第2章 MCS-51系列单片机的结构和原理

1.掌握单片机的基本结构(CPU、ROM、RAM、 定时/计数器、并行I/O、全双工串行口、中断系统、 总线结构)。 2.掌握特殊功能寄存器SFR的功能、作用及它们复 位后的状态。 3.掌握存储器的组织结构(分ROM和RAM)及对 应的寻址方式。 4.了解单片机的工作时钟与时序。

1、P0口作通用I / O口使用

(1)通用输出 此时必须外接上拉电阻。 (2)通用输入 ①读引脚:CPU在执行“MOV” 类输入指令时(如:MOV A , P0),内部产生的操作信号是 “读引脚”。P0.X引脚上的数据 经过缓冲器2读入到内部总线。

注意:在读引脚时,必须先向电路中的锁存器写入1。 MOV P0, #0FFH MOV A, P0

单片机基础(第3版)——第6章

闪速存储器全称为快闪可编程/擦除只读存储器,简称闪速存 储器或Flash ROM。

6.2.2 数据存储器

在单片机系统中,数据存储器用于存放可随时修改 的数据。数据存储器扩展使用随机存储器芯片,随机存 储器(Random Access Memory)简称RAM。

2. 可编程只读存储器(PROM)

PROM(Programmable Read Only Memory)芯片 出厂时没有任何程序信息,其程序是在开发现场由用户 写入的。但这种ROM芯片只能写入一次,其内容一旦 写入就不能再进行修改。

3. 可擦除可编程只读存储器(EPROM)

EPROM(Erasable Programmable Read Only Memory)芯 片的内容也由用户写入,但允许反复擦除重新写入。EPROM是 用紫外线擦除。

2. 内外程序存储器的衔接 出于连续执行程序的需要,内外程序存储器必须统一连 续编址,并使用相同的读指令MOVC。内外ROM面临地 址衔接问题。再考虑到80C51单片机系列芯片中,有些 芯片有内部ROM,有些芯片没有内部ROM。为此, 80C51单片机特别配置了一个EA(访问内外程序存储器 控制)信号。

A10~A0: 11位地址。 O7~O0: 数据读出。 CE/PGM: 片线。 OE: 输出允许信号。

ቤተ መጻሕፍቲ ባይዱ716引脚图 单片程序存储器扩展连接图

(1)存储器扩展的主要内容

存储器扩展的主要内容是地址线、数据线和控制线的连 接。2716的存储容量为2 KB,需11位地址(A10~A0)进 行存储单元编址。芯片的A7~A0引脚与地址锁存器的8位 地址输出对应连接,再把A10~A8引脚与P2口的P2.2~ P2.0相连。采用线选法进行片选,只需在剩下的高位地址 线中取一位(P2.7)与2716的CE端相连即可。

单片机基础(第3版)——第3章

第3章 MCS-51系列单片机指令系统

例如

0000H START

ORG LJMP

ORG 2000H START:-------------------

. . .

主程序实际从2000H开始存放,复位后,通过 跳转指令LJMP转移至2000H开始执行。

第3章 MCS-51系列单片机指令系统

[标号]: 操作码

1)数据传送指令 2)算术运算指令 3)逻辑运算指令

4)位操作指令

5)控制转移指令

第3章 MCS-51系列单片机指令系统

2、符号的说明

(1)Rn:表示当前选中的寄存器区的8个工作寄 存器,(n=0-7)中的一个。 (2) @ Ri: 表 示 寄 存 器 间 接 寻 址 , Ri 只 能 是R0或R1。 (3)#data:8 位 直 接 地 址 , 实 际 使 用 时 data应是00H-FFH中的一个。 (4)#data16: 表 示 包 含 在 指 令 中 的 16 位 立 即数。

第3章 MCS-51系列单片机指令系统

3.2.5

相对寻址

说明

寻址空间:程序存储器

偏移量rel的范围是:–128 ~ +127

转移公式:

PC目的地址 = PC当前地址 + rel

第3章 MCS-51系列单片机指令系统

3.2.6

变址寻址

以DPTR和PC基址寄存器 和累加器A变址寄存器的内 容和为地址,寻址该地址单 元,读取数据。

指令字节数少。单字节指令有49条,双字 节指令有45条,三字节指令仅有17条。

位操作指令丰富。

第3章 MCS-51系列单片机指令系统

§3.1 MCS-51系统单片机指令格式

单片机基础(第3版——第8章

/输出。 方式0实现数据并行输入/输出“并入串出”芯片 (74165)用于பைடு நூலகம்并行输入数据通过移位形成位串, 传送

给串行口;而“串入并出”芯片(74164)则接收串 行口的串行数据, 通过移位形成8位并行数据输 出。

80C51串行口寄存器结构

8.2.2 串行口控制机制

80C51串行口通过控制寄存器、中断功能和波特率设置实现串行通 信控制。

1.串行口控制寄存器(SCON)-98H

■ SM0、SM1——串行口工作方式选择位。其状态组合所对应的 工作方式为:

■ SM0SM1=00,工作方式0;SM0SM1=01,工作方式1; SM0SM1=10,工作方式2;SM0SM1=11,工作方式3。

工作方式0时, 移位操作(串入或串出)的波特率是固定的, 为单片机晶振频率的1/12, 若晶振频率用fosc表示, 则波特率=fosc/12。按此波特率的一个机器周期进行 一次移位, 若fosc=6 MHz, 则波特率为500 kb/s, 即 2 μs移位一次。

利用串行口方式0实现数据并行输入/输出

8.3.3 串行工作方式2 和3

串行工作方式2和3都是11位为一帧的串行通信方式, 即 1个起始位、9个数据位和1个停止位。

在这两种工作方式下, 字符还是8个数据位, 只不过增 加了一个第9数据位(D8), 它是一个可编程位, 其 功能由用户设定。

在发送数据时, 应予先在串行口控制寄存器SCON的 TB8 位中把第9个数据位的内容准备好。

单片机基础(第3版)

第8章 80C51单片机串行通信

1. 串行通信基础知识 2. 80C51串行口 3. 80C51串行口工作方式 4. 串行通信数据传输速率 5. 串行通信应用

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PA

8051

A1 A0

PB 8255

ALE

EA VCC

D7 D6 D5 D4 D3 D2 D1 D0

• 0023H~002AH:串行中断地址区

• 例 (1) P1.0=ACC.2∧B.5∨PSW.3∧ P2.5; • MOV C, ACC.2; • ANL C, B.5; • ORL C, PSW.3; • ANL C, P2.5; • MOV P1.0,C • (2) P3.7= (ACC.5∧ P1.5 )∨(B.3 ∨ PSW.4) • MOV C, ACC.5; • ANL C, P1.5; • MOV 7FH, C; • MOV C, B.3; • ORL C, PSW.4; • ORL C, 7FH; • MOV P3.7,C

P2 P2 P2 P2 P2 P2 P2 P0 P0 P0 P0 P0 P0 P0 P0 .6 .5 .4 .3 .2 .1 .0 .7 .6 .5 .4 .3 .2 .1 .0

A A A A A A 14 13 12 11 10 9 A 8 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

2764(1)芯片内部存储单元的地址范围4000H~7FFFH

口 P2 线 .7 地 A 址 线 15 最 低 1 地 址 最 高 1 地 址 Intel

P2 P2 P2 P2 P2 P2 P2 P0 P0 P0 P0 P0 P0 P0 P0 .6 .5 .4 .3 .2 .1 .0 .7 .6 .5 .4 .3 .2 .1 .0

A A A A A A 14 13 12 11 10 9 A 8 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

2764(2)芯片内部存储单元的地址范围8000H~0BFFFH

7.2.4 8255接口应用

1、8255与单片机的接口电路设计

2764(1) /CE A12 A11 A10 A9 A8 P2.4 P2.3 P2.2 P2.1 P2.0

2764(2) /CE A12 A11 A10 A9 A8

A7 A6 A5 A4 A3 A2 A1 A0

Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0

A7 A6 A5 A4 A3 A2 A1 A0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

2764(2)芯片内部存储单元的地址范围8000H~9FFFH

80C51 P2.7 P2.6 P2.5 P2.4 P2.3 P2.2 P2.1 P2.0 /CE

2764(1) /CE A12 A11 A10 A9 A8 74LS373 P2.6 P2.4 P2.3 P2.2 P2.1 P2.0

80C51 P2.7 P2.6 P2.5 P2.4 P2.3 P2.2 P2.1 P2.0 74LS373 ALE P0.7 P0.6 P0.5 P0.4 P0.3 P0.2 P0.1 P0.0 G D7 D6 D5 D4 D3 D2 D1 D0 Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0

2716 /CE

HERE: LJMP HERE ORG 0200H INTT0: CPL TR0 RETI ORG 0300H TTC0: CPL P1.0 CLR TR0 SETB TR1 RETI ORG 0400H TTC1: CPL P1.0 CLR TR1 SETB TR0 RETI END 产生2:5的矩形波程序清单

80C51单片机中断系统内部结构图

TCON IT 0 = 0 IN T 0 IT 0 = 1 T0 1 PX0 IE 0 EX0 PT0 TF0 EX0 IT 1 = 0 IN T 1 IT 1 = 1 T1 PX1 IE 1 EX1 PT1 TF1 ET1 TX R X TI RI SCO N 中断标志 ≥ 1 ES 源允许 EA 总允许 PS 0 1 0 1 0 优先级 自 然 优 先 级 低 级 中 断 请 求 PC 矢量 地址 硬件查询 0 1 0 1 矢量 地址 1 IE IP 自 然 优 先 级 高 级 中 断 请 求 PC

P2 P2 P2 P2 P2 P2 P2 P0 P0 P0 P0 P0 P0 P0 P0 .6 .5 .4 .3 .2 .1 .0 .7 .6 .5 .4 .3 .2 .1 .0

A A A A A A 14 13 12 11 10 9 A 8 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0

中断响应的条件是什么?

• 1 CPU正处在位一个同级或高级的中断的服务中 • 2 查询中断请求的机器周期不是当前指令的最后一个机 器周期 • 3 当前指令是返回指令(RET,RETI)或访问IE,IP的指令 • •

复位后的状态是怎样的?

PC为0000H,SP为07H,各I/O口锁存器为FFH,SBUF状态不 定,其他寄存器大多被置为00H

2764(2) /CE A12 A11 A10 A9 A8

ALE P0.7 P0.6 P0.5 P0.4 P0.3 P0.2 P0.1 P0.0

G D7 D6 D5 D4 D3 D2 D1 D0

Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0

A7 A6 A5 A4 A3 A2 A1 A0

Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0

A A A A A A 14 13 12 11 10 9 A 8 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

2764(1)芯片内部存储单元的地址范围0000H~1FFFH

口 P2 线 .7 地 A 址 线 15 最 低 1 地 址 最 高 1 地 址 Intel

取自41H单元的低半字节。

• • • • • • • • • • • • •

(7)程序清单; ORG 2000H START: MOV R1, MOV A, ANL A, SWAP A; INC R1; XCH A, ANL A, ORL A, INC R1; MOV @R1, END

#40H;初始化数据指针R1的内容 @R1; 取40H单元内容送A #0FH;保留40H单元内容低4位 40H单元内容高低半字节互换 修改数据指针R1的内容 @R1; (A)与@R1内容互换 #0FH;保留41H单元内容低四位 @R1; 合字生成新字节 修改数据指针R1的内容 A; 新字节送42H单元保存

A7 A6 A5 A4 A3 A2 A1 A0

O7 O6 O5 O4 O3 O2 O1 O0 /PSEN /EA +5V /OE

P0.7 P0.6 P0.5 P0.4 P0.3 P0.2 P0.1 P0.0 /PSEN

O7 O6 O5 O4 O3 O2 O1 O0 /OE

口 P2 线 .7 地 A 址 线 15 最 低 0 地 址 最 高 0 地 址 Intel

O7 O6 O5 O4 O3 O2 O1 O0 /PSEN /EA +5V /OE

O7 O6 O5 O4 O3 O2 O1 O0

O7 O6 O5 O4 O3 O2 O1 O0 /OE

口 P2 线 .7 地 A 址 线 15 最 低 0 地 址 最 高 0 地 址 Intel

P2 P2 P2 P2 P2 P2 P2 P0 P0 P0 P0 P0 P0 P0 P0 .6 .5 .4 .3 .2 .1 .0 .7 .6 .5 .4 .3 .2 .1 .0

• 例:设内部RAM 40H,41H

单元中分别存放8位二进制

数,现分别取这两个单元 中的半个字节,合并成一 个新字节存放在42H单元中 。要求如下:42H单元新字 节的低半字节取自40H单元 的低半字节,而高半字节

开始 取 40H单 元 内 容 保 留 40H单 元 低 半 字 节 取 41H单 元 内 容 保 留 41H单 元 低 半 字 节 合字并保存 结束

SETB

LOOP:JNB MOV MOV

TR1;

启动定时器

定时时间到 Y 重置计数初值 清计数溢出标志 P1.0口 线 取 反

TF1, LOOP;查询计数溢出否 TH1, #0FCH;重置计数初值 TL1, #03H;

CLR

CPL AJMP END

TF1;清计数溢出标志

P1.0; LOOP; 输出取反 重复循环

•

•

图1.4 以运算器为中心的计算机框图 图