PLD设计实例

实验六 交通灯控制电路的PLD设计

实验八交通灯控制电路的PLD设计一、实验目的1、熟练掌握Max+plus II软件平台菜单及命令的使用2、掌握Max+plus II完成电路的四个步骤:图形输入编译波形仿真和下载3、理解并检验仿真波形和真值表之间的对应关系4、了解所用芯片的管脚排列与数字实验系统EPM7000的使用方法5、理解输入与输出波形的逻辑关系,能够从波形图判断电路是否符合设计要求二、预习要求1、阅读附录中Max+plus II的使用方法2、阅读数字实验系统EPM7000的使用方法3、复习教材中有关时序逻辑电路的设计方法4、掌握Max+plus II元器件库中各种不同功能元器件型号及其调用方法5、掌握Max+plus II中电路“层”的使用。

三、实验仪器与设备1、EPM7000S实验系统2、计算机3、Max+plus II软件四、知识点及涉及内容本实验属于综合设计性实验,知识点包括JK触发器的应用,组合电路的分析设计方法,基本门电路的功能掌握与使用以及Max+plus II软件编程与PLD的电路设计。

1、设计任务在某交叉路口的南北方向设置有红灯(A1)、黄灯(B1)、绿灯(C1),东西方向也设置有红灯(A2)、黄灯(B2)、绿灯(C2)。

红灯亮是停车信号,绿灯亮是通车信号,黄灯亮是右转弯信号。

根据交通规则,上述信号灯应该按照8-1流程循环。

试用三个JK触发器设计一个三位二进制同步计数器,并将其输出信号Q3Q2Q1经控制电路启动实验箱上的红、黄、绿信号灯,使其按图8-1流程循环。

图8-1图8-22、简要提示根据设计任务要求,可得整体电路框图如图8-2所示,其中Q3、Q2、Q1与信号灯A1(C2)、B1(B2)、C1(A2)的关系如表8-1所示(表中信号灯“1”表示亮,“0”表示灭)据计数器状态输出可列出三个JK 触发器的状态方程,再与其特征方程联立,列出其驱动表达式;同时,也由Q3、Q2、Q1输入状态列出信号灯控制电路的输出表达式(A 、B 、C 由Q3Q2Q1逻辑运算得到),然后按要求化简,注意输出信号的多次利用才能减少所用门的数量。

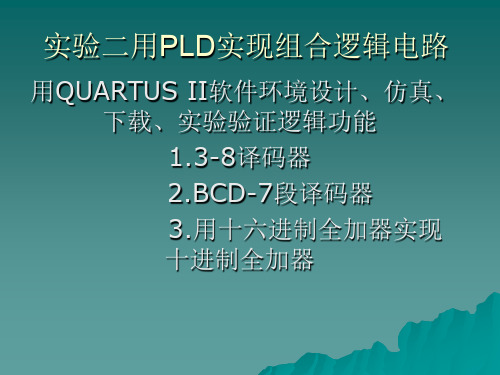

实验二用PLD实现组合逻辑电路

清除方式 紫外線 電力清除 電力清除

--關掉電源

型式 非揮發性 非揮發性 非揮發性 非揮發性 揮發性

安全措施 有 有 有 有 沒有

QUARTUS II设计流程

数字逻辑电路设计环境

选择File

1、建立项目

2、设计输入

双击空白处

选择器件

完成图形输入

Hale Waihona Puke 3、编译项目4、仿真项目

双击双左击键左键

存盘

5、引脚分配

存盘,再编译

6、下载

实验报告要求

总结QUARTURS II操作步骤 设计过程及原理电路图 测试结果或仿真波形图 预习 1、用Verilog HDL设计七段译码器 2、用十六进制全加器实现十进制全加器

实验二用PLD实现组合逻辑电路

用QUARTUS II软件环境设计、仿真、 下载、实验验证逻辑功能 1.3-8译码器 2.BCD-7段译码器 3.用十六进制全加器实现 十进制全加器

CPLD应用讲授內容

CPLD的简介 EDA 工具-QUARTUS II 快速入门电脑辅助数字电路设计 3-8译码器设计、实现过程

CPLD集成单元的內部结构

FPGA/CPLD的制造技术

FPGA/CPLD以CMOS为制作程序

目前共有EPROM、 EEPROM 、FLASH、 SRAM及Anti-Fuse等五种制造技术。

技術種類 EPROM EEPROM FLASH

Anti-Fuse SRAM

可重規劃性 可 可 可 不可 可

pld应用程序举例

PLD应用程序举例PLD〔可编程逻辑器件〕是一种集成电路,它具有重要的应用领域。

在本文档中,我们将介绍几个常见的PLD应用程序的例子,包括数字逻辑电路、数据通信系统和图像处理。

数字逻辑电路数字逻辑电路是PLD应用程序的一种常见形式。

它们由逻辑门和触发器组成,用于实现各种逻辑功能。

下面是一些常见的数字逻辑电路应用程序:1. 门电路门电路由逻辑门组成,逻辑门有与门、或门、非门等。

门电路可以用于实现布尔逻辑操作,如逻辑与、逻辑或、逻辑非等。

PLD可以程序化配置,实现各种不同的逻辑电路。

2. 计数器和时序电路计数器是数字电路中常见的一个组件,可以用来计数和分频。

PLD 可以用来实现各种不同类型的计数器,如二进制计数器、BCD计数器等。

时序电路用于控制信号的时序和时钟分频,也可以通过PLD来实现。

3. 十进制解码器十进制解码器是将BCD码或二进制编码转换为七段显示器所需的信号的电路。

PLD可以用来实现十进制解码器,从而实现数字显示。

数据通信系统PLD在数据通信系统中也有广泛的应用。

它们可以用于实现各种不同的通信协议和接口。

下面是一些常见的数据通信系统应用程序:1. UARTUART〔通用异步收发器〕是一种常见的串行通信接口。

PLD可以用来实现UART接口,使设备能够进行串行通信。

2. SPISPI〔串行外设接口〕是一种用于连接多个外设的通信协议。

PLD 可以用来实现SPI接口,使设备能够与其他外设进行通信。

3. I2CI2C〔串行总线接口〕是一种用于连接多个设备的通信协议。

PLD 可以用来实现I2C接口,使设备能够进行多设备通信。

图像处理PLD也可以在图像处理领域发挥重要作用。

它们可以用于实现各种图像处理算法和滤波器。

下面是一些常见的图像处理应用程序:1. 图像滤波器图像滤波器可以用于平滑、锐化或增强图像。

PLD可以用来实现各种滤波器,如均值滤波器、中值滤波器等。

2. 图像压缩图像压缩是减少图像文件大小的过程。

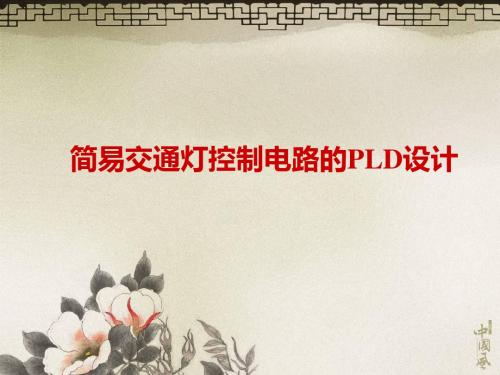

简易交通灯控制的PLD设计

设计的交通灯控制系统具有灵活性高、可靠性好、易于扩展等优点,能 够满足实际交通需求,具有一定的实用价值。

在设计过程中,我们采用了自顶向下的设计方法,将整个系统划分为多 个模块,便于代码编写和调试。同时,我们还采用了仿真测试的方法, 对设计的正确性进行了验证。

电源电路

用于提供稳定的电源,确保交 通灯的正常工作。

交通灯控制系统的基本工作原理

信号采集

通过传感器或其他设备检测道 路上的车辆和行人流量,并将

信号输入控制电路。

信号处理

控制电路根据输入的信号和时 钟电路的定时信号,计算出各 个方向上通行或等待的时间。

输出控制

控制电路根据计算结果,控制 红、绿、黄三色灯的亮灭,指 示车辆和行人通行或等待。

展望

在未来的工作中,我们可以进一步优化交通灯控制逻辑,提高系统的效率和可靠性。例如, 可以通过增加传感器和检测器,实现交通灯的自动调节和智能控制。

此外,我们还可以将该设计应用于其他领域,如智能家居、工业自动化等,实现更广泛的用 途。同时,我们也可以将该设计与其他技术相结合,如人工智能、物联网等,实现更加智能 化的控制和管理。

最后,我们希望本次设计能够为其他相关领域的研究提供一定的参考和借鉴,推动相关领域 的发展和进步。

感谢观看

THANKS

交通灯控制系统需要处理复杂的逻辑 关系,如红、绿、黄灯的顺序切换和 时间间隔,以满足道路交通的需求。

PLD简介

PLD,即可编程逻辑器件,是一种集成 电路,其逻辑功能可以根据用户的需求

进行编程和配置。

PLD包括多种类型,如可编程逻辑阵列 (PLA)、可编程阵列逻辑(PAL)、 通用可编程逻辑(GAL)和复杂可编程

实验二用PLD实现组合逻辑电路15714共35页文档

END

技術種類 EPROM EEPROM FLASH

Anti-Fuse SRAM

可重規劃性 可 可 可 不可 可

清除方式 紫外線 電力清除 電力清除

--關掉電源

型式 非揮發性 非揮發性 非揮發性 非揮發性 揮發性

安全措施 有 有 有 有 沒有

QUARTUS II设计流程

数字逻辑电路设计环境

选择File

CPLD应用讲授內容

CPLD的简介 EDA 工具-QUARTUS II 快速入门电脑辅助数字电路设计 3-8译码器设计、实现过程

CPLD集成单元的內部结构

FPGA/CPLD的制造技术

FPGA/CPLD以CMOS为制作程序

目前共有EPROM、 EEPROM 、FLASH、 SRAM及Anti-Fuse

双击空白处

选择器件

完成图形输入

3、编译项目

4、仿真项目

双击双左击键左键

存盘

5、引脚分配

存盘,再编译

6、下载

实验报告要求

总结QUARTURS II操作步骤 设计过程及原理电路图 测试结果或仿真波形图 预习 1、用Verilog HDL设计七段译码器 2、用十六进制全加器实现十进制全加器

PLD可编程逻辑器件-pld应用程序举例 精品

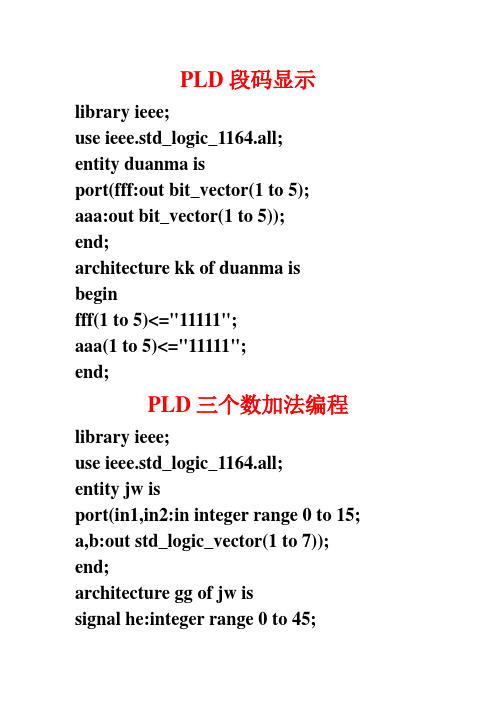

PLD段码显示library ieee;use ieee.std_logic_1164.all;entity duanma isport(fff:out bit_vector(1 to 5); aaa:out bit_vector(1 to 5));end;architecture kk of duanma isbeginfff(1 to 5)<="11111";aaa(1 to 5)<="11111";end;PLD三个数加法编程library ieee;use ieee.std_logic_1164.all;entity jw isport(in1,in2:in integer range 0 to 15; a,b:out std_logic_vector(1 to 7)); end;architecture gg of jw issignal he:integer range 0 to 45;beginhe<=in1+in2;with he selecta<="1111110" when 0|10|20|30|40, "0110000" when 1|11|21|31|41, "1101101" when 2|12|22|32|42, "1111001" when 3|13|23|33|43, "0110011" when 4|14|24|34|44, "1011011" when 5|15|25|35|45, "1011111" when 6|16|26|36, "1110000" when 7|17|27|37, "1111111" when 8|18|28|38, "1111011" when 9|19|29|39, "0000000" when others;with he selectb<="0000000" when 0<=he and he<=9,else "0110000" when 10<=he andhe<=19,else"1101101" when 20<=he andhe<=29,else"1111001" when 30<=he andhe<=39,else"0110011" when 40<=he andhe<=39,else"0000000" when others;end;PLD八个按键两个灯library ieee;use ieee.std_logic_1164.all;entity guozi3 isport(in1,in2:in std_logic_vector(1 to 4); a,b:out std_logic_vector(1 to 8)); end;architecture gg of guozi3 isbeginwith in1 select"0110000" when "0001", "1101101" when "0010", "1111001" when "0011", "0110011" when "0100", "1011011" when "0101", "1011111" when "0110", "1110000" when "0111","1111111" when "1000", "1111011" when "1001", "0000000" when others;with in2 selectb<="0110000"when "0001", "1101101" when "0010", "1111001" when "0011", "0110011" when "0100", "1011011" when "0101", "1011111" when "0110", "1110000" when "0111", "1111111" when "1000", "1111011" when "1001", "0000000" when others;end;PLD顺序语句编程(0加到9) library ieee;use ieee.std_logic_1164.all;entity jinchen isport(in1:in std_logic;a:out std_logic_vector(1 to 7));end;architecture gg of jinchen is signal ss:integer range 0 to 9; beginprocessbeginwait until in1='1';ss<=ss+1;if ss=10 thenss<=0;end if;end process;with ss selecta<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others;end;PLD矢量10个控制2个数码管library ieee;use ieee.std_logic_1164.all;entity kongzhi2 isport (a:out bit_vector(1 to 7);b:in bit_vector(1 to 10));end;architecture ff of kongzhi2 is begina<="1111110"when b="1000000000"else"0110000"when b="010*******"else"1101101"when b="0010000000"else"1111001"when b="1001000000"else"0110011"when b="1000100000"else"1011011"when b="1000010000"else"1011111"when b="1000001000"else"1110000"when b="1000000100"else"1111111"when b="1000000010"else"1110011"when b="1000000001"else"0000000";end;PLD晶振50M控制数码管library ieee;use ieee.std_logic_1164.all; entity jinzheng isport(in50m:in std_logic;a:out std_logic_vector(1 to 7)); end;architecture gg of jinzheng is signal in1:std_logic;signal ss:integer range 0 to 9;signal count:integer range 0 to 25000000;beginprocessbeginwait until in50m='1';count<=count+1;if count=25000000 thencount<=0;in1<=not in1;end if;end process;processbeginwait until in1='1';ss<=ss+1;if ss=10 thenss<=0;end if;end process;with ss selecta<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others;end;PLD晶振50M自动跳变程序(0到59)library ieee;use ieee.std_logic_1164.all;entity jiadxx isport(in50m:in std_logic;a,b:out std_logic_vector(1 to 7)); end;architecture gg of jiadxx issignal in1:std_logic;signal t,g:integer range 0 to 9;signal count:integer range 0 to 59 25000000;beginprocessbeginwait until in50m='1';count<=count+1;if count=25000000 thencount<=0;in1<=not in1;end if;end process;processbeginwait until in1='1';g<=g+1;if g=9 then if g=5 then 改变变量g<=0;t<=t+1;if t=5 thent<=0;end if;end if;end process;with g selecta<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others; with t selectb<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others;end;PLD(1-8数码管显示)第六个显示0 library ieee;use ieee.std_logic_1164.all;entity jiadxx isport(a:out std_logic_vector(1 to 7);b:out std_logic_vector(1 to 3)); end;architecture kk of jiadxx isbegina<="1111110"; --显示的数“0”b<="010"; --显示的位“第6位”end;PLD动态间隔1秒闪烁library ieee;use ieee.std_logic_1164.all;entity jiadxx isport(in50m:in std_logic;b:out std_logic_vector(1 to 3);a:out std_logic_vector(1 to 7)); end;architecture gg of jiadxx issignal count:integer range 0 to 25000000;signal count_one:integer range 0 to 1; signal one_hz:std_logic;beginprocessbeginwait until in50m='1';count<=count+1;if count=25000000 thencount<=0;one_hz<=not one_hz;end if;end process;processbeginwait until one_hz='1';count_one<=count_one+1;if count_one=0 thenb<="000";elseb<="001";end if;end process;a<="1111110";end;PLD动态显示0 1 library ieee;use ieee.std_logic_1164.all;entity dz1121 isport(in50m:in std_logic;a:out std_logic_vector(1 to 7);b:out std_logic_vector(1 to 3));end;architecture gg of ningyi issignal in1:std_logic;signal count_c:integer range 0 to 3; signal count:integer range 0 to 2500; beginprocessbeginwait until in50m='1';count<=count+1;if count=2500 thencount<=0;in1<=not in1;end if;end process;processbeginwait until in1='1';count_c<=count_c+1;if count_c=1 thencount_c<=0;end if;end process;with count_c selecta<="1111110"when 0,"0110000"when 1,"0000000"when others;with count_c selectb<="000" when 0,"001" when 1,"111" when others;end;PLD数码管显示0-7 library ieee;use ieee.std_logic_1164.all;entity xian0-7 isport(in50m:in std_logic;a:out std_logic_vector(1 to 7);b:out std_logic_vector(1 to 3));end;architecture gg of xian0-7 issignal in1:std_logic;signal count_c:integer range 0 to 7; signal count:integer range 0 to 2500; beginprocessbeginwait until in50m='1';count<=count+1;if count=2500 thencount<=0;in1<=not in1;end if;end process;processbeginwait until in1='1';count_c<=count_c+1;case count_c iswhen 0=>b<="000"; --a<="1111110"; when 1=>b<="001";a<="0110000"; when 2=>b<="010";a<="1101101"; when 3=>b<="011";a<="1111001"; when 4=>b<="100";a<="0110011"; when 5=>b<="101";a<="1011011"; when 6=>b<="110";a<="1011111"; when 7=>b<="111";a<="1110000";if count_c=7 thencount_c<=0;end if;end case;end process;end;PLD时钟显示library ieee;use ieee.std_logic_1164.all;entity shizon isport(in50m: std_logic;a:out std_logic_vector(1 to 7);--段码b:out std_logic_vector(1 to 3));--位码end;architecture ff of shizon issignal count:integer range 0 to 250;--整数定义signal count_s:integer range 0 to25000;--半秒定义signalg1,g2,s1,s2,b1,b2:std_logic_vector(1 to 7);--变量范围signal one_hz:std_logic;--定义1赫兹信号signal one_s:std_logic;signal x:integer range 0 to 7;--signal gg1,gg2,ss1,ss2,bb1,bb2:integer range 0 to 9;beginprocessbeginwait until in50m='1';count<=count+1;if count=250 thencount<=0;one_hz<=not one_hz;end if;end process;processbeginwait until in50m='1'; count_s<=count_s+1; if count_s=25000 then count_s<=0;one_s<=not one_s; end if;end process;processbeginwait until one_hz='1'; x<=x+1;case x iswhen 0=>b<="000";a<=g1;when 1=>b<="001";a<=g2;when 2=>b<="010";a<="0000001"; when 3=>b<="011";a<=s1;when 4=>b<="100";a<=s2 ;when 5=>b<="101";a<="0000001"; when 6=>b<="110";a<=b1;when 7=>b<="111";a<=b2;x<=0;end case;end process;processbeginwait until one_s='1';gg1<=gg1+1;if gg1=9 thengg1<=0;gg2<=gg2+1;if gg2=5 thengg2<=0;ss1<=ss1+1;if ss1=9 thenss1<=0;ss2<=ss2+1;if ss2=5 thenss2<=0;bb1<=bb1+1;if bb1=9 thenbb1<=0;bb2<=bb2+1;end if;if bb1=3 and bb2=2 then bb1<=0;bb2<=0;end if;end if;end if;end if;end if;end process;with gg1 selectg1<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others; with gg2 selectg2<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"0000000" when others; with ss1 selects1<="1111110" when 0,"0110000" when 1,"1111001" when 3,"0110011" when 4,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others; with ss2 selects2<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"0110011" when 4,"1011011" when 5,"0000000" when others; with bb1 selectb1<="1111110" when 0,"0110000" when 1,"1101101" when 2,"1111001" when 3,"1011011" when 5,"1011111" when 6,"1110000" when 7,"1111111" when 8,"1111011" when 9,"0000000" when others; with bb2 selectb2<="1111110" when 0,"0110000" when 1,"1101101" when 2,"0000000" when others; end;PLD单个音符编程低2音library ieee;use ieee.std_logic_1164.all;entity ypyy isport(in50m:in std_logic;a:out std_logic);end;architecture gg of ypyy is signal in1:std_logic;signal count:integer range 0 to 25000000;beginprocessbeginwait until in50m='1';count<=count+1;if count=85034 thencount<=0;in1<=not in1;end if;end process;a<=in1;END;PLD双音符编程library ieee;use ieee.std_logic_1164.all;entity ypyy isport(in50m:in std_logic;a:out std_logic);end;architecture gg of ypyy issignal in1:std_logic;signal in2:std_logic;signal count:integer range 0 to 25000000;signal count_1:integer range 0 to 25000000;signal ys1s:integer range 0 to 50000000;signal jia1:integer range 0 to 1; beginprocessbeginwait until in50m='1';count<=count+1;if count=85034 then count<=0;in1<=not in1;end if;end process;processbeginwait until in50m='1'; count_1<=count_1+1; if count_1=63775 then count_1<=0;in2<=not in2;end if;end process;processbeginwait until in50m='1'; ys1s<=ys1s+1;if ys1s=50000000 then ys1s<=0;jia1<=jia1+1;end if;if jia1=0 thena<=in1;elsea<=in2;end if;end process;end;PLD 1-7音符编程(if语句)library ieee;use ieee.std_logic_1164.all;entity ypyy isport(in50m:in std_logic;a:out std_logic);end;architecture gg of ypyy issignal in1:std_logic;signal in2:std_logic;signal in3:std_logic;signal in4:std_logic;signal in5:std_logic;signal in6:std_logic;signal in7:std_logic;signal count:integer range 0 to 25000000;signal count_1:integer range 0 to 25000000;signal count_2:integer range 0 to 25000000;signal count_3:integer range 0 to 25000000;signal count_4:integer range 0 to 25000000;signal count_5:integer range 0 to 25000000;signal count_6:integer range 0 to 25000000;signal ys1s:integer range 0 to 50000000;signal jia1:integer range 0 to 7; beginprocessbeginwait until in50m='1';count<=count+1;if count=95419 thencount<=0;in1<=not in1;end if;end process;processbeginwait until in50m='1';count_1<=count_1+1;if count_1=85034 thencount_1<=0;in2<=not in2;end if;end process;processbeginwait until in50m='1'; count_2<=count_2+1; if count_2=75757 then count_2<=0;in3<=not in3;end if;end process;processbeginwait until in50m='1'; count_3<=count_3+1; if count_3=71633 then count_3<=0;in4<=not in4;end if;end process;processbeginwait until in50m='1'; count_4<=count_4+1; if count_4=63775 then count_4<=0;in5<=not in5;end if;end process;processbeginwait until in50m='1'; count_5<=count_5+1; if count_5=56818 then count_5<=0;in6<=not in6;end if;end process;processbeginwait until in50m='1';count_6<=count_6+1; if count_6=50607 then count_6<=0;in7<=not in7;end if;end process;processbeginwait until in50m='1'; ys1s<=ys1s+1;if ys1s=50000000 then ys1s<=0;jia1<=jia1+1;end if;if jia1=0 thena<=in1;end if;if jia1=1 thena<=in2;end if;if jia1=2 thena<=in3;end if;if jia1=3 then a<=in4;end if;if jia1=4 then a<=in5;end if;if jia1=5 then a<=in6;end if;if jia1=6 then a<=in7;end if;end process; end;。

简易交通灯控制的PLD设计

蜂呜器

电平开关

EPM240T100C5

单步脉冲开关

实验要求

用指示灯显示,验证计数和交通灯的功能(必做); 增加计数的数码管显示功能;(选做) 增加黄灯的声音提醒功能; (选做)

提示

A1(C2) B1(B2) C1(A2)

用三个JK触发器设计一 个三位二进制同步计数器

Q3 、Q2、 Q1经控制电 路启动红、黄、绿信号灯。

控制电路

Q3 Q2 Q1

计数器

真值表

时钟脉冲 CLK 0 1 2 3 4 5 6 7

计数器状态

Q3

Q2

Q1

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

设置输入端电平

保存后仿真

选择功能仿真

产生功能仿真网 表

开始仿真

仿真成功

仿真结果

下载

硬件设置

设置下载电缆的类型

选定下载项

接通实验板电源,开始下载程序。

实验板

数码管各段连接EPM240 的管脚

数码管共阴已接地

电源开关

指示灯

1KHz脉冲发 生器

扩展 I/O口

接下载电缆 接5V 电源

A1(C Q 3 2Q )1Q 2 B1(BQ 21)Q2

C1( A Q 32 Q )1Q2

Quartus II设计流程

创建工程项目

在硬盘新建一个你自己的文件夹, 把工程项目保存在此文件夹里。

选择器件:EPM240T100C5

完成工程项目创建

创建原理图文件

点击

输入器件操作

10分钟学会PLD设计

10分钟学会PLD设计睿浩电子今天我们将带领大家完成你的第一个PLD设计,即使你从没有接触过PLD,也可以让你可以在十分种之内初步学会PLD设计!不信?呵呵我们慢慢往下看。

实验目的我们分别采用VHDL、Verilog-HDL和原理图输入方式设计一个简单的三人表决器,,并下载到PLD实验板进行实际运行。

三人表决器的功能描述:三个人分别用手指拨动开关SW1、SW2、SW3来表示自己的意愿,如果对某决议同意,各人就把自己的指拨开关拨到高电平(上方),不同意就把自己的指拨开关拨到低电平(下方)。

表决结果用LED(高电平亮)显示,如果决议通过那么实验板上L2(黄灯)亮;如果不通过那么实验板上L1(红灯)亮;如果对某个决议有任意二到三人同意,那么此决议通过,L2亮;如果对某个决议只有一个人或没人同意,那么此决议不通过,L1亮功能虽然简单,但是大家可以从这个实验中学习到PLD的设计输入,仿真,下载等一个完整过程。

软件准备本次实验采用Max+plusII 10.2 软件,首先我们需要下载免费软件并安装license。

对于WindowsNT/2000/XP,还需要安装下载电缆的驱动程序。

>> 软件安装和license的获取请点击此处>> 安装下载电缆的驱动程序请点击此处硬件准备PC机一台,JX002B型实验板,电源,下载电缆软硬件均准备好以后,就可以开始我们的设计了。

在三种输入方式中,你也可以先只看一种,比如原理图方式或者VHDL方式,然后可以直接看2-4章的内容下面您可以继续学习以下内容:10分钟学会PLD设计1 -设计输入 1.1 采用原理图输入10分钟学会PLD设计1 -设计输入 1.2 采用VHDL语言输入10分钟学会PLD设计1 -设计输入 1.3 采用Verilog语言输入10分钟学会PLD设计2 -设计的编译10分钟学会PLD设计3 -设计的仿真10分钟学会PLD设计4 -下载1 设计输入1.1 采用原理图设计三人表决器我们根据三人表决器的直值表,可以通过卡诺图化简可以得到:L2=SW1SW2+SW1SW3+SW2SW3L1=_L2那么我们可以在MAX+plusII中用原理图实现上面的三人表决器下面仅把和VHDL不同的详细写下,相同或基本相同的就一带而过:(1)打开MAX+plusII(2)新建一个图形文件:File菜单>new新建文件时选择Graphic Editor file点OK(3)输入设计文件我们现在在图形文件中输入电路,我们这个电路需要AND2、OR3、NOT三个逻辑门电路和输入输出端,你可以Symbol ->Enter Symbol(或者双击空白处)弹出窗口:在Symbol Name中输入and2,点OK同样可以加入or3、input、output、not对input、output,鼠标左键双击PIN_NAME,那么PIN_NAME被选中,并且变黑,然后输入你要改的名字,如SW1把元件拖动到合适位置,将光标放到元件的引线出,可以发现光标变为十字星,此时摁住左键就可以进行连线。

PLD与数字系统设计实验报告

PLD与数字系统设计实验报告A组实验四:数字密码锁1 实验要求使用Xilinx公司的Spartan3S 400AN开发板上的相关模块,利用ISE开发软件完成数字密码锁的设计,要求实现如下功能:利用实验板上的4×3小键盘,设计4位密码锁,当输入密码正确时,在液晶屏上显示“OK”,否则,显示“ERROR”,在输入过程中,显示输入的数据个数,当有错误的输入时,显示“ERROR”,当全部输入正确时,才显示OK。

2 实验原理2.1 4×3数字键盘数字键盘又叫行列式键盘。

用带IO口的线组成行列结构,按键设置在行列的交点上。

例如用4×3的行列式结构可以构成12个键的键盘。

实验中所用到的数字键盘原理如图1所示。

图1 4×3数字键盘例如设置此模块的列为输入端口,行为输出端口。

那么在按下某一个键时,该键所在的开关接通,由输入端口向输出端口输出一个有效电平,继而触发其他模块。

2.2 LCD液晶显示模块开发板上使用的是无字库的12864LCD显示器,12864LCD显示模块是由128*64个液晶显示点组成的一个128列*64行的阵列。

每个显示点对应一位二进制数,1表示亮,0表示灭(但实验所用开发板上该模块实际是低电平表示亮、高电平表示灭)。

存储这些点阵信息的RAM称为显示数据存储器。

以下是关于显示屏的一些参数:图2 128*64 LCD控制器结构框图图3 128*64时序图图4 指令功能表图5 初始化指令流程要显示某个图形就是将相应的点阵信息写入到相应的存储单元中。

图形的点阵信息可以由自己设计也可借助字模软件,问题的关键就是显示点在液晶屏上的位置(行和列)与其在存储器中的地址之间的关系。

由于多数液晶显示模块的驱动电路是由一片行驱动器和两片列驱动器构成,所以12864液晶屏实际上是由左右两块独立的64*64液晶屏拼接而成,每半屏有一个512*8 bits显示数据RAM。

左右半屏驱动电路及存储器分别由片选信号CS1和CS2选择。

可编程逻辑器件(PLD)的实现_计算机逻辑设计_[共3页]

![可编程逻辑器件(PLD)的实现_计算机逻辑设计_[共3页]](https://img.taocdn.com/s3/m/a4193018a1c7aa00b42acb3b.png)

58

图2.43 CPLD的封装和编程

2.8.5 可编程逻辑器件(PLD)的实现

在PLD的芯片图中,用符号×表示可编程开关,实现这种编程开关有两种方式。

一种是之前介绍的金属合金熔丝来做可编程连接。

每一个水平线和垂直线的交叉点通过一个很小的金属熔丝连接起来。

在编程的时候,电路中所有不需要实现的点熔丝就被熔化掉。

这种编程过程是不可逆转的,因为熔丝被熔化后就断开了。

另一种方式是用可编程晶体管来实现。

首先以PLA为例。

根据之前对门电路负载特性的分析,NMOS或非门可以做到扇入很大。

适用于制作PLA的可编程开关。

图2.44(a)展示了一种可编程的或非阵列。

该或非阵列具有n个输入信号:12

,...n

x x x,k个输出信号:12

,...k

S S S。

在每个水平和垂直交叉点上都存在一个可编程开关。

图2.44 用EEPROM晶体管实现的可编程或非阵列。

PLD可编程数字系统课程设计内容(电信10)

PLD可编程数字系统课程设计内容(电信10)第一篇:PLD可编程数字系统课程设计内容(电信10)PLD可编程数字系统课程设计一、设计题目:基于Verilog HDL的数字秒表和电子时钟设计二、设计目的1、掌握Verilog HDL用于数字逻辑系统的设计技术和方法;2、掌握CPLD/FPGA器件的应用方法;3、学习掌握EDA综合开发环境(如ALTERA公司的Quartus II 等)下进行设计、仿真、综合、下载及调试的方法。

三、设计任务基础部分:1、设计用于体育比赛用的数字秒表功能,要求⑴ 计时精度应大于1/100秒,计时器能显示1/100秒的时间;⑵ 计时器的最长计时时间为1小时,为此需要一个6位的显示器,显示的最长时间为59分59.99秒。

2、设置有复位和启/停开关,要求⑴ 复位开关用来使计时器清零,并做好计时准备;⑵ 启/停开关的使用方法与传统的机械计时器相同,即按一下启/停开关,启动计时器开始计时,再按一下启/停开关,计时中止。

3、采用Verilog HDL语言用层次化设计方法设计符合上述功能要求的数字秒表。

4、在此基础上增加电子时钟功能(1)加入一个模式开关按键,按一下,变为秒表模式,再按一下切换回电子时钟模式。

(2)设计电子时钟,要求能够对当前时间进行设置。

用6个数码管分别显示小时、分钟、秒钟。

(3)同时要求能够设置闹钟时间,到达时间后蜂鸣器会响5秒钟。

加分部分:5、加分任务:利用实验箱资源设计一个系统,加分的分数视系统的新颖性,功能和复杂程度而定。

(新颖性体现在:如果多个人实现相同的系统,那么此系统的加分分数相应降低)四、设计步骤1、采用层次化设计方法将设计项目分为若干模块;2、对各模块分别设计,写出行为描述的Verilog HDL源文件;3、对所作设计进行功能仿真,通过有关波形确认设计是否正确;4、完成全部设计后,通过实验箱下载验证课题设计的正确性。

五、课程设计报告要求1、设计目的、任务;2、设计步骤;3、根据分层方法进行模块设计,写出各模块Verilog HDL源代码;4、记录综合、仿真、调试过程及结果;5、总结所做设计及设计方法;6、自我鉴定(实验报告册封底对应栏)。

PLD详细介绍说明

PLD详细介绍说明PLD,全称为Programmable Logic Device,即可编程逻辑器件,是一种用于实现数字逻辑电路的可编程电子器件。

PLD作为一种集成电路,可以按照用户的需求进行重新编程,实现特定的逻辑功能。

PLD的出现使得电子系统设计和制造变得更加灵活和高效。

PLD的核心部分是逻辑门阵列(Logic Gate Array,LGA)和可编程的连接器(Programmable Interconnect),它们组成了PLD的逻辑单元。

LGA是由大量的逻辑门电路组成的一种具有一定逻辑功能的基本电路单元。

可编程连接器则提供了将逻辑单元连接在一起的能力。

通过对逻辑单元的编程和连接,可以实现各种复杂的数字逻辑功能。

PLD的主要优点有以下几点:1.可编程性:PLD可以通过特定的软件工具进行编程,用户可以根据自己的需求设计出特定的逻辑功能,并将其烧录到PLD芯片中。

这种可编程性使得设计和制造过程更加灵活和高效。

2.高度集成:PLD集成了大量的逻辑门电路,能够实现复杂的数字逻辑功能。

相比于传统的离散器件,PLD的高度集成度和小尺寸使得电路板设计更加简化,减少了系统的体积和功耗。

3.可重编程性:PLD允许用户对其进行多次编程和修改,能够快速响应设计变更和需求变化。

这种可重编程性使得设计迭代更加容易,加快了产品的开发和上市时间。

4.低成本:相比于定制的电路设计和制造过程,PLD的生产和使用成本更低。

这是由于PLD的可编程性能够降低生产成本和库存风险,同时也降低了设计和验证的时间成本。

PLD在实际应用中有广泛的应用领域,包括电子设备、通信设备、工业自动化等。

以下是几个典型应用案例:1.控制器设计:PLD可以用于设计各种类型的控制器,例如逻辑控制器、定时控制器、序列控制器等。

这些控制器能够实现复杂的控制逻辑,满足不同的应用需求。

2.信号处理:PLD可以用于设计数字信号处理电路,例如滤波器、数据压缩器等。

这些电路能够对输入信号进行数字化处理,滤除杂散信号和噪音,提取出感兴趣的信号。

简易交通灯控制的PLD设计PPT课件

C1( A Q 32 •Q )1•Q 2

7

Quartus II设计流程

8

创建工程项目

9

在硬盘新建一个你自己的文件夹, 把工程项目保存在此文件夹里。

10

选择器件:EPM240T100C5

11

完成工程项目创建

12

创建原理图文件

点击

48

感谢聆听

不足之处请大家批评指导

Please Criticize And Guide The Shortcomings

演讲人:XXXXXX 时 间:XX年XX月XX日

49

简易交通灯控制电路的PLD设计

1

设计任务

某交叉路口南北方向有红灯(A1)、黄灯(B1)、绿 灯(C1),东西方向有红灯(A2)、黄灯(B2)、绿 灯(C2)。红灯亮是停车信号,绿灯亮是通车信号, 黄灯亮是右转弯信号。

N

W

E

S

2

交通规则

南北方向红灯亮及东西方向绿灯亮(3S) 南北方向黄灯亮及东西方向黄灯亮(1S) 南北方向绿灯亮及东西方向红灯亮(3S) 南北方向黄灯亮及东西方向黄灯亮(1S)

1

0

1

1

1

南北方向信号灯

A1(红)

B1(黄)

C1(绿)

1

0

0

1

0

0

1

0

0

0

1

0

0

0

1

0

0

1

0

01Biblioteka 010A2(红) 0 0 0 0 1 1 1 0

东西方向信号灯

B2(黄)

C2(绿)

0

pld设计实例

PLD设计实例引言可编程逻辑器件〔PLD〕是一种数字电路设备,可以根据用户的需要来重新配置其逻辑功能。

PLD在数字系统设计中起着重要的作用,能够提高设计效率和可重用性。

本文将介绍一个PLD设计实例,详细说明设计过程和实现步骤。

设计目标在本实例中,我们的设计目标是实现一个4位全加器电路。

全加器是一种常用的组合逻辑电路,用于将两个输入位和一个进位输入位相加,同时产生和位和进位输出位。

设计过程1. 确定输入输出首先,我们需要确定设计的输入和输出。

在这个实例中,我们的输入是两个4位的二进制数和一个进位输入位,输出是一个4位的二进制和结果和一个进位输出位。

2. 确定逻辑方程根据全加器的功能,我们可以确定其逻辑方程。

全加器的和输出位可以通过对两个输入位和进位位进行异或操作得到,进位输出位可以通过对两个输入位和进位位进行与操作得到。

因此,全加器的逻辑方程如下:和输出位 = 输入位1 ⊕ 输入位2 ⊕ 进位输入位进位输出位 = (输入位1 ∧ 输入位2) ∨ (输入位1 ∧ 进位输入位) ∨ (输入位2 ∧ 进位输入位)3. 确定逻辑电路图根据全加器的逻辑方程,我们可以绘制其逻辑电路图。

在这个实例中,我们需要实现4个全加器来组成4位的全加器电路。

每个全加器的输入和输出如下:输入:输入位1、输入位2、进位输入位输出:和输出位、进位输出位将4个全加器依次连接,形成4位的全加器电路。

4. PLD实现利用PLD来实现我们的设计。

PLD可以通过配置其内部的逻辑功能块来实现不同的数字电路设计。

在本实例中,我们可以使用PLD的可编程逻辑阵列〔PLA〕功能块来实现全加器电路。

首先,我们需要将全加器的逻辑方程转换成与、或、非逻辑块的组合。

然后,根据PLD的可编程特性,我们可以将这些逻辑块配置到PLD的PLA功能块中。

5. 配置PLD根据全加器的逻辑电路图,我们可以将对应的逻辑块配置到PLD的PLA功能块中,以实现全加器电路。

配置PLD的具体方法可以参考PLD芯片的技术手册。

pld设计实例

第四章pld设计实例本章中,我们将应用VHDL说话和电路道理图,在Altera公司的MAX+PLUS II软件平台上实现一些PLD设计实例。

实例中所用的芯片是Altera公司可编程逻辑器件EPF10K10LC84-3,并将每一设计成果下载到杭州众和电子技巧开创开创的EDA实验开创体系长进行验证和演示。

4.1数字显示译码器一.设计要求:当每输入一脉冲旌旗灯号时,数码管就显示一随脉冲旌旗灯号递增的十六进制数,从数字1开端直至数字F。

二.设计方法:此电路的设计框图如图4-1a所示。

当低频的脉冲旌旗灯号输入计数器后,七段译码器将计数器的输出译为响应的十六进制数,并由数码管显示出来。

设计时,底层的计数器、译码器模块可由VHDL说话来实现;顶层的设计则可直截了当采取道理图输入法(图4-1b)。

图4-1a 数字显示译码器的设计框图三.源法度榜样和道理图:四位二进制加法计数器cnt4b.vhd的VHDL源法度榜样w h e n"1100"=>l e d7s<="0111001";--显示“C”w h e n"1101"=>l e d7s<="1011110";--显示“D”w h e n"1110"=>l e d7s<="1111001";--显示“E”w h e n"1111"=>l e d7s<="1110001";--显示“F”when others => led7s<= null;end case;end process;end;七段译码器decl.vhd的VHDL源法度榜样图4-1b 数字显示译码器道理图四.实验板设备:本实例采取实验板中的第8种构造。

时钟旌旗灯号CLK1采取CLOCK1中的任何一组,CLK2采取CLOCK2中的1024HZ,按键5作为清零操纵旌旗灯号,按键6作为时钟使能旌旗灯号,译码成果显示在数码管1上。

简易智能密码锁的PLD实现

简易智能密码锁的PLD实现设计并实现一个数字密码锁,密码锁有四位数字密码和一个确认开锁按键,密码输入正确,密码锁打开,密码输入错误进行警示。

1. 设计要求

1、密码设置:通过键盘进行 4 位数字密码设定输入,在数码管上显示所输入数字。

通过密码设置确定键(BTN 键)进行锁定。

2、开锁:在闭锁状态下,可以输入密码开锁,且每输入一位密码,在数码管上显示“-”,提示已输入密码的位数。

输入四位核对密码后,按“开锁”键,若密码正确则系统开锁,若密码错误系统仍然处于闭锁状态,并用蜂鸣器或led 闪烁报警。

3、在开锁状态下,可以通过密码复位键(BTN 键)来清除密码,恢复初始密码“0000”。

闭锁状态下不能清除密码。

4、用点阵显示开锁和闭锁状态。

提高要求:

1、输入密码数字由右向左依次显示,即:每输入一数字显示在最右边的数码管上,同时将先前输入的所有数字向左移动一位。

2、密码锁的密码位数(4~6 位)可调。

3、自拟其它功能。

2. 工作要求

⑴调研、查找并收集资料。

⑵总体设计,画出设计方案总框图。

⑶单元电路设计,画出各单元电路图。

⑷画出设计方案总电路原理图。

⑸用相应软件仿真,给出关键点波形,有条件时下载。

3. 撰写毕业论文要求

⑴课题名称,内容摘要,目录

⑵设计要求

⑶比较和选定设计的系统方案,画出系统框图。

⑷单元电路设计,参数计算和器件选择,画出相关波形。

⑸画出完整电路图并说明电路的工作原理。

⑹实践结果分析,总结方案的优缺点、实用价值。

⑺器件清单,体会,参考文献。

基于PLD的三层电梯的控制设计

基于PLD的三层电梯的控制设计【摘要】电梯作为现代化的产物在咱们的生活当中已必不可少。

随着经济建设的高速进展,我国电梯需求量愈来愈大。

由此,一个更为庞大的电梯市场已经在国内轰然形成。

本设计是基于可编程逻辑器件(PLD)技术中的甚高速集成电路硬件描述语言(VHDL)语言所开发的三层电梯控制程序。

本程序具有VHDL语言设计里最为常常利用的三个模块:实体entity、结构体architecture、进程执行单元process。

通进程序调试及运行仿真,结果表明,本程序能够完成:电梯运行所在楼层指示、电梯运行方向指示、关门延时设置、看门狗报警、超载报警、故障报警等。

本设计对更高层的电梯控制设计具有必然的拓展性。

【关键词】:电梯控制,程序设计,PLD,VHDLABSTRACTThe product as a modern elevator in our lives has been the sustained and rapid development of economic construction, China's increasing demand for a result, a much larger domestic elevator market has formed a bang. This design is based on Programmable Logic Devices (PLD)in a Very High speed of the integrated hardware Describe Language (VHDL)in developing the third floor of the lift of control procedures. this program has vhdl language designed for the best of three modules :entity, architecture, process. Through the program run, debug and simulation results show that the application can finish:the floor, in the direction, the delay, the guard dog the police, and failure the police, etc. this design with higher the control of the design.【KEY WORD】:lift control, programmer, PLD, VHDL目录引言 (2)一、设计的基础依据 (2)(一)EDA技术介绍 (2)(二)VHDL语言介绍 (2)(三)MAX+plusII软件介绍 (3)二、方案论证 (3)(一)基于PLC技术的电梯控制设计方案 (3)(二)基于PLD技术的电梯控制设计方案 (4)(三)方案选择 (4)三、程序设计 (5)(一)算法分析 (5)(二)程序设计 (7)四、程序调试 (14)五、程序仿真 (16)(一)波形输入成立 (16)(二)电梯运行情形仿真 (18)(三)电梯功能仿真 (20)总结 (21)附录一三层电梯控制的源程序 (22)附录二引脚锁定情形 (26)参考文献 (27)引言我国部份地域人口高度密集,人和土地资源欠缺的矛盾日趋激化,这就要求人们合理地利用土地去解决人与土地的矛盾。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第四章PLD设计实例

本章中,我们将应用VHDL语言和电路原理图,在Altera公司的MAX+PLUS II软件平台上实现一些PLD设计实例。

实例中所用的芯片是Altera公司可编程逻辑器件EPF10K10LC84-3,并将每一设计结果下载到杭州众和电子技术开发有限公司开发的EDA 实验开发系统上进行验证和演示。

4.1数字显示译码器

一.设计要求:

当每输入一脉冲信号时,数码管就显示一随脉冲信号递增的十六进制数,从数字1开始直至数字F。

二.设计方法:

此电路的设计框图如图4-1a所示。

当低频的脉冲信号输入计数器后,七段译码器将计数器的输出译为相应的十六进制数,并由数码管显示出来。

设计时,底层的计数器、译码器模块可由VHDL语言来实现;顶层的设计则可直接采用原理图输入法(图4-1b)。

图4-1a 数字显示译码器的设计框图

三.源程序和原理图:

四位二进制加法计数器cnt4b.vhd的VHDL源程序

七段译码器decl.vhd的VHDL源程序

图4-1b 数字显示译码器原理图

四.实验板配置:

本实例采用实验板中的第8种结构。

时钟信号CLK1采用CLOCK1中的任何一组,CLK2采用CLOCK2中的1024HZ,按键5作为清零控制信号,按键6作为时钟使能信号,译码结果显示在数码管1上。

习题:设计一能递增显示各种不同符号的显示器,工作方式同此实例。

4.28位二进制并行加法器

一.设计要求:

当外加时钟信号的上升沿到达时,能实现8位二进制数并行相加,并输出和及进位信号。

二.设计方法:

多位加法器的构成有两种方式:并行和串行。

并行加法器是一种超前进位加法逻辑电路,每位的进位只由加数和被加数决定,而与低位的进位无关,因而运算速度较快;串行加法器则是将全加器级联构成多位加法器,虽然电路比较简单,但运算速度较慢。

并行加法器通常比串行级联加法器占用更多的资源,随着位数的增加,相同位数的并行加法器与串行加法器的容量差快速增大。

因此,在工程中使用加法器时,要在速度和容量之间寻找平衡。

实验结果表明,4位二进制并行加法器和串行级联加法器占用几乎相同的资源。

这样,多位数加法器可以由4位二进制并行加法器串联构成。

本实例中的8位二进制并行加法器即是由2个4位二制并行加法器级联而成的。

4位二制并行加法器由VHDL语言来实现;顶层的8位二进制并行加法器则通过原理图输入法将两个4位二进制加法器级连而成。

4位二进制并行加法器add4b.vhd的VHDL语言源程序

图4-2 8位二进制并行加法器原理图

四.实验板配置:

本实例采用实验板中的第4种结构。

低位的进位信号CIN通过按键输入,输出的进位信号用发光二极管D8来显示;加数A从低到高由按键1、2输入,被加数B从低到高由按键3、4输入,输出的和由数码管7、8显示。

习题:设计一8位二进制减法器。

(提示:根据二进制数相减等于补码相加的道理,将减数的每一位取反,同时将加法器的借位输入cin0置高电平。

注意,此种结构的减法器,其溢出或借位的输出电平是0。

)

4.3模可变8位二进制加法计数器

一.设计要求:

每当外加时钟上升沿到达时,8位计数器即累加一次。

可变模通过2个选择位M1、M0来决定,要求当M1、M0取00、01、10、11四个数值时,分别可构成10进制、16进制、32进制、128进制4种加法计数方式。

二.设计方法:

采用VHDL语言进行设计,通过选择位M1、M0的不同取值来控制进位信号的产生,从而实现不同进制的计数器。

三.源程序:

模可变8位二进制加法计数器cnt8b.vhd的VHDL语言源程序

四.实验板配置:

本实例采用实验板中的第4种结构。

时钟信号CLK采用CLOCK1中的任何一组,清零信号由按键8控制,选择位M的数值由按键1输入,输出结果在数码管7、8上显示。

习题:设计一4位模可变加减计数器。

4.4秒表

一.设计要求:

当外加时钟信号的频率为1HZ,要求秒表能精确到1秒。

二.设计方法:

图4-3a 秒表的设计框图

电路的设计框图如图4-3a所示。

由于秒钟是六十进制的,所以可通过一十进制计数器和一六进制计数器来完成时间的计数。

整个设计采用自上而下的设计方法,底层的计数模块采用VHDL语言来实现,顶层则可直接采用原理图输入法。

十进制加法计数器cnt10.vhd的VHDL语言源程序

六进制加法计数器cnt6.vhd的VHDL语言源程序

图4-3b 秒表的原理图

四.实验板配置:

本实例采用实验板中的第1种结构。

时钟信号CLK采用CLOCK1中的1HZ,清零信号CLR和时钟使能信号CS分别由按键1、2控制,输出结果显示在数码管1、2上。

习题:设计一能精确到秒的60秒定时器。

4.5 六位数字频率计

一.设计要求:

采用直接测频法设计一六位数字频率计,要求测频范围为10-10KHZ,频率计的输出用六只数码发光管显示。

闸门控制信号由外加的8HZ时钟输入信号经分频产生,闸门宽度保持1S不变。

二.设计方法:

测频的方法主要可分为两种:一种为直接测量法,即在一定的闸门时间内测量被测信号的脉冲个数;另一种为间接测量法,如周期测量法、V-F转换法等。

直接测量法适合于高频信号的频率测量,间接测量法更适合于低频信号(频率小于10HZ)的频率测量。