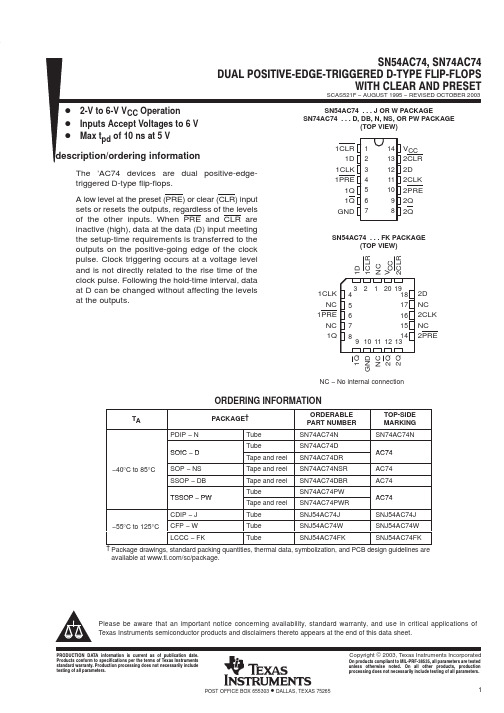

74HC74PW中文资料

74HC74管脚排列中文资料

74HC74管脚排列

74HC74 概述

74HC74是一款高速CMOS器件,74HC74引脚兼容低功耗肖特基TTL (LSTTL)系列。

74HC74遵循JEDEC标准no.7A。

74HC74是双路D 型上升沿触发器,带独立的数据(D)输入、时钟(CP)输入、设置(SD)和复位(RD)输入、以及互补的Q和Q输出。

设置和复位为异步低电平有效,且不依赖于时钟输入。

74HC74数据输入口的信息在时钟脉冲的上升沿传输到Q口。

为了获得预想中的结果,D输入必须在时钟脉冲上升沿来临之前,保持稳定一段就绪时间。

74HC74时钟输入的施密特触发功能使得电路对于缓慢的脉冲上升和下降具备更高的容差性。

74HC74 特性

工作电压范围:2.0~6.0 V

对称输出阻抗

高抗扰

低功耗

ESD保护

HBM EIA/JESD22-A114-A超过2000 V

MM EIA/JESD22-A115-A超过200 V

74HC74 参数

74HC74 基本参数

电压 2.0~6.0V

驱动电流+/-5.2 mA

传输延迟14 ns@5V

74HC74 其他特性

逻辑电平CMOS

功耗考量低功耗或电池供电应用74HC74 封装与引脚

SO14, SSOP14, DIP14, TSSOP14。

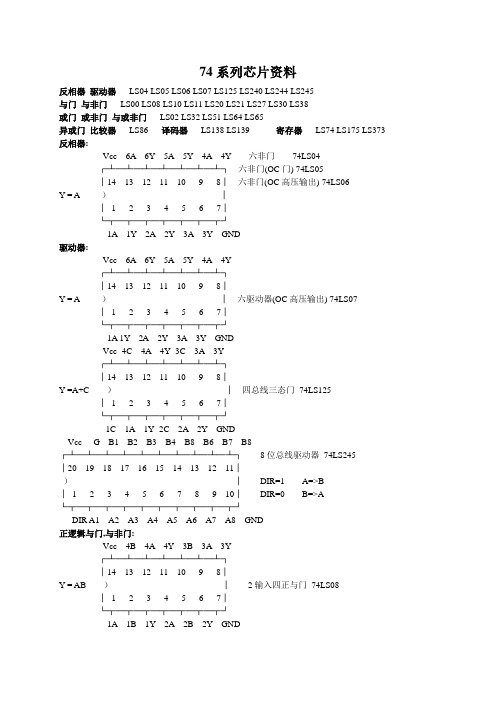

74HC系列芯片资料

7474HC4052 74HC4053 74HC4060 74HC4066 74HC4075 74HC42 74HC423A 74HC4514 74HC4538A 74HC4543 74HC51 74HC521 74HC533 74HC534 74HC540 74HC541 74HC58 74HC589 74HC594 74HC595 74HC597 74HC620 74HC623 74HC640 74HC643 74HC646 74HC648 74HC688 74HC7266 74HC73 74HC74A 74HC75 74HC76 74HC85 74HC86 74HC942 74HC943 74LS00 74LS02 74LS03 74LS04 74LS05 74LS08 74LS09 74LS10 74LS109 74LS11 74LS112 74LS113 74LS114 74LS122 74LS123 74LS125 74LS160 74LS136 74LS138 74LS139 74LS14 74HC147 74HC148 74HC149 74LS151 74LS153 74LS155 74LS156 74LS157 74LS158 74LS160A 74LS161A 74LS162A 74LS163A 74LS164 74LS168 74LS169 74LS173 74LS174 74LS175 74LS190 74LS191 74LS192 74LS193 74LS194A 74LS195A 74LS20 74LS21 74LS240 74LS244 74LS245 74LS253 74LS256 74LS257 74LS258 74LS27 74LS279 74LS28 74LS283 74LS30 74LS32 74LS352 74LS367 74LS368A 74LS373 74LS76 74LS379 74LS38 74LS390 74LS393 74LS42 74LS48 74LS49 74LS51 74LS540 74LS541 74LS74 74LS682 74LS684 74LS75 74LS83A 74LS85 74LS86 74LS90 74LS95B 74LS688 74LS136 74LS651 74LS653 74LS670 74LS73A 74、74HC、74LS系列芯片资料2006-9-22 23:06系列 电平 典型传输延迟ns 最大驱动电流(-Ioh/Lol)mA AHC CMOS 8.5 -8/8AHCT COMS/TTL 8.5 -8/8HC COMS 25 -8/8HCT COMS/TTL 25 -8/8ACT COMS/TTL 10 -24/24F TTL 6.5 -15/64ALS TTL 10 -15/64LS TTL 18 -15/24注:同型号的74系列、74HC系列、74LS系列芯片,逻辑功能上是一样的。

74HC74中文资料_数据手册_参数

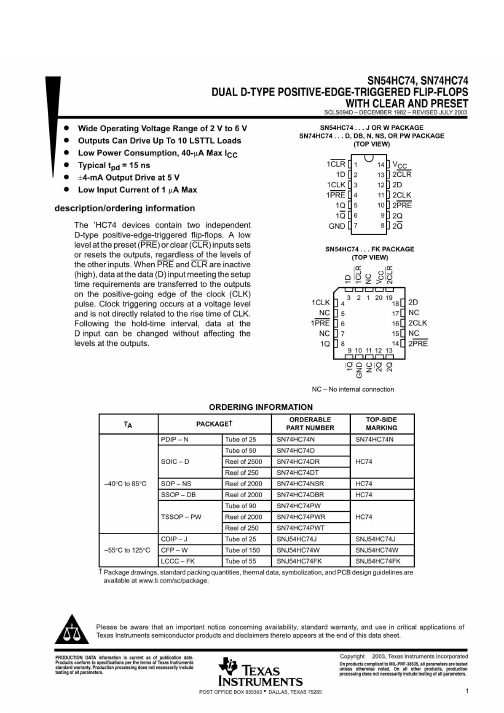

74HC74宽工作电压范围2 V 6 VD输出可以开车10 LSTTL LoadsD低功耗,40-µA马克斯ICCD典型信息= 15 nsD±4-mA输出驱动VD低输入电 流的5点1µA Maxdescription /订购informationThe HC74设备包含两个independentD-type positive-edge-triggered拖鞋。74HC74在预置(PRE)或 清除(CLR)输入设置或重置输出的低电平,而不考虑其他输入的电平。当PRE和CLR处于非活动状态(高)时,满足setuptime要求的数据 (D)输入处的数据被传输到时钟(CLK)脉冲正向边缘的输出端。时钟触发发生在电压水平,与CLK的上升时间没有直接关系。在保持时间 间隔之后,可以在不影响输出电平的情况下更改输入端的数据。订购包图纸,标准包装数量,74HC74热数据,符号,和PCB设计指南超 过“绝对最大额定值”下列出的应力可能对设备造成永久性损坏。这些只是应力等级,设备在这些或任何其他条件下的功能运行,超 出“推荐操作条件”的指示,是不受限制的。长时间暴露在绝对最大额定条件下可能会影响设备的可靠性。如果观察输入和输出电流额 定值,可能会超过输入和输出电压额定值。封装热阻抗按JESD 5计算环保(RoHS &没有某人/ Br): TI定义“绿色”意味着“Pb-Free”,此 外,使用包装材料,不含卤素,包括溴(Br)或锑(某人)总数的0.1%以上产品的重量。(3)实验室,峰值温度。湿度敏感性级别评级根据 JEDECindustry标准分类和soldertemperature峰值。重要信息和免责声明:本页所提供的信息代表德州仪器自提供之日起的知识和信念。TI 的知识和信念基于第三方提供的信息,对于这些信息的准确性不作任何陈述或保证。74HC74目前正在努力更好地整合来自第三方的信 息。TI已采取并将继续采取合理措施,提供具有代表性和准确的信息,但可能未对来料和化学品进行破坏性测试或化学分析。TI和TI供 应商认为某些信息是专有的,因此CAS号码和其他有限的信息可能无法发布。在任何情况下,TI因该等信息而产生的责任都不应超过 TIto客户在本文件中每年销售的TI部件的采购总价

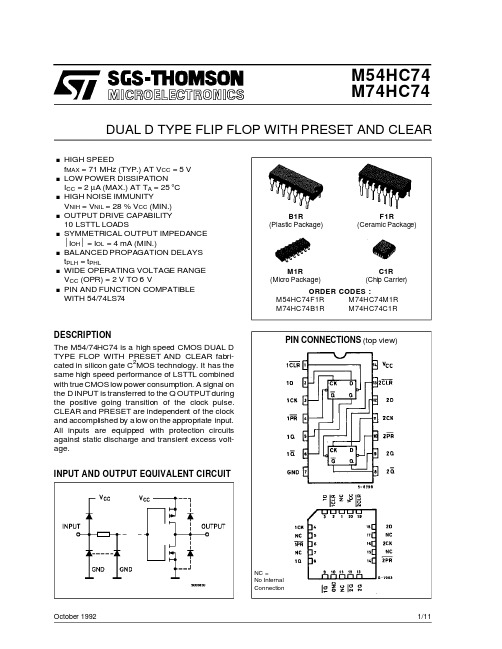

M74HC74B1中文资料

IEC LOGIC SYMBOL

4, 10 5, 9 6, 8 7 14

1PR, 2PR 1Q, 2Q 1Q, 2Q GND V CC

LOGIC DIAGRAM

2/11

元器件交易网

M54/M74HC74

ABSOLUTE MAXIMUM RATINGS

Symbol VCC VI VO IIK IOK IO ICC or IGND PD Tstg TL Supply Voltage DC Input Voltage DC Output Voltage DC Input Diode Current DC Output Diode Current DC Output Source Sink Current Per Output Pin DC VCC or Ground Current Power Dissipation Storage Temperature Lead Temperature (10 sec) Parameter Value -0.5 to +7 -0.5 to VCC + 0.5 -0.5 to VCC + 0.5 ± 20 ± 20 ± 25 ± 50 500 (*) -65 to +150 300 Unit V V V mA mA mA mA mW

VIH

High Level Input Voltage Low Level Input Voltage

V IL

4/11

元器件交易网

M54/M74HC74

AC ELECTRICAL CHARACTERISTICS (C L = 50 pF, Input t r = tf = 6 ns)

o

Value -40 to 85 oC -55 to 125 oC 74HC 54HC Min. Max. Min. Max. 95 19 16 190 38 32 190 38 32 4.2 21 25 110 22 19 110 22 19 110 22 19 0 0 0 35 7 6 10 pF pF ns ns ns ns MHz 110 22 19 225 45 38 225 45 38 ns ns ns Unit

74HCT7404N资料

GENERAL DESCRIPTION

The 74HC/HCT7404 are high-speed Si-gate CMOS devices specified in compliance with JEDEC standard no.7A.

The “7404” is an expandable, First-In First-Out (FIFO) memory organized as 64 words by 5 bits. A guaranteed 15 MHz data-rate makes it ideal for high-speed applications. A higher data-rate can be obtained in applications where the status flags are not used (burst-mode).

Fig.5 Functional diagram.

September 1993

4

Philips Semiconductors

5-Bit x 64-word FIFO register; 3-state

full pagewidth

September 1993

R (1)

R FP

S

Q

DOR

MR

SO

61 x

MGA670

handbook, halfpage

OE 1

DIR 2

SI 3

n.c. 4

D0 5 D1 6 D2 7 D3 8 D4 9 GND 10

20 VCC 19 SO 18 DOR

17 n.c.

7404

16 Q0 15 Q1 14 Q2 13 Q3 12 Q4 11 MR

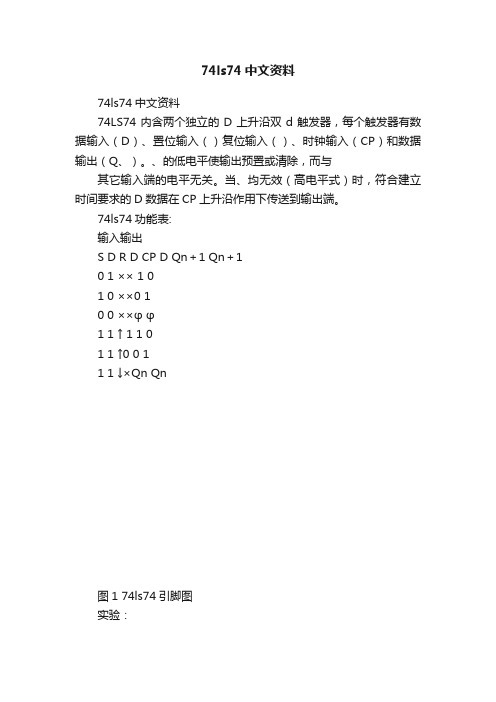

74ls74中文资料

74ls74中文资料74ls74中文资料74LS74内含两个独立的D上升沿双d触发器,每个触发器有数据输入(D)、置位输入()复位输入()、时钟输入(CP)和数据输出(Q、)。

、的低电平使输出预置或清除,而与其它输入端的电平无关。

当、均无效(高电平式)时,符合建立时间要求的D数据在CP上升沿作用下传送到输出端。

74ls74功能表:输入输出S D R D CP D Qn+1 Qn+10 1 ×× 1 01 0 ××0 10 0 ××φ φ1 1 ↑ 1 1 01 1 ↑0 0 11 1 ↓×Qn Qn图1 74ls74引脚图实验:用74LS74构成4位寄存器一个D触发器可实现一位二进数的存储,因此应采用4个D触发器实现4位寄存器。

由于要实现移位寄存,4个D触发器之间应相互联接。

(1)首先在图2中完成相应的联线,构成可实现并入并出、串入串出、并入串出、串入并出的多功能移位寄存。

按图接好电路。

(2) D3 D2 D1 D0分别接逻辑开关,Q3 Q2 Q1 Q0接发光二极管;(3) 先清零;(4) 按下列要求,实现相应功能,观察结果,并描述工作过程。

并入并出:使数据输入端D3D2D1D0=1011,给CP端输入一个正单脉冲,观察Q3Q2Q1Q0发光二极管的状态,、将结果填入表中。

并入串出:使数据输入端D3D2D1D0=1011,给CP端输入4个正单脉冲,观察Q3端发光二极管的状态,将结果填入表6中。

串入并出:使数据输入端D0分别为1011,同时通过给CP端输入正单脉冲将D0端的4 个数据送入寄存器。

观察Q3Q2Q1Q0端发光二极管的状态,将结果填入表中。

串入串出:使数据输入端D0分别为1011,同时通过给CP端输入正单脉冲,将D0端的4 个数据送入寄存器。

在CP端输完8个脉冲后,观察Q3端发光二极管的状态,将结果填入表2中。

并入并出:D3D2D1D0=10111个CP脉冲Q3Q2Q1Q0=结论:并入串出D3D2D1D0=10114个CP脉冲Q3=结论串入并出D3=10114个CP脉冲Q3Q2Q1Q0=结论串入串出D3=10118个CP脉冲Q3=结论图274ls153芯片管脚图引脚逻辑功能以及封装2007年12月17日 23:53 本站原创作者:本站用户评论()关键字:74ls153管脚图逻辑功能图封装:74LS163引脚功能表及管脚定义图(带时序波形图)发布:2011-08-30 | 作者: | 来源: huangjiapeng| 查看:2620次 | 用户关注:定时器由与系统秒脉冲(由时钟脉冲产生器提供)同步的计数器构成,要求计数器在状态信号ST作用下,首先清零,然后在时钟脉冲上升沿作用下,计数器从零开始进行增1计数,向控制器提供模5的定时信号TY和模25的定时信号TL。

74系列中文资料(超级全)

┌┴─┴─┴─┴─┴─┴─┴┐ 双 D 触发器 74LS74

│14 13 12 11 10 9 8 │

)

│

│ 1 2 3 4 5 6 7│

└┬─┬─┬─┬─┬─┬─┬┘

1Cr 1D 1Ck 1St 1Q -1Q GND

Vcc 8Q 8D 7D 7Q 6Q 6D 5D 5Q ALE

┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8 位锁存器 74LS373

Vcc -G B1 B2 B3 B4 B8 B6 B7 B8

┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8 位总线驱动器 74LS245

│20 19 18 17 16 15 14 13 12 11│

)

│ DIR=1 A=>B

│ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A

└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘

___

)

│ Y = A+B

│ 1 2 3 4 5 6 7│

└┬─┬─┬─┬─┬─┬─┬┘

1Y 1A 1B 2Y 2A 2B GND

Vcc 2Y 2B 2A 2D 2E 1F

┌┴─┴─┴─┴─┴─┴─┴┐ 双与或非门 74S51

│14 13 12 11 10 9 8│

_____

)

│ 2Y = AB+DE

DIR A1 A2 A3 A4 A5 A6 A7 A8 GND

正逻辑与门,与非门:

Vcc 4B 4A 4Y 3B 3A 3Y

┌┴─┴─┴─┴─┴─┴─┴┐

│14 13 12 11 10 9 8│

Y = AB )

│ 2 输入四正与门 74LS08

│ 1 2 3 4 5 6 7│

74HC74管脚排列中文资料

74HC74管脚排列

74HC74 概述

74HC74是一款高速CMOS器件,74HC74引脚兼容低功耗肖特基TTL (LSTTL)系列。

74HC74遵循JEDEC标准no.7A。

74HC74是双路D 型上升沿触发器,带独立的数据(D)输入、时钟(CP)输入、设置(SD)和复位(RD)输入、以及互补的Q和Q输出。

设置和复位为异步低电平有效,且不依赖于时钟输入。

74HC74数据输入口的信息在时钟脉冲的上升沿传输到Q口。

为了获得预想中的结果,D输入必须在时钟脉冲上升沿来临之前,保持稳定一段就绪时间。

74HC74时钟输入的施密特触发功能使得电路对于缓慢的脉冲上升和下降具备更高的容差性。

74HC74 特性

工作电压范围:2.0~6.0 V

对称输出阻抗

高抗扰

低功耗

ESD保护

HBM EIA/JESD22-A114-A超过2000 V

MM EIA/JESD22-A115-A超过200 V

74HC74 参数

74HC74 基本参数

电压 2.0~6.0V

驱动电流+/-5.2 mA

传输延迟14 ns@5V

74HC74 其他特性

逻辑电平CMOS

功耗考量低功耗或电池供电应用74HC74 封装与引脚

SO14, SSOP14, DIP14, TSSOP14。

74、74HC、74LS系列芯片资料(注解)

74HC242/243 TRI-STAT TRANSCEIVER三态收发器

74HC244 OCTAL 3-STATE BUFFER八个三态缓冲门

74HC245 OCTAL 3-STATE TRANSCEIVER三态收发器

74HC251 8-CH 3-STATE MUX8路3态多路器

7475 QUAD LATCHES双锁存器

7476 J-K FLIP-FLOPJ-K触发器

7485 4-BIT MAGNITUDE COMPARATOR四位比较器

7486 2-INPUT EXCLUSIVE OR GATES双端异或门

74HC00 QUAD 2-INPUT NAND GATES双输入与非门

7406 HEX INVERTING GATES HV高输出反向器

7408 QUAD 2-INPUT AND GATE与门

7409 QUAD 2-INPUT AND GATES OC与门

7410 TRIPLE 3-INPUT NAND GATES与非门

7411 TRIPLE 3-INPUT AND GATES与门

74HC137 3-TO-8 DECODERS W/LATCHES 3-8线译码器

74HC138 3-8 LINE DECODER3线至8线译码器至4线译码器

74HC14 TRIGGERED HEX INVERTER六触发反向器

74HC147 10-4 LINE PRIORITY ENCODER编码器

74HC193 BINARY UP/DN COUNTER二进制加减计数

74HC194 4BIT BI-DIR SHIFT4位双向移位寄存器

74hc芯片

74hc芯片74hc芯片是一种常见的数字集成电路芯片,其名称中的74表示“批线”,hc表示“高速CMOS”。

它是基于高速串行CMOS技术制造的数字逻辑芯片,具有高速、低功耗、可靠性高等特点,广泛应用于数字电路设计中。

74hc芯片采用的是CMOS技术,即互补金属氧化物半导体技术。

CMOS技术的特点是电路功耗低、抗干扰能力强、集成度高。

通过CMOS技术的应用,74hc芯片在功能上比较丰富,并且具有很高的可靠性,适用于各种数字电路设计需求。

74hc芯片的引脚数目有多种不同的封装,如DIP、SOP、TSSOP等。

常用的有14引脚、16引脚、20引脚等,不同封装的芯片可以满足不同的应用需求。

74hc芯片提供了许多不同的逻辑功能,如与门、或门、非门、异或门等。

这些逻辑门可以根据不同的输入信号给出相应的输出信号,实现各种数字电路的功能。

74hc芯片的工作电压通常为2V至6V之间,具有较高的抗电源噪声能力和抗振荡能力。

其输入电压逻辑高电平范围为2V至6V,逻辑低电平范围为0V至1V。

输出电压逻辑高电平范围为2.4V至6V,逻辑低电平范围为0V至0.4V。

74hc芯片在数字电路设计中应用广泛。

它可以用于逻辑门电路的设计和实现,如与门、或门、非门等。

它也可以用于时序电路的设计和实现,如时钟电路、计数器电路等。

此外,74hc芯片还可以用于存储器电路的设计和实现,如触发器、巨与门等。

总之,74hc芯片是一种基于高速串行CMOS技术制造的数字集成电路芯片,具有高速、低功耗、可靠性高等特点。

它在数字电路设计中有广泛的应用,可以实现各种逻辑、时序和存储器电路的功能。

SN74AVC4T774PW资料

FEATURES12345678161514131211109DIR1DIR2A1A2A3A4DIR3DIR4V CCA V CCB B1B2B3B4GND OEPW PACKAGE (TOP VIEW)D I R 1V C C ADIR2A1A2A3A4DIR3V CCB B1B2B3B4GNDD I R 4O ERGY PACKAGE (TOP VIEW)11689234567151413121110D I R 1D I R 2V C C AV C C BA1A2A3A4B1B2B3B4D I R 3D I R 4G N DO ERSV PACKAGE (TOP VIEW)16151412345678910111213DESCRIPTION/ORDERING INFORMATIONSN74AVC4T7744-BIT DUAL-SUPPLY BUS TRANSCEIVERWITH CONFIGURABLE VOLTAGE TRANSLATION AND 3-STATE OUTPUTSSCES693A–FEBRUARY 2008–REVISED FEBRUARY 2008•Each Channel Has an Independent DIR Control •Latch-Up Performance Exceeds 100mA Per InputJESD 78,Class II•Control Inputs V IH /V IL Levels Are Referenced to •ESD Protection Exceeds the Following Levels V CCA Voltage(tested per JESD 22)•Fully Configurable Dual-Rail Design Allows –8000-V Human-Body Model (A114-A)Each Port to Operate Over the Full 1.2-V to –250-V Machine Model (A115-A)3.6-V Power-Supply Range –1500-V Charged-Device Model (C101)•I/Os Are 4.6-V Tolerant•I off Supports Partial Power-Down-Mode Operation•Typical Data Rates–380Mbps (1.8-V to 3.3-V Translation)–200Mbps (<1.8-V to 3.3-V Translation)–200Mbps (Translate to 2.5V or 1.8V)–150Mbps (Translate to 1.5V)–100Mbps (Translate to 1.2V)This 4-bit noninverting bus transceiver uses two separate configurable power-supply rails.The A port is designed to track V CCA .V CCA accepts any supply voltage from 1.2V to 3.6V.The B port is designed to track V CCB .V CCB accepts any supply voltage from 1.2V to 3.6V.The SN74AVC4T774is optimized to operate with V CCA /V CCB set at 1.4V to 3.6V.It is operational with V CCA /V CCB as low as 1.2V.This allows for universal low-voltage bidirectional translation between any of the 1.2-V,1.5-V,1.8-V,2.5-V,and 3.3-V voltage nodes.ORDERING INFORMATIONT APACKAGE (1)(2)ORDERABLE PART NUMBER TOP-SIDE MARKINGQFN –RGYTape and reel SN74AVC4T774RGYR WT774QFN –RSV Tape and reel SN74AVC4T774ZVK –40°C to 85°CTube SN74AVC4T774PW TSSOP –PWWT774Tape and reelSN74AVC4T774PWR(1)Package drawings,thermal data,and symbolization are available at /packaging .(2)For the most current package and ordering information,see the Package Option Addendum at the end of this document,or see the TI website at .Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.PRODUCTION DATA information is current as of publication date.Copyright ©2008,Texas Instruments IncorporatedProducts conform to specifications per the terms of the Texas Instruments standard warranty.Production processing does not necessarily include testing of all parameters.元器件交易网DESCRIPTION/ORDERING INFORMATION (CONTINUED)SN74AVC4T7744-BIT DUAL-SUPPLY BUS TRANSCEIVERWITH CONFIGURABLE VOLTAGE TRANSLATION AND 3-STATE OUTPUTSSCES693A–FEBRUARY 2008–REVISED FEBRUARY 2008The SN74AVC4T774is designed for asynchronous communication between data buses.The logic levels of the direction-control (DIR)input and the output-enable (OE)input activate either the B-port outputs or the A-port outputs or place both output ports in the high-impedance mode.The device transmits data from the A bus to the B bus when the B outputs are activated,and from the B bus to the A bus when the A outputs are activated.The input circuitry on both A and B ports is always active and must have a logic HIGH or LOW level applied to prevent excess I CC and I CCZ .The SN74AVC4T774is designed so that the control pins (DIR1,DIR2,DIR3,DIR4,and OE)are supplied by V CCA .This device is fully specified for partial-power-down applications using I off .The I off circuitry disables the outputs,preventing damaging current backflow through the device when it is powered down.The V CC isolation feature ensures that if either V CC input is at GND,then both ports are in the high-impedance state.To ensure the high-impedance state during power up or power down,OE should be tied to V CCA through a pullup resistor;the minimum value of the resistor is determined by the current-sinking capability of the driver.Since this device has CMOS inputs,it is very important to not allow them to float.If the inputs are not driven to either a high V CC state,or a low GND state,an undesirable larger than expected I CC current may result.Since the input voltage settlement is governed by many factors (e.g.capacitance,board-layout,package inductance,surrounding conditions,etc.),ensuring that they these inputs are kept out of erroneous switching states and tying them to either a high or a low level minimizes the leakage-current.FUNCTION TABLE(Each Bit)CONTROL INPUTS OUTPUT CIRCUITS OPERATION OE DIR A PORT B PORT L L Enabled Hi-Z B data to A data L H Hi-Z Enabled A data to B dataHXHi-ZHi-ZIsolationLOGIC DIAGRAM (POSITIVE LOGIC)(1)(1)Shown for a single channel2Submit Documentation FeedbackCopyright ©2008,Texas Instruments IncorporatedProduct Folder Link(s):SN74AVC4T774元器件交易网TYPICAL APPLICATIONABSOLUTE MAXIMUM RATINGS (1)SN74AVC4T7744-BIT DUAL-SUPPLY BUS TRANSCEIVERWITH CONFIGURABLE VOLTAGE TRANSLATION AND 3-STATE OUTPUTSSCES693A–FEBRUARY 2008–REVISED FEBRUARY 2008Figure 1.Typical Application of the SN74AVC4T774over operating free-air temperature range (unless otherwise noted)MINMAX UNIT V CCASupply voltage range–0.5 4.6VV CCBI/O ports (A port)–0.5 4.6V IInput voltage range (2)I/O ports (B port)–0.5 4.6V Control inputs–0.5 4.6A port –0.5 4.6Voltage range applied to any output in the high-impedance or V O V power-off state (2)B port –0.5 4.6A port –0.5V CCA +0.5V O Voltage range applied to any output in the high or low state (2)(3)VB port –0.5V CCB +0.5I IK Input clamp current V I <0–50mA I OK Output clamp current V O <0–50mA I OContinuous output current±50mA Continuous current through V CCA ,V CCB ,or GND±100mA T stg Storage temperature range.–65150°C (1)Stresses beyond those listed under "absolute maximum ratings"may cause permanent damage to the device.These are stress ratings only,and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions"is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.(2)The input voltage and output negative-voltage ratings may be exceeded if the input and output current ratings are observed.(3)The output positive-voltage rating may be exceeded up to 4.6V maximum if the output current rating is observed.Copyright ©2008,Texas Instruments Incorporated Submit Documentation Feedback3Product Folder Link(s):SN74AVC4T774元器件交易网PACKAGE THERMAL IMPEDANCERECOMMENDED OPERATING CONDITIONS (1)(2)(3)SN74AVC4T7744-BIT DUAL-SUPPLY BUS TRANSCEIVERWITH CONFIGURABLE VOLTAGE TRANSLATION AND 3-STATE OUTPUTSSCES693A–FEBRUARY 2008–REVISED FEBRUARY 2008UNITPW package (1)108θJAPackage thermal impedanceRGY package (2)39°C/WRSV package (1)184(1)The package thermal impedance is calculated in accordance with JESD 51-7.(2)The package thermal impedance is calculated in accordance with JESD 51-5.V CCIV CCOMIN MAX UNIT V CCA Supply voltage 1.2 3.6V V CCB Supply voltage1.23.6V 1.2V to 1.95VV CCI ×0.65High-level V IHData inputs(4)1.95V to2.7V 1.6Vinput voltage2.7V to3.6V 21.2V to 1.95VV CCI ×0.35Low-level V ILData inputs(4)1.95V to2.7V 0.7Vinput voltage2.7V to3.6V 0.81.2V to 1.95V V CCA ×0.65DIRHigh-level V IH(referenced to V CCA )(5) 1.95V to 2.7V 1.6V input voltage(DIRx,OE)2.7V to3.6V 21.2V to 1.95V V CCA ×0.35DIRLow-level V IL (referenced to V CCA )(5) 1.95V to 2.7V 0.7V input voltage (DIRx,OE)2.7V to3.6V0.8V I Input voltage 03.6V Active state 0V CCO V OOutput voltageV3-state3.61.1V to 1.2V –31.4V to 1.6V–6I OHHigh-level output current 1.65V to 1.95V –8mA 2.3V to 2.7V –93V to 3.6V –121.1V to 1.2V 31.4V to 1.6V6I OLLow-level output current 1.65V to 1.95V 8mA 2.3V to 2.7V 93V to 3.6V12Δt/Δv Input transition rise or fall rate 5ns/V T A Operating free-air temperature–4085°C (1)V CCI is the V CC associated with the input port.(2)V CCO is the V CC associated with the output port.(3)All unused data inputs of the device must be held at V CCI or GND to ensure proper device operation.Refer to the TI application report,Implications of Slow or Floating CMOS Inputs ,literature number SCBA004.(4)For V CCI values not specified in the data sheet,V IH min =V CCI ×0.7V,V IL max =V CCI ×0.3V (5)For V CCA values not specified in the data sheet,V IH min =V CCA ×0.7V,V IL max =V CCA ×0.3V4Submit Documentation FeedbackCopyright ©2008,Texas Instruments IncorporatedProduct Folder Link(s):SN74AVC4T774元器件交易网ELECTRICAL CHARACTERISTICS(1)(2)(3)SN74AVC4T774 4-BIT DUAL-SUPPLY BUS TRANSCEIVERWITH CONFIGURABLE VOLTAGE TRANSLATION AND3-STATE OUTPUTSSCES693A–FEBRUARY2008–REVISED FEBRUARY2008over recommended operating free-air temperature range(unless otherwise noted)T A=25°C–40°C to85°C PARAMETER TEST CONDITIONS V CCA V CCB UNITMIN TYP MAX MIN MAXI OH=–100µA 1.2V to3.6V 1.2V to3.6V V CCO–0.2I OH=–3mA 1.2V 1.2V0.95I OH=–6mA 1.4V 1.4V 1.05V OH V I=V IH VI OH=–8mA 1.65V 1.65V 1.2I OH=–9mA 2.3V 2.3V 1.75I OH=–12mA3V3V 2.3I OL=100µA 1.2V to3.6V 1.2V to3.6V0.2I OL=3mA 1.2V 1.2V0.25I OL=6mA 1.4V 1.4V0.35V OL V I=V IL VI OL=8mA 1.65V 1.65V0.45I OL=9mA 2.3V 2.3V0.55I OL=12mA3V3V0.7ControlI I V I=V CCA or GND 1.2V to3.6V 1.2V to3.6V±0.025±0.25±1µAinputs0V0V to3.6V±0.1±1±5I off A or B port V I or V O=0to3.6VµA0V to3.6V0V±0.1±1±5V O=V CCO or GND,I OZ A or B port 3.6V 3.6V±0.5±2.5±5µAV I=V CCI or GND,OE=V IH1.2V to3.6V 1.2V to3.6V8I CCA V I=V CCI or GND,I O=00V0V to3.6V–2µA0V to3.6V0V81.2V to3.6V 1.2V to3.6V8I CCB V I=V CCI or GND,I O=00V0V to3.6V8µA0V to3.6V0V–2I CCA+I CCB V I=V CCI or GND,I O=0 1.2V to3.6V 1.2V to3.6V16µAControlC i V I=3.3V or GND 3.3V 3.3V 2.53pFinputsC io A or B port V O=3.3V or GND 3.3V 3.3V56pF(1)All unused control inputs of the device must be held at VCC or GND to ensure proper device operation.Refer to the TI applicationreport,Implications of Slow or Floating CMOS Inputs,literature number SCBA004.(2)V CCO is the V CC associated with the output port.(3)V CCI is the V CC associated with the input port.Copyright©2008,Texas Instruments Incorporated Submit Documentation Feedback5Product Folder Link(s):SN74AVC4T774元器件交易网SWITCHING CHARACTERISTICSSWITCHING CHARACTERISTICSSN74AVC4T7744-BIT DUAL-SUPPLY BUS TRANSCEIVERWITH CONFIGURABLE VOLTAGE TRANSLATION AND 3-STATE OUTPUTSSCES693A–FEBRUARY 2008–REVISED FEBRUARY 2008over recommended operating free-air temperature range,V CCA =1.2V (unless otherwise noted)(see Figure 2)V CCB =1.5V V CCB =1.8V V CCB =2.5V V CCB =3.3V V CCB =1.2VFROM TO ±0.1V±0.15V±0.2V±0.3VPARAMETERUNIT(INPUT)(OUTPUT)TYP TYP TYP TYP TYP t PLH 3.5 2.8 2.7 2.7 3.1A B ns t PHL 3.5 2.8 2.7 2.7 3.1t PLH 3.8 3.4 3.23 2.9B A ns t PHL 3.8 3.4 3.23 2.9t PZH 6 4.8 4.4 5.39.3OE A ns t PZL 6 4.8 4.4 5.39.3t PZH 6.7 6.7 6.6 6.7 6.6OE B ns t PZL 6.7 6.7 6.6 6.7 6.6t PHZ 4.3 3.6 3.7 3.34OE A ns t PLZ 4.3 3.6 3.7 3.34t PHZ 4.4 4.4 4.4 4.4 4.4OEBns t PLZ4.44.44.44.44.4over recommended operating free-air temperature range,V CCA =1.5V ±0.1V (see Figure 2)V CCB =1.5V V CCB =1.8V V CCB =2.5V V CCB =3.3V V CCB =1.2VFROM TO ±0.1V ±0.15V ±0.2V ±0.3V PARAMETERUNIT(INPUT)(OUTPUT)TYP MIN MAX MIN MAX MIN MAX MIN MAX t PLH 3.10.3 4.40.2 3.90.1 3.60.1 3.9A B ns t PHL 3.10.3 4.40.2 3.90.1 3.60.1 3.9t PLH 2.90.6 5.10.4 4.90.2 4.60.1 4.5B A ns t PHL 2.90.6 5.10.4 4.90.2 4.60.1 4.5t PZH 5.3 1.17.10.9 6.20.7 5.50.1 6.4OE A ns t PZL 5.3 1.17.10.9 6.20.7 5.50.1 6.4t PZH 4.4 1.18.2 1.18.2 1.18.2 1.18.2OE B ns t PZL 4.4 1.18.2 1.18.2 1.18.2 1.18.2t PHZ 3.6 1.2 4.80.8 5.40.4 5.11 5.4OE A ns t PLZ 3.6 1.2 4.80.8 5.40.4 5.11 5.4t PHZ 3.10.3 5.60.2 5.70.3 5.60.356OEBns t PLZ3.10.35.60.25.70.35.60.35.66Submit Documentation FeedbackCopyright ©2008,Texas Instruments IncorporatedProduct Folder Link(s):SN74AVC4T774元器件交易网SWITCHING CHARACTERISTICS SWITCHING CHARACTERISTICSSN74AVC4T774 4-BIT DUAL-SUPPLY BUS TRANSCEIVERWITH CONFIGURABLE VOLTAGE TRANSLATION AND3-STATE OUTPUTSSCES693A–FEBRUARY2008–REVISED FEBRUARY2008over recommended operating free-air temperature range,V CCA=1.8V±0.15V(see Figure2)V CCB=1.5V V CCB=1.8V V CCB=2.5V V CCB=3.3VV CCB=1.2VFROM TO±0.1V±0.15V±0.2V±0.3V PARAMETER UNIT (INPUT)(OUTPUT)TYP MIN MAX MIN MAX MIN MAX MIN MAX t PLH 2.80.1 4.10.1 3.60.1 3.10.1 3.3A B nst PHL 2.80.1 4.10.1 3.60.1 3.10.1 3.3t PLH 2.60.4 4.30.1 4.10.1 3.80.1 3.7B A nst PHL 2.60.4 4.30.1 4.10.1 3.80.1 3.7t PZH50.8 6.70.6 5.80.4 4.80.3 4.6OE A ns t PZL50.8 6.70.6 5.80.4 4.80.3 4.6t PZH 3.30.2 6.70.2 6.60.2 6.70.2 6.7OE B ns t PZL 3.30.2 6.70.2 6.60.2 6.70.2 6.7t PHZ 3.40.7 4.70.3 5.10.1 4.50.85OE A ns t PLZ 3.40.7 4.70.3 5.10.1 4.50.85t PHZ 2.90.1 5.70.1 5.80.1 5.80.1 5.8OE B ns t PLZ 2.90.1 5.70.1 5.80.1 5.80.1 5.8over recommended operating free-air temperature range,V CCA=2.5V±0.2V(see Figure2)V CCB=1.5V V CCB=1.8V V CCB=2.5V V CCB=3.3VV CCB=1.2VFROM TO±0.1V±0.15V±0.2V±0.3V PARAMETER UNIT (INPUT)(OUTPUT)TYP MIN MAX MIN MAX MIN MAX MIN MAXt PLH 2.60.1 3.80.1 3.20.1 2.70.1 2.6A B nst PHL 2.60.1 3.80.1 3.20.1 2.70.1 2.6t PLH 2.50.5 3.40.2 3.10.1 2.80.1 2.6B A nst PHL 2.50.5 3.40.2 3.10.1 2.80.1 2.6t PZH 4.70.7 6.20.5 5.20.3 4.10.3 3.6OE A ns t PZL 4.70.7 6.20.5 5.20.3 4.10.3 3.6t PZH 2.30.4 4.50.4 4.50.4 4.50.4 4.5OE B ns t PZL 2.30.4 4.50.4 4.50.4 4.50.4 4.5t PHZ30.2 4.30.1 4.90.140.7 4.3OE A ns t PLZ30.2 4.30.1 4.90.140.7 4.3t PHZ 1.901 4.70.1 4.60.1 4.70.1 4.7OE B ns t PLZ 1.901 4.70.1 4.60.1 4.70.1 4.7Copyright©2008,Texas Instruments Incorporated Submit Documentation Feedback7Product Folder Link(s):SN74AVC4T774元器件交易网SWITCHING CHARACTERISTICSOPERATING CHARACTERISTICSSN74AVC4T7744-BIT DUAL-SUPPLY BUS TRANSCEIVERWITH CONFIGURABLE VOLTAGE TRANSLATION AND 3-STATE OUTPUTSSCES693A–FEBRUARY 2008–REVISED FEBRUARY 2008over recommended operating free-air temperature range,V CCA =3.3V ±0.3V (see Figure 2)V CCB =1.5V V CCB =1.8V V CCB =2.5V V CCB =3.3V V CCB =1.2VFROM TO ±0.1V ±0.15V ±0.2V ±0.3V PARAMETERUNIT(INPUT)(OUTPUT)TYP MIN MAX MIN MAXMIN MAX MIN MAX t PLH 2.50.1 3.60.130.1 2.60.1 2.4A B ns t PHL 2.50.1 3.60.130.1 2.60.1 2.4t PLH 2.60.5 3.40.2 2.90.1 2.50.1 2.3B A ns t PHL 2.60.5 3.40.2 2.90.1 2.50.1 2.3t PZH 4.50.9 5.90.550.3 3.80.3 3.3OE A ns t PZL 3.80.9 5.90.550.3 3.80.3 3.3t PZH 1.90.4 3.60.4 3.60.4 3.60.4 3.6OE B ns t PZL 1.90.4 3.60.4 3.60.4 3.60.4 3.6t PHZ 2.70.1 4.20.1 4.60.3 3.80.7 3.9OE A ns t PLZ 2.70.1 4.20.1 4.60.3 3.80.7 3.9t PHZ 2.30.1 4.50.1 4.50.1 4.60.1 4.6OEBns t PLZ2.30.14.50.14.50.14.60.14.6T A =25°CV CCA =V CCA =V CCA =V CCA =V CCA =TEST V CCB =1.2VV CCB =1.5VV CCB =1.8VV CCB =2.5VV CCB =3.3VPARAMETERUNITCONDITIONSTYP TYP TYP TYP TYP Outputs 33334enabled A to BOutputs 11122C L =0,disabled C pdA(1)f =10MHz,pFOutputs t r =t f =1ns 1213141517enabled B to AOutputs 22222disabled Outputs 1213141617enabled A to BOutputs 22222C L =0,disabled C pdB(1)f =10MHz,pFOutputs t r =t f =1ns 33334enabled B to AOutputs 11122disabled(1)Power dissipation capacitance per transceiver8Submit Documentation FeedbackCopyright ©2008,Texas Instruments IncorporatedProduct Folder Link(s):SN74AVC4T774元器件交易网PARAMETER MEASUREMENT INFORMATIONV OH V OLLOAD CIRCUIT × V CCOOpenOutput Control (low-level enabling)Output Waveform 1S1 at 2 × V CCO (see Note B)Output Waveform 2S1 at GND (see Note B)0 V0 VV CCI0 VV CCAV CCOVOLTAGE WAVEFORMS PROPAGATION DELAY TIMESVOLTAGE WAVEFORMS PULSE DURATIONVOLTAGE WAVEFORMS ENABLE AND DISABLE TIMESInputt pd t PLZ /t PZL t PHZ /t PZHOpen 2 × V CCO GNDTEST S1NOTES: A.C L includes probe and jig capacitance.B.Waveform 1 is for an output with internal conditions such that the output is low, except when disabled by the output control.Waveform 2 is for an output with internal conditions such that the output is high, except when disabled by the output control.C.All input pulses are supplied by generators having the following characteristics: PRR v 10 MHz, Z O = 50 Ω, dv/dt ≥ 1 V/ns.D.The outputs are measured one at a time, with one transition per measurement.E.t PLZ and t PHZ are the same as t dis .F.t PZL and t PZH are the same as t en .G.t PLH and t PHL are the same as t pd .H.V CCI is the V CC associated with the input port.I.V CCO is the V CC associated with the output port.1.2 V 1.5 V ± 0.1 V 1.8 V ± 0.15 V2.5 V ± 0.2 V3.3 V ± 0.3 V2 k Ω2 k Ω2 k Ω2 k Ω2 k ΩV CCO R L 0.1 V 0.1 V 0.15 V 0.15 V 0.3 VV TP C L 15 pF 15 pF 15 pF 15 pF 15 pFSN74AVC4T7744-BIT DUAL-SUPPLY BUS TRANSCEIVERWITH CONFIGURABLE VOLTAGE TRANSLATION AND 3-STATE OUTPUTSSCES693A–FEBRUARY 2008–REVISED FEBRUARY 2008Figure 2.Load and Circuit and Voltage WaveformsCopyright ©2008,Texas Instruments Incorporated Submit Documentation Feedback9Product Folder Link(s):SN74AVC4T774元器件交易网PACKAGING INFORMATIONOrderable Device Status (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball Finish MSL Peak Temp (3)SN74AVC4T774PW ACTIVE TSSOP PW 1690Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AVC4T774PWG4ACTIVE TSSOP PW 1690Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AVC4T774PWR ACTIVE TSSOP PW 162000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AVC4T774PWRG4ACTIVE TSSOP PW 162000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AVC4T774RGYR PREVIEW QFN RGY 161000TBD Call TI Call TI SN74AVC4T774RSVRPREVIEWQFNRSV163000TBDCall TICall TI(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -The planned eco-friendly classification:Pb-Free (RoHS),Pb-Free (RoHS Exempt),or Green (RoHS &no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt):This component has a RoHS exemption for either 1)lead-based flip-chip solder bumps used between the die and package,or 2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free (RoHS compatible)as defined above.Green (RoHS &no Sb/Br):TI defines "Green"to mean Pb-Free (RoHS compatible),and free of Bromine (Br)and Antimony (Sb)based flame retardants (Br or Sb do not exceed 0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Levelrating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.PACKAGE OPTION ADDENDUM14-Mar-2008Addendum-Page 1元器件交易网TAPE AND REEL INFORMATION*All dimensions are nominalDevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant SN74AVC4T774PWR TSSOP PW 162000330.012.47.0 5.6 1.68.012.0Q1SN74AVC4T774RGYRQFNRGY161000180.012.43.84.31.58.012.0Q1*All dimensions are nominalDevice Package Type Package Drawing Pins SPQ Length(mm)Width(mm)Height(mm) SN74AVC4T774PWR TSSOP PW162000346.0346.029.0 SN74AVC4T774RGYR QFN RGY161000190.5212.731.8IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers AudioData Converters AutomotiveDSP BroadbandClocks and Timers Digital ControlInterface MedicalLogic MilitaryPower Mgmt Optical NetworkingMicrocontrollers SecurityRFID TelephonyRF/IF and ZigBee®Solutions Video&ImagingWirelessMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2008,Texas Instruments Incorporated。

74HC174中文资料

74HC/HCT174 Hex D-type flip-flop with reset; positive-edge trigger

Product specification Supersedes data of September 1993 File under Integrated Circuits, IC06

DC CHARACTERISTICS FOR 74HC

For the DC characteristics see “74HC/HCT/HCU/HCMOS Logic Family Specifications”.

Output capability: standard ICC category: MSI

AC CHARACTERISTICS FOR 74HC GND = 0 V; tr = tf = 6 ns; CL = 50 pF

Tamb (°C)

TEST CONDITIONS

SYMBOL PARAMETER

74HC

+25

−40 to +85

−40 to +125

UNIT

VCC (V)

WAVEFORMS

Note

1. H = HIGH voltage level h = HIGH voltage level one set-up time prior to the LOW-to-HIGH CP transition L = LOW voltage level I = LOW voltage level one set-up time prior to the LOW-to-HIGH CP transition X = don’t care ↑= LOW-to-HIGH CP transition

HC74资料

fmax

Maximum Clock Frequency (50% Duty Cycle) (Figures 1 and 4) Maximum Propagation Delay, Clock to Q or Q (Figures 1 and 4) Maximum Propagation Delay, Set or Reset to Q or Q (Figures 2 and 4) Maximum Output Transition Time, Any Output (Figures 1 and 4) Maximum Input Capacitance Power Dissipation Capacitance (Per Flip-Flop)

元器件交易网

SL74HC74

Dual D Flip-Flop with Set and Reset

High-Performance Silicon-Gate CMOS

The SL74HC74 is identical in pinout to the LS/ALS74. The device inputs are compatible with standard CMOS outputs; with pullup resistors, they are compatible with LS/ALSTTL outputs. This device consists of two D flip-flops with individual Set, Reset, and Clock inputs. Information at a D-input is transferred to the corresponding Q output on the next positive going edge of the clock input. Both Q and Q outputs are available from each flip-flop. The Set and Reset inputs are asynchronous. • Outputs Directly Interface to CMOS, NMOS, and TTL • Operating Voltage Range: 2.0 to 6.0 V • Low Input Current: 1.0 µA • High Noise Immunity Characteristic of CMOS Devices

74HC00中文资料(真值表-引脚图-电气参数及应用电路)

VCC = 6.0V

0 to 400

ns

DC SPECIFICATIONS直流电气规格

SYMBOL符号

Parameter参数

Test Condition测试条件

Value数值

Unit单位

VCC

-

TA=25℃

-40to85℃

-55to125℃

(V)

最小

典型

最大

最小

最大

最小

最大

VIH

High Level Input-

-

8

15

-

19

-

22

6.0

-

7

13

-

16

-

19

tPLH tPHL

Propagation Delay Time传递延迟时间

2.0

-

-

27

75

-

95

-

110

ns

4.5

-

9

15

-

19

-

22

6.0

-

8

13

-

16

-

19

图2 74HC00传播延迟时间波形

图3 74HC00外形图

图4 74HC00输入输出等效电路

SYMBOL符号

Parameter参数

Value数值

Unit单位

VCC

Supply Voltage电源电压

-0.5 to +7

V

VI

DC Input Voltage直流输入电压

-0.5 to VCC + 0.5

V

VO

DC Output Voltage直流输出电压

74HC00中文资料

单位

ns ns

参数

tPLH输出由低到高传输延迟时间 tPHL输出由高到低传输延迟时间

测试条件

Vcc =5V,CL=50Pf(‘H00 为 25Pf) RL=400Ω(‘H00 和‘S00 为 260Ω,

‘LS00 为 2KΩ

‘00 最大

22

15

‘H00 最大

10

10

‘S00 最大 4.5

5

‘LS00 最大 15

15

54S00/74S00

54LS00/74LS00

单

最小 额定 最大 最小 额定 最大 最小 额定 最大 最小 额定 最大 位

电 源 电 压 54 4.5

5

5.5 4.5

5

5.5 4.5

5

Vcc

74 4.75 5 5.25 4.75 5 5.25 4.75 5

5.5 4.5 5.25 4.75

5 5

5.5 5.25

Vcc=最大

VI=5.5V VI=7V

1

IIH输入高电平电流 Vcc=最大

VIH=2.4V VIH=2.7V

40

IIL输入低电平电流 Vcc=最大

VIL=0.4V VIL=0.5V

-1.6

IOS输出短路电流

Vcc=最大

54 -20 -55 74 -18 -55

ICCH输出高电平时电源电流

Vcc=最大

海纳电子资讯网:www.fpga-arm.com 为您提供各种IC中文资料

54XXX …………………………………. -55~125℃ 74XXX …………………………………. 0~70℃ 存储温度 ………………………………………….-65~150℃ 功能表

74系列功能大全(中文)

74系列功能大全(中文)74、74HC、74LS系列芯片资料,从网上下的,集合了一下系列电平典型传输延迟ns 最大驱动电流(-Ioh/Lol)mAAHC CMOS 8.5 -8/8AHCT COMS/TTL 8.5 -8/8HC COMS 25 -8/8HCT COMS/TTL 25 -8/8ACT COMS/TTL 10 -24/24F TTL 6.5 -15/64ALS TTL 10 -15/64LS TTL 18 -15/24注:同型号的74系列、74HC系列、74LS系列芯片,逻辑功能上是一样的。

74LSxx的使用说明如果找不到的话,可参阅74xx或74HCxx的使用说明。

有些资料里包含了几种芯片,如74HC161资料里包含了74HC160、74HC161、74HC162、74HC163四种芯片的资料。

找不到某种芯片的资料时,可试着查看一下临近型号的芯片资料。

7400 QUAD 2-INPUT NAND GATES 与非门7401 QUAD 2-INPUT NAND GATES OC 与非门7402 QUAD 2-INPUT NOR GATES 或非门7403 QUAD 2-INPUT NAND GATES 与非门7404 HEX INVERTING GATES 反向器7406 HEX INVERTING GATES HV 高输出反向器7408 QUAD 2-INPUT AND GATE 与门7409 QUAD 2-INPUT AND GATES OC 与门7410 TRIPLE 3-INPUT NAND GATES 与非门7411 TRIPLE 3-INPUT AND GATES 与门74121 ONE-SHOT WITH CLEAR 单稳态74132 SCHMITT TRIGGER NAND GATES 触发器与非门7414 SCHMITT TRIGGER INVERTERS 触发器反向器74153 4-LINE TO 1 LINE SELECTOR 四选一74155 2-LINE TO 4-LINE DECODER 译码器74180 PARITY GENERATOR/CHECKER 奇偶发生检验74191 4-BIT BINARY COUNTER UP/DOWN 计数器7420 DUAL 4-INPUT NAND GATES 双四输入与非门7426 QUAD 2-INPUT NAND GATES 与非门7427 TRIPLE 3-INPUT NOR GATES 三输入或非门7430 8-INPUT NAND GATES 八输入端与非门7432 QUAD 2-INPUT OR GATES 二输入或门7438 2-INPUT NAND GATE BUFFER 与非门缓冲器7445 BCD-DECIMAL DECODER/DRIVER BCD译码驱动器7474 D-TYPE FLIP-FLOP D型触发器7475 QUAD LATCHES 双锁存器7476 J-K FLIP-FLOP J-K触发器7485 4-BIT MAGNITUDE COMPARATOR 四位比较器7486 2-INPUT EXCLUSIVE OR GATES 双端异或门74HC00 QUAD 2-INPUT NAND GATES 双输入与非门74HC02 QUAD 2-INPUT NOR GATES 双输入或非门74HC03 2-INPUT OPEN-DRAIN NAND GATES 与非门74HC04 HEX INVERTERS 六路反向器74HC05 HEX INVERTERS OPEN DRAIN 六路反向器74HC08 2-INPUT AND GATES 双输入与门74HC107 J-K FLIP-FLOP WITH CLEAR J-K触发器74HC109A J-K FLIP-FLOP W/PRESET J-K触发器74HC11 TRIPLE 3-INPUT AND GATES 三输入与门74HC112 DUAL J-K FLIP-FLOP 双J-K触发器74HC113 DUAL J-K FLIP-FLOP PRESET 双JK触发器74HC123A RETRIGGERABLE MONOSTAB 可重触发单稳74HC125 TRI-STATE QUAD BUFFERS 四个三态门74HC126 TRI-STATE QUAD BUFFERS 六三态门74HC132 2-INPUT TRIGGER NAND 施密特触发与非门74HC133 13-INPUT NAND GATES 十三输入与非门74HC137 3-TO-8 DECODERS W/LATCHES 3-8线译码器74HC138 3-8 LINE DECODER 3线至8线译码器74HC139 2-4 LINE DECODER 2线至4线译码器74HC14 TRIGGERED HEX INVERTER 六触发反向器74HC147 10-4 LINE PRIORITY ENCODER 10-4编码器74HC148 8-3 LINE PRIORITY ENCODER 8-3编码器74HC149 8-8 LINE PRIORITY ENCODER 8-8编码器74HC151 8-CHANNEL DIGITAL MUX 8通道多路器74HC153 DUAL 4-INPUT MUX 双四输入多路器74HC154 4-16 LINE DECODER 4线至16线译码器74HC155 2-4 LINE DECODER 2线至4线译码器74HC157 QUAD 2-INPUT MUX 四个双端多路器74HC161 BINARY COUNTER 二进制计数器74HC163 DECADE COUNTERS 十进制计数器74HC164 SERIAL-PARALLEL SHIFT REG 串入并出74HC165 PARALLEL-SERIAL SHIFT REG 并入串出74HC166 SERIAL-PARALLEL SHIFT REG 串入并出74HC173 TRI-STATE D FLIP-FLOP 三态D触发器74HC174 HEX D FLIP-FLOP W/CLEAR 六D触发器74HC175 HEX D FLIP-FLOP W/CLEAR 六D触发器74HC181 ARITHMETIC LOGIC UNIT 算术逻辑单元74HC182 LOOK AHEAD CARRYGENERATR 进位发生器74HC190 BINARY UP/DN COUNTER 二进制加减计数器74HC191 DECADE UP/DN COUNTER 十进制加减计数器74HC192 DECADE UP/DN COUNTER 十进制加减计数器74HC193 BINARY UP/DN COUNTER 二进制加减计数器74HC194 4BIT BI-DIR SHIFT 4位双向移位寄存器74HC195 4BIT PARALLEL SHIFT 4位并行移位寄存器74HC20 QUAD 4-INPUT NAND GATE 四个四入与非门74HC221A NON-RETRIG MONOSTAB 不可重触发单稳74HC237 3-8 LINE DECODER 地址锁3线至8线译码器74HC242/243 TRI-STAT TRANSCEIVER 三态收发器74HC244 OCTAL 3-STATE BUFFER 八个三态缓冲门74HC245 OCTAL 3-STATE TRANSCEIVER 三态收发器74HC251 8-CH 3-STATE MUX 8路3态多路器74HC253 DUAL 4-CH 3-STATE MUX 4路3态多路器74HC257 QUAD 2-CH 3-STATE MUX 4路3态多路器74HC258 2-CH 3-STATE MUX 2路3态多路器74HC259 3-8 LINE DECODER 8位地址锁存译码器74HC266A 2-INPUT EXCLUSIVE NOR GATE 异或非74HC27 TRIPLE 3-INPUT NOR GATE三个3输入或非门74HC273 OCTAL D FLIP-FLOP CLEAR 8路D触发器74HC280 9BIT ODD/EVEN GENERATOR 奇偶发生器74HC283 4BIT BINARY ADDER CARRY 四位加法器74HC299 3-STATE UNIVERSAL SHIFT 三态移位寄存74HC30 8-INPUT NAND GATE 8输入端与非门74HC32 QUAD 2-INPUT OR GATE 四个双端或门74HC34 NON-INVERTER 非反向器74HC354 8-CH 3-STATE MUX 8路3态多路器74HC356 8-CH 3-STATE MUX 8路3态多路器74HC365 HEX 3-STATE BUFFER 六个三态缓冲门74HC366 3-STATE BUFFER INVERTER 缓冲反向器74HC367 3-STATE BUFFER INVERTER 缓冲反向器74HC368 3-STATE BUFFER INVERTER 缓冲反向器74HC373 3-STATE OCTAL D LATCHES 三态D型锁存器74HC374 3-STATE OCTAL D FLIPFLOP 三态D触发器74HC393 4-BIT BINARY COUNTER 4位二进制计数器74HC4016 QUAD ANALOG SWITCH 四路模拟量开关74HC4020 14-Stage Binary Counter 14输出计数器74HC4017 Decade Counter/Divider with 10 Decoded Outputs 十进制计数器带10个译码输出端74HC4040 12 Stage Binary Counter 12出计数器74HC4046 PHASE LOCK LOOP 相位监测输出器74HC4049 LEVEL DOWN CONVERTER 电平变低器74HC4050 LEVEL DOWN CONVERTER 电平变低器74HC4051 8-CH ANALOG MUX 8通道多路器74HC4052 4-CH ANALOG MUX 4通道多路器74HC4053 2-CH ANALOG MUX 2通道多路器74HC4060 14-STAGE BINARY COUNTER 14阶BIN计数74HC4066 QUAD ANALOG MUX 四通道多路器74HC4075 TRIPLE 3-INPUT OR GATE 3输入或门74HC42 BCD TO DECIMAL BCD转十进制译码器74HC423A RETRIGGERABLE MONOSTAB 可重触发单稳74HC4511 BCD-7 SEG DRIVER/DECODER 7段译码器74HC4514 4-16 LINE DECODER 4至16线译码器74HC4538A RETRIGGERAB MONOSTAB 可重触发单稳74HC4543 LCD BCD-7 SEG LCD用的BCD-7段译码驱动74HC51 AND OR GATE INVERTER 与或非门74HC521 8BIT MAGNITUDE COMPARATOR 判决定路74HC533 3-STATE D LATCH 三态D锁存器74HC534 3-STATE D FLIP-FLOP 三态D型触发器74HC540 3-STATE BUFFER 三态缓冲器74HC541 3-STATE BUFFER INVERTER三态缓冲反向器74HC58 DUAL AND OR GATE 与或门74HC589 3STATE 8BIT SHIFT 8位移位寄存三态输出74HC594 8BIT SHIFT REG 8位移位寄存器74HC595 8BIT SHIFT REG 8位移位寄存器出锁存74HC597 8BIT SHIFT REG 8位移位寄存器入锁存74HC620 3-STATE TRANSCEIVER 反向3态收发器74HC623 3-STATE TRANSCEIVER 八路三态收发器74HC640 3-STATE TRANSCEIVER 反向3态收发器74HC643 3-STATE TRANSCEIVER 八路三态收发器74HC646 NON-INVERT BUS TRANSCEIVER 总线收发器74HC648 INVERT BUS TRANCIVER 反向总线收发器74HC688 8BIT MAGNITUDE COMPARATOR 8位判决电路74HC7266 2-INPUT EXCLUSIVE NOR GATE 异或非门74HC73 DUAL J-K FLIP-FLOP W/CLEAR 双JK触发器74HC74A PRESET/CLEAR D FLIP-FLOP 双D触发器74HC75 4BIT BISTABLE LATCH 4位双稳锁存器74HC76 PRESET/CLEAR JK FLIP-FLOP 双JK触发器74HC85 4BIT MAGNITUDE COMPARATOR 4位判决电路74HC86 2INPUT EXCLUSIVE OR GATE 2输入异或门74HC942 BAUD MODEM 300BPS低速调制解调器74HC943 300 BAUD MODEM 300BPS低速调制解调器74LS00 QUAD 2-INPUT NAND GATES 与非门74LS02 QUAD 2-INPUT NOR GATES 或非门74LS03 QUAD 2-INPUT NAND GATES 与非门74LS04 HEX INVERTING GATES 反向器74LS05 HEX INVERTERS OPEN DRAIN 六路反向器74LS08 QUAD 2-INPUT AND GATE 与门74LS09 QUAD 2-INPUT AND GATES OC 与门74LS10 TRIPLE 3-INPUT NAND GATES 与非门74LS109 QUAD 2-INPUT AND GATES OC 与门74LS11 TRIPLE 3-INPUT AND GATES 与门74LS112 DUAL J-K FLIP-FLOP 双J-K触发器74LS113 DUAL J-K FLIP-FLOP PRESET 双JK触发器74LS114 NEGATIVE J-K FLIP-FLOP 负沿J-K触发器74LS122 Retriggerable Monostab 可重触发单稳74LS123 Retriggerable Monostable 可重触发单稳74LS125 TRI-STATE QUAD BUFFERS 四个三态门74LS13 QUAL 4-in NAND TRIGGER 4输入与非触发器74LS160 BCD DECADE 4BIT BIN COUNTERS 计数器74LS136 QUADRUPLE 2-INPUT XOR GATE 异或门74LS138 3-8 LINE DECODER 3线至8线译码器74LS139 2-4 LINE DECODER 2线至4线译码器74LS14 TRIGGERED HEX INVERTER 六触发反向器74HC147 10-4 LINE PRIORITY ENCODER 10-4编码器74HC148 8-3 LINE PRIORITY ENCODER 8-3编码器74HC149 8-8 LINE PRIORITY ENCODER 8-8编码器74LS151 8-CHANNEL DIGITAL MUX 8通道多路器74LS153 DUAL 4-INPUT MUX 双四输入多路器74LS155 2-4 LINE DECODER 2线至4线译码器74LS156 2-4 LINE DECODER/DEMUX 2-4译码器74LS157 QUAD 2-INPUT MUX 四个双端多路器74LS158 2-1 LINE MUX 2-1线多路器74LS160A BINARY COUNTER 二进制计数器74LS161A BINARY COUNTER 二进制计数器74LS162A BINARY COUNTER 二进制计数器74LS163A DECADE COUNTERS 十进制计数器74LS164 SERIAL-PARALLEL SHIFT REG 串入并出74LS168 BI-DIRECT BCD TO DECADE 双向计数器74LS169 4BIT UP/DN BIN COUNTER 四位加减计数器74LS173 TRI-STATE D FLIP-FLOP 三态D触发器74LS174 HEX D FLIP-FLOP W/CLEAR 六D触发器74LS175 HEX D FLIP-FLOP W/CLEAR 六D触发器74LS190 BINARY UP/DN COUNTER 二进制加减计数器74LS191 DECADE UP/DN COUNTER 十进制加减计数器74LS192 DECADE UP/DN COUNTER 十进制加减计数器74LS193 BINARY UP/DN COUNTER 二进制加减计数器74LS194A 4BIT BI-DIR SHIFT 4位双向移位寄存器74LS195A 4BIT PARALLEL SHIFT4位并行移位寄存器74LS20 QUAD 4-INPUT NAND GATE 四个四入与非门74LS21 4-INPUT AND GATE 四输入端与门74LS240 OCTAL 3-STATE BUFFER 八个三态缓冲门74LS244 OCTAL 3-STATE BUFFER 八个三态缓冲门74LS245 OCTAL 3-STATE TRANSCEIVER 三态收发器74LS253 DUAL 4-CH 3-STATE MUX 4路3态多路器74LS256 4BIT ADDRESS LATCH 四位可锁存锁存器74LS257 QUAD 2-CH 3-STATE MUX 4路3态多路器74LS258 2-CH 3-STATE MUX 2路3态多路器74LS27 TRIPLE 3-INPUT NOR GATES 三输入或非门74LS279 QUAD R-S LATCHES 四个RS非锁存器74LS28 QUAD 2-INPUT NOR BUFFER 四双端或非缓冲74LS283 4BIT BINARY ADDER CARRY 四位加法器74LS30 8-INPUT NAND GATES 八输入端与非门74LS32 QUAD 2-INPUT OR GATES 二输入或门74LS352 4-1 LINE SELECTOR/MUX 4-1线选择多路器74LS365 HEX 3-STATE BUFFER 六个三态缓冲门74LS367 3-STATE BUFFER INVERTER 缓冲反向器74LS368A 3-STATE BUFFER INVERTER 缓冲反向器74LS373 OCT LATCH W/3-STATE OUT三态输出锁存器74LS76 Dual JK Flip-Flop w/set 2个JK触发器74LS379 QUAD PARALLEL REG 四个并行寄存器74LS38 2-INPUT NAND GATE BUFFER 与非门缓冲器74LS390 DUAL DECADE COUNTER 2个10进制计数器74LS393 DUAL BINARY COUNTER 2个2进制计数器74LS42 BCD TO DECIMAL BCD转十进制译码器74LS48 BCD-7 SEG BCD-7段译码器74LS49 BCD-7 SEG BCD-7段译码器74LS51 AND OR GATE INVERTER 与或非门74LS540 OCT Buffer/Line Driver 8路缓冲驱动器74LS541 OCT Buffer/LineDriver 8路缓冲驱动器74LS74 D-TYPE FLIP-FLOP D型触发器74LS682 8BIT MAGNITUDE COMPARATOR 8路比较器74LS684 8BIT MAGNITUDE COMPARATOR 8路比较器74LS75 QUAD LATCHES 双锁存器74LS83A 4BIT BINARY ADDER CARRY 四位加法器74LS85 4BIT MAGNITUDE COMPARAT 4位判决电路74LS86 2INPUT EXCLUSIVE OR GATE 2输入异或门74LS90 DECADE/BINARY COUNTER 十/二进制计数器74LS95B 4BIT RIGHT/LEFT SHIFT 4位左右移位寄存74LS688 8BIT MAGNITUDE COMPARAT 8位判决电路74LS136 2-INPUT XOR GATE 2输入异或门74LS651 BUS TRANSCEIVERS 总线收发器74LS653 BUS TRANSCEIVERS 总线收发器74LS670 3-STATE 4-BY-4 REG 3态4-4寄存器74LS73A DUAL J-K FLIP-FLOP W/CLEAR 双JK触发器。

SN74AC74PWE4中文资料

PACKAGING INFORMATIONOrderable Device Status (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball FinishMSL Peak Temp (3)5962-88520012A ACTIVE LCCC FK 201TBD POST-PLATE N /A for Pkg Type 5962-8852001CA ACTIVE CDIP J 141TBD A42SNPB N /A for Pkg Type 5962-8852001DA ACTIVE CFPW 141TBD A42N /A for Pkg Type 5962-8852001VCA ACTIVE CDIP J 141TBD A42SNPB N /A for Pkg Type 5962-8852001VDA ACTIVE CFP W 141TBD A42N /A for Pkg Type SN74AC74D ACTIVE SOIC D 1450Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AC74DBLE OBSOLETE SSOP DB 14TBDCall TI Call TISN74AC74DBR ACTIVE SSOP DB 142000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AC74DBRE4ACTIVE SSOP DB 142000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AC74DE4ACTIVE SOIC D 1450Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AC74DG4ACTIVE SOIC D 1450Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AC74DR ACTIVE SOIC D 142500Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AC74DRE4ACTIVE SOIC D 142500Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AC74DRG4ACTIVE SOIC D 142500Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AC74N ACTIVE PDIP N 1425Pb-Free (RoHS)CU NIPDAU N /A for Pkg Type SN74AC74NE4ACTIVE PDIP N 1425Pb-Free (RoHS)CU NIPDAU N /A for Pkg Type SN74AC74NSR ACTIVE SO NS 142000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AC74NSRE4ACTIVE SO NS 142000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AC74PW ACTIVE TSSOP PW 1490Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AC74PWE4ACTIVE TSSOP PW 1490Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AC74PWLE OBSOLETE TSSOP PW 14TBDCall TI Call TISN74AC74PWR ACTIVE TSSOP PW 142000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AC74PWRE4ACTIVE TSSOP PW 142000Green (RoHS &no Sb/Br)CU NIPDAULevel-1-260C-UNLIMSNJ54AC74FK ACTIVE LCCC FK 201TBD POST-PLATE N /A for Pkg Type SNJ54AC74J ACTIVE CDIP J 141TBD A42SNPB N /A for Pkg Type SNJ54AC74WACTIVECFPW141TBDA42N /A for Pkg Type(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.18-Jul-2006OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -The planned eco-friendly classification:Pb-Free (RoHS),Pb-Free (RoHS Exempt),or Green (RoHS &no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt):This component has a RoHS exemption for either 1)lead-based flip-chip solder bumps used between the die and package,or 2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free (RoHS compatible)as defined above.Green (RoHS &no Sb/Br):TI defines "Green"to mean Pb-Free (RoHS compatible),and free of Bromine (Br)and Antimony (Sb)based flame retardants (Br or Sb do not exceed 0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annualbasis.18-Jul-2006IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityLow Power Wireless /lpw Telephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2006, Texas Instruments Incorporated。

74hc74的中文资料

D(L) 20*

保持时间tH

5*

*表示以 CP 上升沿为参考

54H74/74H74 最小 额定 最大

4.5

5

5.5

4.75 5 5.25

2

0.8

0.8

-1000

20 20

0

35

15 13.5 25

10* 15*

5*

54S74/74S74 最小 额定 最大

4.5 5

5.5

4.75 5

5.25

2 0.8

0.5V)

D CLR PR CP

-1.6

-2

-3.2

-4

-1.6

-2

-3.2

-4

-2

-0.4

-6 -4

-0.8 -0.8

mA

-4

-0.4

IOS输出短路电流

Vcc=最大

54 74

-20 -18

-57 -57

-40 -40

-100 -100

-40 -40

-100 -100

-20 -20

-100 -100

VI=5.5V(‘LS74 为 PR,CLR

1

1

1

0.2

7V)

IIH 输 入 高 电 平 电 流

Vcc=最大

VIH=2.4V(‘S74 和’LS74 为 2.7V)

D CLR PR CP

40

50

50

120

150

150

80

100

100

80

100

100

20

40 40

uA

20

IIL输入低电平电 流

Vcc=最大 VIL=0.4V(‘S74 为

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

74HC74; 74HCT74

handbook, halfpage handbook, halfpage

1RD 1

VCC 14 13 12 2RD 2D 2CP 2SD 2Q

1RD 1D 1CP 1SD 1Q 1Q GND

1 2 3 4 5 6 7

MNA417

14 VCC 13 2RD 12 2D

1D 1CP 1SD 1Q

Fig.1

Pin configuration DIP14, SO14 and (T)SSOP14.

Fig.2 Pin configuration DHVQFN14.

2003 Jul 10

4

元器件交易网

Philips Semiconductors

Product specification

元器件交易网

INTEGRATED CIRCUITS

DATA SHEET

74HC74; 74HCT74 Dual D-type flip-flop with set and reset; positive-edge trigger

Product specification Supersedes data of 1998 Feb 23 2003 Jul 10

2003 Jul 10

2

元器件交易网

Philips Semiconductors

Product specification

Dual D-type flip-flop with set and reset; positive-edge trigger

FUNCTION TABLES Table 1 See note 1 INPUT SD L H L Table 2 See note 1 INPUT SD H H Note 1. H = HIGH voltage level; L = LOW voltage level; X = don’t care; ↑ = LOW-to-HIGH CP transition; Qn+1 = state after the next LOW-to-HIGH CP transition. ORDERING INFORMATION PACKAGE TYPE NUMBER 74HC74N 74HCT74N 74HC74D 74HCT74D 74HC74DB 74HCT74DB 74HC74PW 74HCT74PW 74HC74BQ 74HCT74BQ TEMPERATURE RANGE −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C PINS 14 14 14 14 14 14 14 14 14 14 PACKAGE DIP14 DIP14 SO14 SO14 SSOP14 SSOP14 TSSOP14 TSSOP14 DHVQFN14 DHVQFN14 RD H H CP ↑ ↑ D L H RD H L L CP X X X D X X X

74HC74; 74HCT74

GENERAL DESCRIPTION The 74HC/HCT74 is a high-speed Si-gate CMOS device and is pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A. The 74HC/HCT74 are dual positive-edge triggered, D-type flip-flops with individual data (D) inputs, clock (CP) inputs, set (SD) and reset (RD) inputs; also complementary Q and Q outputs. The set and reset are asynchronous active LOW inputs and operate independently of the clock input. Information on the data input is transferred to the Q output on the LOW-to-HIGH transition of the clock pulse. The D inputs must be stable one set-up time prior to the LOW-to-HIGH clock transition for predictable operation. Schmitt-trigger action in the clock input makes the circuit highly tolerant to slower clock rise and fall times.

74HC74; 74HCT74

OUTPUT Q H L H Q L H H

OUTPUT Qn+1 L H Qn+1 H L

MATERIAL plastic plastic plastic plastic plastic plastic plastic plastic plastic plastic

CODE SOT27-1 SOT27-1 SOT108-1 SOT108-1 SOT337-1 SOT337-1 SOT402-1 SOT402-1 SOT762-1 SOT762-1

MNA418

handbook, halfpage

4 3 2

S C1 1D R

5

5 9

1

6

6 8

10 11 12 13

S C1 1D R

MNA419

9

8

Fig.3 Logic symbol.

Fig.4 IEC logic symbol.

handbook, halfpage

4

Hale Waihona Puke 1SD SD D CP FF Q RD 1Q 6 Q

Dual D-type flip-flop with set and reset; positive-edge trigger

74HC74; 74HCT74

handbook, halfpage

4 10 1SD 2SD 2 12 3 11 SD 1Q 1D Q D 2D 2Q 1CP CP 2CP FF 1Q Q 2Q RD 1RD 2RD 1 13

Product specification

Dual D-type flip-flop with set and reset; positive-edge trigger

2 3

1D 1CP

1Q

5

1 10

1RD 2SD SD D CP FF Q RD 2Q 8 Q

12 11

2D 2CP

2Q

9

13

2RD

MNA420

Fig.5 Functional diagram.

2003 Jul 10

5

元器件交易网

Philips Semiconductors

QUICK REFERENCE DATA GND = 0 V; Tamb = 25 °C; tr = tf = 6 ns TYPICAL SYMBOL tPHL/tPLH PARAMETER propagation delay nCP to nQ, nQ nSD to nQ, nQ nRD to nQ, nQ fmax CI CPD Notes 1. CPD is used to determine the dynamic power dissipation (PD in µW). PD = CPD × VCC2 × fi × N + Σ(CL × VCC2 × fo) where: fi = input frequency in MHz; fo = output frequency in MHz; CL = output load capacitance in pF; VCC = supply voltage in Volts; N = total load switching outputs; Σ(CL × VCC2 × fo) = sum of the outputs. 2. For 74HC74 the condition is VI = GND to VCC. For 74HCT74 the condition is VI = GND to VCC − 1.5 V. maximum clock frequency input capacitance power dissipation capacitance per flip-flop notes 1 and 2 CONDITIONS HC CL = 15 pF; VCC = 5 V 14 15 16 76 3.5 24 15 18 18 59 3.5 29 ns ns ns MHz pF pF HCT UNIT

元器件交易网

Philips Semiconductors

Product specification

Dual D-type flip-flop with set and reset; positive-edge trigger

FEATURES • Wide supply voltage range from 2.0 to 6.0 V • Symmetrical output impedance • High noise immunity • Low power dissipation • Balanced propagation delays • ESD protection: HBM EIA/JESD22-A114-A exceeds 2000 V MM EIA/JESD22-A115-A exceeds 200 V.