NXP LPC111x芯片中文手册—11 带SSP的SPI01

LPC1114的IO配置部分的中文手册

表111. LPC111x 引脚配置引脚配置--图8–10引脚描述表8–114引脚配置--图8–10引脚描述表8–114引脚配置图8–8-图8–10引脚描述表8–112表8–114图8–10表8–112表8–113表8–1143. LPC111x 引脚描述表 112. LPC1113/14 引脚描述表 (LQFP48 封装)RESET — 外部复位输入:此引脚上的低电平会使设备复位,I/O 端口和外设复位成初始的默认状态,并使处理器从0地址开始执行。

I/O PIO0_0 — 通用数字输入/输出引脚。

PIO0_1/CLKOUT/ CT32B0_MAT2PIO0_2/SSEL0/ CT16B0_CAP04[1]I/O PIO0_1 —通用数字输入/输出引脚。

复位时低电平启动在线系统编程命令处 理程序。

O CLKOUT — 时钟输出脚。

OCT32B0_MAT2 —32位定时器0匹配输出2。

10[1]I/O PIO0_2 —通用数字输入/输出引脚。

O SSEL0 —SPI0从机选择。

ICT16B0_CAP0 —16位定时器0捕获输入0。

PIO0_314[1] I/OPIO0_3 —通用数字输入/输出引脚。

.I/O SCK0 —SPI0串行时钟。

PIO0_7/CTS 23[1] I/O PIO0_7 —通用数字输入/输出引脚(大电流输出驱动器)。

I CTS —UART清除发送。

PIO0_8/MISO0/CT16B0_MAT0PIO0_9/MOSI0/CT16B0_MAT1 SWCLK/PIO0_10/ SCK0/CT16B0_MAT2TDI/PIO0_11/AD0/CT32B0_MAT3 TMS/PIO1_0/AD1/CT32B1_CAP0 TDO/PIO1_1/AD2/CT32B1_MAT0TRST/PIO1_2/AD3/CT32B1_MAT1 27[1] I/O PIO0_8 —通用数字输入/输出引脚。

NXP mcu

置的新型开漏工作模式

LPC1100

◎ 四个通用计数器/计数器 ◎ 可编程的看门狗定时器(WDT),带锁死功能 ◎ 系统计时器 ◎ 各外设自带时钟分频器,有利于降低功耗

芯片特色:

Cortex-M0处理器性能 ● Cortex-M0微控制器可以轻松超越高端8位和16位器件的

性能水平; ● 内核额定性能为0.9DMIPS/MHz,相当于与其最接近的8位

EasyCortex M3-1300开发平台板载USB仿真器,支持USB2.0 Device,具有带电气隔离的RS-485接口等功能。EasyCortexM3-1300开发平台配套 提供多种免费商业化软件包及其详尽的开发文档,加快产品开发。

集学习、实验、开发于一体的 “三合一”高性价比开发板

● 功能特点 ◎ 标配CPU:LPC1343,全面支持LPC1313、LPC1100系列 芯片; ◎ 处理速率高达72MHz; ◎ 片上集成HID和大容量USB设备驱动; ◎ 内置嵌套向量中断控制器(NVIC); ◎ 32KB片上Flash程序存储器,支持在系统编程(ISP)和在 应用编程(IAP); ◎ 8KB SRAM可供高性能CPU通过指令总线、系统总线和 数据总线访问; ◎ 串行调试端口和串行跟踪端口; ◎ 3种低功耗模式:睡眠、深度睡眠和深度掉电; ◎ 集成PMU(电源管理单元),进一步降低功耗; ◎ 掉电检测,设有4个独立的中断和强制复位阈值; ◎ 片内集成上电复位电路; ◎ 内置系统节拍定时器(SysTick),方便操作系统移植; ◎ 3.3V单电源供电(2.0V ~3.6V); ◎ 工作温度:-40°C ~ 85°C。

Cortex-M0组件 Cortex-M0处理器

中断

嵌套向量 中断控制器

(NVIC)

LPC111x开发步骤详解

7 新建文件 工程创建完成后,系统为工程自动分配两个文件 夹,里面已经包含部分文件,用户编写程序需要 新建.c文件

创建.c文件过程

注:在设计编程的 过程中,我们通常在已 有程序基础上,根据实 际要求进行修改,因此 在创建.c文件时,也通 常复制已有程序,直接 粘贴到目标工程,进行 修改。

4.3 编译 调试 下载

微控制器及开发环境介绍

LPC1114

LPCXpresso

LPC111x

LPC111x是基于ARM Cortex-M0的32位微控制器, 可用于高集成度和低功耗的嵌入式应用。

LPC111x特性:

LPC111x CPU的工作频率最高达50MHz; ARM Cortex-M0处理器内置有嵌套向量中断控制器(NVIC); 时钟系统 晶体振荡器的工作范围为1MHz~25MHz; PLL允许CPU无需使用高频晶体而工作在最大CPU速率下。时 钟可以由主振荡器、内部RC振荡器或看门狗振荡器提供; 12MHz内部RC振荡器可调节到1%的精度;可以选择用作一个 系统时钟; 单个3.3V电源(2.0V~3.6V);带分频器的时钟输出功能可以 反映主振荡器时钟、IRC时钟、CPU时钟或看门狗时钟;

3.2网络注册

之后弹出序列号生成窗口,系统自动根据用户的硬件配置生成 序列号,点击Copy to clipboard 点击下一步,出现注册激活页,此时要保证计算机已联网,将 出现web表格,根据要求填写相应信息 填写完毕后,会在所提交的邮箱内收到一封注册信息:用户名 和密码,根据邮件提供的网站登录注册,将会收到第二封包含 激活密码的邮件

LPC111x

串行接口: UART:可产生小数波特率,带有内部FIFO,支持RS485/EIA-485,具有moderm控制; 2个SPI接口,SSP控制器,具有FIFO和多协议功能; I2C总线接口支持全部I2C总线规范和Fast-mode Plus模式, 数据速率高达1Mbit/s,具有多地址识别和监控模式; 其它外设: 多达42个通用I/O(GPIO)引脚,上拉/下拉电阻可配置;

NXPLPC111x芯片中文手册―11带SSP的SPI01

up .w hd 1. 如何阅读本章所有 LPC111x 系列中的 SPI 模块均相同。

第二个 SPI 模块, SPI1,只存在于LQFP48和 PLCC44封装上,在 HVQFN33封装上则没有。

注释:两个 SPI 模块都包含全部的 SSP 特征集,所有相关寄存器都使用 SSP 前缀命名。

2. 特性? 兼容 Motorola SPI 、 4线 TI SSI 和美国国家半导体公司的 Microwire 总线。

? 同步串行通信。

? 支持主机和从机操作。

? 收发均有 8帧 FIFO 。

?每帧有 4-16位数据。

3. 基本描述SPI/SSP是一个同步串行端口 (SSP控制器,可控制 SPI 、 4线 SSI 和 Microwire 总线。

它可以与总线上的多个主机和从机相互作用。

在数据传输过程中,总线上只能有一个主机与一个从机进行通信。

原则上数据传输是全双工的, 4~16位帧的数据由主机发送到从机或由从机发送到主机。

但实际上,大多数情况下只有一个方向上的数据流包含有意义的数据。

LPC111x 系列处理器有两个 SPI/同步串行端口控制器。

u d u UM10398Semiconductors LPC1100开发,尽在第 11章 :LPC111x 带有 SSP 的 SPI0/1 4. 引脚描述表 161622. SPI 引脚描述SCK0/1I/OSCK CLK SK 串行时钟。

SCK/CLK/SK是用来同步数据传输的时钟信号。

它由主机驱动,从机接收。

当使用 SPI 接口时,时钟可编程为高电平有效或低电平有效,否则总是高电平有效。

SCK 仅在数据传输过程中切换。

在其它时间里, SPI/SSP接口保持无效状态或不驱动它(使其处于高阻态。

SSEL0/1I/OSSEL FS CS 帧同步 /从机选择。

当 SPI/SSP接口是总线主机时,它在串行数据启动前驱动该信号为有效状态。

在数据发送出去之后又将该信号恢复为无效状态。

LPC111x 产品数据手册

LPC1111/12/13/14 32-位 ARM Cortex-M0 微控制器

4. 订购信息

表1 订购信息 器件编号 LPC1111FHN33/101 LPC1111FHN33/102 LPC1111FHN33/201 LPC1111FHN33/202 LPC1112FHN33/101 LPC1112FHN33/102 LPC1112FHN33/201 LPC1112FHN33/202 LPC1113FHN33/201 LPC1113FHN33/202 LPC1113FHN33/301 LPC1113FHN33/302 LPC1114FHN33/201 LPC1114FHN33/202 LPC1114FHN33/301 LPC1114FHN33/302 LPC1113FBD48/301 LPC1113FBD48/302 LPC1114FBD48/301 LPC1114FBD48/302 LPC1114FA44/301[1] LPC1114FA44/302[1] [1] 名称 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 HVQFN33 LQFP48 LQFP48 LQFP48 LQFP48 PLCC44 PLCC44 封装信息 描述 HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm HVQFN:超薄塑料热增强型扁平封装;无引线;33 个 引脚;裸片尺寸:7×7×0.85mm LQFP48:塑料薄型QFP;48 条引线;裸片尺寸:7×7 ×1.4mm LQFP48:塑料薄型QFP;48 条引线;裸片尺寸:7×7 ×1.4mm LQFP48:塑料薄型QFP;48 条引线;裸片尺寸:7×7 ×1.4mm LQFP48:塑料薄型QFP;48 条引线;裸片尺寸:7×7 ×1.4mm PLCC44:带引线的塑料芯片载体;44 条引线 PLCC44:带引线的塑料芯片载体;44 条引线 版本 n/a n/a n/a n/a n/a n/a n/a n/a n/a n/a n/a n/a n/a n/a n/a n/a sot313-2 sot313-2 sot313-2 sot313-2 sot187-2 sot187-2

NXP芯片手册1

NXP LPCXpresso-CN用户手册V1.0

NXP LPCXpresso-CN开发板用户手册Rev. 1.0Releas e: 2010-12-14 NXP Semiconductors (Shanghai) Ltd地址:上海市裕通路100号宝矿洲际商业中心19-21层电话: +86 21 2205 2222传真: +86 21 2205 2518恩智浦半导体/microcontrollers目录NXP LPCXPRESSO-CN开发板用户手册 (1)1.概述 (5)1.1核心芯片介绍 (5)1.2开发板简介 (5)1.3硬件资源列表 (5)1.4软件资源列表 (6)2.快速启用 (7)2.1文档描述 (7)2.2版本信息 (7)2.3硬件资源要求 (7)2.4准备工作 (7)2.5使用出厂程序 (8)2.6恢复出厂程序 (9)2.6.1编译出厂程序 (9)2.6.2下载出厂程序 (9)3.NXP LPCXPRESSO-CN开发板详细介绍 (10)3.1硬件接口一览表 (10)3.2出厂跳线设置 (10)3.3硬件接口介绍 (10)3.3.1JTAG调试口 (10)3.3.2UART (10)3.3.3USB Mini AB接口 (11)3.3.4LM75温度传感器 (11)3.3.5LED (11)4.软件资源介绍 (12)4.1LED B LINKY测试 (12)4.2S YS T ICK测试 (12)4.3T IMER32测试 (12)4.4SSP测试 (12)4.5UART测试 (13)4.6I2C T EMPERATURE S ENSOR测试 (13)5.软件资源测试 (14)5.1MDK介绍 (14)5.2编译例程 (14)5.2.1打开例程 (14)5.2.2编译例程 (15)5.3使用仿真器调试和下载程序 (17)5.3.1使用ULINK2调试和下载程序 (17)5.3.2使用ColinkEx下载和调试程序 (23)5.4使用ISP下载程序 (26)1.概述1.1核心芯片介绍NXP LPCXpresso-CN开发板使用LPC1114F301芯片,此芯片使用高性能的ARM® Cortex ™-M0 32位的RISC内核(针对8位/16位微控制器应用设计),工作频率为50MHz,属LPC1100系列微控制器。

LPC1114

00 P = 1

01 P = 2

10 P = 4

11

P=8

-

保留. 不要将1写到这些保留位中。

0x00 0x0

4.4 系统 PLL状态寄存器

User manual

Rev. 00.10 — 11 January 2010

© NXP B.V. 2010. All rights reserved.

10 of 326

此LPC111X 数据手册之中文翻译,由武汉理工大学UP团队友情提供,仅供学习交流之用,欢迎指正,共同修改完善。

NXP Semiconductors

0

复位SPI0外设。

1

SPI0 复位失效。

1

I2C_RST_N

I2C复位控制

0x1

0

复位I2C 外设。

1

I2C 复位失效。

UM10398_0

User manual

Rev. 00.10 — 11 January 2010

© NXP B.V. 2010. All rights reserved.

13 of 326

-

0x0DC

保留

R/W

0x0E0

CLKOUT时钟源选择

R/W

0x0E4

CLKOUT时钟源更新允许

R/W

0x0E8

CLKOUT时钟分频器

-

0x0EC - 0x0FC 保留

R

0x100

POR捕获PIO状态0

R

0x104

POR捕获PIO状态1

0x000 0x000 0x000 0x000 0x001 0x85F 0x000 0x000 0x000 0x000 0x000 0x000 0x000 0x000 0x000 依赖用户

NXP mcu

TinyM0核心板电路为LPC111x芯片的最小系统,硬件支持2.54mm间距的 标准排针。用户可以将TinyM0核心板配套自行设计的底板进行产品开发。 ● 支持多款芯片

和16位竞争产品的2至4倍。

Cortex-M0内核

● 32位ARM RISC处理器,16位Thumb指令集; ● 功耗与面积高度优化,设计专用于低成本、低功耗场合; ● 24位SysTick定时器; ● 32位硬件乘法器; ● 中断现场自动保存,有处理决定性、固定延迟的中断能力; ● 系统接口支持小端或字节不变的大端数据访问; ● SWD串行线调试。

LPC1300选型表:

器件型号 LPC1343 LPC1342 LPC1313 LPC1311

Flash (KB) 32 16 32 8

SRAM(KB) 8 4 8 2

USB 2.0 Device Device

-

I2C(Fast+) 1 1 1 1

ADC 8ch/10bit 8ch/10bit 8ch/10bit 8ch/10bit

置的新型开漏工作模式

LPC1100

◎ 四个通用计数器/计数器 ◎ 可编程的看门狗定时器(WDT),带锁死功能 ◎ 系统计时器 ◎ 各外设自带时钟分频器,有利于降低功耗

芯片特色:

Cortex-M0处理器性能 ● Cortex-M0微控制器可以轻松超越高端8位和16位器件的

性能水平; ● 内核额定性能为0.9DMIPS/MHz,相当于与其最接近的8位

06_LPC111x 通用 IO (GPIO)

PIO0_0 - PIO0_11 PIO1_0 - PIO1_11 PIO2_0

R/W

31:12

-

-

3.5 GPIO 中断事件寄存器

p u

位 11:0 31:12 UM10398_0

表 56.

标志

IEV

w .

-

GPIOnIEV 寄存器 (GPIO 0IE V, 地址 0x50 00 800C 至 GPIO 3IEV, 地址 0x50 03 (GPIO0 IEV x500 GPIO3 x500 0C) 位域描述 80 800 访问方式 值 描述 复位值

每个GPIO寄存器都支持多达12位的宽度,可以在字地址已半字或字的形式进行访问。

UM10398_0

© NXP B.V. 2010. All rights reserved.

er man ual Us Use anu

uary 2010 Rev. 00.10 — 11 Jan Janu

此LPC111X 数据手册之中文翻译,由武汉理工大学UP团队友情提供,仅供学习交流之用,欢迎指正,共同修改完善。

w .

u h

d e . t

n c . u

GPIO 端口3 PIO3_0 - PIO3_5 PIO3_4 和 PIO3_5 PIO3_0 - PIO3_5

IO GP GPI 总数

PIO3_2; PIO3_4; PIO3_5 28 PIO3_2; PIO3_4; PIO3_5 28 PIO3_2; PIO3_4; PIO3_5 28 42 38 42 PIO3_2; PIO3_4; PIO3_5 28

18-LPC111x_SW调试

p.w h ut.ed u.c n1.如何阅读本章LPC111x系列处理器的调试功能均一样。

2.特性•支持ARM SWD(串行线调试)模式。

•可直接调试可访问所有的内存地址,寄存器和外设。

•可无目标资源调试。

•四个断点。

四个指令断点可以被用于重映射作为代码补丁的指令地址。

两个数据比较器可以被用于重映射作为文字值补丁的地址。

•两个数据观测点可用作触发器。

3.简介ARM Cortex-M0集成了调试功能。

并支持串行线调试。

ARM Cortex-M0配置为支持四个断点和两个观察点。

4.描述使用LPC111x串行线调试模式进行调试。

5.引脚描述下表描述了关于调试的各引脚的功能。

其中一些功能与其它功能复用引脚,因此不能同时使用。

表242488.J T AG引脚描述TCK输入钟。

TMS输入J T AG测试模式选择。

在TAP状态机中TMS引脚选择下一个状态。

TDI输入J T AG测试数据输入。

该引脚是移位寄存器的串行数据输入。

TDO输出J T AG测试数据输出。

该引脚是移位寄存器的串行数据输出。

当处在TCK信号的下降沿的时候数据被移位发送出处理器。

TRST输入J T AG测试复位。

TRST引脚能重启调试逻辑中的测试逻辑。

up .w h u t .e d u .c n LPC1100开发,尽在CoocoxNXP Semiconductors UM10398第18章:LPC111x SW 调试SWCLK输入串行时钟。

在SWD 模式下这个引脚用作调试逻辑的时钟(SWDCLK)。

在JTAG 模式下是TCK 引脚。

SWDIO 输入/输出串行数据输入/输出。

SWDIO 引脚被用于外部调试工具与LPC111x 处理器进行通信,并控制处理器。

6.调试说明重要:用户应该意识到在调试时候的某些限制。

最重要的是,由于ARM Cortex-M0集成的限制,LPC111x 不能使用通常的方式从深度睡眠模式中唤醒CPU 。

在调试期间,建议不要使用这种模式。

MEMORY存储芯片LPC1115FBD48_303中文规格书

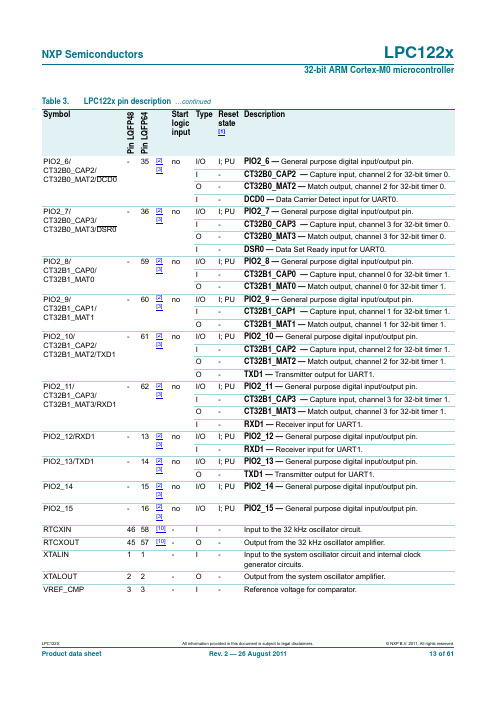

LPC122X All information provided in this document is subject to legal disclaimers.© NXP B.V. 2011. All rights reserved.Product data sheet Rev. 2 — 26 August 2011 13 of 61NXP Semiconductors LPC122x 32-bit ARM Cortex-M0 microcontroller PIO2_6/CT32B0_CAP2/CT32B0_MAT2/DCD0-35[2][3]no I/O I; PU PIO2_6 — General purpose digital input/output pin.I -CT32B0_CAP2 — Capture input, channel 2 for 32-bit timer 0.O -CT32B0_MAT2 — Match output, channel 2 for 32-bit timer 0.I -DCD0 — Data Carrier Detect input for UART0.PIO2_7/CT32B0_CAP3/CT32B0_MAT3/DSR0-36[2][3]no I/O I; PUPIO2_7 — General purpose digital input/output pin.I -CT32B0_CAP3 — Capture input, channel 3 for 32-bit timer 0.O -CT32B0_MAT3 — Match output, channel 3 for 32-bit timer 0.I -DSR0 — Data Set Ready input for UART0.PIO2_8/CT32B1_CAP0/CT32B1_MAT0-59[2][3]no I/O I; PUPIO2_8 — General purpose digital input/output pin.I -CT32B1_CAP0 — Capture input, channel 0 for 32-bit timer 1.O -CT32B1_MAT0 — Match output, channel 0 for 32-bit timer 1.PIO2_9/CT32B1_CAP1/CT32B1_MAT1-60[2][3]no I/O I; PUPIO2_9 — General purpose digital input/output pin.I -CT32B1_CAP1 — Capture input, channel 1 for 32-bit timer 1.O -CT32B1_MAT1 — Match output, channel 1 for 32-bit timer 1.PIO2_10/CT32B1_CAP2/CT32B1_MAT2/TXD1-61[2][3]no I/O I; PUPIO2_10 — General purpose digital input/output pin.I -CT32B1_CAP2 — Capture input, channel 2 for 32-bit timer 1.O -CT32B1_MAT2 — Match output, channel 2 for 32-bit timer 1.O -TXD1 — Transmitter output for UART1.PIO2_11/CT32B1_CAP3/CT32B1_MAT3/RXD1-62[2][3]no I/O I; PUPIO2_11 — General purpose digital input/output pin.I -CT32B1_CAP3 — Capture input, channel 3 for 32-bit timer 1.O -CT32B1_MAT3 — Match output, channel 3 for 32-bit timer 1.I -RXD1 — Receiver input for UART1.PIO2_12/RXD1-13[2][3]no I/O I; PUPIO2_12 — General purpose digital input/output pin.I -RXD1 — Receiver input for UART1.PIO2_13/TXD1-14[2][3]no I/O I; PUPIO2_13 — General purpose digital input/output pin.O -TXD1 — Transmitter output for UART1.PIO2_14-15[2][3]no I/O I; PUPIO2_14 — General purpose digital input/output pin.PIO2_15-16[2][3]no I/O I; PUPIO2_15 — General purpose digital input/output pin.RTCXIN 4658[10]-I -Input to the 32 kHz oscillator circuit.RTCXOUT 4557[10]-O -Output from the 32 kHz oscillator amplifier.XTALIN 11-I -Input to the system oscillator circuit and internal clock generator circuits.XTALOUT 22-O -Output from the system oscillator amplifier.VREF_CMP 33-I -Reference voltage for comparator.Table 3.LPC122x pin description …continuedSymbol P i n L Q F P 48P i n L Q F P 64Start logic inputType Reset state [1]DescriptionLPC122X All information provided in this document is subject to legal disclaimers.© NXP B.V. 2011. All rights reserved.Product data sheet Rev. 2 — 26 August 2011 14 of 61NXP Semiconductors LPC122x 32-bit ARM Cortex-M0 microcontroller[1]Pin state at reset for default function: I = Input; O = Output; PU = internal pull-up enabled; IA = inactive, no pull-up/down enabled.[2]3.3 V tolerant, digital I/O pin; default: pull-up enabled, no hysteresis.[3]If set to output, this normal-drive pin is in low mode by default.[4]I 2C-bus pins; 5 V tolerant; open-drain; default: no pull-up/pull-down; no hysteresis.[5] 3.3 V tolerant, digital I/O pin with RESET function; default: pull-up enabled, no hysteresis. An external pull-up resistor is required on this pin for the Deep power-down mode.[6]3.3 V tolerant, digital I/O pin with analog function; default: pull-up enabled, no hysteresis.[7]If set to output, this normal-drive pin is in high mode by default.[8]3.3 V tolerant, digital I/O pin with analog function and WAKEUP function; default: pull-up enabled, no hysteresis.[9] 3.3 V tolerant, high-drive digital I/O pin; default: pull-up enabled, no hysteresis.[10]If the RTC is not used, RTCXIN and RTCXOUT can be left floating.To enable a peripheral function, find the corresponding port pin, or select a port pin if thefunction is multiplexed, and program the port pin’s IOCONFIG register to enable that function. The primary SWD functions and RESET are the default functions on their pinsafter reset. V DD(IO)4763-I -Input/output supply voltage.V DD(3V3)4456-I - 3.3 V supply voltage to the internal regulator and the ADC. Also used as the ADC reference voltage.V SSIO4864-I -Ground.V SS4355-I -Ground.Table 3.LPC122x pin description …continuedSymbol P i n L Q F P 48P i n L Q F P 64Start logic inputType Reset state [1]Description Table 4.Pin multiplexing Peripheral FunctionType Available on ports:Analog comparatorsROSCI/O PIO0_29--ACMP0_I0I PIO0_19--ACMP0_I1I PIO0_20--ACMP0_I2I PIO0_21--ACMP0_I3I PIO0_22--ACMP0_OO PIO0_27--ACMP1_I0I PIO0_23--ACMP1_I1I PIO0_24--ACMP1_I2I PIO0_25--ACMP1_I3I PIO0_26--ACMP1_O O PIO0_28--。

LPC11C1x_C_CANDriver

13.4.1 调用C_CAN API ........................................................................................................1 13.4.2 CAN初始化 ................................................................................................................2 13.4.3 CAN中断处理程序 ....................................................................................................3 13.4.4 CAN Rx报文对象配置...............................................................................................3 13.4.5 CAN接收 ....................................................................................................................3 13.4.6 CAN发送 ....................................................................................................................4 13.4.7 CANopen配置.............................................................................................................4 13.4.8 CANopen处理程序.....................................................................................................6 13.4.9 CAN/CANopen回调函数 ...........................................................................................6 13.4.10 CAN报文接收的回调 ................................................................................................7 13.4.11 CAN报文发送回调 ....................................................................................................7 13.4.12 CAN错误回调 ............................................................................................................7 13.4.13 CANopen SDO加速的读回调....................................................................................8 13.4.14 CANopen SDO加速的写回调....................................................................................8 13.4.15 CANopen SDO分段的读回调....................................................................................9 13.4.16 CANopen SDO分段的写回调..................................................................................10 13.4.17 CANopen fall-back SDO处理程序回调...................................................................11

LPC111x中文版用户手册

20101102

LPC111x/LPC11C1x 用户手册

• 增加了 LPC111x/102/202/302 (LPC1100L 系列 ) ( 表 1,表 280)。 • 更新了 PLL 输出频率 (< 100 MHz),见 3.10 节 “ 系统 PLL 功能描述 ”。 • 更新了对深度睡眠模式和深度掉电模式的描述,见 3.8 节 “ 电源管理 ”。 • 增加了第五章 “LPC111x/LPC11Cxx 功耗配置 ” 。 • WDT 更改为 24 位定时器,见 17 章 “LPC111x/LPC11Cxx 看门狗定时器 (WDT)”。 • 21.6.2 章节的 “ 调试连接 ”。 • SYSTCKCAL 寄存器的地址改为 0x4004 8154 ( 表 6 和表 33)。 • 添加了比较 flash 映像的注解 ( 20.10 章节的 “flash 映像的注解 ”)。 • 在 20.5 部分 -“UART ISP 命令 ” 中,ISP 的波特率被严格限制 (230400 bps 除外)。 • Flash 写操作的干扰影响 (20.5.7 节的 “ 复制 RAM 到 flash<Flash address> <RAM address> <no of

版权所有 2012恩智浦有限公司 未经许可,禁止转载

NXP Semiconductors

UM10398

LPC111x/LPC11Cxx User manual

修改记录 版本 5 更新:

4 更新: 3 更新:

2 更新:

1

日期

描述

20110621

LPC111x/LPC11C1x/LPC11C2x 用户手册

片上 C_CAN 驱动器和闪存的系统编程工具通过 C_CAN 连接在 LPC11Cxx 里,此外 LPC11C2x 还包含一个一个片上 CAN 收发器。

LPC1114的IO配置部分的中文手册

表111. LPC111x 引脚配置引脚配置--图8–10引脚描述表8–114引脚配置--图8–10引脚描述表8–114引脚配置图8–8-图8–10引脚描述表8–112表8–114图8–10表8–112表8–113表8–1143. LPC111x 引脚描述表 112. LPC1113/14 引脚描述表 (LQFP48 封装)RESET — 外部复位输入:此引脚上的低电平会使设备复位,I/O 端口和外设复位成初始的默认状态,并使处理器从0地址开始执行。

I/O PIO0_0 — 通用数字输入/输出引脚。

PIO0_1/CLKOUT/ CT32B0_MAT2PIO0_2/SSEL0/ CT16B0_CAP04[1]I/O PIO0_1 —通用数字输入/输出引脚。

复位时低电平启动在线系统编程命令处 理程序。

O CLKOUT — 时钟输出脚。

OCT32B0_MAT2 —32位定时器0匹配输出2。

10[1]I/O PIO0_2 —通用数字输入/输出引脚。

O SSEL0 —SPI0从机选择。

ICT16B0_CAP0 —16位定时器0捕获输入0。

PIO0_314[1] I/OPIO0_3 —通用数字输入/输出引脚。

.I/O SCK0 —SPI0串行时钟。

PIO0_7/CTS 23[1] I/O PIO0_7 —通用数字输入/输出引脚(大电流输出驱动器)。

I CTS —UART清除发送。

PIO0_8/MISO0/CT16B0_MAT0PIO0_9/MOSI0/CT16B0_MAT1 SWCLK/PIO0_10/ SCK0/CT16B0_MAT2TDI/PIO0_11/AD0/CT32B0_MAT3 TMS/PIO1_0/AD1/CT32B1_CAP0 TDO/PIO1_1/AD2/CT32B1_MAT0TRST/PIO1_2/AD3/CT32B1_MAT1 27[1] I/O PIO0_8 —通用数字输入/输出引脚。

NXPLPC111x芯片中文手册―11带SSP的SPI01

up .w hd 1. 如何阅读本章所有 LPC111x 系列中的 SPI 模块均相同。

第二个 SPI 模块, SPI1,只存在于LQFP48和 PLCC44封装上,在 HVQFN33封装上则没有。

注释:两个 SPI 模块都包含全部的 SSP 特征集,所有相关寄存器都使用 SSP 前缀命名。

2. 特性? 兼容 Motorola SPI 、 4线 TI SSI 和美国国家半导体公司的 Microwire 总线。

? 同步串行通信。

? 支持主机和从机操作。

? 收发均有 8帧 FIFO 。

?每帧有 4-16位数据。

3. 基本描述SPI/SSP是一个同步串行端口 (SSP控制器,可控制 SPI 、 4线 SSI 和 Microwire 总线。

它可以与总线上的多个主机和从机相互作用。

在数据传输过程中,总线上只能有一个主机与一个从机进行通信。

原则上数据传输是全双工的, 4~16位帧的数据由主机发送到从机或由从机发送到主机。

但实际上,大多数情况下只有一个方向上的数据流包含有意义的数据。

LPC111x 系列处理器有两个 SPI/同步串行端口控制器。

u d u UM10398Semiconductors LPC1100开发,尽在第 11章 :LPC111x 带有 SSP 的 SPI0/1 4. 引脚描述表 161622. SPI 引脚描述SCK0/1I/OSCK CLK SK 串行时钟。

SCK/CLK/SK是用来同步数据传输的时钟信号。

它由主机驱动,从机接收。

当使用 SPI 接口时,时钟可编程为高电平有效或低电平有效,否则总是高电平有效。

SCK 仅在数据传输过程中切换。

在其它时间里, SPI/SSP接口保持无效状态或不驱动它(使其处于高阻态。

SSEL0/1I/OSSEL FS CS 帧同步 /从机选择。

当 SPI/SSP接口是总线主机时,它在串行数据启动前驱动该信号为有效状态。

在数据发送出去之后又将该信号恢复为无效状态。

LCISP教程

教程:使用FlashMagic下载LCP1114LPC1114不像LPC1343一样,它没有USB Bootloader(引导区)(这并不奇怪,因为他没有USB)。

虽然你可以使用专用的硬件设备对其进行下载,如针对ARM的Segger J-Link或者很多支持ARM的Crossworks的硬件仿真器(如果你使用Corssworks),如果你没有硬件仿真器仍然可以使用由NXP支持的一款免费软件FlashMagic来对设备下载程序。

如果你已经使用SWD方式写入固件,FlashMagic也可以用来升级你的设备。

(例如,在启动后直接进入深度睡眠模式)几乎所有NXP的LPC系列内建ISP Bootloader来允许用户使用FlashMagic来升级Flash,只需对你的MCU和UART进行简单的连接。

在使用LPC1114评估板的情况下,你只需要设置ISP跳线,复位芯片,然后自动进入ISP模式。

这个唯一的硬件要求是一个廉价的3.3V逻辑电平的UART,例如使用USB2COM接口板作为一个例子,到LPC1114到接口板的连接如下:连接USB2COM到LPC1114评估板USB2COM接口板LPC1114GND GNDRXD TXDTXD RXD设置UART的注意事项:如果你不知道USB转UART的串口波特率和COM端口号,你可以进入Windows设备管理器,查看设备的属性窗口,在Port(COM&LPT)选项里,在“端口设置”标签可以找到和修改相关的信息。

,我们建议,波特率至少设置57600,因为他默认的设置是一个相对缓慢的9600波特率。

步骤一:进入ISP模式1.连接UART转接板到LPC1114,如上面表格列出2.设置ISP跳线3.按复位按键并释放来复位开发板步骤二:配置Flashmagic1.开始FlashMagic2.点击“Select Device…”按钮,并从弹出的窗口选择相应设备,在这里我们使用LPC1114开发板,我们选择LPC1114/3013.设置波特率,COM口和晶振频率(在这里选择12.0M)4.选择”Erase blocks used by Hex file”复选框5.当你创建工程用”Browse”按钮来选择fimemare.hex文件创建的地址,这是一个编译后要写入设备Flash的代码。

LPC1114-LPC11U14和LPC1343对比学习(七)SSP

LPC1114/LPC11U14和LPC1343对比学习(七)SSPLPC1114 和LPC11U14 有两路SSP 总线,而LPC1343 只有一路SSP 总线,其他没有太大的区别,不过LPC11U14 的SSP1 总线都有两路管脚可以设置,进一步增加了芯片的灵活性。

三种芯片的SSP 总线初始化基本一致:但是需要注意,LPC1114 和LPC1343 的SSP0 总线,再设置好时钟后,还必须选择时钟的输出引脚,LPC_IOCON->SCK_LOC = SSP0_SCK_SELECT;而LPC1114 的SSP1 总线和LPC11U14 的两路SSP 总线则不需要这样设置。

对于LPC1114 的SSP1 总线可以理解,因为没有管脚映射。

但是LPC11U14 却有管脚映射功能,如果没有此寄存器,如果多个管脚都设置成同一的功能,真不知道会出现什么样的效果。

就是能正常工作,感觉程序没有以前那样严谨了,不知道NXP 为什么会这样设计对于SSP 总线,需要知道主从设置的主要区别,在主模式下器件的片选管脚可以随意设定而不一定要总线的NSS 管脚,而且就算使用此管脚也要设置成普通GPIO 端口,通过程序控制器件片选。

但是在从模式下从机管脚必须使用总线的NSS。

在使用SSP 总线来控制SD 卡时,SD 卡的初始化必须要尽量降低SSP 总线速度,一般在400K 以下比较安全,如果不想降低SSP 总线速度,那就必须在初始化函数中添加延时来降低速度,保证SD 卡初始化成功。

之后就可以加快SSP 总线速度,提高SD 卡读写速度。

tips:感谢大家的阅读,本文由我司收集整编。

仅供参阅!。

嵌入式微控制器 LPC1114FHN33 LPC1114 资料

NXP 50-MHz, 32-bitCortex-M0™ microcontrollers LPC1100Built around the new Cortex-M0 architecture, the smallest, lowest power, and most energy-efficient ARM core ever developed, these MCUs are ideally equipped for use in many traditional 8/16-bit applications.} Analog peripheral - 10-bit Analog-to-Digital Converter with eight channels and conversion rates up to 400 K samples per second } Other :- U p to 42 general-purpose I/O (GPIO) pins with configurable pull-up/down resistors and a new, configurable open-drain operating mode - F our general-purpose counter/timers, with a total of four capture inputs and 13 match outputs- Programmable Watchdog Timer (WDT) with lock-out feature - System tick timer- Each peripheral has its own clock divider for power savings Applications } White goods } e-Metering} Consumer peripherals } Remote sensors} 8/16-bit applications } Industrial networking } System supervisorsKey features} ARM Cortex-M0 processor - 50 MHz operation - N ested Vectored Interrupt Controller for fast deterministic interrupts - W akeup Interrupt Controller allows automatic wake from a priority interrupt - T hree reduced-power modes: Sleep, Deep-sleep, and Deep power-down } Memories- Up to 128 KB Flash memory - Up to 16 KB SRAM } Serial peripherals - U ART with fractional baud rate generation, internal FIFO, and RS-485 support - U p to 2 SPI controllers with FIFO and multi-protocol capabilities - I 2C-bus interface supporting full I 2C-bus specification and Fast mode plus with a data rate of 1 Mbit/s with multiple address recognition and monitor modeDate of release: January 2010Document order number : 9397 750 16865Printed in the Netherlands© 2010 NXP B.V.All rights reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.LPC1100 block diagramNXP’s LPC1100 is the lowest-priced 32-bit MCU solution in the market. It offers greater value than existing 8/16-bit microcontroller by delivering unprecedented performance, simplicity, low power, and dramatic reductions in code size for every application.With over 45 DMIPS of performance compared to thesub-DMIP performance typical of 8-bit MCUs and 3 to 5 DMIPS for 16-bit MCUs, the LPC1100 not only execute basic control tasks but sophisticated algorithms as well, making even the most complex tasks within reach. Using less time to do more tasks translates directly into lower energy consumption.This level of performance is delivered at 50 MHz, with extensive power optimization, at less than 10 mA.Challenging the belief that 8/16-bit microcontrollers use less code, industry-standard Coremark benchmarks show that the LPC1100 requires 40-50% less code for most common microcontroller tasks. Development toolsThe LPC1100 family is supported by the LPCXpresso , an easy to use, comprehensive development tool platform for under US$30, as well as development tools from IAR, Keil, Hitex, Code Red, and many others. For the most current listing, please visit /microcontrollers.Additional features} Serial Wire Debug (4 breakpoints)} High-current output driver (20 mA) on one pin } High-current sink drivers (20 mA) on two pins} Integrated PMU (Power Management Unit) to minimize power consumption during Sleep, Deep-sleep, and Deep power-down modes} Single 3.3 V power supply (1.8 to 3.6 V)} Over 5 kV ESD for rugged applications} 13 GPIO pins can be used as edge and level sensitive interrupt sources} Clock generation unit with divider that can reflect the main oscillator clock, IRC clock, CPU clock, and Watchdog clock.} Processor wake-up from Deep-sleep mode via interrupts from various peripherals} Brownout detect with four separate thresholds for interrupt and forced reset} Power-On Reset (POR)} Crystal oscillator with an operating range of 1 MHz to 25 MHz } 12 MHz internal RC oscillator trimmed to 1% accuracy that can also be used as a system clock} PLL allows CPU operation up to the maximum CPU rate without the need for a high-frequency crystal. Can be run run from the main oscillator, the internal RC oscillator, or the Watchdog oscillator.} Available in 48-pin LQFP , 33-pin HVQFN, or 44-pin PLCC packageLPC111x ordering options。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

h u t.e d u.c n1.如何阅读本章所有LPC111x系列中的SPI模块均相同。

第二个SPI模块,SPI1,只存在于LQFP48和PLCC44封装上,在HVQFN33封装上则没有。

注释:两个SPI模块都包含全部的SSP特征集,所有相关寄存器都使用SSP前缀命名。

2.特性•兼容Motorola SPI、4线TI SSI和美国国家半导体公司的Microwire总线。

•同步串行通信。

•支持主机和从机操作。

•收发均有8帧FIFO。

•每帧有4-16位数据。

3.基本描述SPI/SSP是一个同步串行端口(SSP)控制器,可控制SPI、4线SSI和Microwire总线。

它可以与总线上的多个主机和从机相互作用。

在数据传输过程中,总线上只能有一个主机与一个从机进行通信。

原则上数据传输是全双工的,4~16位帧的数据由主机发送到从机或由从机发送到主机。

但实际上,大多数情况下只有一个方向上的数据流包含有意义的数据。

LPC111x系列处理器有两个SPI/同步串行端口控制器。

u p.wu p .wh ut.ed u.c n4.引脚描述表161622.SPI引脚描述SCK0/1I/O SCK CLK SK串行时钟。

SCK/CLK/SK是用来同步数据传输的时钟信号。

它由主机驱动,从机接收。

当使用SPI接口时,时钟可编程为高电平有效或低电平有效,否则总是高电平有效。

SCK仅在数据传输过程中切换。

在其它时间里,SPI/SSP接口保持无效状态或不驱动它(使其处于高阻态)。

SSEL0/1I/O SSEL FS CS帧同步/从机选择。

当SPI/SSP接口是总线主机时,它在串行数据启动前驱动该信号为有效状态。

在数据发送出去之后又将该信号恢复为无效状态。

该信号的有效状态根据所选的总线和模式可以是高或低。

当SPI/SSP接口作为总线从机时,该信号根据使用的协议来判断主机数据的存在。

当只有一个总线主机和一个总线从机时,来至主机的帧同步信号或从机选择信号直接与从机相应的输入相连。

当总线上接有多个从机时,需要管理好这些从机的帧选择/从机选择输入,以免一次传输有多个从机响应。

MISO0/1I/O MISO DR(M)DX(S) MOSI0/1I/O MOSI DX(M)DR(S)SI(M)SO(S)SO(M)SI(S)主机输入从机输出。

MISO信号线从从机传送串行数据传送到主机。

当SPI/SSP作为从机,串行数据从该信号输出。

当SPI/SSP作为主机,从该信号得到串行数据时钟。

当SPI/SSP作为从机但未被FS/SSEL选定,它不会驱动该信号(保持高阻态)。

主机输出从机输入。

MOSI信号线从主机传送串行数据到从机。

当SPI/SSP作为主机,串行数据从该信号输出。

当SPI/SSP作为从机,从该信号得到串行数据时钟。

注释:SCK0功能在三个不同的引脚上复用(在HVQFN封装上有两个引脚)。

通过设置IOCON_LOC寄存器(见7–4.2小节)选择一个引脚作为SCK0功能,另外在IOCON寄存器中设置功能。

SCK1引脚没有复用。

up .w hu t.e d u.n 5.时钟和功耗管理SPI 模块由AHBCLKCTRL 寄存器(见表3–19)控制。

用于SPI 时钟分频器和预分频器的SPI 外设时钟,由SSP0/1CLKDIV 寄存器(见3–4.15小节)控制。

可以通过设置SSP0/1CLKDIV 寄存器(见3–4.15小节)来禁止SPI0/1_PCLK 时钟。

SPI 模块可以通过设置AHBCLKCTRL 寄存器禁止(表3–19)以节省功耗。

6.寄存器描述SPI 控制器寄存器地址如表11–163和表11–164所示。

注释:使用SSP 前缀的寄存器名称,表示SPI 控制器完全兼容SSP 功能。

[1]复位值仅指已使用位中的数据,不包括保留位的内容。

表164.寄存器概览:SPI1(基址0x 404000580080000)控制寄存器0。

选择串行时钟频率,总线类型和数据长度。

SSP0CR1R/W 0x004控制寄存器1。

选择主机/从机和其他模式。

0SSP0DR R/W 0x008数据寄存器。

写满将发送FIFO ,读空将接收FIFO 。

0SSP0SR RO 0x00C 状态寄存器。

-SSP0CPSR R/W 0x010时钟预分频寄存器。

0SSP0IMSC R/W 0x014中断屏蔽设置和清零寄存器。

0SSP0RIS R/W 0x018原始中断状态寄存器。

-SSP0MIS R/W 0x01C 屏蔽中断状态寄存器。

0SSP0ICRR/W0x020SSPICR 中断清零寄存器。

NA控制寄存器0。

选择串行时钟频率,总线类型和数据长度。

SSP1CR1R/W 0x004控制寄存器1。

选择主机/从机和其他模式。

0SSP1DRR/W 0x008数据寄存器。

写满将发送FIFO ,读空将接收FIFO 。

0SSP1SR RO0x00C 状态寄存器。

-SSP1CPSR R/W 0x010时钟预分频寄存器。

0SSP1IMSC R/W0x014中断屏蔽设置和清零寄存器。

0SSP1RIS R/W 0x018原始中断状态寄存器。

-SSP1MIS R/W 0x01C 屏蔽中断状态寄存器。

0SSP1ICRR/W0x020SSPICR 中断清零寄存器。

NAu p .wh ut.ed u.c n[1]复位值仅指已使用位中的数据,不包括保留位的内容。

6.1SPI/SSP控制寄存器0该寄存器控制SPI/SSP控制器的基本操作。

表165:SPI/SSP控制0(SSP0CR0-address0x40040000,SSP1CR0-address3:0DSS数据长度选择。

该字段控制着每帧传输的位数目。

不支持且不使用值0000-0010。

000000114-位传输1005-位传输1016-位传输1107-位传输1118-位传输0009-位传输00110-位传输01011-位传输01112-位传输10013-位传输10114-位传输11015-位传输11116-位传输FRF帧格式0000SPITIMicrowire1不支持且不应使用这个组合。

CPOL时钟输出极性。

该位只用于SPI模式。

00SPI控制器使总线时钟在两帧传输之间保持低电平。

SPI控制器使总线时钟在两帧传输之间保持高电平。

CPHA时钟输出相位。

该位只用于SPI模式。

00SPI控制器在帧传输的第一个时钟跳变沿捕获串行数据,也就是说,传输远离时钟线的帧间状态。

SPI控制器在帧传输的第二个时钟跳变沿捕获串行数据,也就是说,传输紧邻时钟线的帧间状态。

5:8SCR串行时钟频率。

SCR之值为总线上每传输一个数据位所对应的预分频时钟数减1。

假设CPSDVSR为预分频器的分频值,APB时钟PCLK为预分频器的时钟,则位频率为PCLK/(CPSDVSR×[SCR+1])。

0x00uhu t.e d u.cn 6.2SPI/SSP0控制寄存器1该寄存器控制着SPI/SSP 控制器的工作方式的某些方面。

表166:SPI/SSP 控制寄存器1(SSP0(SSP0C C R1–地址0x 404000400000044,SS SSPP 1CR1–地址6.3SPI/SSP 数据寄存器软件可将要发送的数据写入该寄存器,或从该寄存器读出接收到的数据。

表167:SPI/SSP 数据寄存器(S SP SP00DR –地址0x40x400040008,SSP1SSP1DD R –地址回环模式0正常操作模式串行输入脚同时也是串行输出脚(MOSI 或MISO ),而不是仅作为串行输入脚(MISO 或MOSI 分别起作用)。

SSE允许SPI 。

0禁止SPI 控制器。

SPI 控制器可与串行总线上的其它器件相互通信。

在设置该位之前,软件应将合适的控制信息写入其它SPI/SSP 寄存器和中断控制器寄存器。

MS主机/从机模式。

该位只能在SSE 位为0时写入。

SPI 控制器作为总线主机,驱动SCLK 、MOSI 和SSEL 线并接收MISO 线。

SPI 控制器作为总线从机,驱动MISO 线并接收SCLK 、MOSI 和SSEL 线。

SOD从机输出禁止。

该位只与从机模式有关(MS=1)。

如果该位为1,将阻塞SSI 控制器驱动发送数据线(MISO )。

07:4-保留,用户软件不要向保留位写入1。

从保留位读出的值未定义。

NA要发送的帧数据写入该寄存器。

如果Tx FIFO 以前为空,且总线上的SPI 控制器不忙,则立刻开始发送数据。

否则,写入该寄存器的数据要等到所有数据发送(或接收)完后才能发送。

如果数据长度小于16位,软件必须对数据进行右对齐后再写入该寄存器。

读:当状态寄存器的RNE 位为1时,指示Rx FIFO 不为空,软件可读取该寄存器。

软件读取该寄存器时,SSP 控制器将返回Rx FIFO 中最早收到的一帧数据。

如果数据长度小于16位,该字段的数据必须进行右对齐,高位补零。

0x0000up .whu td u.cn 6.4SPI/SSP 状态寄存器该只读寄存器反映了SSP 控制器的当前状态。

表168:SPI/SSP 状态寄存器(S (SS S P 0SR –地址0x40x40004000000C,SSP1SR –地址0TFE 发送FIFO 空。

发送FIFO 为空时该位为1,反之为011TNF 发送FIFO 未满。

Tx FIFO 满时该位为0,反之为1。

12RNE 接收FIFO 非空。

接收FIFO 为空时该位为0,反之为1。

03RFF 接收FIFO 满。

接收FIFO 满时该位为1,反之为0。

04BSY 忙。

SPI 控制器空闲时该位为0,当前正在0发送/接收一帧数据和/或Tx FIFO 非空时该位为1。

7:5-保留。

用户软件不要向保留位写入1。

从保留位读出的值NA未定义。

6.5SPI/SSP 时钟预分频寄存器SPI_PCLK 到SPI 预分频器时钟的分频系数,由该寄存器控制。

换而言之,SSPCR0寄存器中SCR 系数,决定位时钟。

表169:SPI/SSP 时钟预分频寄存器(SSP0(SSP0C C P SR –地址0x40x400040000110,SSP1CPSR –地址0x4x400057:0CPSDVSR 这是2到254之间的一个偶数,SPI_PCLK 经分频后得到预分频器输出时钟。

位0读总是为0。

重要提示:必须正确初始化SSPnCPSR ,否则SPI 控制器将不可能正常发送数据。

在从机模式时,SPI 时钟频率由主机提供,不能超过3–4.15小节中选定的SPI 外设时钟频率的1/12。

寄存器SSPnCPSR 中的值与时钟频率无关。

主机模式,CPSDVSR min =2或更高(仅限偶数)。

6.6SPI/SSP 中断屏蔽设置/清除寄存器该寄存器控制SPI 控制器中4个可能的中断条件是否已经允许。