基于FPGA_DSP的高速基带信号处理平台的设计_谭左红

基于FPGA+DSP的高速基带信号处理平台的设计

第 3期

ห้องสมุดไป่ตู้

2 0 1 4年 1月

科

学

技

术

与

工

程

Vo 1 . 1 4 N o . 3 J a n .2 0 1 4

1 6 7 1 —1 8 1 5 ( 2 0 1 4 ) 0 3 — 0 2 3 9 — 0 5

S c i e n c e T e c h n o l o g y a n d E n g i n e e r i n g

出 了一种改进高速基 带信号处理平 台的硬件 设计方 案。该 方案采 用 F P G A+D S P的处理 架构 , 依托 高性 能 的器 件和 高速接 口, 搭建 了一个高性 能的通用 基带信号处理平 台。该平 台直接实现对 中频数 字信号 的处 理 , 融合数 字上 下变频 与基 带算法于

一

的处理器 , 其优势在于 : ①充分结合了 D S P和 F P G A 各 自的优点 , 更好地发挥 了性能 ; ②结构灵活、 通用 性强 、 适用 于模块化设计 ; ③对不同结构的算法都有 较强 的适应能力 , 尤其适合实时信号处理; ④算法执 行效 率高 、 开 发周 期短 、 系 统易 于维 护和 扩展 等 。 结合各类无线通信 系统实际算 法需求 , 低层信 号预处理算法的数据 为符号级数据 , 虽然数据量大 但运 算结 构 相对 比较 简单 , 适 于用 F P G A 进 行 硬 件 实现。高层处理算法的数据 为比特型数据 , 其特点

一

是数据量较少 , 但算法的控制结构复杂 , 适于用 D S P 来 实 现 。F P G A 具 有 明 显 的 并 行 处 理 优 势 和 灵 活 性, D S P运算 速度 快 、 寻址 方 式 灵 活 , 二 者 均 能 满 足 处 理 复 杂算 法 的要 求 , 这样以 F P G A +D S P的架 构 为核 心 , 借 助 于高性 能 的器件 和高 速接 口 , 设计 了一 个 高性 能 信 号 处 理 硬 件 平 台 J 。该 平 台具 有 灵 活 的处理 结构 , 对 不 同结 构 的算 法都 有 较 强 的适 应 能 力, 尤其适合实时信号的处理。

基于DSP和FPGA的通用数字信号处理系统设计

p e r f o r m d a t a p r o c e s s i n g a n d a c c o mp l i s h t h e c o n t r o l o f US B i n t e r f a c e,ADC ,DA C,e t c .r e s p e c t i v e l y .Th e s y s t e m c a n i m— p l e me n t s p e c t r a l a n a l y s i s ,d i g i t a l f i l t e r d e s i g n a n d o t h e r c l a s s i c d i g i t a l s i g n a l p r o c e s s i n g a l g o r i t h ms .Ha r d wa r e d e b u g r e —

Ab s t r a c t :I n n o wa d a y s ,t h e f u n c t i o n a n d s t r u c t u r e o f e l e c t r o n i c e q u i p me n t a r e b e c o mi n g i n c r e a s i n g l y c o mp l i c a t e d .Th e r e —

s u h s s u g g e s t t h a t i t me e t s t h e d e s i g n r e q u i r e me n t s , a n d c o u l d b e i mp l e me n t e d t o r e a l p r o j e c t a n d d i g i t a l s i g n a l p r o c e s s i n g

基于DSP_FPGA的高速数字信号处理平台

术,该平台还具有一定的开放性和可

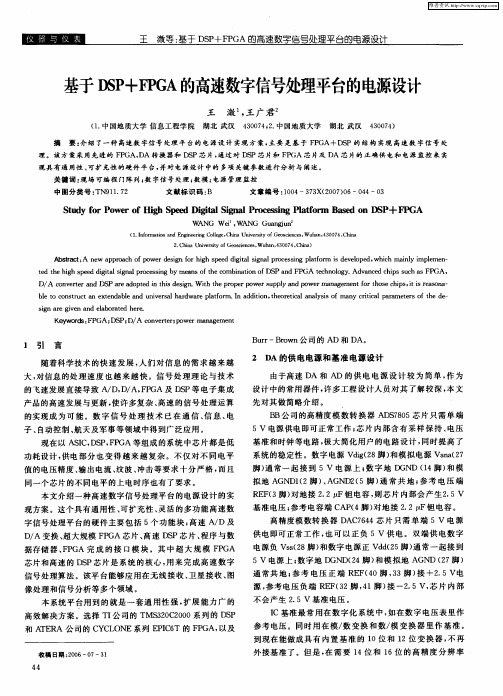

示意图与图2相似,只是核电压不同。

程序与数据存储器 F L A S H 采用 扩展性,可以很好地满足设计的完善、

由超大规模FPGA芯片和高速的DSP芯 Intel公司的E28F320,其存储容量为 功能的扩充及程序的更改。

片组成系统的核心,是为了发挥两者 32Mbit。由 DSP 的供电芯片TPS70348

图2 DSP芯片的供电示意图

表 1 FPGA 芯片与 DSP 芯片的比较

F P G A 芯片

编程方式

V H D L 、A H D L 语言及图形编程等,

实现容易

资源重复利用性

通过外部处理器动态配置

硬件资源结构

可实现并行的乘法器/加法器操作

处理速度

并行运算速度快,只受硬件结构限制

适合的信号处理运算 高速并行处理

的优势。FPGA 芯片与 DSP 芯片相比, 为其一起供电,TPS70348芯片的复位

系统的软件设计流程

由于其结构上的优势,FPGA芯片更适 信号 /RESET为 FLASH 和 DSP的共同复

本文设计的平台通过动态配置可

w w w . e e p w . c o m . c n 电子产品世界 2004.10 /下半月 91

式中:SNR为输出信号的信噪比; B 为比特分辨数,即A/D 的转换位数; 为采样速率;输入模拟信号的最高频

理技术已在通信、信息、电子、自动控

总体硬件框架

制、航天及军事等领域中得到广泛应

图1为本文要介绍

用。

的高速数字信号处理平

以现代通信理论为基础,以数字 台的硬件框图,主要包

信号处理为核心的软件无线电技术是 括五个功能块:高速A/

一种基于DSP和FPGA的实时信号处理平台设计

T 1 1是 A I 司推 出的一款 高性能浮点 D P处理器 . s0 D公 S 采用超级 哈佛结构 , 可直接构成 分布式并行 系统 和共享存储式并 行系统, 主要性 能 指 标 如 21 F1 : - 3 () 1内部核时钟频 率可达 30 z 即指令周 期为 33 s 内核 具有 双运算模 块——x和 Y, 条相互 独立 的 18 i内部数 3 2 bt 据 总线 ; () 3支持 81/26 bt /63/4 i 定点和 3 /4 i 26 bt 浮点数据格式 ; ()4 46 位数据线 和 3 位 地址线, 2 可提供4 G的统一寻址空 问; ()4 DMA通道 , 51 个 提供 了处理 核零开销数据传输 ; () 6支持 慢速 设 备和 流水 协议 两种 外设 访 问模式 , 芯片 内部 集成 SR D AM 控 制 器 ; ()通 道全双T链路 V , 74 I单个链路 V最大通信速率 20 ye/, I 5 MB ts 总 s

用到 雷 达 信 号 处 理 系统 中。

[ 关键词 ] 雷达信 号处理

O 引 言 .

DS T 11 F G P S 0 P A D P通过 F G S P A来进行 S M的读写控制 ; RA ()P 6F GA实现 处理板与外 部的通讯 和控制 , 如串 口 、 系统 状态输 出 及 控 制 输 入 、 出接 口 。 输 22 路 口 电路 设 计 .链

T 1 1物 理 引 脚 D P行 地 址 S0 S

A0

A1

21 .信号处理平 台原理框 图 信 号 处 理 板 硬 件 架 构 如 图 1 示 。信 号 处 理 平 台 采 用 A 所 D— s — s 0 为 主 处 理 芯 片 , 簇 4片 T 1 1 内 核 时 钟 3 0 P T l1 一 S0 , 0 MHz簇 总 线 速 , 度 为 7 M, 内包 含 2 6 yeS AM及 1MB t F A H。4片 A 5 簇 5 MB t DR 6 ye L S D— S — SIl P T 之间通过共享总线 的方式实现 紧耦合 。 O

基于FPGA+DSP的高速数据采集系统设计

基于FPGA+DSP的高速数据采集系统设计

杨永东;曾庆立

【期刊名称】《吉首大学学报(自然科学版)》

【年(卷),期】2009(030)004

【摘要】介绍了1种基于FPGA和DSP的高速数据采集系统的设计和实现,其FPGA采用Altera公司ACEX 1K系列的EPIK50TC144_3器件,DSP芯片采用TI 公司TMs320系列的TMS320C6713器件.该系统将A/D采样的数据送往FP-GA,经过FPGA预处理后送到DSP,最终通过USB接口送到主控台,其系统的数据采集的实时速度最高可达到100 MB/s,适用于大部分的高速数据采集场合.

【总页数】4页(P65-68)

【作者】杨永东;曾庆立

【作者单位】吉首大学物理科学与信息工程学院,湖南,吉首,416000;吉首大学物理科学与信息工程学院,湖南,吉首,416000

【正文语种】中文

【中图分类】TP29

【相关文献】

1.基于FPGA+DSP的USB高速数据采集系统设计与实现 [J], 李冬冬;吴玉斌;郝永平;王磊

2.基于FPGA+DSP弹载SAR信号处理系统设计 [J], 陈勇

3.基于FPGA+DSP的高速视频实时处理系统设计 [J], 张小永

4.基于FPGA+DSP的弹载组合导航系统设计 [J], 李炳臻;李杰;胡陈君;张泽宇;纪

志敏

5.基于FPGA+DSP的高速视频实时处理系统设计 [J], 张小永

因版权原因,仅展示原文概要,查看原文内容请购买。

5.7一种基于高性能dsp和fpga的drfm信号处理模块的设计与应用

5.DSP技术的开发应用1325.7一种基于高性能DSP和FPGA的DRFM信号处理模块的设计与应用李云杰张庆兴高梅国北京理工大学信息科学技术学院电子工程系北京10009l摘要;本文介绍了一种基于高性能DSP和FP(:A的DRFRI信号处理模块的设计方案,时谊模块的总体设计方案、主要电路单元设计、通用性设计和信号完整性设计等内容做了详细讨论.最后列举了谊DRFM信号处理模块的具休应用.关键词:FPGADSPDRFM一、引言数字射频储存器(DRFM)是现代电子干扰机的关键部件,它能高保真的存储和复制信号加上移频、时延等调制,产生高逼真度的欺骗信号,实现对威胁目标的欺骗干扰[1】。

传统的数字储频系统是在中频或基带进行信号采集存储的,处理带宽和处理能力均有限.随着半导体技术的飞速发展,AI)C和DAC的转换速率和精度不断提高,DSP和FPGA的信号处理能力越来越强。

这些高性能集成电路Ic的出现为更高速的DRFM信号处理模块的研制提供了保障。

本文的主要内容即是一种基于高性能DSP和FPGA的DRFM信号处理模块的设计和应用。

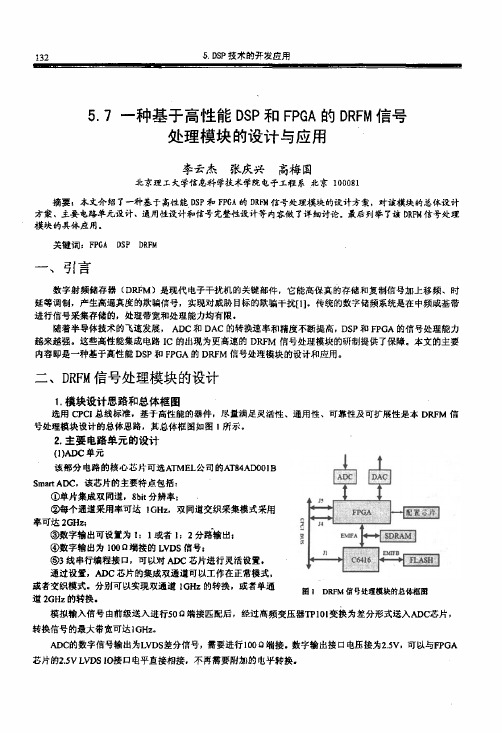

二、DRFM信号处理模块的设计1.模块设计思路和总体框图选用CPCI总线标准,基于高性能的器件.尽量满足灵括性、通用性、可靠性及可扩展性是本DRFM信号处理模块设计的总体思路.其总体框图如图I所示。

2.主要电路单元的设计(1)ADC单元该部分电踌的核心芯片可选ATMEL公司的AT84AD001BSmartADC.该芯片的主要特点包括:①单片集成双同道.8bit分辨率:@每个通道采用率可达1GHz,双同道交织采集模式采用率可达2GHz;③数字输出可设置为1:1或者1:2分路输出;④数字输出为100f/端接的LVDS信号#⑤3线串行编程接口,可以对ADC芯片进行灵活设置.通过设置,ADC芯片的熹成双通道可以工作在正常摸式,或者交织模辛i分别可以实现取通道1GHz的转换·或者单通圈lDRFM信号处理模块的总体框圉道2GHz的转换.模拟输入信号由前级送入进行500端接匹配后,经过高频变压器TPIOI变换为差分形式送入ADC芯片,转换信号的最大带宽可达lGHz。

基于FPGA的高速光纤通信基带板的设计_

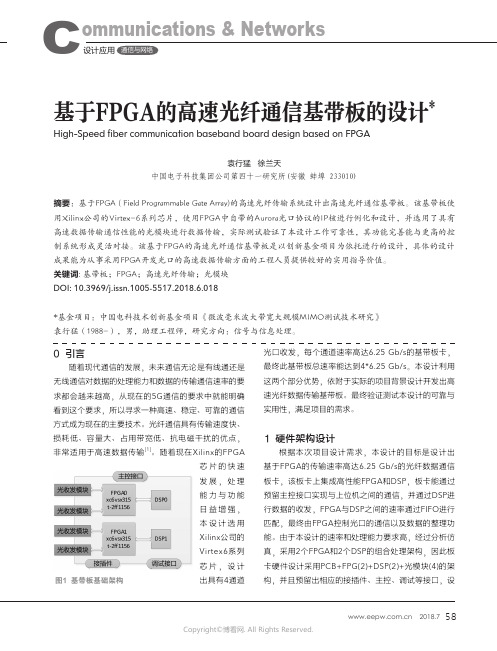

图1 基带板基础架构计的基础架构如图1所示,详细设计的架构如图2所示。

在板卡设计中选取的F P G A是X i l i n x公司的XC6VSX315T-2FF1156型号作为主控芯片用来控制光纤接口的主要功能,主要完成光收发模块的使能控制、光传输的链路管理以及数据的传输。

XC6VSX315T包含49200个Slices和25344 Block RAM,18个用户I/O,可以满足FPGA外围电路设计和后期扩展与增强功能的设计[2]。

设计中要求的光口传输速率是6.25 Gb/s,XC6VSX315T共有5组20个GTX数据收发接口,GTX通道的传输速率最快可达6.6 Gb/s,满足技术指标中的信号传输速率的要求[3]。

光收发模块选用标准的成熟光收发模块,该模块最高传输速度可达4*6.25 Gb/s。

整个板卡选用特定芯片完成主控与基带板之间的数据交互,从而来控制板卡的主要功能。

2 软件架构设计本次设计基于FPGA的高速光纤通信基带板卡时就块、数据控制与整理模块和Aurora 8B10B IP核的调用模块。

本次光口数据传输过程中使用的协议是Xilinx公司提供的一种免费的数据链路层协议——Aurora协议,该协议已经验证是稳定可靠的传输协议,已得到实际应用,该协议核内部封装了高速串行数据接口硬核,可编程逻辑器件通过绑定GTX通道进行数据的收发交互。

单个GTX通道的数据传输速率可达G bit级别,根据不同的需求可以实现多个通道的组合使用,从而可实现几十G bit,甚至上百G bit速率的数据传输。

因此,本次设计图2 基带板详细架构图3 FPGA功能实现代码lane又能实现数据的双工传输。

所以本设计中的Aurora 协议接口就在Xilinx公司的Virtex-6芯片上实现。

Aurora 8B/10B顶层模块例化了Aurora 8B/10B通道模块、TX和RX本地链路模块、全局逻辑模块以及GTP/GTX收发器。

基于DSP+FPGA的高速数字信号处理平台的电源设计

现 具有 通 用 性 、 可扩 充性 的硬 件 平 台 , 对 电 源设 计 中的 多项 关键 参 数 进 行 分析 与 阐述 。 并 关键 词 : 场 可 编程 门阵 列 ; 字 信号 处 理 ; 现 数 数模 ; 源 管理 监控 电 中 图分 类 号 : 9 17 TN 1 .2 文献 标 识 码 : B 文 章编 号 :0 4 7X(O7 O —04— 3 10 —33 2O )6 4 0

A ta t A e a pr a h o o rd sgn f ih s e d diia i n lp o e sn af r sde eo d, ih mail m pe e - bsr c : n w p o c fp we e i orhg p e gt lsg a r c s ig plto m i v lpe whc ny i lm n

( . no mai n n ie r g C l g , hn ie s yo e s i cs W u n 4 0 7 , i 1 Ifr t n a d E gn ei o l e C iaUnv ri fG o c n e , h ,3 0 4 Chn o n e t e a 2 Ch a Unv ri fG o c n e . u n 4 0 7 , hm ) . i ies yo e s i c s W h , 3 0 4 C n t e i

t h i h s e ii l in l r e sn y me n f h o i ai no S n P d e t ehg p e d gt g a p o s i b a so ec mb n t fD P a d F GA c n lg . v n e hp u h a GA, d as c g t o t h o o y Ad a c c i ss c s e d FP

FPGA与DSP的高速通信接口设计与实现

2.1链路口通信协议分析 Tsl01的链路口共有11根引脚,通过8根数据线

44

欢迎网上投稿www.aetnet.cn www.aetnet.com.cn

万方数据

《电子技术应用》2007年第4期

集成嘲瞳翔AppIicalIonof Integrated c㈣s

(kDAT[7..0],这里x可以是0、1、2或3,代表TSl01或 .Is201的0号一3号链路口中的一个,以下同)进行数据

知数据块传输的结束,

当能确定DMA传输数

据个数时,可以将此引

脚悬空。

TS201链路口的收

发机制非常相似,本文

图3 FPGA接收‘rSl01数据时序图

仅给出发送数据时序图,如图5所

2.3基于FPGA的TS201链路口设计 图4给出了FPGA与TS20l进行链路口通信的设计

框图。由于TS201的握手信号较多,所以相对TSl01的 链路口设计容易些。本设计FPGA时钟50MHz,TSlol核 时钟500MHz,链路口时钟为DSP核时钟的4分频,采用 4bit方式,单向实际数据传输速率为125MBps。

1 TSl01和TS201的链路口分析与比较 TSl01和TS210都是高性能的浮点处理芯片,目前两

来越广泛。ADI公司的TigerSHARC系列DSP芯片浮点 处理性能优越,故基于这类DSP的DSP+FPGA处理系

者都广泛应用于复杂的信号处理领域。rIs201是继rI’S101 之后推出的新型芯片,核时钟最高可达600MHz,其各类

7IS201

4个完全双向的链路口 通过SoC BUS接到片内SoC接口,

映射到存储区 24根引脚

16根LVDS数据线 时钟双沿触发的lbit,4bitDDR数据

结合FPGA与DSP实现对高速中频采样信号处理平台的设计详解

结合FPGA与DSP实现对高速中频采样信号处理平台的设计详解现代社会正向数字化、信息化方向高速发展,在这一过程中,往往需要高速信号的实时性数字化处理。

例如,随着科技的进步,现代雷达等应用信号的数字化处理上有了长足的发展,但也带来了新的问题,这些应用的数字信号处理具有海量运行需求的应用背景,如巡航导弹末制导雷达地形匹配、合成孔径雷达的成像处理、相控阵雷达的时空二维滤波处理等领域。

目前,单片DSP难以胜任许多信号处理系统的要求。

而常见的解决方案也是高速A/D采样与信号处理功能是在多块不同的板卡上实现,这给实际应用带来很多不便。

鉴于上述现有技术所存在的问题,本设计平台的目的是:

(1)实现高速中频信号(如雷达信号)的数字化处理并进行实时传输数据或进行数据的实时计算,并能通过输出电路进行结果显示;

(2)自定义控制总线可以实现对高速中频信号处理板进行灵活控制,具有较强的可配置性和丰富的灵活性;

(3)高速A/D采样与D/A回放及数据处理单元集成在一块板上,在集成度高的同时也降低了高速信号在传输过程中出现差错的概率。

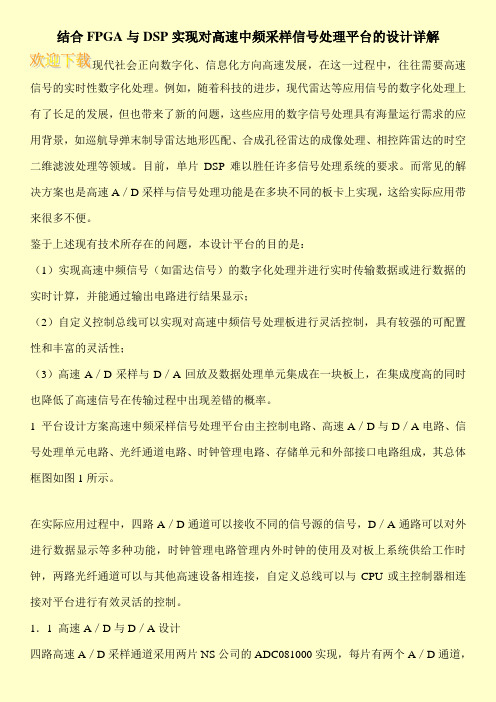

1 平台设计方案高速中频采样信号处理平台由主控制电路、高速A/D与D/A电路、信号处理单元电路、光纤通道电路、时钟管理电路、存储单元和外部接口电路组成,其总体框图如图1所示。

在实际应用过程中,四路A/D通道可以接收不同的信号源的信号,D/A通路可以对外进行数据显示等多种功能,时钟管理电路管理内外时钟的使用及对板上系统供给工作时钟,两路光纤通道可以与其他高速设备相连接,自定义总线可以与CPU或主控制器相连接对平台进行有效灵活的控制。

1.1 高速A/D与D/A设计

四路高速A/D采样通道采用两片NS公司的ADC081000实现,每片有两个A/D通道,。

基于DSP和FPGA的通用数字信号处理系统设计

基于DSP和FPGA的通用数字信号处理系统设计作者:孙靖舒来源:《电脑知识与技术》2020年第20期摘要:随着科学技术的不断发展,如今社会对于电子设备的结构与功能要求也在日益提升。

为此,该文将设计出一种体积小、能耗低的通用数字信号处理系统,并在系统中采用FPGA为系统的硬件加工,以DSP为数字处理核心,最终对其他硬件没备进行有效控制。

关键词:DSP;FPDA;通用数字信号处理;系统设计中图分类号:TP311文献标识码:A文章编号:1009-3044(2020)20-0221-02随着信息技术和电子技术的不断发展,如今数字信号处理已经被广泛地运用到各行各业中,并发挥出良好的应用效果。

但随着人们对于电子设备功能需求的日益增加,如今电子没备的结構也越来越复杂,其不仅极大地增加电子设备的体积和运行能耗,还有可能影响到没备的实际运行效果。

为此,本文将没计出一种能耗低,体积小的通用数字信号处理系统,以期能够为业内人士提供理论参考。

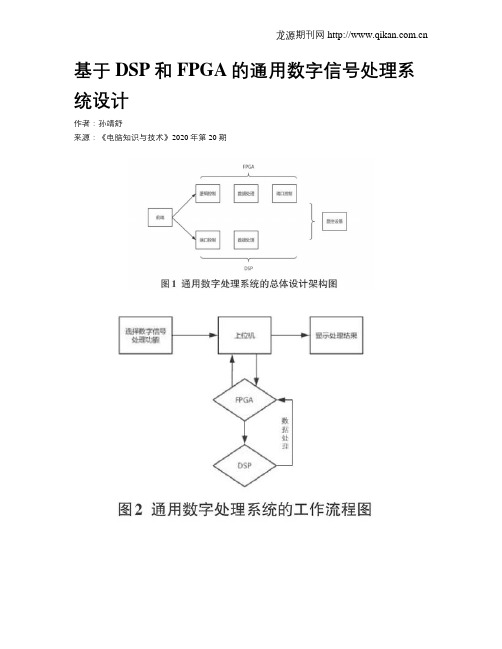

1系统总体设计本文所没计的基于DSP和FPGA的通用数字信号处理系统,其实际总体没计架构如图1所示。

整个系统有前端、FPGA、DSP以及显控设备四部分共同组成,其中前端设备在系统中用于数字模拟信号的输工作;FPGA则是用于控制ADC和DAC部分,其中ADC主要是对前端所输出的信号进行数据采集、滤波、变频、抽取、处理以及对系统外部端口电路进行实时逻辑控制,而DAC则是负责与DSP接口相互连接,然后通过输出基带信号来对DSP部分进行逻辑控制;DSP部分是本系统设计中数字核心处理部分,该部分是本系统没计中的核心部分主要负责通过核心算法对FPGA所传递出的模拟信号进行进一步的分析和处理,并在处理完成后,得到的数据传递给显控没备进行实际显示。

在实际运行过程中,本文所没计的通用数字处理系统的工作流程如图2所示。

操作者可以通过上位机的人机交互界面来选择实际数字信号处理功能,并通过USB接口来将上位机的控制命令传递给FPGA,之后FPGA又会将命令指令传递给DSP,DSP将会根据上位机所发布的指令来对数据进行实际处理,并在完成处理后,将经过处理的数据传回给FPGA,最终FP-GA 则又会通过USB接口将处理后的数据传递给上位机,再由上位机的显示程序和人机交互界面进行显示[1]。

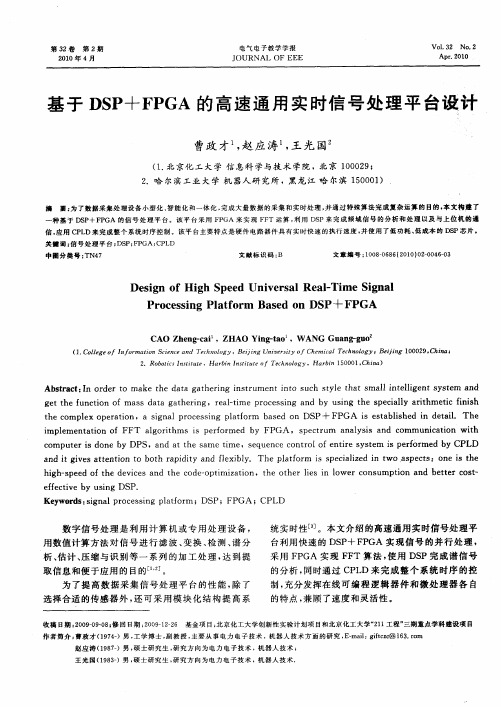

基于DSP+FPGA的高速通用实时信号处理平台设计

c mp tri d n y DP o u e s o eb S,a da h a i e e u n ec n r l fe tr y tm sp r r d b PL n tt es met m ,s q e c o to n ies se i e{ me y C D o 0

第 3 2卷

第 2期

电气 电 子 教学 学 报 J 0URNAL 0F EE E

Vo J 2 NO 2 l3 .

Ap . 01 r2 0

21 0 0年 4月

基 于 DS +F G 的 高速通 用 实 时信 号处 理 平 台设计 P P A

曹政 才 , 应 涛 王光 国 赵 ,

h g — p e ft e d v c s a d t e c d — p i z t n,t e o h r l s i o r c n u t n a d b t e o t i h s e d o h e ie n h o e o tmia i o h t e i n l we o s mp i n e t r c s- e o e f c i e b sn P. fe t y u i g DS v

De i n o i h S e d Un v r a a — m e S g l s g fH g p e i e s lRe lTi i na

P o e sn lto m a e n DS r c si g P a f r B s d o P+ F PGA

i p e e t to f F T l o ih s i p ro me y FP m lm n a i n o F a g rt m s e f r d b GA , s e t u a a y i a d c mmu ia in wih p c r m n l ss n o nct t o

一种基于DSP+FPGA的程序在线升级方法及系统[发明专利]

![一种基于DSP+FPGA的程序在线升级方法及系统[发明专利]](https://img.taocdn.com/s3/m/da890d36cd1755270722192e453610661ed95afb.png)

(19)中华人民共和国国家知识产权局(12)发明专利申请(10)申请公布号 (43)申请公布日 (21)申请号 202010346578.8(22)申请日 2020.04.27(71)申请人 湖北三江航天红峰控制有限公司地址 432000 湖北省孝感市北京路特8号(72)发明人 潘玥 郑磊 潘静 (74)专利代理机构 武汉东喻专利代理事务所(普通合伙) 42224代理人 李佑宏(51)Int.Cl.G06F 8/654(2018.01)G06F 5/06(2006.01)(54)发明名称一种基于DSP+FPGA的程序在线升级方法及系统(57)摘要本发明公开了一种基于DSP+FPGA的程序在线升级方法及系统,其中上位机配套软件解析DSP在线升级固件信息,依据预设的通讯协议将在线升级数据和在线升级指令发送给FPGA,FPGA将在线升级数据和在线升级指令通过FIFO传输至DSP;DSP读取并解析FIFO的缓存数据,将解析后的在线升级数据缓存于可读写存储单元;DSP依据解析后的在线升级指令获取所述可读写存储单元的升级数据,以实现待升级硬件设备的在线升级操作,从而提高了程序运行速率,节省了DSP处理器资源,保障程序升级的正确率与可靠性。

权利要求书2页 说明书5页 附图1页CN 111506335 A 2020.08.07C N 111506335A1.一种基于DSP+FPGA的程序在线升级方法,其特征在于,该方法包括如下步骤:上位机获取DSP在线升级固件信息,并依据预设的通讯协议将在线升级数据和在线升级指令发送给FPGA,FPGA将在线升级数据和在线升级指令通过FIFO传输至DSP;DSP读取并解析FIFO的缓存数据,将解析后的在线升级数据缓存于可读写存储单元;所述DSP依据解析后的在线升级指令获取所述可读写存储单元的升级数据,载入非易失性存储单元以实现待升级硬件设备的在线升级操作。

2.根据权利要求1所述的一种基于DSP+FPGA的程序在线升级方法,其特征在于,所述DSP依据解析后的在线升级指令获取所述可读写存储单元的升级数据具体为:所述DSP将解析后的在线升级数据存储于可读写存储单元,DSP的用户程序依据解析后的在线升级指令调用程序升级功能静态库,以获取在线升级数据。

基于DSP-FPGA的超高速跳频系统基带设计

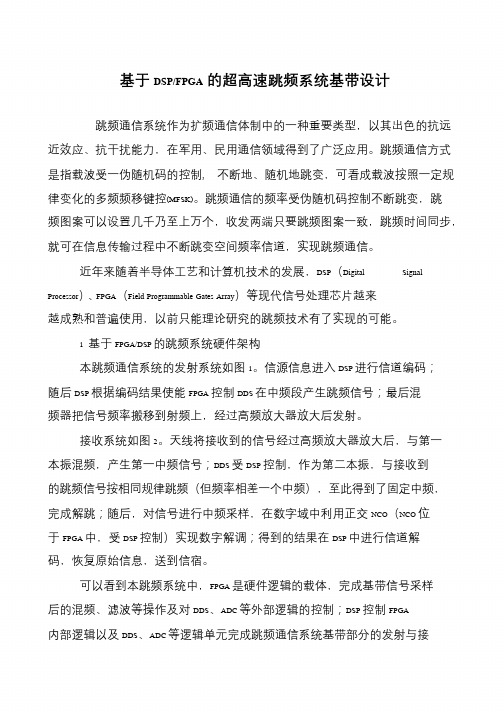

基于DSP/FPGA的超高速跳频系统基带设计跳频通信系统作为扩频通信体制中的一种重要类型,以其出色的抗远近效应、抗干扰能力,在军用、民用通信领域得到了广泛应用。

跳频通信方式是指载波受一伪随机码的控制, 不断地、随机地跳变,可看成载波按照一定规律变化的多频频移键控(MFSK)。

跳频通信的频率受伪随机码控制不断跳变,跳频图案可以设置几千乃至上万个,收发两端只要跳频图案一致,跳频时间同步,就可在信息传输过程中不断跳变空间频率信道,实现跳频通信。

近年来随着半导体工艺和计算机技术的发展,DSP(Digital Signal Processor)、FPGA(Field Programmable Gates Array)等现代信号处理芯片越来越成熟和普遍使用,以前只能理论研究的跳频技术有了实现的可能。

1 基于FPGA/DSP 的跳频系统硬件架构本跳频通信系统的发射系统如图1。

信源信息进入DSP 进行信道编码;随后DSP 根据编码结果使能FPGA 控制DDS 在中频段产生跳频信号;最后混频器把信号频率搬移到射频上,经过高频放大器放大后发射。

接收系统如图2。

天线将接收到的信号经过高频放大器放大后,与第一本振混频,产生第一中频信号;DDS 受DSP 控制,作为第二本振,与接收到的跳频信号按相同规律跳频(但频率相差一个中频),至此得到了固定中频,完成解跳;随后,对信号进行中频采样,在数字域中利用正交NCO(NCO 位于FPGA 中,受DSP 控制)实现数字解调;得到的结果在DSP 中进行信道解码,恢复原始信息,送到信宿。

可以看到本跳频系统中,FPGA 是硬件逻辑的载体,完成基带信号采样后的混频、滤波等操作及对DDS、ADC 等外部逻辑的控制;DSP 控制FPGA内部逻辑以及DDS、ADC 等逻辑单元完成跳频通信系统基带部分的发射与接。

基于DSP和FPGA的信号处理平台

基于DSP和FPGA的信号处理平台

王延昭

【期刊名称】《数字通信世界》

【年(卷),期】2008(000)005

【摘要】本文介绍了一种基于DSP和FPGA高速数字信号处理平台的实现方案,草点研究了试验平台的硬件实现结构,软件实现结构以及不同模式之间的切换,充分体现了软件无线电系统的灵活性,开放性和兼容性的特点.

【总页数】3页(P46-48)

【作者】王延昭

【作者单位】西安电子科技大学信息科学研究所

【正文语种】中文

【中图分类】TN91

【相关文献】

1.一种基于DSP和FPGA的实时信号处理平台设计 [J], 梁之勇;竺红伟

2.一种基于DSP+FPGA架构的InSAR实时信号处理平台设计 [J], 王光;索志勇

3.基于DSP+FPGA的高速通用实时信号处理平台设计 [J], 曹政才;赵应涛;王光国

4.基于FPGA+DSP的高速中频采样信号处理平台的实现 [J], 苏永芝;耿玉玲

5.基于FPGA+DSP的高速基带信号处理平台的设计 [J], 谭左红;田增山

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

科学技术与工程

Science Technology and Engineering

Vol. 14 No. 3 Jan. 2014 2014 Sci. Tech. Engrg.

基于 FPGA + DSP 的高速基带信号 处理平台的设计

2) FPGA 选型: 作为处理平台的协处理器,不仅 要求所选 FPGA 具有丰富的内部逻辑资源,而且需 要足够多的 I / O 口来完成信号的转接和通信任务。 结 合 需 求,本 设 计 中 选 择 ALTERA 公 司 的 EP4SGX230KF40C4 这款 FPGA 芯片。它是一款高 性能超大规模可编程逻辑器件,具有成熟的收发器 和存储器接口技术,其内部包含 182 400 个 Combinational ALUTs,13. 9 Mb RAM 以及 1 288 个嵌入式 乘法器,硬件资源十分丰富,适合复杂算法及高速信 号处理等对器件性能要求较高的场合[6]。 2. 2 FPGA 和射频板接口设计

谭左红 田增山

( 重庆邮电大学无线定位与空间测量研究所,重庆 400065)

摘 要 针对目前无线通信系统基带信号处理平台功能单一、灵活性差、运算能力弱等问题,在传统处理器架构的基础上提

出了一种改进高速基带信号处理平台的硬件设计方案。该方案采用 FPGA + DSP 的处理架构,依托高性能的器件和高速接

文献标志码 A

目前软件无线电发展迅速,基带信号处理作为 软件无线电的关键技术之一备受青睐。高速基带处 理平台是软件无线电的基础,系统在此完成信号的 调制解调、比特流处理、扩频和解扩、上 / 下变频和控 制等功能,以满足不同无线通信系统对数字信号处 理运算速度和运算量的要求。高速数字信号处理器 是基带处理平台的核心,基于目前的硬件水平,国内 外基带处理器常用的数字信号处理器有 DSP、FPGA、ARM、ASIC 等,它们均有各自的优点和不足,单 一的处理器都无法较好地满足软件无线电对于高速 基带处理平台的要求,目前主流的设计中均采用两 种或以上的处理器的组合[1]。因此,本设计中采用 FPGA + DSP 的架构作为数字信号处理器,相比单一 的处理器,其优势在于: ①充分结合了 DSP 和 FPGA 各自的优点,更好地发挥了性能; ②结构灵活、通用 性强、适用于模块化设计; ③对不同结构的算法都有 较强的适应能力,尤其适合实时信号处理; ④算法执 行效率高、开发周期短、系统易于维护和扩展等。

FPGA 是基带处理平台和射频前端衔接的主要 器件,不仅肩负着数字上下变频和数据预处理任务, 还需完成对高速数据的接收、缓存以及控制命令的 收发。对于接收通道,FPGA 通过高速并行接口接 收 A / D 转化后的数据,先对数据进行下变频到基 带,包括 NCO、滤波、抽取和频点选择等,然后根据 需要对基带数据进行预处理,如信号同步、相关等。 对于发射通道,FPGA 先将从 DSP 过来的数据进行 预处理,然后上变频到中频,再送到前端 D / A 传输

理完成的数据最终经以太网口传到上位机的显示控 制界面。

2 硬件平台的详细设计

2. 1 关键器件选型 高速的数字信号处理器是整个硬件平台的关

键,主要是对 DSP 和 FPGA 芯片的选择。 1) DSP 选型: DSP 是基带算法处理的核心,选型

非常关键,在选择 DSP 芯片之前,需要对基带信号 处理单元的需求进行详细分析。以目前数据传输速 率最快的 LTE 系统为例,LTE 在 20 MHz 频谱带宽 能够提供下行 100 Mb / s、上行 50 Mb / s 的峰值速率, 按照最高的 100 Mb / s 来计算,则每 10 ms 帧所要处 理的 最 大 数 据 量 为 1 Mb。根 据 3GPP TS 36. 211 V9. 1. 0 规定的下行数据基带处理流程,并按固定位 置复用的方式进行处理,每个数据比特须经过最多 10 个环节的处理过程,估算平均每环节上每比特的 处理要求 8 条指令,则 10 ms 内必须完成的处理指 令数是: 1 000 000 × 10 × 8 = 80 000 000 条,对应的 处理能力要求是 8 000 MIPS( MIPS 表示每秒百万指 令) [4]。考虑到其他指令的处理,则整个基带数据 处理的需求应不小于 9 000 MIPS。根据以上需求分 析,从系统的灵活性和成本等角度出发,选择了 TI 公司的 TMS320C6455 定点数字信号处理器,其最高 工作频率为 1. 2 GHz,有高达 9 600 MIPS 的峰值定 点运算能力[5]。除了接口资源十分丰富外,其内部 有增强型第二代卷积译码协处理器( VCP2) 和增强 型第二代 Turbo 译码协处理器( TCP2) ,能极大提高 系统的性能,可高效执行通信系统的多种相关核心 信号处理算法。

根据需求,FPGA 和射频板之间的接口速率应 不低于 1 Gb / s,这对连接器的要求较高,本设计中 选用的是一种高速差分 HSMC 连接器。一个 HSMC 连接器包括有 3 种传输线: 16 对的高速 RapidIO 收 发器,最 大 速 率 能 达 到 6. 25 Gb / s; 52 对 高 速 的

图 2 FPGA 与 DSP 连接图

除了 EMIF 接口外,还可以选用 Serial RapidIO 接口,它是一种高速串行接口,在物理层采用串行差 分模拟信号传输的 RapidIO 标准,能提供高达 3. 125 Gb / s 的传输速率。采用这种接口不仅能提高传输 速率,而且所需传输线也只需几对差分对即可,但由 于这种高速的差分接口对 PCB 布线要求非常严格, 在本设计中只作为备用接口使用。 2. 4 网络接口设计

以下行接收链路为例,经 A / D 采样后的 12 位 并行高速数据通过高速的 HSMC 连接器进入基带 FPGA,FPGA 接收数据后首先进行数据转换,将 12 位并 行 数 据 转 换 成 16 位 有 符 号 数 据,继 而 进 行 DDC,DDC 内部对中频信号进行数字混频、降采样 和滤波后输出基带信号,随后对基带信号进行预处 理,如信号同步、信道估计等。预处理后的数据依次 缓存在 FPGA 内部开辟的 FIFO 中传送给 DSP,DSP 通过乒乓操作完成数据的无缝缓冲与实时处理,处

口,搭建了一个高性能的通用基带信号处理平台。该平台直接实现对中频数字信号的处理,融合数字上下变频与基带算法于

一体,具有模块化、灵活性等特点。实验结果表明,该基带处理平台能快速接收并实时处理各类基带信号,数据处理能力达到

了较高水平。

关键词 信号处理 通用基带 FPGA DSP

中图法分类号 TP925. 5;

结合各类无线通信系统实际算法需求,低层信 号预处理算法的数据为符号级数据,虽然数据量大 但运算结构相对比较简单,适于用 FPGA 进行硬件 实现。高层处理算法的数据为比特型数据,其特点

2013 年 8 月 28 日收到

国家科学与技术重大项目

( 2011ZX03006-003( 7) ) 、重庆市基础与前沿研究

1 系统硬件方案设计

1. 1 系统方案 按照软件无线电的设计思想,基带处理平台的

宗旨是完成包括 GSM、CDMA、CDMA2000、WCDMA、 TD-SCDMA、LTE 等多种通用算法的实时处理。所 以整个基带处理平台主要难点在于对高速信号的正 确收发、存储与实时处理。基带处理平台主要包括 三大功能模块,即数字中频处理模块、基带数据收发 和预处理模块以及基带数据算法处理模块。前两个 模块由 FPGA 实现,后一个模块由 DSP 实现,这样的 分配能充分发挥 FPGA 和 DSP 各自的最佳性能。

240

科学技术与工程

14 卷

到射频。 DSP 主要负责关键算法的运算,如信道编解码、

信号检测、噪声滤波等,除此之外还要完成 DSP 内 置外部接口的通信、与上位机和 FPGA 之间的交互 等任务[3]。系统整体框图如图 1 所示。

图 1 系统硬件总体架构图

整个系统分为上行和下行两个通道,两个通道 的数据处理分别用两块 DSP 芯片实现,两个通道不 仅能独立工作而且相互能进行快速的数据交互,很 大程度上提高了系统数据处理的实时性和并行能 力。DSP 与 FPGA 之间存在丰富的接口,包括用于 高速数据传输的快速串口 ( serial rapidIO) 和 64 bit EMIF ( external memory interface) 接口以及用于控制 命令传输的多通道缓冲串口 ( McBSP) 和通用输入 输出口( GPIO) 。DSP 与 DSP 之间也有用于高速数 据传 输 的 Serial RapidIO 和 用 于 控 制 命 令 传 输 的 McBSP 接口,数据交互非常方便。另外,FPGA 和 DSP 均外扩了一个高速的 DDR2-SDRAM 和大容量 的 FLASH,完成高速数据和程序的存储。整个基带 处理硬件系统通过以太网连接至上位机,实现人机 交互。 1. 2 信号处理流程

3期

谭左红,等: 基于 FPGA + DSP 的高速基带信号处理平台的设计

241

LVDS 传输线,速率达到 1. 6 Gb / s; 16 对高速的模拟 LVDS 传输线,速率达到 1. 1 Gb / s。显然,通过这种 高速差分的 HSMC 连接器能满足传输速率的要求。 2. 3 FPGA 和 DSP 接口设计

整个基带处理平台的控制和管理需要 PC,而且 经基带处理后的数据也要 PC 后续处理和显示,因

此我们借助以太网和 PC 建立联系,实现数据交互 和系统控制。系统网口模块如图 3 所示。

计划项目( cstc2013jcyjA40032; cstc2013jcyjA40034;

cstc2013jcyjA40041) 资助

第一作者简介: 谭左红( 1989—) ,男,硕士。研究方向: 移动通信、无

线定位。E-mail: tanzuohongoy@ 163. com。

是数据量较少,但算法的控制结构复杂,适于用 DSP 来实现。FPGA 具 有 明 显 的 并 行 处 理 优 势 和 灵 活 性,DSP 运算速度快、寻址方式灵活,二者均能满足 处理复杂算法的要求,这样以 FPGA + DSP 的架构 为核心,借助于高性能的器件和高速接口,设计了一 个高性能 信 号 处 理 硬 件 平 台[2]。 该 平 台 具 有 灵 活 的处理结构,对不同结构的算法都有较强的适应能 力,尤其适合实时信号的处理。