龙芯2处理器设计

龙芯CPU 2F 简介

龙芯CPU 2F 简介龙芯2号F版本(简称“龙芯2F”)是一款实现64位MIPSⅢ指令集的通用RISC处理器,其基本性能参数如下表。

龙芯2F处理器的微体系结构如下图所示,它除了具有先进的微体系结构外,它还集成了DDR2控制器、PCI/PCI-X及Local IO控制器,是一款具有较高集成度的SoC芯片。

龙芯2F 在性能功耗比方面相比与国际同类芯片具有优势,市场应用前景广阔。

目前,龙芯2F已实现大批量生产。

龙芯2F结构图龙芯2F处理器、主板及性能在龙芯官方论坛里,在广大关注者的热切期盼下,我们终于看到了传说中的龙芯2F处理器和相关主板的样品实物照片。

据有关人士透露,这是龙梦开发中的家庭服务器主板,由龙芯2F处理器(意法半导体生产)搭配AMD CS5536南桥芯片(第一张照片的左上方)组成,同时提供双千兆网络控制器、Sil3114 SATA控制器、32MB NOR Flash闪存、一个IDE接口、四个eSATA 接口(支持RAID)、一个PCI扩展槽等,可用作网络存储、BT下载、打印、邮件、web、数据库、防火墙等服务,充分考虑了DIY需求。

32MB NOR Flash闪存容量不大,但主要是用来DIY一些专用设备的,比如防火墙,需要更多存储的话则可以通过IDE和SATA接口实现。

另外,所有设备都可以支持66M PCI,IO性能应该是不错的,而且hdparm -t的硬盘速度应该可以达到60-80MB/s,是福珑的2倍多。

至于北桥功能,龙芯2F本身已经集成。

龙芯2F 系统芯片(SoC)已于今年7月底流片成功(Taped Out),在之后两个月的严格测试中没有发现任何设计错误,现已正式定型。

根据与计算所签订的有偿授权协议,意法半导体公司最近已启动百万片量级的龙芯2F大规模生产。

至于龙芯2F的具体性能水平和正式发布时间,暂时还没有透露,但以上消息已经颇为振奋人心,大家只需耐心等待。

龙芯2F主板样品实物图。

注意很多芯片还没有焊上。

龙芯2F处理器数据手册

龙芯2F处理器数据手册1.0版中国科学院计算技术研究所意法半导体有限公司北京龙芯中科技术服务中心有限公司2008年8月龙芯2F处理器数据手册芯片特点兼容64位的MIPS III指令集及其扩展指令集;四发射动态超标量,2个定点单元,2个全流水浮点乘/加单元和1个load/store访存单元;9-10级的超流水线结构,支持寄存器重命名、动态调度、分支预测和其他的乱序执行技术;兼容IEEE754标准的浮点单元,支持全流水的浮点加减、乘法、乘加等运算,支持硬件除法和开平方根运算,浮点单元还支持龙芯多媒体指令;64项JTLB(Joint TLB),每个表项以奇/偶页成对组织,记录4KB-4MB页大小的共128个页面,TLB中通过执行保护位防止缓冲区溢出攻击;16项独立的指令TLB,提高指令地址映射的效率;分离的64KB一级指令Cache和64KB一级数据cache,四路组相联结构,块大小为32字节;片内512KB二级cache,四路组相联结构,块大小为32字节,可通过软件控制二级Cache的打开和关闭;集成64位DDR2内存控制器,最高频率为333MHz;集成32位PCI/PCI-X总线控制器,符合PCI-X 1.0b规范,兼容PCI2.3;1 GHz的主频,可动态调节频率甚至关闭处理器的Core时钟,支持动态功耗管理;1 GHz时的功耗小于5W;集成视频加速模块,支持YUV格式到RGB 格式的转换,支持图像缩放。

HFCBGA 452概述龙芯2F是龙芯2E的改进版,具有更高的I/O 接口带宽和访存带宽,支持软件动态调节处理器工作频率,兼容MIPS64指令集。

龙芯2F集成了高性能的龙芯64位CPU核、DDR2内存控制器、PCI/PCI-X总线控制器、Local-Bus接口、中断控制器和视频加速单元。

龙芯2F使用CMOS 90nm工艺制程制造。

龙芯2F处理器数据手册目录芯片特点 (2)HFCBGA 452 (2)概述 (2)目 录 (I)图目录 (III)表目录 (IV)1.引言 (1)2.接口描述 (3)2.1接口信号模块 (3)2.2PCI总线接口信号 (4)2.3DDR2SDRAM总线接口信号 (4)2.4L OCAL BUS总线信号 (5)2.5初始化信号 (6)2.6中断信号 (7)2.7JTAG信号 (7)2.8测试和控制信号 (8)2.9时钟信号 (8)2.10电源和地 (9)3. IO总线接口描述 (11)3.1PCI/PCI-X接口特性 (11)3.2接口工作模式 (11)3.3PCI总线仲裁器 (11)3.4系统接口连接 (11)3.5L OCAL BUS总线描述 (12)3.6中断处理 (13)4. DDR2 SDRAM控制器接口描述 (15)4.1DDR2SDRAM控制器特性 (15)4.2DDR2SDRAM读协议 (15)4.3DDR2SDRAM写协议 (16)4.4DDR2SDRAM参数设置顺序 (16)4.5DDR2SDRAM采样模式配置 (17)5.初始化过程 (18)6.电气特性 (19)6.1绝对最大最小额定值 (19)6.2推荐工作条件 (19)6.3直流参数 (20)龙芯2F处理器数据手册6.4交流电气特性 (21)6.5功耗特性 (23)7. 热特性 (24)7.1热阻率 (24)7.2回流焊温度曲线 (24)8.引脚排列和封装 (25)8.1引脚排列 (25)8.2封装尺寸 (28)9.修订历史 (30)龙芯2F处理器数据手册图目录图1.1 龙芯2F结构框图 (1)图2-1 龙芯2F处理器接口信号框图 (3)图3-1 龙芯2F单处理器系统连接 (12)图3-2 龙芯2F多处理器系统连接 (12)图3-3 LOCAL BUS总线读时序 (13)图3-4 LOCAL BUS总线写时序 (13)图4-1 DDR2 SDRAM读协议,CAS LATENCY = 3, READ LATENCY = 3, BURST LENGTH = 8 (16)图4-2 DDR2 SDRAM写协议,CAS LATENCY = 3, WRITE LATENCY = READ LATENCY -1 = 2, BURST LENGTH = 4. (16)图5-1 当作为主桥时初始化过程 (18)图7-1 回流焊温度曲线 (24)图8-1 HFCBGA452 机械数据&封装尺寸 (29)龙芯2F处理器数据手册表目录表2-1 PCI总线信号 (4)表2-2 DDR2 SDRAM控制器接口信号 (5)表2-3 LOCAL BUS总线信号 (5)表2-4 初始化接口信号 (6)表2-5 中断接口信号 (7)表2-6 JTAG接口信号 (7)表2-8 时钟信号 (8)表2-9 处理器内部/外部频率配置 (8)注1:当倍频系统为1时,产生处理器CORE时钟的PLL被旁路,此时,CORE时钟等于SYSCLK的输入时钟频率; (9)注2:SYSCLK输入时钟必须满足对应倍频系数的输入频率要求,否则不能保证处理器工作的稳定性;.. 9注3:板级设计时,为满足处理器CORE时钟调整的灵活性,SYSCLK的输入时钟建议使用100MHZ; (9)表2-10 DDR内部/外部分频系数 (9)注1:MEMCLK输入时钟必须满足对应倍频系数的输入频率要求,否则不能保证内存控制器工作的稳定性; (9)表2-10 电源和接地信号 (9)表4-1 DDR2 SDRAM行/列地址转换 (15)表6-1 绝对最大额定值 (19)表6-2 推荐的工作温度和电压 (19)表6-3 直流参数 (20)表6-4 直流参数(JTAG) (20)表6-5 时钟参数特性 (21)表6-6 信号输入建立和保持时间 (21)表6-7 PCI和LOCAL BUS信号输出延迟时间 (22)(测试条件:SYSCLK=100MHZ, PCICLK=133MHZ, CORECLK=1000MHZ) (22)表6-8 JTAG参数特性 (22)龙芯2F处理器数据手册(测试条件:TCK=100MHZ) (22)表6-9 功耗特性 (23)表7-1 回流焊温度参数 (24)表8-1 龙芯2F引脚排列(左手边) (25)表8-1 龙芯2F引脚排列(中间) (26)表8-1 龙芯2F引脚排列(右手边) (27)表9-1修订文档 (30)龙芯2F处理器数据手册1.引言龙芯2F是一款集成龙芯64位CPU核,兼容MIPS64的高性能低功耗处理器芯片。

龙芯2Nehalem处理器架构深度对比分析

龙芯2/Nehalem处理器架构深度对比分析在谈到MIPS的时候,它意味着一种RISC(Reduced Instruction Set Computing,精简指令集)处理器,一种指令集,同时,MIPS又是一间公司。

MIPS处理器是一种很流行的RISC处理器,而MIPS的意思是“无内部互锁流水级的微处理器”(Microprocessor without Interlocked Piped Stages),其机制是尽量避免流水线中的数据相关导致的互锁问题。

它最早是在80年代初期由斯坦福(Stanford)大学Hennessy教授领导的研究小组研制出来的。

MIPS公司的R系列就是在此基础上开发的RISC工业产品的微处理器。

这些系列产品为很多计算机公司采用构成各种工作站和计算机系统。

MIPS 79R4400MC处理器,顶盖上的积分符号显得极具学院气息龙芯一开始是一款MIPS-like(类MIPS)处理器,这个后缀like是非常重要的,在2005年(龙芯2C之前),ICT(计算所)并没有MIPS公司的许可证,因此有4条被专利保护的指令不能实现,因此只能称为MIPS-like处理器,换一种方式叫做95% MIPS Compatible(95% MIPS兼容)。

这四条指令是lwl, lwr, swl, swr,属于访存地址不对齐(Unaligned Memory Access)的指令(32位模式为4条,64位模式为8条),这些指令的美国专利保护在2006年到期。

龙芯1是32位处理器,龙芯2是64位处理器。

Sony PS2上的EmotionEngine可能是最为一般人熟知的MIPS处理器2007年,ICT通过ST意法半导体获得了MIPS的授权,龙芯2成为了MIPS-compatible(MIPS兼容)的处理器(就像AMD等厂商的处理器叫做x86兼容处理器一样),目前的龙芯2F指令系统主要由以下四个部分组成:(1)MIPS III指令集;(2)独有的普通用户态指令,如乘累加指令(MIPS IV中定义了乘加指令,但龙芯2号没有采用)等;(3)部分与处理器结构紧密相关的核心态指令,如对Cache或TLB操作的指令(这些指令一般随结构的不同而不同,即使在MIPS的不同处理器中也是如此)以及在未来的龙芯3号中进行多核之间同步和通信的指令等;(4)龙芯独有的多媒体指令。

龙芯2K1000处理器数据手册说明书

龙芯2K1000处理器数据手册V1.22020年4月龙芯中科技术有限公司版权声明本文档版权归龙芯中科技术有限公司所有,并保留一切权利。

未经书面许可,任何公司和个人不得将此文档中的任何部分公开、转载或以其他方式散发给第三方。

否则,必将追究其法律责任。

免责声明本文档仅提供阶段性信息,所含内容可根据产品的实际情况随时更新,恕不另行通知。

如因文档使用不当造成的直接或间接损失,本公司不承担任何责任。

龙芯中科技术有限公司Loongson Technology Corporation Limited地址:北京市海淀区中关村环保科技示范园龙芯产业园2号楼Building No.2, Loongson Industrial Park, Zhongguancun Environmental Protection Park电话(Tel):************传真(Fax):************阅读指南《龙芯2K1000处理器数据手册》主要介绍龙芯2K1000处理器接口结构,特性,电气规范,以及硬件设计指导。

修订历史文档更新记录文档名: 龙芯2K1000处理器数据手册版本号:V1.2创建人: 芯片研发部创建日期: 2020-4更新历史序号. 更新日期版本号更新内容1 2017-7 V1.0 第一版2 2018-8 V1.1 1.增加CAMERA和VPU相关内容2.修改DVO0和UART2的复用关系3.更新LIO读写时序4.增加芯片分级信息3 2020-4 V1.2 1. 1.2.3节将DVO解释为通用并行显示接口2. 1.2.4节内存控制器功能描述修改3. 1.2.21节增加CAN总线描述内容4. 1.3节芯片工作温度更新5. 2.3节更正DVO0_CLKP/N与LIO_RDn/WRn的复用关系6. 2.6节USB接口功能描述修改7. 2.14节更正SDIO_DATA[3:0]与GPIO[39:36]复用关系8. 3.4节增加LIO波形图的说明9. 3.14节增加GMAC接口说明10.5.22节增加SATA/PCIE时钟特性11.第8章封装图改为矢量图,增加DIE位置信息12.增加第9章订货信息13.更新TBD相关内容手册信息反馈: *******************也可通过问题反馈网站/向我司提交芯片产品使用过程中的问题,并获取技术支持。

龙芯2E多处理器芯片组的设计与实现

●

De i n a d i l me t t n o lip o e s r c i s tb s d o d o E sg n mp e n a i fmu t- r c s o h p e a e n Go s n 2 CPU o

F N h -i 。 e g ・ , N X e u ’ A GZ i n b ・ HU P n 一 A u - n ,S N N n -u j U igh i ’

维普资讯

第2 5卷 第 5期

20 0 8年 5 月

计 算 机 应 用 研 究

Ap lc t n Re e r h o o u e s p i ai s a c fC mp t r o

Vo . 5 No 5 12 . M a 0 8 v2 0

Ke o d :mut po esr h st g b l d rs s a e G S ;G d o E C U yw r s l -rc s ;c i e ; l a d es p c ( A ) o sn2 P i o p o a

0 引言

随着 V S 和微处 理器技术 的发展 , 用微处 理器构 建 的 LI 利 并行 计算 机已经取代大型 主机和 向量机在 高性 能计算 领域 占 据主流地 位。并行 计算 机按 体系结 构主要 分为对 称多处 理机 S 、 MP 分布式共享 内存 C N MA、 C. U 大规 模并 行处 理 MP P和机 群 csr l t 四类 。高性 能并 行计 算机 面 临 的挑战 主要 有 : ue 硬 件上 可扩展规模受 限 , 通信和 同步 的性 能不 能很 好地随处理器

学习龙芯汇编语言程序设计

第四篇,在 C 语言中嵌入汇编。

在 C 语言中直接使用机器指令。

第五篇,介绍一些指令(一般的指令直接看手册,只介绍需要注意的)

联机分时系统

六十年代末七十年代初最热的技术之一是联机分时系统。在这之前,程序员要使用计算机一 般是使用穿孔卡片或穿孔纸带,然后是排队,轮到后,独自占用。往往编译出错,便要把计 算机让给别人用,修改后,再排队,重复上面的过程。随着计算机的内存不断增大和速度不 断提高,技术人员就研究出了让多个用户分享一台计算机的办法。不但程序员获益(编辑, 编译,运行,好象独占一台电脑),商业用户也可以用来远程访问联机的数据库,这让计算 机的应用大为扩展,象银行异地处理业务,飞机订票管理这样的应用也可以实现了。专业厂 家的系统都很昂贵,而且和专有的硬件结合在一起,一般用户无法很便宜地获得。这些分时 系统有的使用字符终端,有的使用电传打字机(出于成本考虑,比终端便宜)。

在 UNIX 开发出来后,由于可移植,各种新开发的,更便宜的硬件上也能提供联机分时服务 了。

后来分时技术不断改进,现在已经有了基于网络的远程登陆,比如论坛大侠 lyxmoo 在拿到 龙芯盒子之后,慷慨提供 SSH 服务,让没有盒子的朋友们也能体验一下使用龙芯的感受。

以前提供分时服务的计算机,属于大型机(速度约每秒一百万次)。

通用寄存器$31还是处理器硬件约定的 JAL 指令的链接寄存器。(JALR 可以使用任何一个 通用寄存器)。通用寄存器$0,它的值恒为零。

由于 MIPS 采用将比较运算的结果放入任意一个指定的通用寄存器,所以龙芯没有整数比较 运算结果的标志寄存器(浮点运算使用状态寄存器的一个状态位)。

指令说明:

move 目的寄存器,源寄存器,表示把源寄存器的值传送至“目的寄存器”

国产龙芯cpu简介

国产CPU的昨天,今天和明天——关于龙芯CPU发展的简要研究背景:在最近两年多的时间里,国产CPU如雨后春笋,频频展露出喜人的"尖尖角". 2001年3月,中星微系统公司开发出数码影像处理芯片"星光1号";2001年7月,方舟公司的"方舟1号"嵌入式CPU问世;2002年9月,中科院计算所研制成功我国首款通用高性能CPU"龙芯1号";2002年11月,上海复旦微电子公司推出高性能嵌入式32位微处理"神威1号";2002年12月,北京大学"众志1号"面世;2003年2月,上海交通大学的"汉芯1号"面世……国产CPU的发展源于何时?现状怎样?未来目标如何?我们就这些问题,以国产CPU的典型代表“龙芯”系列为线索,循着其发展历程,共同探索国产CPU 的昨天、今天和明天。

(一)龙芯昨天龙芯(英语:GODSON)是中国中国科学院自主开发的通用CPU,采用简单指令集,类似于MIPS指令集。

第一型的速度是266MHz,最早在2002年开始使用,龙芯2号第二型为500MHz,第三型的目标在1GHz。

“十五”期间,国家863计划提出了自主研发CPU的战略思路。

·2001年3月起,中国科学院计算技术研究所正式启动处理器设计项目。

·2001年3月,中科院计算技术研究所开始研制具有中国自主知识产权的高性能通用CPU芯片,被命名为“龙芯”。

项目领导是中科院计算所所长李国杰,具体技术主管是研究院胡伟武。

·2001年10月龙芯的FPGA验证成功,通过中国科学院主持的“龙芯(Godson)CPU设计与验证系统”项目评审。

·2002年6月“龙芯1号”CPU研制成功。

·2002年7月“龙芯1号”CPU小批量投片成功。

·2002年8月6日由中国科学院计算技术研究所和江苏综艺集团等合资组建的“北京神州龙芯集成电路设计有限公司”正式成立。

龙芯 2 号和 3 号处理器嵌入式开发指南说明书

我们希望通过本手册,能够为龙芯用户建立起一个调试开发基本的概念。能够让用户快 速上手使用龙芯处理器的相关产品。

龙芯中................................................................................................................................................. 1 第一章资源获取............................................................................................................................... 2 第二章 Pmon ...................................................................................................................................4

2.2.1 安装 makedepand......................................

双核cpu是什么双核cpu的优势

双核cpu是什么-双核cpu的优势双核cpu是什么-双核cpu的优势简介从双核技术本身来看,到底什么是双内核?毫无疑问双内核应该具备两个物理上的运算内核,而这两个内核的设计应用方式却大有文章可作。

据现有的资料显示,AMDOpteron处理器从一开始设计时就考虑到了添加第二个内核,两个CPU内核使用相同的系统请求接口SRI、HyperTransport技术和内存控制器,兼容90纳米单内核处理器所使用的940引脚接口。

而英特尔的双核心却仅仅是使用两个完整的CPU封装在一起,连接到同一个前端总线上。

可以说,AMD的解决方案是真正的"双核",而英特尔的解决方案则是"双芯"。

可以设想,这样的两个核心必然会产生总线争抢,影响性能。

不仅如此,还对于未来更多核心的集成埋下了隐患,因为会加剧处理器争用前端总线带宽,成为提升系统性能的瓶颈,而这是由架构决定的。

因此可以说,AMD的技术架构为实现双核和多核奠定了坚实的基础。

AMD直连架构(也就是通过超传输技术让CPU内核直接跟外部I/O相连,不通过前端总线)和集成内存控制器技术,使得每个内核都有自己的高速缓存可资遣用,都有自己的专用车道直通I/O,没有资源争抢的问题,实现双核和多核更容易。

而Intel是多个核心共享二级缓存、共同使用前端总线的,当内核增多,核心的处理能力增强时,肯定要遇到堵的问题。

HT技术HT技术是超线程技术,是造就了PENTIUM4的一个辉煌时代的武器,尽管它被评为失败的技术,但是却对P4起一定推广作用,双核心处理器是全新推出的处理器类别;HT技术是在处理器实现2个逻辑处理器,是充分利用处理器资源,双核心处理器是集成2个物理核心,是实际意义上的双核心处理器。

其实引用《现代计算机》杂志所比喻的HT技术好比是一个能用双手同时炒菜的厨师,并且一次把一碟菜放到桌面;而双核心处理器好比2个厨师炒两个菜,并同时把两个菜送到桌面。

龙芯——中国人的cpu

龙芯——中国人的cpu龙芯(英语:Loongson,旧称GODSON[1])是中国科学院计算所自主开发的通用CPU,采用简单指令集,类似于MIPS指令集。

第一型的速度是266MHz,最早在2002年开始使用。

龙芯2号速度最高为1GHz。

龙芯3号还未有成品,而设计的目标则在多核心的设计。

众所周知,CPU是决定电脑性能的核心部件,也是整个系统的核心。

其负责整个系统指令的执行、数学与逻辑的运算;数据的存储与传送;以及对内对外输入/输出的控制。

而在这个电脑核心部件市场领域里,人们最为熟悉的两个品牌无疑是Intel和AMD,他们在处理器市场的强势地位似乎无人能撼动。

在CPU技术上,我们跟国外厂商有着较大的差距,缺乏具有自主知识产权的CPU芯片,是我国计算机产业的一大“芯”病,也是我们这些电子工作者、网络人胸口永远的痛。

过去,代表着国际IT顶尖技术的CPU芯片一直被英特尔等国外巨头所垄断,中国企业及消费者为之付出了巨额版权费。

好在神州龙芯公司先后推出了“龙芯1号”、“龙芯2号”,打破了中国无“芯”的历史。

“龙芯”的诞生被业内人士誉为民族科技产业化道路上的一个里程碑。

商品化的“龙芯”1号CPU的研制成功标志着我国已打破国外垄断,初步掌握了当代CPU设计的关键技术,为改变我国信息产业“无芯”的局面迈出了重要的步伐,对我国形成有自主知识产权的计算机产业有重要的推动作用,对中国的CPU核心技术、国家安全、经济发展都有举足轻重的作用。

我们有信心:“龙芯” 对Intel说“不” !对PC产业来讲,包括联想、方正这样的大企业利润也是相当低的,主要原因就是我们买别人的芯片来组装,只是一个组装工厂而已。

而且,在国际CPU巨头AMD与英特尔的明争暗斗中,中国PC厂商无论怎样都掩盖不了“看他人脸色”的尴尬处境, 既要哄着占有份额优势的英特尔,又不敢得罪价格占优的AMD,而这一切都缘于我们无“芯”可挑大梁,缘于中国PC业长期以来没有占据技术的制高点。

龙芯2号处理器系统优化关键技术

北 京 10 8 ) 0 0 0

Crtc lTe h qu so y tm iia c ni e fS s e Optm ia i n f r Go s n 2 Pr c so i z to o d o - o e s r

wa st e o v a h y ny n Go s n一 o e s n e h d o de r a e p ro ma c o s r s li g y o r s l e c c e s no ms i d o 2 pr c sora d m t o s t c e s e f r n e ls e utn fom r TLB mis s c a a gme i g he a sz s, u h s u ntn t p ge ie, s fwa e o t r TLB a d n FAST—TLB—REFI LL, a e r

Ke r s Go s n一 r c s o ;c c e s no ms ofwa e TLB;Un a h c lr t y wo d d o 2 p o e s r a h y ny ;s t r c c e Ac ee a e

摘 要 系统软件 作 为 处理 器和应 用程 序之 间 的接 口, 于 充分利 用 处理 器的 特性 来 维护 处理 器与 应 用 对 程序 的稳 定性 和提 高应 用程 序 的性 能起 着极其 重 要 的作 用. 述 了在 Ln x内核 中解 决龙 芯 2号 处理 描 iu

W uM ig,Z a g Fu i ,L nW e,Xu Xin h o,Yu n Na n h n x n i i aca a n,a d W a gJa n n in

龙芯 2G 处理器用户手册 上册 - 多核处理器架构、寄存器描述与系统软件编程指南说明书

龙芯2G处理器用户手册上册多核处理器架构、寄存器描述与系统软件编程指南2012年3月中国科学院计算技术研究所龙芯中科技术有限公司版权声明本文档版权归北京龙芯中科技术有限公司所有,并保留一切权利。

未经书面许可,任何公司和个人不得将此文档中的任何部分公开、转载或以其他方式散发给第三方。

否则,必将追究其法律责任。

免责声明本文档仅提供阶段性信息,所含内容可根据产品的实际情况随时更新,恕不另行通知。

如因文档使用不当造成的直接或间接损失,本公司不承担任何责任。

龙芯中科技术有限公司Loongson Technology Corporation Limited地址:北京市海淀区中关村科学院南路10号No.10 Kexueyuan South Road, Zhongguancun Haidian District, Beijing电话(Tel):************传真(Fax):************阅读指南本手册分为两部分,第一部分(第1章~第10章)介绍龙芯2G多核处理器架构与寄存器描述,对芯片系统架构、主要模块的功能与配置、寄存器列表及位域进行详细说明;第二部分(第11章~第16章)是系统软件编程指南,对BIOS和操作系统开发过程中的常见问题进行专题介绍。

关于龙芯2G多核芯片所集成的GS464高性能处理器核的相关资料,请参阅《龙芯GS464处理器核用户手册》。

IV修订历史目录图目录.......................................................................................................................... I V 表目录 (V)第一部分 (7)1 概述 (1)2 系统配置与控制 (3)2.1 控制引脚说明 (3)2.2 Cache一致性 (4)2.3 系统节点级的物理地址空间分布 (4)2.4 地址路由分布与配置 (6)2.5 芯片配置及采样寄存器 (11)3 GS464处理器核 (13)4 二级Cache (15)5 矩阵转置模块 (17)6 处理器核间中断与通信 (20)7 I/O中断 (22)8 DDR2/3 SDRAM控制器配置 (25)8.1 DDR2/3 SDRAM控制器功能概述 (25)8.2 DDR2/3 SDRAM读操作协议 (26)8.3 DDR2/3 SDRAM写操作协议 (26)8.4 DDR2/3 SDRAM参数配置格式 (27)9 HyperTransport控制器 (73)9.1 HyperTransport硬件设置及初始化 (73)9.2 HyperTransport协议支持 (74)9.3 HyperTransport中断支持 (76)9.4 HyperTransport地址窗口 (76)9.4.1 HyperTransport空间 (76)9.4.2 HyperTransport控制器内部窗口配置 (77)9.5 配置寄存器 (78)9.5.1 Bridge Control (80)9.5.2 Capability Registers (80)9.5.3 自定义寄存器 (82)9.5.4 接收地址窗口配置寄存器 (83)9.5.5 中断向量寄存器 (85)9.5.6 中断使能寄存器 (87)9.5.7 Interrupt Discovery & Configuration (88)9.5.8 POST地址窗口配置寄存器 (89)9.5.9 可预取地址窗口配置寄存器 (90)9.5.10 UNCACHE地址窗口配置寄存器 (91)9.5.11 HyperTransport总线配置空间的访问方法 (92)10 低速IO控制器配置 (94)10.1 LPC控制器 (94)10.2 UART控制器 (96)10.2.1 数据寄存器(DAT) (96)10.2.2 中断使能寄存器(IER) (96)10.2.3 中断标识寄存器(IIR) (97)10.2.4 FIFO控制寄存器(FCR) (98)10.2.5 线路控制寄存器(LCR) (98)10.2.6 MODEM控制寄存器(MCR) (100)10.2.7 线路状态寄存器(LSR) (100)10.2.8 MODEM状态寄存器(MSR) (102)10.2.9 分频锁存器 (102)10.3 SPI控制器 (103)10.3.1 控制寄存器(SPCR) (103)10.3.2 状态寄存器(SPSR) (104)10.3.3 数据寄存器(TxFIFO) (104)10.3.4 外部寄存器(SPER) (104)10.4 IO控制器配置 (106)第二部分 (110)11 中断的配置及使用 (111)11.1 中断的流程 (111)11.2 中断路由及中断使能 (111)11.2.1 中断路由 (112)11.2.2 中断使能 (114)11.3 中断分发 (115)12 串口的配置及使用 (117)12.1 可选择的串口 (117)12.2 PMON的串口配置 (117)12.3 Linux内核的串口配置 (118)13 EJTAG调试 (120)13.1 EJTAG介绍 (120)13.2 EJTAG工具使用 (121)13.2.1 环境准备 (121)13.2.2 PC采样 (121)13.2.3 读写内存 (121)13.2.4 执行说明 (121)14 地址窗口配置转换 (125)14.1 一二级交叉开关地址窗口配置方法 (125)14.2 一级交叉开关地址窗口 (125)14.3 一级交叉开关地址窗口配置时机 (127)14.4 二级交叉开关地址窗口 (127)14.5 对地址窗口配置的特别处理 (128)14.6 HyperTransport地址窗口 (129)14.6.1 处理器核对外访问地址窗口 (130)14.6.2 外部设备对处理器芯片内存DMA访问地址窗口 (131)14.6.3 低速设备地址窗口 (131)14.7 地址空间配置实例分析 (131)14.7.1 一级交叉开关实例1 (132)14.7.2 一级交叉开关实例2 (133)14.7.3 二级交叉开关实例1 (134)14.7.4 二级交叉开关实例2 (135)15 系统内存空间分布设计 (137)15.1 系统内存空间 (137)15.2 系统内存空间与外设DMA空间映射关系 (140)15.3 系统内存空间的其它映射方法 (141)16 X系统的内存分配 (142)龙芯2G处理器用户手册图目录图目录图1-1龙芯2G芯片结构 (1)图3-1 GS464结构图 (14)图7-1龙芯2G处理器中断路由示意图 (22)图8-1 DDR2 SDRAM行列地址与CPU物理地址的转换 (25)图8-2 DDR2 SDRAM读操作协议 (26)图8-3 DDR2 SDRAM写操作协议 (26)图9-1龙芯2号中HT协议的配置访问 (93)图11-1 2G-690e中断流程图 (111)图11-2 龙芯2G处理器中断路由示意图 (112)图13-1 EJTAG调试系统 (120)图16-1显卡处理图像显示的过程 (142)表目录表2-1 控制引脚说明 (3)表2-2 节点级的系统全局地址分布 (4)表2-3 节点内的地址分布 (5)表2-4 节点内的地址分布 (6)表2-5 一级交叉开关地址窗口寄存器表 (6)表2-6 2级XBAR处,标号与所述模块的对应关系 (9)表2-7 MMAP字段对应的该空间访问属性 (9)表2-8二级XBAR地址窗口转换寄存器表 (9)表2-9二级XBAR缺省地址配置 (10)表2-10芯片配置寄存器(物理地址0x1fe00180) (11)表2-11 芯片采样寄存器(物理地址0x1fe00190) (11)表4-1 二级Cache锁窗口寄存器配置 (15)表5-1 矩阵转置编程接口说明 (17)表5-2 矩阵转置寄存器地址说明 (18)表5-3 trans_ctrl寄存器的各位解释 (18)表5-4 trans_status寄存器的各位解释: (19)表6-1处理器核间中断相关的寄存器及其功能描述 (20)表6-2 0号处理器核核间中断与通信寄存器列表 (20)表6-3 1号处理器核的核间中断与通信寄存器列表 (20)表6-4 2号处理器核的核间中断与通信寄存器列表 (21)表6-5 3号处理器核的核间中断与通信寄存器列表 (21)表7-1中断控制寄存器 (23)表7-2 IO控制寄存器地址 (23)表7-3中断路由寄存器的说明 (23)表7-4中断路由寄存器地址 (24)表8-1 DDR2 SDRAM配置参数寄存器格式 (27)表9-1 H yperTransport总线相关引脚信号 (73)表9-2 HyperTransport接收端可接收的命令 (75)表9-3 两种模式下会向外发送的命令 (75)表9-4 默认的HyperTransport地址窗口的地址 (76)表9-5 龙芯2G处理器HyperTransport接口地址窗口分布 (77)表9-6龙芯2号处理器HyperTransport接口中提供的地址窗口 (77)表9-7本模块中所有软件可见寄存器 (78)表10-1 LPC控制器地址空间分布 (94)表10-2 LPC配置寄存器含义 (95)表10-3 IO控制寄存器 (106)表10-4寄存器详细描述 (107)表11-1中断路由寄存器的说明 (112)表11-2中断路由寄存器地址 (113)表11-3中断控制位连接及属性配置 (114)表14-1 【请给出表头】 (126)表14-2 【请补充表头】 (127)第一部分多核处理器架构、寄存器描述1概述龙芯2G是一个3-4核的处理器,采用65nm工艺制造,最高工作频率为1GHz,主要技术特征如下:•片内集成3-4个64位的四发射超标量GS464高性能处理器核;•片内集成4 MB的分体共享二级Cache(由4个体模块组成,每个体模块容量为1MB) ;•通过目录协议维护多核及I/O DMA访问的Cache一致性;•片内集成2个64位400MHz的DDR2/3控制器;•片内集成1个16位800MHz的HyperTransport控制器;•片内集成1个LPC、2个UART、1个SPI、16路GPIO接口;龙芯2G芯片整体架构基于两级互连实现,结构如图1-1所示。

龙芯芯片的发展历程

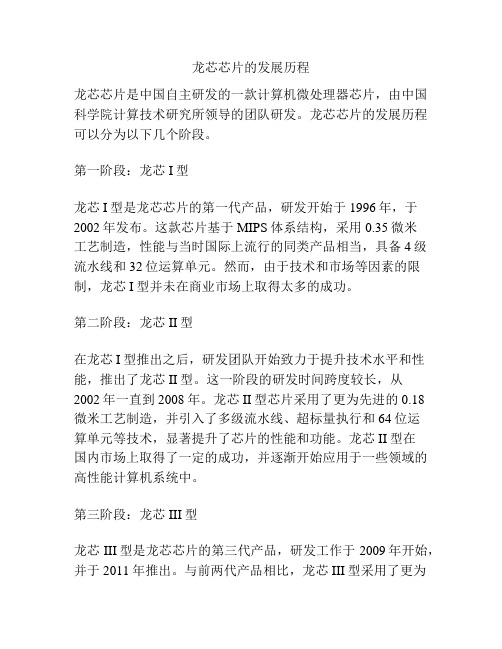

龙芯芯片的发展历程龙芯芯片是中国自主研发的一款计算机微处理器芯片,由中国科学院计算技术研究所领导的团队研发。

龙芯芯片的发展历程可以分为以下几个阶段。

第一阶段:龙芯I型龙芯I型是龙芯芯片的第一代产品,研发开始于1996年,于2002年发布。

这款芯片基于MIPS体系结构,采用0.35微米工艺制造,性能与当时国际上流行的同类产品相当,具备4级流水线和32位运算单元。

然而,由于技术和市场等因素的限制,龙芯I型并未在商业市场上取得太多的成功。

第二阶段:龙芯II型在龙芯I型推出之后,研发团队开始致力于提升技术水平和性能,推出了龙芯II型。

这一阶段的研发时间跨度较长,从2002年一直到2008年。

龙芯II型芯片采用了更为先进的0.18微米工艺制造,并引入了多级流水线、超标量执行和64位运算单元等技术,显著提升了芯片的性能和功能。

龙芯II型在国内市场上取得了一定的成功,并逐渐开始应用于一些领域的高性能计算机系统中。

第三阶段:龙芯III型龙芯III型是龙芯芯片的第三代产品,研发工作于2009年开始,并于2011年推出。

与前两代产品相比,龙芯III型采用了更为先进的65纳米工艺制造,大大提升了芯片的性能和能效。

此外,龙芯III型还引入了全新的多核技术,具备2到16个处理核心,支持更高的并行计算能力和多任务处理能力。

这使得龙芯芯片在服务器、超级计算机等领域的应用得到了进一步的拓展。

第四阶段:龙芯IV型龙芯IV型是龙芯芯片的第四代产品,研发工作于2014年开始,目前仍在进行中。

龙芯IV型的最大特点是采用了更为先进的28纳米工艺制造,进一步提升了芯片的性能和能效。

该芯片还将应用更强大的多核技术,预计最高可支持64个处理核心。

龙芯IV型将继续拓展芯片的应用领域,为中国的高性能计算和人工智能发展提供更强大的支持。

未来发展龙芯芯片的未来发展将继续致力于提升技术水平和性能,推出更先进的产品。

研发团队将继续改进芯片的核心架构和制造工艺,不断提高性能、能效和可靠性。

龙芯及嵌入式介绍_V4.0

龙芯产品-芯片系列

龙芯2F • • • • • • 800MHz-1GHz@90nm,5100万晶体管 64位,MIPS III兼容,龙芯媒体扩展 四发射超标量结构,高效的乱序执行流水线 低功耗设计(3-5w) 性能高于1GHz的Pentium III。 应用于网络安全、工控、数控等领域

龙芯2G • 1.0GHz@65nm • DDR2/3, HT1.0, PCI, LPC, SPI, UART等 • 应用于高性能桌面 龙芯2H • • • • 单芯片SOC解决方案 支持高清音视频1080P解码 集成2D/3D GPU 集成DDR2/3、PCI-E、HT、SATA2.0、USB2.0、GMAC 可应用于:PC、数控机床、金融终端、网络安全等

我国由于缺少自主的 CPU技术和产业,信息 业严重受制于人,国 家安全受到威胁

我国的电子工业利润 率只有3%,武器装备 面临后门和禁运

产业化进展

建立现代企业治理架构 龙芯全国产业布局

产业环境 市场推广 上下游合作企业 达到上百家,产 业环境初步建立

产品线

成立公司 北京市牵头成 立龙芯产业化 核心企业,融 资2亿元到位

龙芯1B芯片与主流arm芯片对比

功能 处理器

龙芯LS1B

龙芯LS232 双发射 300MHz

TI AM1808

ARM926EJ-S 单发射 375MHz/ 456MHz DDR2 16bit 156MHz 168KB RAM USB1.1 X1,USB2.0 X1(OTG) 百兆X1/MII RMII 支持 9 X 16bit X3 X2 X2 X2 无 无 MMC、SD 无 X1 X1音频, X1视频 无 361 BGA

龙芯产品-参考方案

◆ Loongson——2F 6U CPCI主板 —龙芯2F处理器(3W@800MHZ) — 8*DDR2内存颗粒,容量1GB,DDR2 533; — PLX6254,支持透明和非透明模式; — 4Mbit BootROM,并外扩32MB NOR Flash; —支持LVDS显示,最大分辨率可达1600X1200; — PCI总线32bit/33MHz — 1个VGA接口、双千兆网口、PS2接口支持前面 板或背板输出;前面板输出1个USB2.0,背板支持3 个USB2.0;前面板输出1个单功能RS232接口,背板 支持2个RS232/RS422/RS485接口 — 板载1个CF卡口, 1个软驱接口,1个并口; —可扩展性:支持1个Single Size的PMC卡, —支持高可用热插拔功能。 符合P1386.1/Draft2.4规范 符合PICMG 2.0R3.0规范 符合PICMG 2.16R1.0规范 应用于高端工业控制等领域(如:数控机床)

龙芯cpu发展历程

龙芯cpu发展历程龙芯CPU是中国自主研发的一款处理器芯片,其发展历程可以追溯到上世纪90年代。

在那个时候,中国的计算机产业还相对薄弱,主要依赖进口的处理器芯片。

为了摆脱对外国技术的依赖,中国开始了自主研发处理器的探索。

1997年,中国科学院计算技术研究所成立了“龙芯计划”,旨在研发一款具有自主知识产权的处理器芯片。

经过多年的努力,2002年,龙芯CPU的第一代产品问世。

这款处理器采用了自主设计的指令集架构,性能相对较低,但标志着中国在处理器领域取得了重要突破。

随着技术的不断进步,龙芯CPU逐渐迎来了发展的机遇。

2004年,龙芯CPU的第二代产品发布,性能得到了显著提升。

这款处理器在国内外市场上获得了一定的认可,被广泛应用于高性能计算、服务器等领域。

2008年,龙芯CPU的第三代产品问世。

这款处理器在性能、功耗和可靠性方面都有了重大突破,成为当时国内最先进的处理器之一。

龙芯CPU的应用范围也进一步扩大,涉及到了移动设备、嵌入式系统等领域。

2011年,龙芯CPU的第四代产品发布。

这款处理器在性能上达到了国际先进水平,具备了与国外同类产品相媲美的竞争力。

龙芯CPU开始在国内市场上与国外品牌展开竞争,逐渐获得了一定的市场份额。

随着时间的推移,龙芯CPU的发展步伐越来越快。

2015年,龙芯CPU的第五代产品发布,性能再次得到了提升。

这款处理器在高性能计算、人工智能等领域展现出了强大的计算能力,成为中国自主研发的处理器的代表之一。

如今,龙芯CPU已经成为中国计算机产业的重要组成部分。

它不仅在国内市场上取得了一定的成功,还开始向国际市场拓展。

龙芯CPU的发展不仅推动了中国计算机产业的进步,也为中国在全球科技竞争中赢得了一席之地。

然而,龙芯CPU的发展之路并不平坦。

在技术上,龙芯CPU仍然面临着与国外品牌竞争的挑战。

在市场上,龙芯CPU还需要进一步提升品牌知名度和市场份额。

为了实现长期发展,龙芯CPU需要继续加大研发投入,提高技术创新能力,不断提升产品性能和质量。

【计算机研究与发展】_龙芯2处理器_期刊发文热词逐年推荐_20140728

科研热词 龙芯2号 龙芯2处理器 龙芯2号微处理器 龙芯2 高速缓存 评估方法 芯片组 自适应 栈 快速地址计算 微线程 带宽 同时多线程 同时多微线程 北桥 功耗建模 功耗 写失效 写分配 内存控制器 体系结构 pci cache asic设计

推荐指数 2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

2011年 序号 1 2 3 4 5 6 7 8 9 10

科研热词 龙芯异构多核 龙芯处理器 龙芯3号处理器 锁l2cache 软tlb 超页技术 核间切换开销 寄存器重命名 存储单元 tlb

推荐指数 1 1 1 1 1 1 1 1 1 1

2012年 序号 1 2 3 4 5 6 7 8

2006年 序号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35

科研热词 龙芯2号处理器 非阻塞的cache 门级电路仿真器 链接后优化 输入向量控制 软错误 软tlb 转移猜测 超标量流水线 结构验证 漏电功耗 浮点部件 模拟仿真 有界模型检验 故障注入 性能分析 形式验证 形式化验证 寄存器重命名 容错处理器 字级模型检验 多媒体指令集 处理器设计 可靠性设计 动态调度 功能验证 功能部件设计 低功耗设计 乱序执行 uncache accelerate satcnf load指令猜测执行 glto cache别名 *phdd

推荐指数 3 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

2007年 序号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 ห้องสมุดไป่ตู้5 16 17 18 19 20 21 22 23 24

龙芯2E嵌入式处理器模块设计

块。该模块能独立工作 , 同时又具有 一定的扩展功能 , 可作为 其它嵌入式系统的子卡应 用, 以简化和方便嵌入式系统的开发

工作 。 系统框架如 图 1 所示 。系统核心为 L ogo E处理器 , on sn 2

算技术研究所最新发布 的一款 6 位片 内集成 D R内存控 制 4 D 器的高性能处理器 ,国内首个 采用了 9 M S 设计工 0mC O 的 n 艺 。晶体管数量为 470万个 ,面积 3 m ,典型工作频 率 0 5m : 70MH 下的实测功耗 为(~ ) 非常适合应用于高端 嵌入式 5 z 5 7 W,

,

吴 W 少 U

, ∞

史

。

咄

岗 ,

U

∞

1 国科学院 计算技术研究所 , 冲 北京 10 8 000

2中国科学院 研究生院 , . 北京 10 8 00 0

G

g

3 . 首都师范大学 , 北京 103 007

1 n t u f C m u n eh ooy C i s A a e fS in e , e ig 1 0 8 , hn . s tt o o p t g T c n l , hn e c d my o ce c s B i n 0 0 C ia I i e i g e j 0

d sg ot b i g . a o k a o e n b a d f s n u e a s ra ot a t e t r i a . l h s s l ie n w x a — e in n r r eI c n w r l n o o r a h a d s ei l p r s h e n 1 t as h d t l m I o a mal z a d t o e p n s so n ef c : C a d OC B w ih r u e a d u h e a d n t e mb d e s se .h k y e h o o is f t e in i t r e P I n L AL US h c a e s d s a g t r c r i o h r e e d d y t ms e e tc n l ge o h a T

龙芯二进制 latex

龙芯二进制是一种处理器架构,它与LaTeX没有直接的关系。

LaTeX是一种基于TeX的排版系统,用于制作高质量的技术和科学文档。

它使用标记语言来描述文档的结构和样式,并生成PDF、DVI等格式的输出。

如果您想在LaTeX中使用龙芯二进制指令集进行编码或调试,您需要使用汇编语言编写程序,并将其编译为二进制文件。

然后,您可以在LaTeX文档中插入这些二进制文件,并在需要时调用它们。

但是,请注意,这需要对汇编语言和LaTeX都有深入的了解,并且可能需要一些额外的工具和设置才能实现。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

主流CPU的谱系和龙芯的位置

440 / 750 / 970 / Power4+

低 能 耗

Low Power (mW)

MIPS

MIPS

龙芯

XScale ARM Low

龙芯

IA32

龙芯

IA64

High Performance (GHz)

高 性 能

Mid

High

5

龙芯处理器Roadmap

SPEC分值 分值 1000

3

部分处理器的SPEC CPU2000值

处理器

UltraSPARC-II UltraSPARC-III

参数

300MHz, 16K+16K(L1),L2 , 900MHz, 32K+64K(L1), 8M(L2) 500MHz, 64K+64K(L1), 4M(L2) 1001MHz, 64K+64K(L1), 8M(L2) 500MHz, 32K+32K(L1), 8M(L2) 500MHz, 32K+32K(L1), 8M(L2) 1GHz, 16K+16K(L1), 256K(L2,on) 2GHz, 12K+8K(L1), 256K(L2,on) 550MHz, 512K+1M(L1) 875MHz, 0.75M+1.5M(L1) 450MHz, 64K+32K(L1), 8M(L2)

龙芯2号研发历程

Version 2A Physical Design ASIC, 0.18um, 250MHz ASIC, 0.18um, 300MHz Tiled placement, 2B1

crafted cell, 0.18um,

Architecture Features 64-bit, 4-issue, OOO, 32KB+32KB L1 64-bit, 4-issue, OOO, 32KB+32KB L1 reduced queue size Split Read, BTB, RAS, Off-chip L2 9-stage pipeline, 64KB+64KB L1, paired single FP Multiply-Add, SMP, On-chip L2, Prefetch, Pico-architecture tuning DDR controller, interconnect, IO

龙芯3.2 龙芯 0.13-0.09um, 64位,多线程 位 龙芯3.3 龙芯

龙芯3 龙芯

800

2GHz的P4 的 SPEC分值在 分值在 600到750之间 到 之间 龙芯2.3 龙芯 0.18-0.13um, 64位, 4发射 位 发射 龙芯2.2 龙芯

600

400

龙芯2 龙芯

1.3GHz的P4 的 实测分值为 定点342 定点 浮点272 浮点

Via C3 Godson 2C

龙芯2号处理器设计

中国科学院计算技术研究所 CPU组 组 2004.11.10

1

内容提要

基本情况介绍

研究目标 研究目标 目前进展 目前进展 近期工作计划

关键技术

结构设计 处理器验证 物理设计

2

龙芯2号研究目标

研究目标

研制出具有自主知识产权,达到国际先进水平的64位高性 研制出具有自主知识产权,达到国际先进水平的 位高性 能通用CPU芯片和配套的 以及服务器系统样机. 芯片和配套的PC以及服务器系统样机. 能通用 芯片和配套的 以及服务器系统样机 建立开发平台,设计方法,研究队伍. 建立开发平台,设计方法,研究队伍.

龙芯2号进展

已经完成多次流片,包括0.18um的定型芯片 已经完成多次流片,包括 的定型芯片

2002年7月开始概念结构设计,10月开始详细结构设计 年 月开始概念结构设计 月开始概念结构设计, 月开始详细结构设计 2003年10月17日首片成功运行 年 月 日首片成功运行 2004年9月28日0.18um定型芯片的试流片运行 年 月 日 定型芯片的试流片运行

Tapeout Time 2003.07.13

Performance Failed 3X-5X Godson-1

2B

2003.08.13

2004.03.07

2X Godson-2B

350-400MHz 2C More custom, 0.18um, 450-500MHz 0.13um, Cu, 600-800MHz 0.13um, Cu, more custom, 800-1000 MHz Based on Godson2 IP

基本完成院重大专项和863重点项目 重点项目 基本完成院重大专项和

实测性能是龙芯1号的 倍以上 实测性能是龙芯 号的10倍以上 号的 全面超过VIA的性能,实测性能达到 的性能, 全面超过 的性能 实测性能达到PIII的水平 的水平 完全可以满足桌面的应用

系统设计进展

完成PC和服务器主板的设计, 完成 和服务器主板的设计,正在进行笔记本主板的联调 和服务器主板的设计 64位北桥设计,已经完成 位北桥设计, 位北桥设计 已经完成RTL设计 设计 完成MIPS64 Linux kernel 和Debian的完整发行版的移植,包 完成 的完整发行版的移植, 的完整发行版的移植 8等 媒体播放, 括xwindows, Open Office, Mozilla, 媒体播放 Email, Xpdf等

200

0.18um, 32位 位 单发射 龙芯1.2 龙芯 龙芯1.3 龙芯 以300MHz UltraSparc II为基准 为基准

龙芯1 龙芯

时间 2003 2004 2005 2006 2007

6

2001

2002

龙芯2号处理器特点

高性能

64位,四发射,乱序执行 位 四发射, 64KB+64KB片内一级 片内一级Cache, 1MB-8MB片外二级 片外二级Cache 片内一级 , 片外二级 IEEE 754兼容浮点部件,专门的媒体支持 兼容浮点部件, 兼容浮点部件 双精度浮点运算10亿次 亿次/秒 单精度浮点运算20亿次 亿次/秒 双精度浮点运算 亿次 秒,单精度浮点运算 亿次 秒 SPEC CPU2000实测性能相当于 实测性能相当于500MHz-1GHz的PIII系列 实测性能相当于 的 系列 完全满足桌面应用的要求

样机系统指标

MIPS兼容,64位 超流水,4发射 MIPS兼容,64位,超流水,4发射,乱序执行 发射, 兼容 流片主频500MHz以上,SPEC CPU2000值为 分以上, 以上, 值为300分以上, 流片主频 以上 值为 性能与1GHz以上的 以上的PIII或PIV相当 性能与 以上的 或 相当

10

龙芯1号和龙芯2号

11

分值 100 120 140 160 20 40 60 80 0

SPEC初步性能比较(1)

Godson 2Cvs1A-ref-origin

266MHz Godson-1 vs. 270MHz Godson-2C 500MHz的龙芯 号性能是龙芯 号性能的 倍以上 的龙芯2号性能是龙芯 号性能的10倍以上 的龙芯 号性能是龙芯1号性能的

Godson 1A Godson 2C

12Βιβλιοθήκη 分值 120 140 160 100 20 40 60 80 0

SPEC初步性能比较(2)

Godson 2CvsVia C3-ref-origin

733MHz Via-C3 vs. 270MHz Godson-2C 500MHz的龙芯 号性能将大大超过 的龙芯2号性能将大大超过 的龙芯 号性能将大大超过VIA的处理器 的处理器

通过封装改进和工艺调整,正常电压范围达到 通过封装改进和工艺调整,正常电压范围达到 500MHz-600MHz

改进封装:通过散热片可以散 改进封装:通过散热片可以散3w-4w 沟道宽度: 沟道宽度:0.16um或0.17um 或 阈值电压: 阈值电压:-5%或-10% 或 不用改gds2版图,SMIC已经开始加工 版图, 不用改 版图 已经开始加工

SPECfp2000 100 410 422 756 343 386 264 745 414 651 433 1158

4

Alpha 21264 Alpha 21264C MIPS R12000 MIPS R14000 Pentium III Pentium IV PA-8600 PA-8700+ Power3-II Power4+

采用0.18um CMOS标准单元工艺,500MHz 标准单元工艺 采用 标准单元工艺, 针对缓冲区溢出攻击的专门安全支持 MIPS兼容,支持 兼容, 兼容 支持LINUX, VxWorks, WinCE等主流操 等主流操 作系统 1350万晶体管,面积 万晶体管, 万晶体管 面积6.2mm*6.7mm 功耗: 功耗:2w-4w@500MHz 7 低成本: 套片<20美元 低成本:CPU+套片 套片 美元

2004.06-08

500-800MHz PIII 1.3-1.4GHz PIV 1.5-2.0GHz PIV TeraFLOPs CC-NUMA

2D

2004.09-12

2D1

2005.01-06

SOC

2006.01-06

9 Balance between frequency and architecture is most important

Godson-2C主频

已完成多次流片,目前为C方案(Godson-2C) 已完成多次流片,目前为 方案( ) 方案

是0.18um的定型芯片 的定型芯片

正常电压范围(1.8v±10%)主频为 ± 主频为400MHz-450MHz 正常电压范围 主频为

目前由于封装散热较小(只能散 目前由于封装散热较小(只能散1w-2w,实测 ,实测400MHz时 时 3w左右),因此降低电压运行在 左右),因此降低电压运行在90MHz*3或90MHz*4 左右),因此降低电压运行在 或