西安交大计算机组成_实验八

《计算机组成原理》学生实验报告

《计算机组成原理》学生实验报告(2011~2012学年第二学期)专业:信息管理与信息系统班级: A0922学号:10914030230姓名:李斌目录实验准备------------------------------------------------------------------------3 实验一运算器实验-----------------------------------------------------------7 实验二数据通路实验-------------------------------------------------------13 实验三微控制器实验--------------------------------------------------------18 实验四基本模型机的设计与实现------------------------------------------22实验准备一、DVCC实验机系统硬件设备1、运算器模块运算器由两片74LS181构成8位字长的ALU。

它是运算器的核心。

可以实现两个8位的二进制数进行多种算术或逻辑运算,具体由74181的功能控制条件M、CN、S3、S2、S1、S0来决定,见下表。

两个参与运算的数分别来自于暂存器U29和U30(采用8位锁存器),运算结果直接输出到输出缓冲器U33(采用74LS245,由ALUB信号控制,ALUB=0,表示U33开通,ALUB=1,表示U33不通,其输出呈高阻),由输出缓冲器发送到系统的数据总线上,以便进行移位操作或参加下一次运算。

进位输入信号来自于两个方面:其一对运算器74LS181的进位输出/CN+4进位倒相所得CN4;其二由移位寄存器74LS299的选择参数S0、S1、AQ0、AQ7决定所得。

触发器的输出QCY就是ALU结果的进位标志位。

QCY为“0”,表示ALU结果没有进位,相应的指示灯CY灭;QCY为“1”,表示ALU结果有进位,相应的指示灯CY点亮。

西安交通大学计算机组成原理实验报告

西安交通大学计算机组成原理实验报告姓名:***班级:物联网**学号:实验一存储器的访问与实现一、实验目的1、理解计算机主存储器的分类及作用;2、掌握ROM、RAM的读写方法。

二、实验原理存储器按存取方式分,可分为随机存储器和顺序存储器。

如果存储器中的任何存储单元的内容都可随机存取,称为随机存储器,计算机中的主存储器都是随机存储器。

如果存储器只能按某种顺序存取,则称为顺序存储器,磁带是顺序存储器,磁盘是半顺序存储器,它们的特点是存储容量大,存取速度慢,一般作为外部存储器使用。

如果按存储器的读写功能分,有些存储器的内容是固定不变的,即只能读出不能写入,这种存储器称为只读存储器(ROM);既能读出又能写入的存储器,称为随机读写存储器(RAM)。

实际上真正的ROM基本上不用了,用的是光可擦除可编程的ROM(EPROM)和电可擦除可编程的ROM(EEPROM)。

EEPROM用的越来越多,有取代EPROM之势,比如容量很大的闪存(FLASH)现在用的就很广泛,常说的U盘就是用FLASH做的。

按信息的可保存性分,存储器可分为非永久性记忆存储器和永久性记忆存储器。

ROM、EPROM、EEPROM都是永久记忆存储器,它们断电后存储内容可保存。

RAM则是非永久性记忆存储器,断电后存储器中存储的内容丢失。

随机读写存储器类型随机存储器按其元件的类型来分,有双极存储器和MOS存储器两类。

在存取速度和价格两方面,双极存储器比MOS存储器高,故双极存储器主要用于高速的小容量存储体系。

在MOS存储器中,根据存储信息机构的原理不同,又分为静态随机存储器(SRAM)和动态随机存储器(DRAM)。

静态随机存储器采用双稳态触发器来保存信息,只要不断电,信息就不会丢失;动态随机存储器利用记忆电容来保存信息,使用时只有不断地给电容充电才能使信息保持。

静态随机存储器的集成度较低,功耗也较大;动态随机存储器的集成度较高,功耗低。

现在计算机中,内存容量较大,常由动态随机存储器构成。

计算机组成原理实验参考答案(西南交大)

[原创]西南交通大学计算机组成实验参考答案注1、引脚分配依照EP3C40F780C8芯片注2、一定要参照实验指导书阅读此文实验一:多路数据选择器的设计f=((~sel)a)+((sel)b)当sel=0时,f=a,否则f=b。

引脚分配参考:a[3:0] AH12 AF14 AA8 AB8b[3:0] AF12 AG12 AA10 U8f[3:0] E24 F22 E22 F21sel: AC5实验二基于原理图方式的3-8译码电路的设计f0=(~en)+(~a)(~b)(~c)f1=(~en)+(~a)(~b)cf2=(~en)+(~a)b(~c)f3=(~en)+(~a)bcf4=(~en)+a(~b)(~c)f5=(~en)+a(~b)cf6=(~en)+ab(~c)f7=(~en)+abcen为使能端,低电平有效,高电平时输出全为1。

引脚分配参考:a: AH12,b: AF14,c: AA8,en: AC5f[7:0] F24 H24 H23 L23 L24 M24 J22 AE8实验三四位加法器设计实验思路:用Verilog HDL语言编写一位全加器,再用原理图方式用四个全加器组合实现四位加法器。

Adder.vmodule Adder(a, b, cin, cout, sum);input a, b, cin;output cout, sum;assign {cout, sum}=a+b+cin; endmodule原理图:{cout, sum}=a+b+cincin为进位输入,cout为进位输出。

引脚分配参考:a[3:0] AH12 AF14 AA8 AB8b[3:0] AF12 AG12 AA10 U8sum[3:0] E24 F22 E22 F21cin: AC5,cout: F24实验四:七段LED数码管显示译码器设计本实验使用Verilog HDL实现。

module Exp4(f, clk, rst, in, out, sel);input [15:0]in; //输入input f, clk, rst; //计数开关,时钟,置零开关output reg[7:0]out; //数码管输出output reg[2:0]sel; //数码管3-8译码器输出reg[15:0]counter;reg[3:0]data;reg clk_alt;reg[9:0]l;//change frequency 变频段always @(posedge clk)beginif(l>=1023)l=0;else l=l+1;clk_alt=l[2];end//select 选择在哪一个数码管显示always @(posedge clk)beginsel=sel+1;if(sel>=4)sel=0;case(sel)0:data=counter[3:0];1:data=counter[7:4];2:data=counter[11:8];3:data=counter[15:12];endcaseend//count and reset 计数和清零always @(posedge clk_alt or posedge rst)beginif (rst==1) counter=0;else if (f==1) counter=in;else counter=counter+1;end//translate 译码段,此处可以使用二进制或十六进制,后面的实验同,不再赘述。

实验八 指令调度和延迟分支

--

2019

学年

第

2

学期

课程名称计算机组成原理

实验序号实验8

实验项目指令调度和延迟分支

实验地点软件开发教学实训平台

实验学时2实验类型验证性

指导教师···

专业计算机科学与技术班级2017级计算机(2)

学号···姓名玄月二五

2019年3月

一、实验目的及要求

1、认识和学习指令调度;

2、了解调度指令延迟分支。

2、调度指令延迟分支的三种方法:为防止事故扩大,厂站值班员可不待调度指令自行进行以下紧急操作,但事后应立即向调度汇报:

(1)对人身和设备安全有威胁的设备停电;

(2)将故障停运已损坏的设备隔离;

(3)当厂站用电部分或全部停电时,恢复其电源;

(4)现场规程规定的可以不待调度指令自行...

四、实验结果分析

操作令又分为:单项操作令、逐项操作令和综合操作令。

a.单项操作令:值班调度员向运行值班员发布的单一一项操作的指令。

b.逐项操作令:值班调度员向运行值班员发布的操作指令是具体的逐项操作步骤和内容,要求运行值班员按照指令的操作步骤和内容逐项进行操作。

c.综合操作令:值班调度员给运行值班员发布的不涉及其他厂站配合的综合操作任务的调度指令。其具体的逐项操作步骤和内容,以及安全措施,均由运行值班员自行按规程拟订。

二、实验内容:

1、指令调度概念

(1)概念

(2)分类

2、调度指令延迟分支

三、实验过程及工件原理(实验步骤)

1.指令调度

(1)概念:是指电网调度机构值班调度员对其下级值班调度员或调度管辖厂站值班员发布有关运行和操作的指令。

(2)分类

1口头令:由值班调度员口头下达(无须填写操作票)的调度指令。

西安交大计算机组成原理—习题解答(第八章)

.

Q D C1 +5V

。. .

。

&

。 Q R。

.。

Q D C2 Q R

.

Q D C3

. .

1 。

。

。 Q R。

.

Q D C4

. .

。 Q R。

。

&

CLR

。 S D

Q C5

。

Q

.

10MH 脉冲源

.

Copyright ©2012 Computer Organization Group. All rights reserved.

第八章 8.5 ⑵ 解 时序产生器

⑵ 时序产生器逻辑图如下: 节拍译码逻辑如下: T1=C1·/C2 T2=C2 T3=/C1

+5V T3 & T1 & T2 &

Q D C1

. 。.

。

&

。 Q R。

. . 。

Q D C2 Q R

. .

1 。

。

Q D C3

。 Q R。

。

&

CLR

。 S D

Q C4

。

Q

Copyright ©2012 Computer Organization Group. All rights reserved.

第八章 8.2

8.2请分别分析用硬布线和门阵列两种组合逻辑控制单 元设计技术设计控制器的特点。 解:这两种技术采用的设计方法一样,均为组合逻辑 设计技术,但实现方法不一样。硬布线控制单元基于 传统的逻辑门电路组合逻辑设计方法来构建控制单元 ,门阵列控制器则采用集成度更高、性能更好的门阵 列芯片,利用硬件描述语言等工具编程完成逻辑设计 、通过烧制实现门阵列芯片内部的电路制作。

西安交大计算机组成_实验八

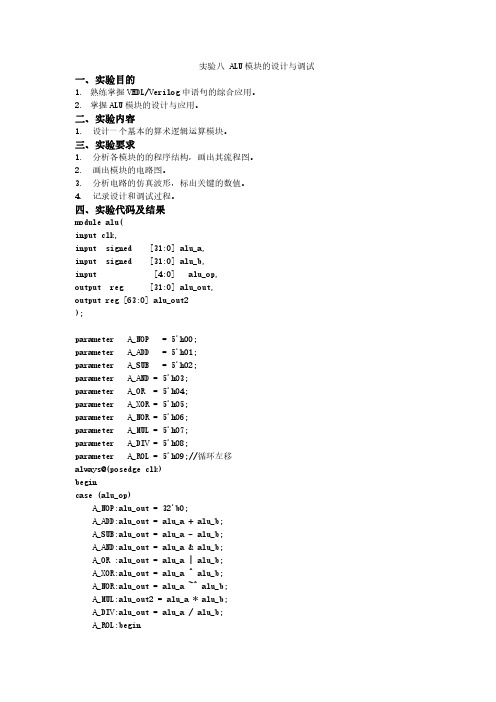

实验八ALU模块的设计与调试一、实验目的1.熟练掌握VHDL/Verilog中语句的综合应用。

2.掌握ALU模块的设计与应用。

二、实验内容1.设计一个基本的算术逻辑运算模块。

三、实验要求1.分析各模块的的程序结构,画出其流程图。

2.画出模块的电路图。

3.分析电路的仿真波形,标出关键的数值。

4.记录设计和调试过程。

四、实验代码及结果module alu(input clk,input signed[31:0]alu_a,input signed[31:0]alu_b,input[4:0]alu_op,output reg[31:0]alu_out,output reg[63:0]alu_out2);parameter A_NOP=5'h00;parameter A_ADD=5'h01;parameter A_SUB=5'h02;parameter A_AND=5'h03;parameter A_OR=5'h04;parameter A_XOR=5'h05;parameter A_NOR=5'h06;parameter A_MUL=5'h07;parameter A_DIV=5'h08;parameter A_ROL=5'h09;//循环左移always@(posedge clk)begincase(alu_op)A_NOP:alu_out=32'b0;A_ADD:alu_out=alu_a+alu_b;A_SUB:alu_out=alu_a-alu_b;A_AND:alu_out=alu_a&alu_b;A_OR:alu_out=alu_a|alu_b;A_XOR:alu_out=alu_a^alu_b;A_NOR:alu_out=alu_a~^alu_b;A_MUL:alu_out2=alu_a*alu_b;A_DIV:alu_out=alu_a/alu_b;A_ROL:beginalu_out[31:0]={alu_a[30:0],alu_a[31]};endendcaseendEndmodule仿真代码:module sim();reg[31:0]alu_a;reg[31:0]alu_b;reg clk;reg[4:0]alu_op;wire[31:0]alu_out;wire[63:0]alu_out2;alu t(clk,alu_a,alu_b,alu_op,alu_out,alu_out2);always begin#50clk=~clk;endinitial beginclk<=1;#55alu_a<=32'h01;alu_b<=32'h11;alu_op<=5'h01;#55alu_op<=5'h09;#110alu_op<=5'h07;#110alu_op<=5'h08;endEndmodulea=01,b=11,分别相加,将a循环左移一位,相乘,相除,相乘结果保存到[63:0]alu_out2中。

西安交大计算机系统结构实验报告.

《计算机系统结构课内实验》实验报告第一次实验:记分牌算法和Tomasulo算法第二次实验:cache性能分析班级:物联网21姓名:李伟东学号:2120509011日期:2015.5.21第一次实验:记分牌算法和Tomasulo算法一、实验目的及要求1. 掌握DLXview模拟器的使用方法;2. 进一步理解指令动态调度的基本思想,了解指令动态调度的基本过程与方法;3. 理解记分牌算法和Tomasulo算法的基本思想,了解它们的基本结构、运行过程;4. 比较分析基本流水线与记分牌算法和Tomasulo算法的性能及优缺点。

二、实验环境DLXview模拟器三、实验内容1.用DLX汇编语言编写代码文件*.s(程序中应包括指令的数据相关、控制相关以及结构相关),以及相关的初始化寄存器文件*.i和数据文件*.d;2.观察程序中出现的数据相关、控制相关、结构相关,并指出三种相关的指令组合;四、实验步骤将自己编写的程序*.s、*.i、*.d装载到DLXview模拟器上,(1)分别用基本流水线、记分牌算法和Tomasulo算法模拟,针对每一种模拟做如下分析:①统计程序的执行周期数和流水线中的暂停时钟周期数;②改变功能部件数目重新模拟,观察并记录性能的改变;③改变功能部件延迟重新模拟,观察并记录性能的改变;论述功能部件数目、功能部件延迟对性能的影响。

(2)记录运行记分牌算法时的功能部件状态表和指令状态表;(3)记录运行Tomasulo算法时的指令状态表和保留站信息;五、实验结果1)基本流水线原始即加法延迟2,乘法延迟5,实验结果显示该段程序运行了11个时钟周期增加了一个除法器。

加法器延迟2,乘法器延迟5,除法器延迟19。

实验结果显示该段程序运行了11个时钟周期。

增加除法器对程序的执行无影响。

加法器延迟2,乘法器延迟6,无除法器。

实验结果显示该段程序运行了12个时钟周期乘法器的延迟对程序执行有有影响。

加法器延迟1,乘法器延迟5。

计算机组成原理实验八简单模型计算机实验

计算机组成原理实验八简单模型计算机实验关键信息项:1、实验目的2、实验设备3、实验原理4、实验步骤5、数据记录与分析6、注意事项7、故障处理8、实验结果评估标准11 实验目的本实验旨在通过构建和操作简单模型计算机,深入理解计算机组成原理中的核心概念,包括数据存储、运算处理、指令执行等,培养学生的实际动手能力和对计算机系统的综合理解能力。

111 具体目标1111 掌握简单模型计算机的基本结构和工作原理。

1112 熟悉各种指令的编码和执行过程。

1113 能够运用所学知识设计和实现简单的计算任务。

12 实验设备121 硬件设备计算机主机、实验箱、连接线等。

122 软件工具特定的模拟软件、编程环境等。

13 实验原理131 模型计算机结构包括运算器、控制器、存储器、输入设备和输出设备等主要部件,以及它们之间的连接和协同工作方式。

132 指令系统定义了各种操作指令的格式、功能和编码方式。

133 数据存储与传输说明数据在存储器中的存储方式和在各部件之间的传输机制。

14 实验步骤141 连接实验设备按照正确的方式将计算机主机与实验箱等设备进行连接,并确保连接稳定可靠。

142 启动软件工具打开相应的模拟软件和编程环境,进行初始化设置。

143 设计指令序列根据实验要求,设计一系列的指令来完成特定的计算任务。

144 输入指令到模型计算机通过编程环境将指令输入到模型计算机的存储器中。

145 启动模型计算机运行设置相关参数,启动模型计算机执行指令序列。

146 观察运行过程和结果密切观察模型计算机在执行指令过程中的各种状态变化,以及最终的输出结果。

15 数据记录与分析151 记录实验过程中的关键数据包括指令的执行时间、存储器的状态变化、运算结果等。

152 对数据进行分析对比预期结果,分析实验数据的准确性和合理性,找出可能存在的偏差和错误原因。

16 注意事项161 设备操作规范严格按照设备的操作说明进行连接和使用,避免因不当操作造成设备损坏。

西安交大自动化专业XXXX计算机控制专题实验

计算机控制专题实验一、实验目的掌握计算机控制系统各个环节的设计以与系统的组成。

通过实验使学生能够较熟练地设计计算机控制系统的各个环节和完整的系统,熟练掌握系统的调试和控制器参数的整定方法。

巩固和深化理论教学内容,培养学生的工程实践技能,综合运用所学专业知识解决实际问题的能力。

二、实验设备1.计算机一台2.数据采集卡PCI-9112卡一块,端子板LD-9188一块与电缆3.温度控制箱一套4.WindowsXP系统,Matlab软件,ADLINK软件包。

(Labview软件) 三、实验内容与要求1.了解温度控制系统的构成,熟悉各环节的工作原理。

掌握MatlabGUI 设计系统监控画面与编程方法。

2.熟练应用MatlabGUI设计系统监控画面,要求监控画面中有:1)控制系统名称“温度监控系统”与“设计人:×××”,2)显示实时温度控制曲线,横坐标为时间单位秒,纵坐标为温度,X围为0~100C°,加网格,3)数字显示实时温度,与控制输出,4)显示控制棒图,标记温度设定值,实时温度,控制输出,5)设定值温度与PID三个参数,并可以实时修改,6)可选的优化方法,7)有运行,停止,保存,结束等按钮功能。

3.设计编写采样、滤波、PID控制与优化算法等相关程序。

4.完成PID参数整定,调试出稳定的温度控制系统,观察并分析过程控制的PID整定规律。

保存最佳的整定参数与控制曲线图。

四、实验硬件与软件说明1.数字采集卡:数据采集卡PCI-9112插在主板上的PCI插槽中,包含数字信号与模拟信号两种。

模拟信号有两种模拟输入:16路单端模拟输入(A0~A15)和8路差分模拟输入(AL0~AL7/AH0~AH7),2路模拟量输出(AO1和AO2)。

引脚图见图1。

图1 16路单端模拟输入和8路差分模拟输入引脚图引脚说明:(模拟输入/输出与定时计数器)AI n—―Analog Input Channel n (single-ended)AIH n—―Analog High Input Channel n (differential)AIL n—―Analog Low Input Channel n (differential)ExtRef n—―External Reference Voltage for D/A CH nAO n—―Analog Output Channel nExtCLK—―External Clock InputExtTrig——External Trigger SignalCLK——Clock input for 8254GATE——Gate input for 8254COUT n——Signal output of Counter nV.ERF——Voltage ReferenceA.GND——Analog GroundGND——Ground实验中采用单端输入与输出,模数转换通道选用A/D的0号通道和数模转换通道选用D/A的0号通道。

西安交通大学组成专题实验报告汇编

计算机组织与结构专题实验报告 MIPS 单周期处理器的设计学生姓名 赵荣建 专业班级 计算机45班 学 号 2140505119 指导教师 姜欣宁 完成日期 2017-05-09一.实验目的根据所学的CPU组成原理,自主设计一个MIPS32位的单周期处理器。

二.设计方案参照计算机组成原理教材上的MIPS32位处理器的工作原理。

1.构建数据通路取指周期:a.从指令寄存器PC输出端得到地址b.送地址到指令存储器IM地址端Ac.从指令存储器IM的数据端RD得到指令d.计算下地址:通过运算器,PC+4形成下地址,送回到PC。

2. .MIPS 寄存器集:定义了32个32位的寄存器3.MIPS三种指令格式:R-类型、I-类型和J-类型R-类型格式:* 所有指令操作吗OP都是0;特定操作由funct决定。

* 机器语言指令中,字段分配格式如上图;前两个寄存器rs、 rt 是源寄存器,rd是目的寄存器。

而在汇编语言格式中,第一个寄存器是目的寄存器。

如:add $t0,$s4,$s5 #[rd]=[rs]+[rt],[t0]=[s4]+[s5];I-类型格式:* 指令含4个字段;op, rs, rt 和 imm* 有两个寄存器操作数和一个16位立即数操作数,一些指令中,rt也可作为源寄存器。

J-类型格式:* 有一个26位立即数操作数,扩展后形成目的地址。

4.算逻单元ALU 的设计ALU 工作原理图* 两级控制:通过系统控制器(Control )B A和运算器控制器(ALU Control)产生ALU的控制信号:ALUoper* ALU控制信号对照表:5.单周期数据通路的构建1)构件:PC、指令存储器、寄存器文件RF和数据存储器; 2)取指令的过程:PC→IM: A/RD3)取源操作数的过程:IM:RD→RF:A1/RD1。

4)立即数的符号扩展的过程:IM:RD(Instr:15:0)→Sign Extend(15:0→Signimm31:0);其中Signimm15:0=Instr15:0, Signimm31:16=Instr155)存储器地址计算:6)向寄存器文件写入数据RegWrite信号被置成1,写入过程在时钟周期最后的时钟上升沿完成。

计算机组成原理实验报告

《计算机组成与系统结构》实验指导书计算机与信息工程系2013年7月目录实验概述 .......................................................... 实验项目一专用寄存器(1)........................................... 实验项目二通用寄存器.............................................. 实验项目三专用寄存器(2)........................................... 实验项目四数据输出/移位门......................................... 实验项目五微程序计数器............................................ 实验项目六运算器.................................................. 实验项目七程序计数器.............................................. 实验项目八存储器读写.............................................. 实验项目九微程序存储器读写........................................ 实验项目十中断.................................................... 实验项目十一模型计算机设计........................................实验概述一、实验目的1.加深对讲授内容的理解,通过实验来掌握计算机系统原理。

熟练地掌握计算机中每个部件的电路设计方法并完成调试和分析结果。

2.熟悉所用的仿真软件。

学会使用仿真软件上机调试电路。

计算机15 西安交通大学 组成原理 最终报告

计算机组织与结构专题实验报告 ——实验设计总体实现学 院 电信学院指导老师 姜新宁 专业班级 计算机15 组员姓名 高君宇组员学号 2110505112邮 箱 309852008@目录一、实验目的 (3)二、实验要求 (3)三、实验原理 (3)3.1指令集: (3)3.2控制器的设计: (4)3.3通用寄存器组 (6)3.4存储器 (6)3.5总体数据通路设计: (6)四、设计思路与源代码 (7)4.1通用寄存器组regfile (9)4.2取指部分instru_fetch (9)4.3指令译码部分decoder_unit (10)4.4执行部分exe_unit (11)4.5存储器部分memory_unit (12)4.6程序包exp_cpu_components (12)4.7顶层设计实体exp_cpu (12)五、实验步骤 (13)六、实验现象 (13)七、实验心得 (16)八、程序源代码 (16)一、实验目的设计16位串行CPU,实现算术和逻辑运算指令、转移指令、访存指令、堆栈指令和控制指令。

二、实验要求根据系统的设计方案,直接利用硬件描述语言vhdl,编程完成,并调试、实现实验要完成的工作主要包括:指令系统的设计,FPGA-CPU的整体结构设计及其细化,逻辑设计的具体实现(VHDL语言程序的编写),软件模拟,以及硬件调试。

三、实验原理3.1指令集:图1-一个指令的执行流程图指令系统在整个计算机系统结构设计中处于核心的地位。

指令系统设计不仅直接关系到计算机系统硬件的设计,而且必然影响后期系统软件的设计。

1)指令类型:算数类:ADD SUB 逻辑类:AND OR寄存器访问类:SET MOV 存储器访问类:LOAD STORE条件转移类:BEQ 无条件转移类:JMP2)指令格式:字长:使用固定长度16位操作码:为方便使用及操作,规定为4位操作数:为使用多个操作数,每个操作数规定为1至3位3)指令系统依据MIPS指令集设计,指令字长为16位,整个指令系统包括了运算指令、转移指令和存储指令等三类。

西安交通大学组成专题实验报告

西安交通大学组成专题实验报告计算机组织与结构专题实验报告 MIPS单周期处理器的设计学生姓名赵荣建专业班级计算机45班学号2140505119 指导教师姜欣宁完成日期 2021-05-09一.实验目的根据所学的CPU组成原理,自主设计一个MIPS32位的单周期处理器。

二.设计方案参照计算机组成原理教材上的MIPS32位处理器的工作原理。

1.构建数据通路取指令指令译码指令执行存储器访问结果写回取指周期:a.从指令寄存器PC输出端得到地址b.送地址到指令存储器IM地址端Ac.从指令存储器IM的数据端RD得到指令d.计算下地址:通过运算器,PC+4形成下地址,送回到PC。

2. .MIPS 寄存器集:定义了32个32位的寄存器3.MIPS三种指令格式:R-类型、I-类型和J-类型R-类型格式:* 所有指令操作吗OP都是0;特定操作由funct决定。

* 机器语言指令中,字段分配格式如上图;前两个寄存器rs、 rt是源寄存器,rd是目的寄存器。

而在汇编语言格式中,第一个寄存器是目的寄存器。

如:add $t0,$s4,$s5 #[rd]=[rs]+[rt],[t0]=[s4]+[s5]; I-类型格式:* 指令含4个字段;op, rs, rt 和 imm* 有两个寄存器操作数和一个16位立即数操作数,一些指令中,rt也可作为源寄存器。

J-类型格式:* 有一个26位立即数操作数,扩展后形成目的地址。

4.算逻单元ALU的设计<<210Add<<2JumpMemToReg4Add01ControlMemReadMemWriteBranchALUopALUsrcRegWriteIn structionMemoryPC0R1Rdata132R21RegisterFileW1WdataALU32zeroResult32AddrRdata20212DataData0321Memory3Wdata{15~0}sign32 extend2ALUcontrol6{5~0}ALU工作原理图BA321zeroALU3232Result* 两级控制:通过系统控制器(Control)3ALUoperFunc6ALUcontrol2ALUop 和运算器控制器(ALU Control)产生 ALU的控制信号:ALUoper* ALU控制信号对照表:ALUop Func(来自R型指令的func字段)操作 ALUop1 ALUop2 F5 0 0 1 1 1 1 1 0 1 × × × × × × × × × × × × F4 × × × × × × × F3 × × 0 0 0 0 1 F2 × × 0 0 1 1 0 F1 × × 0 1 0 0 1 F0 × × 0 0 0 1 0 010:ADD 110:SUB 010:ADD 110:SUB 000:AND 001: OR 111:SLT 5.单周期数据通路的构建1)构件:PC、指令存储器、寄存器文件RF和数据存储器; 2)取指令的过程:PC→IM: A/RD3)取源操作数的过程:IM:RD→RF:A1/RD1。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

);

parameter A_NOP = 5'h00; parameter A_ADD = 5'h01; parameter A_SUB = 5'h02; parameter A_AND = 5'h03; parameter A_OR = 5'h04; parameter A_XOR = 5'h05; parameter A_NOR = 5'h06; parameter A_MUL = 5'h07; parameter A_DIV = 5'h08; parameter A_ROL = 5'h09;//循环左移 always@(posedge clk) begin case (alu_op)

4. 记录设计和调试过程。

四、实验代码及结果mFra bibliotekdule alu(

input clk,

input signed [31:0] alu_a,

input signed [31:0] alu_b,

input

[4:0] alu_op,

output reg

[31:0] alu_out,

output reg [63:0] alu_out2

a=01,b=11,分别相加,将 a 循环左移一位,相乘,相除,相乘结果保存到[63:0] alu_out2 中。

rtl 电路图:

五、调试和心得体会

由于 verilog 语言的优势,直接使用 case 语句即可完成一个 alu。

alu_out[31:0] = {alu_a[30:0],alu_a[31]}; end endcase end Endmodule

仿真代码: module sim(

); reg [31:0] alu_a; reg [31:0] alu_b; reg clk; reg [4:0] alu_op; wire [31:0] alu_out; wire [63:0] alu_out2; alu t(clk,alu_a,alu_b,alu_op,alu_out,alu_out2); always begin #50 clk=~clk; end initial begin clk<=1; #55 alu_a<=32'h01; alu_b<=32'h11; alu_op<=5'h01; #55 alu_op<=5'h09; #110 alu_op<=5'h07; #110 alu_op<=5'h08; end Endmodule

实验八 ALU 模块的设计与调试

一、实验目的

1. 熟练掌握 VHDL/Verilog 中语句的综合应用。

2. 掌握 ALU 模块的设计与应用。

二、实验内容

1. 设计一个基本的算术逻辑运算模块。

三、实验要求

1. 分析各模块的的程序结构,画出其流程图。

2. 画出模块的电路图。

3. 分析电路的仿真波形,标出关键的数值。

A_NOP:alu_out = 32'b0; A_ADD:alu_out = alu_a + alu_b; A_SUB:alu_out = alu_a - alu_b; A_AND:alu_out = alu_a & alu_b; A_OR :alu_out = alu_a | alu_b; A_XOR:alu_out = alu_a ^ alu_b; A_NOR:alu_out = alu_a ~^ alu_b; A_MUL:alu_out2 = alu_a * alu_b; A_DIV:alu_out = alu_a / alu_b; A_ROL:begin