LPM宏模块使用方法

实验2参数可设置宏功能模块lpm的应用

功能描述

浮点加法器、减法器模块 浮点参数化除法器宏模块 浮点参数化乘法器宏模块 参数化存储乘法器宏模块 参数化乘累加器宏模块 参数化乘加器宏模块 参数化整数平方根运算宏模块 参数化除法器宏模块 参数化绝对值运算宏模块(Altera推荐使用)

10 lpm_add_sub

11 lpm_compare 12 lpm_counter 13 lpm_divide

参数化加法器-减法器宏模块(Altera推荐使 用)

参数化比较器宏模块(Altera推荐使用) 参数化计数器宏模块(Altera推荐使用) 参数化除法器宏模块(Altera推荐使用)

第四页,编辑于星期三:十二点 三十分。

一、参数可设置模块库(续3)

门电路

序号 模块名称

功能描述

1 lpm_and/or/xor 参数化与门模块/或门/异或门模块

地址低4位,十 六进制表示9

地址高4位,十 六进制表示9

存储数据 9 ×9=81

保存,文件名romdata.hex

第十三页,编辑于星期三:十二点 三十分。

二、利用lpm-rom设计一个乘法器

定制lpm_rom元件 Tools→MegaWizard Plug-In Manager

第十四页,编辑于星期三:十二点 三十分。

第七页,编辑于星期三:十二点 三十分。

一、参数可设置模块库(续6)

2、调用宏功能模块的方法

新建原理图编辑文件,双击 打开Symbol对话框调用

也可通过菜单Tools→MegaWizard Plug-In Manager

第八页,编辑于星期三:十二点 三十分。

二、利用lpm-rom设计一个乘法器

1、ROM工作原理

二、利用lpm-rom设计一个乘法器

LPM的使用

七段码显示 a b c d e f g 1 1 1 1 1 1 0 0 1 1 0 0 0 0 1 1 0 1 1 0 1 1 1 1 1 0 0 1

. . .

提高电路设计效率的常用方法

• 对ROM储存内容进行初始化的文件格 式是: Hexademial(Intel-Formal)File(.hex)

提高电路设计效率的常用方法

(4)给电路加上相应的输入模块input和输 出模块output,并给出相应的名字,构建 完整的电路。

(5)如果未对ROM进行初始化,则电路编 译之后,在message窗口有如下信息: Critical Warning: Can‘t find Memory Initialization File or Hexadecimal (IntelFormat) File …/seg7/rom.mif -- setting all initial values to 0

或 Altera Memory Initialize File(.mif)

提高电路设计效率的常用方法

(2)以.bdf方式(图形化设计方式)打开 一个新的设计,并将该设计文件命名为 seg7.bdf,然后把新文件设定在当前 project下。

(3)从megafunctions中选择器件lpm_rom 宏单元,并放在设计文件中,同时设置其 各项接口信息与参数。

提高电路设计效率的常用方法

以七段数码管显示为例说明LPM的应用:

• (1)确定译码关系表显示译码关系表

字符 二进制表示 a3 a2 a1 a0 0 0 0 0 0 1 0 0 0 1 2 0 0 1 0 3 0 0 1 1

. . . . . .

提高电路设计效率的常用方法

使用LPM宏单元库

lpm_rom模块的使用

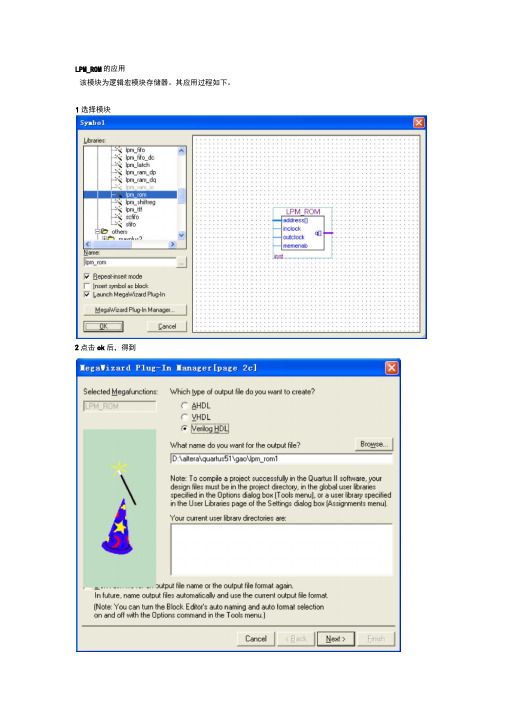

LPM_ROM的应用该模块为逻辑宏模块存储器。

其应用过程如下。

1选择模块2点击ok后,得到3属性编辑:可以根据实际需要选择数据宽度和内存的容量,默认是修改空间和数据属性,Cyclone系列支持最大存储深度4k。

8bit,32个字空间。

该界面可以选择输出引脚的属性, 需要把hex文件或者mif放置该模块:Iprr< Back Next >All Fil«address[7.> dockResource Estitnaift1 M4KFinish其中mif文件或者hex文件可以由多种形式生成。

或由多种工具获得,女口Quartus的Text File编辑器、Matlab等。

完成设置:Kegaf izard Plug-In lanager - LPI_ROI [page 6 of 6] —S UBM aryWto the 'Finish' button i$ pressed, the MegaV/izard Plug-In Manager 囚illcreate the checked file$ in the follo^irig list You may choose to includeor exclude a file by checking or ur»cbecking 韶co悴pondingcheckbox^ respective^. The state of checkboxes will be remembered forthe next MegaWizard Plug-In Manager session.T he M tga^Vizard Plug in Mdnagei will create thwe fies in the directar)J:D:\altera\quartus51 \jgao\File| Descriptiori0 Ipm_rom1 vIpm_rom1 inc 商Ipm_rom1 .cmp 0Ipm_rom1 .bsf □Ipm_rom1 ^inst.v 3Ipm_rom1_bb.7Variation fileAHDL Include HieVHDL Ccmponent declaratkn fileQuartus symbol fileInstantiation template fileVerilog 'Black Bos' declaration fileCocixnentaliDn Cancel< flack也册t >Finishpiri rml,!-*7 L—acWressR.-Ol *irmst1t按照基本操作步骤添加引脚,并进行编译,排除错误。

第7章LPM参数化宏模块的应用

【例8-28】 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY Tone IS PORT ( Index : IN STD_LOGIC_VECTOR(7 DOWNTO 0); CODE : OUT INTEGER RANGE 0 TO 15; HIGH : OUT STD_LOGIC; Tone : OUT INTEGER RANGE 0 TO 16#7FF# ); END; ARCHITECTURE one OF Tone IS BEGIN Search : PROCESS(Index) BEGIN CASE Index IS -- 译码电路,查表方式,控制音调的预置数 WHEN "00000001" => Tone <= 773; CODE <= 1; HIGH <= '0'; WHEN "00000010" => Tone <= 912; CODE <= 2; HIGH <= '0'; WHEN "00000100" => Tone <= 1036; CODE <= 3; HIGH <= '0'; WHEN "00001000" => Tone <= 1116; CODE <= 4; HIGH <= '0'; WHEN "00010000" => Tone <= 1197; CODE <= 5; HIGH <= '0'; WHEN "00100000" => Tone <= 1290; CODE <= 6; HIGH <= '0'; WHEN "01000000" => Tone <= 1372; CODE <= 7; HIGH <= '0'; WHEN "10000000" => Tone <= 1410; CODE <= 1; HIGH <= '1'; WHEN OTHERS => Tone <= 2047; CODE <= 0; HIGH <= '0'; END CASE; END PROCESS; END;

LPM参数化宏模块应用

Megafunctions来源

(1) 来源于AMPP(Altera Megafunction Partners Program )的megafunctions. (2)megacore: 是Altera公司经过严格测试,可以 应用于Altera公司PLD的,并获得最高性能价 格比的复杂功能代码. (3)Altera的OpenCore Evaluation Feature允许 用户可以先对megacore进行评估(用于仿真 和验证),若要下载,需要购买许可文件. (4)MegaCore函数可以从Altera网站上的IP megastore下载.

Part 3 LPM参数化宏模块使用

LPM(Library of Parameterized Modules)介绍

在90年代,随着PLD密度、复杂性和性能的飞

速提高,设计者发现:在各种EDA工具之间 建立一种通用的功能元件集合十分必要,这 样,可以保证设计的独立于结构的特性,缩 短产品的开发时间。 1993年,为满足设计者的要求,LPM被EIA (Electronic Industries Association )确 立为过渡标准。

QuartusII和MaxplusII中提供的LPM功能模块

Megafuntions介绍

除了LPM功能模块,Altera还在QuartusII中提

供了宏功能模块(Megafunctions). 宏功能模块是经过测试和优化的,参数化的,具 有知识产权(IP)的模块.它们能充分地利用所 要使用的可编程器件的结构. 通过使用宏单元模块,设计者可以将注意力集 中在提高系统级的性能上,而不必重新设计一 些通用功能模块.

Altera Intellectual Property: IP MegaStore

LPM宏模块的应用

E §7.1.1 计数器LPM模块文本代码的调用

D (3)设定计数器,含时钟使能和进位输出:单击Next,选中

A 技

Modulus,并选择12,表示模12计数器(若选择Plain binary 表示普通二进制计数器),选择时钟使能控制Clock Enable和 进位输出Carry-out。

术

与

应

用

§7.1 计数器LPM宏模块调用

lpm_counter_component.lpm_width=4;//计数位宽

endmodule

E

例化语句中,未设定的端口必须接上特定的电平。 计数器模块lpm_counter是一个可设定参数的封闭模块,只

D

能通过参数传递说明语句defparam将用户设定的参数通过

A

文件CNT4B.v传递进lpm_counter中。

lpm_counter_component.lpm_modulus=12,//模12计数器

lpm_counter_component.lpm_port_updown=“PORT_USED”,//使用加减计数

lpm_counter_component.lpm_type=“LPM_COUNTER”,//计数器类型

应

.aload(1`b0), .aset(1`b0), .cin(1`b1), .cnt_en(1`b1), .eq(), .sclr(1`b0), .sset(1`b0));

用

defparam lpm_counter_component.lpm_direction=“UNUSED”,//单方向计数参数未用

例7-2:24位寄存器(defparam语句应用示例)

E

module REG24B (input [23: 0] d, input clk, output[23: 0] q); lpm_ff U1 (.q(q[11: 0], .data(d[11: 0]), .clock(clk));

LPM宏函数使用

•

EAB是在输入、输出口上带有寄存器的 RAM块,利用它可以非常方便地实现一些 规模不太大的ROM、RAM、双端口RAM和 FIFO等功能。

• EP1K中的EAB是FPGA中的嵌入式阵列块, 主要可以用来做存储器之类的东西,如 RAM、ROM、FIFO等。在用LPM宏单元做 RAM存储器时,可以用EAB来做,也可以 不用EAB做。如果不用EAB来做,那么 LPM就会调用FPGA中的触发器来实现存储 器的功能,这样做非常浪费FPGA资源。因 此,通常情况下都是选择用EAB来做各: 00 09 12 1b 24 2d 36 3f 48 51 5a 63 6c 75 7e 87; a0 : 00 0a 14 1e 28 32 3c 46 50 5a 64 6e 78 82 8c 96; b0 : 00 0b 16 21 2c 37 42 4d 58 63 6e 79 84 8f 9a a5; c0 : 00 0c 18 24 30 3c 48 54 60 6c 78 84 90 9c a8 b4; d0 : 00 0d 1a 27 34 41 4e 5b 68 75 82 8f 9c a9 b6 c3; e0 : 00 0e 1c 2a 38 46 54 62 70 7e 8c 9a a8 b6 c4 d2; f0 : 00 0f 1e 2d 3c 4b 5a 66 78 87 96 a5 b4 c3 d2 e1; end;

1.利用图形法

• 第2图说明:输入是地址,地址里面的内容 就是x,y乘积的结果

• • • • • • • • • • •

library ieee; use ieee.std_logic_1164.all; library lpm; use lpm.lpm_components.all; entity romlpm is port(address: in std_logic_vector(7 downto 0); inclock: in std_logic; q: out std_logic_vector(7 downto 0)); end romlpm; architecture str of romlpm is begin

第7章 LPM宏模块的应用

E D A 技 术 与 应 用

通过Quartus II设置DSP模块构建:Assignments→Setting,在 左栏选择Analysis&Synthesis Settings项,在对话框中按More Settings按钮,在弹出的对话框中选择DSP Block Balancing项 的DSP blocks。

(2)文件直接编辑法:

使用Quartus II以外的编辑器设计.mif文件

E D A 技 术 与 应 用

例7-5:编辑器设计.mif文件

DEPTH=128; :数据深度,即存储的数据个数 WIDTH=8; :输出数据宽度 ADDRESS_RADIX=HEX;:地址数据类型,HEX表示选择十六进制 数据类型 DATA_RADIX=HEX;:存储数据类型,HEX表示选择十六进制数据 类型 CONTENT :此为关键词 BEGIN :此为关键词 0000 : 0080; 0001 : 0086; 0002 : 008C; …(数据略去) 007E : 0073; 007F : 0079; END;

1. .mif格式文件

E D A 技 术 mif数据表格中键入数据。 表格中的数据格式可通过右击 窗口边缘的地址数据所弹出的 窗口中选择。

表中任一数据对应的地址为左 列数与顶行数之和。

完成数据输入后,选择 File→Save As,保存此数据文 件,如取名为data7X8.mif。

E D A 技 术 与 应 用

例化语句中,未设定的端口必须接上特定的电平。

计数器模块lpm_counter是一个可设定参数的封闭模块,只 能通过参数传递说明语句defparam将用户设定的参数通过 文件CNT4B.v传递进lpm_counter中。

教学课件:第7章-LPM参数化宏模块应用

导出数据

用户可以将LPM中的数据导出到 Excel中,以便进行更深入的数据 分析和可视化。

共享数据

通过集成,LPM和Excel可以共享数 据,确保两个工具中的数据保持一 致,提高工作效率。

与Power BI的集成

数据可视化

数据交互

LPM参数化宏模块可以与Power BI集 成,将数据从LPM中导入到Power BI 中进行数据可视化。

的共享和传输。

自动化流程

通过集成,用户可以使用其他应 用程序中的自动化功能,实现

LPM参数化宏模块的自动化运行, 提高工作效率。

插件扩展

LPM参数化宏模块可以通过插件 扩展与其他应用程序进行集成, 实现更广泛的应用场景和功能。

05

总结与展望

总结

LPM参数化宏模块应用是教学课件第7章的核心内容,通过这一章节的学习,学生可以了解 LPM参数化宏模块的基本概念、原理和应用方法。

功能

LPM参数化宏模块具有高度的可 配置性和可扩展性,能够满足用 户多样化的需求,同时提高软件 开发的效率和灵活性。

应用场景与优势

应用场景

LPM参数化宏模块广泛应用于各种 软件领域,如游戏开发、仿真软件、 工业控制软件等。

优势

LPM参数化宏模块的优势在于其可定 制性和灵活性,能够快速适应不同的 应用场景和需求,同时减少软件开发 的时间和成本。

教学课件:第7章-lpm参 数化宏模块应用

• 引言 • LPM参数化宏模块概述 • LPM参数化宏模块应用实例 • LPM参数化宏模块与其他工具的集成 • 总结与展望

01

引言

主题介绍

lpm参数化宏模块应用

介绍lpm参数化宏模块的基本概念、功能和特点。

LPM计数器模块使用方法

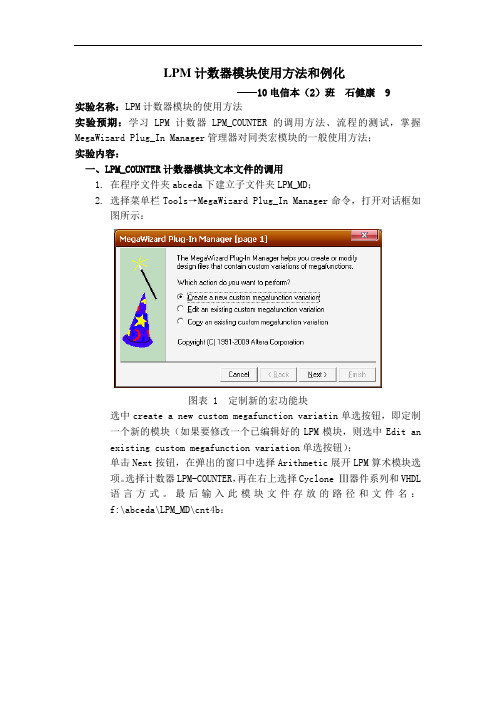

LPM计数器模块使用方法和例化——10电信本(2)班石健康 9实验名称:LPM计数器模块的使用方法实验预期:学习LPM计数器LPM_COUNTER的调用方法、流程的测试,掌握MegaWizard Plug_In Manager管理器对同类宏模块的一般使用方法;实验内容:一、LPM_COUNTER计数器模块文本文件的调用1.在程序文件夹abceda下建立子文件夹LPM_MD;2.选择菜单栏Tools→MegaWizard Plug_In Manager命令,打开对话框如图所示:图表 1 定制新的宏功能块选中create a new custom megafunction variatin单选按钮,即定制一个新的模块(如果要修改一个已编辑好的LPM模块,则选中Edit an existing custom megafunction variation单选按钮);单击Next按钮,在弹出的窗口中选择Arithmetic展开LPM算术模块选项。

选择计数器LPM-COUNTER,再在右上选择Cyclone Ⅲ器件系列和VHDL语言方式。

最后输入此模块文件存放的路径和文件名:f:\abceda\LPM_MD\cnt4b:单击next按钮,弹出对话框。

选择4位计数器,选择“Creat an updown input…”使计数器有加减控制功能。

单击next按钮,打开对话框,选择Modulus…12,则表示模12计数器,从0记到11(若选择Plain binary则表示是普通的二进制计数器)。

然后选择时钟使能控制Clock Enable和进位输出Carry-out,如图:7.再单击next按钮,打开对话框,选择4位数据同步加载控制Load和异步清零控制Clear,如图:8.再按next按钮结束设置。

二、例化1)生成的LPM计数器模块VHDL源程序cnt4b如下:LIBRARY ieee;USE lpm;USE ;ENTITY cnt4b ISPORT(aclr : IN STD_LOGIC ;clk_en : IN STD_LOGIC ;clock : IN STD_LOGIC ;data : IN STD_LOGIC_VECTOR (3 DOWNTO 0);sload : IN STD_LOGIC ;updown : IN STD_LOGIC ;cout : OUT STD_LOGIC ;q : OUT STD_LOGIC_VECTOR (3 DOWNTO 0) );END cnt4b;ARCHITECTURE SYN OF cnt4b ISSIGNAL sub_wire0 : STD_LOGIC ;SIGNAL sub_wire1 : STD_LOGIC_VECTOR (3 DOWNTO 0);COMPONENT lpm_counterGENERIC (lpm_direction : STRING;lpm_modulus : NATURAL;lpm_port_updown : STRING;lpm_type : STRING;lpm_width : NATURAL);PORT (sload : IN STD_LOGIC ;clk_en : IN STD_LOGIC ;aclr : IN STD_LOGIC ;clock : IN STD_LOGIC ;cout : OUT STD_LOGIC ;q : OUT STD_LOGIC_VECTOR (3 DOWNTO 0);data : IN STD_LOGIC_VECTOR (3 DOWNTO 0);updown : IN STD_LOGIC);END COMPONENT;BEGINcout <= sub_wire0;q <= sub_wire1(3 DOWNTO 0);lpm_counter_component : lpm_counterGENERIC MAP (lpm_direction => "UNUSED",lpm_modulus => 12,lpm_port_updown => "PORT_USED",lpm_type => "LPM_COUNTER",lpm_width => 4)PORT MAP (sload => sload,clk_en => clk_en,aclr => aclr,clock => clock,data => data,updown => updown,cout => sub_wire0,q => sub_wire1);END SYN;它调用了更底层的文件lpm_counter,同时可以作为一个底层元件被上一层设计调用或例化。

《EDA技术与Verilog HDL》PPT第3版 第6章 LPM宏模块用法

6.3 LPM_RAM宏模块用法

6.3.3 测试LPM_RAM

图6-19 图6-18的RAM仿真波形

6.3 LPM_RAM宏模块用法

6.3.4 Verilog代码描述的存储器初始化文件加载表述

6.3 LPM_RAM宏模块用法

6.3.5 存储器设计的结构控制

图6-20 例6-6的RTL电路模块图

6.6.1 建立嵌入式锁相环元件

图6-35 输出第二个时钟信号c1

6.6 LPM嵌入式锁相环调用

6.6.1 建立嵌入式锁相环元件

图6-36 采用了嵌入式锁相环作时钟的正弦信号发生器电路

6.6.2 测试锁相环

6.7 In-System Sources and Probes Editor用法

(1)在顶层设计中嵌入In-System Sources and Probes模块。 (2)设定参数。

图6-37 为In-System Sources and Probes模块设置参数

6.7 In-System Sources and Probes Editor用法

(3)与需要测试的电路系统连接好。

图6-38 在电路中加入In-System Sources and Probes测试模块

6.7 In-System Sources and Probes Editor用法

6.3.2 以原理图方式对LPM_RAM进行调用

图6-13 调用单口LPM RAM

6.3 LPM_RAM宏模块用法

6.3.2 以原理图方式对LPM_RAM进行调用

图6-14 设定RAM参数

6.3 LPM_RAM宏模块用法

6.3.2 以原理图方式对LPM_RAM进行调用

图6-15 设定RAM仅输入时钟控制

实验三 LPM模块的使用

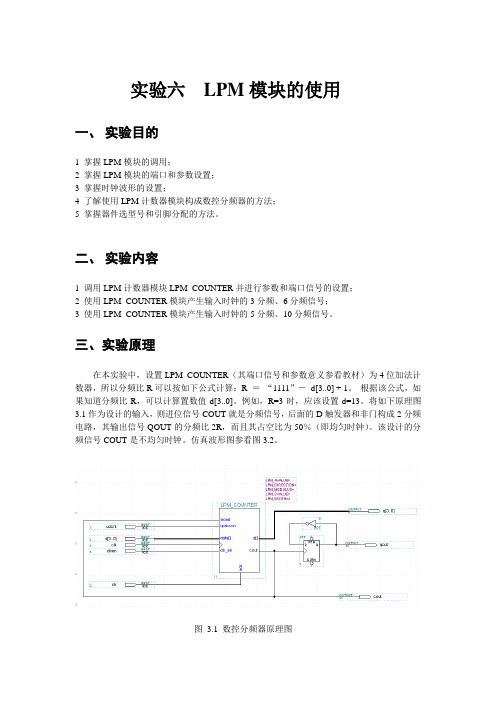

实验六LPM模块的使用一、实验目的1 掌握LPM模块的调用;2 掌握LPM模块的端口和参数设置;3 掌握时钟波形的设置;4 了解使用LPM计数器模块构成数控分频器的方法;5 掌握器件选型号和引脚分配的方法。

二、实验内容1 调用LPM计数器模块LPM_COUNTER并进行参数和端口信号的设置;2 使用LPM_COUNTER模块产生输入时钟的3分频、6分频信号;3 使用LPM_COUNTER模块产生输入时钟的5分频、10分频信号。

三、实验原理在本实验中,设置LPM_COUNTER(其端口信号和参数意义参看教材)为4位加法计数器,所以分频比R可以按如下公式计算:R =“1111”-d[3..0] + 1。

根据该公式,如果知道分频比R,可以计算置数值d[3..0]。

例如,R=3时,应该设置d=13。

将如下原理图3.1作为设计的输入,则进位信号COUT就是分频信号,后面的D触发器和非门构成2分频电路,其输出信号QOUT的分频比2R,而且其占空比为50%(即均匀时钟)。

该设计的分频信号COUT是不均匀时钟。

仿真波形图参看图3.2。

三、实验步骤(一)3分频和6分频数控分频器的设计1 建立一个工程(注意要正确设置工程的保存目录),工程名可以命名为LPM_CNT_4【菜单命令file/project/name 】;2 按图3.1画出原理图【注意LPM_COUNTER 模块符号在mega_lpm 库目录之下,调用时,出现对话框,选cancel 。

D 触发器符号是DFF 】;3 设置LPM_COUNTER 的端口信号和参数【选中LPM 模块,点右键,点editports/parameters ,然后将不用的端口信号设置为unused ,则原理图中该信号隐藏,使用的信号设置为used ,则原理图中该信号出现,各信号的意义见教材或者在软件的帮助中查看。

参数设置:将LPM_WIDTH 的值设置为4,点change ,其他的参数值不设置,然后确定,则设置完成】;4 选器件:将器件型号选为EP1k30144_3;【assign/device :ACEX1k 系列,将选项show onlyfast speed grades 前的“√”去掉】5 编译;6 建立波形文件,然后保存,其文件名必须与工程名一致;【波形设置:①设置仿真时间为10us: 菜单命令file/end time ,然后输入10us ,确定。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

RTL图:

波形仿真:

实验总结

通过这次实验,我学会了如何使用工具快速设计相关器件的VHDL代码。加强了如何去例化元件。在实验过程中,我遇到了无法编译成功的困难,原因是:我生成的计数器代码和给的代码是不一样的,主要是接口不一样,例化的时候出现了接口不搭配,改正后就成功了。

指导教师意见

签名: 年 月 日

cnt_en1: IN STD_LOGIC ;

data1: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

sclr1: IN STD_LOGIC ;

updown1: IN STD_LOGIC ;

cout1: OUT STD_LOGIC ;

q1: OUT STD_LOGIC_VECTOR (3 DOWNTO 0)

data: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

sclr: IN STD_LOGIC ;

updown: IN STD_LOGIC ;

cout: OUT STD_LOGIC ;

q: OUT STD_LOGIC_VECTOR (3 DOWNTO 0)

);

END COMPONENT;

利用计数宏模块构建一个12进制计数器。

实验数据

1、由于软件之间的偏差,cnt4bb,需要重新设计,设计如下:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

entity cnt4bb IS

PORT(aload1: IN STD_LOGIC ;

clock1: IN STD_LOGIC ;

sload: IN STD_LOGIC ;

updown: IN STD_LOGIC ;

cout: OUT STD_LOGIC ;

q: OUT STD_LOGIC_VECTOR (3 DOWNTO 0)

);

END COMPONENT;

BEGIN

U1:CNT4B PORT MAP(sclr1,cnt_en1,clock1,data1,aload1,updown1,cout1,q1);

实验报告

学院: 专业:电子信息工程 班级:

姓名

学号

实验组

实验时间

2019.6

指导教师

成绩

实验项目名称

LPM宏模块使用方法

实验目的

实验目的

1、了解LPM的参数设置方法。

2、了解LPM模块的调用方法。

3、掌握元件例化语句的使用方法,掌握利用VHDL语言实现层次化设计的方法。

实验原理和步骤

实验原理与实验步骤

BEGIN

U1:CNT4BPORT MAP(aload1,clock1,cnt_en1,data1,sclr1,updown1,cout1,q1);

END SYN1;

可以对刚才的项目CNT4B创建项目,编译,创建符号,然后调用此符号进行编译调试。

实验仪器

电脑、quartusII9.0软件。

实验内容

实验内容

(1)首先建立一个文件夹,比如:D:\LPM_MD.

(2)选择Tool—MegaWizard Plug_In Manager命令,弹出一个如下对话框。

点击next ,

单击Arithmetic选择LPM_COUNTER,器件采用默认,选择VHDL语言,指定模块存放的路径和名字。点击next.

点击finish,就可以了。

clock1: IN STD_LOGIC ;

cnt_en1: IN STD_LOGIC ;

data1: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

sclr1: IN STD_LOGIC ;

updown1: IN STD_LOGIC ;

cout1: OUT STD_LOGIC ;

q1: OUT STD_LOGIC_VECTOR (3 DOWNTO 0)

);

END cnt4bb;

ARCHITECTURE SYN1 OF cnt4bb IS

COMPONENTCNT4BPORT

(

aload: IN STD_nt_en: IN STD_LOGIC ;

LPM(Library of Parameterized Modules)主要是对altera FPGA结构功能做了优化设计。在许多设计中,必须利用LPM模块才能进行设计。设计者可以根据自己电路的需要,从而在项目中十分便利地调用相应的LPM模块,并设置适当的参数,就能满足自己的需要。

计数LPM模块调用和设置如下:

通过FILE-OPEN ,既可以打开刚才设计的VHDL语言程序了。

刚才设计的计数器就可以通过创建项目,用顶层文件进行例化或原理图调用了。

用元件例化语句调用源程序:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

entity cnt4bb IS

PORT(aload1: IN STD_LOGIC ;

);

END cnt4bb;

ARCHITECTURE SYN1 OF cnt4bb IS

COMPONENTCNT4B PORT

(

aclr: IN STD_LOGIC ;

clk_en: IN STD_LOGIC ;

clock: IN STD_LOGIC ;

data: IN STD_LOGIC_VECTOR (3 DOWNTO 0);