亿佰特(Ebyte)28GHz-5G通信频段射频前端模块深度解析

亿佰特(Ebyte)-如何选择天线(天线选择指南)

如何选择天线(天线选择指南)1. 简介天线(antenna)是一种变换器,它把传输线上传播的导行波,变换成在无界媒介中传播的电磁波,或者进行相反的变换。

频率越低,波长越长,天线越长。

一般天线都具有可逆性, 即同一副天线既可用作发射天线,也可用作接收天线,同一天线作为发射或接收的基本特性参数是相同的。

2. 天线的种类如果在同一款射频产品中使用,是有很多方案可以选择的,尺寸、成本、性能这个都是重要的因素。

以外置天线为例,说明如何选择天线。

3. 天线的参数图 1 各种不同的天线从天线的理论参数来讲,天线的输入阻抗、天线的极化方式、天线的增益、天线的波瓣宽度这 4 个方面的因素可以决定天线的性能。

3.1. 天线的输入阻抗天线的输入阻抗是天线馈电端输入电压与输入电流的比值,最佳的天线都会做成标准的50 欧姆,同时无线模块的阻抗也是标准的 50 欧姆,这样天线和无线模块完全匹配,保证没有传输信号的流失,进而保证无线模块的距离。

但是实际生产过程中都不能保证天线和模块都是标准的 50 欧姆,所以无线模块和天线不可能完全匹配。

匹配的优劣一般用四个参数来衡量:反射系数、行波系数、驻波比和回波损耗,主要由驻波比和回波损耗这两个参数来决定。

驻波比为 1 表示完全匹配;驻波比为无穷大表示全反射,完全失配,一般驻波比要求小于 1.5。

回波损耗,又称为反射损耗,是电缆链路由于阻抗不匹配所产生的反射,是一对线自身的反射。

不匹配主要发生在连接器的地方,但也可能发生于电缆中特性阻抗发生变化的地方,所以施工的质量是提高回波损耗的关键。

一般要求回波损耗大于 14dB 。

3.2. 天线的极化方式天线的极化,就是指天线辐射时形成的电场强度方向。

由于电波的特性,决定了水平极化传播的信号在贴近地面时会在大地表面产生极化电流,极化电流因受大地阻抗影响产生热能而使电场信号迅速衰减,而垂直极化方式则不易产生极化电流,从而避免了能量的大幅衰减,保证了信号的有效传播。

亿佰特(Ebyte)-ZigBee无线模块组网典型应用(ZigBee组网应用)

1.ZigBee技术简介ZigBee是一种短距离,低功耗,低速率,低成本的一种无线自组网通信技术。

2.ZigBee网络特点ZigBee网络有如下特点:低功耗,自组网,多跳路由,高安全,抗干扰能力强……3.ZigBee网络角色3.1协调器ZigBee协调器(英文名:ZigBee Coordinate,通常简写为:ZC)。

协调器在ZigBee网络中,有且只能有一个协调器,它在网络中起了网络搭建和网络维护的功能。

是整个网络的中心枢纽。

是等级最高的父节点。

3.2路由器ZigBee路由器(英文名:ZigBee Router,通常简写为:ZR),路由器在ZigBee网络中既可以充当父节点,也可以充当子节点,有信息转发和辅助协调器维护网络的功能。

3.3终端ZigBee终端(英文名:ZigBee End-Device,通常简写为:ZED),终端在ZigBee网络中,其功能最为简单,只能加入网络,为最末端的子节点设备。

只能与其父节点进行通信,如果两个终端之间需要通信,必须经过父节点进行多跳或者单跳通信。

是ZigBee网络中可允许存在的数量最多的节点,也是唯一允许低功耗的网络设备。

4.ZigBee拓扑结构ZigBee根据网络结构可分为三种,即:星状网络、树状网络和网状网络。

4.1星状网络ZigBee星状网络在ZigBee网络中属于一种最为简单的网络拓扑结构。

包含一个协调器(中心节点)和若干个路由器和终端(附属节点)组成。

该结构如下图所示:该结构网络中,每个附属节点只能与中心节点通信,如果需要两个附属节点之间通信,必须经过中心节点进行数据转发。

4.2树状网络ZigBee树状网络包含一个协调器,若干个路由器和终端组成。

其网络拓扑结构如下图所示:ZigBee树状网络可以看做多个星状网络组成,每个树杈分支处(带节点的路由器)可看做组成星状网络的“中心节点”,每个字设备只能与其父节点通信,最高级的父节点为协调器。

在树状网络中,协调器将整个网络搭建起来,路由器作为承接点,将网络以树状向外扩散。

亿佰特WiFi模组选型指南以及WiFi模块应用方案详解

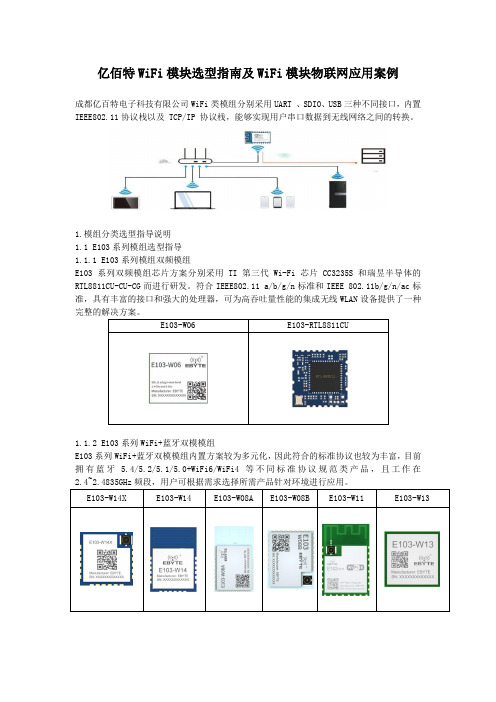

亿佰特WiFi模块选型指南及WiFi模块物联网应用案例成都亿百特电子科技有限公司WiFi类模组分别采用UART 、SDIO、USB三种不同接口,内置IEEE802.11协议栈以及 TCP/IP 协议栈,能够实现用户串口数据到无线网络之间的转换。

1.模组分类选型指导说明1.1 E103系列模组选型指导1.1.1 E103系列模组双频模组E103系列双频模组芯片方案分别采用TI第三代Wi-Fi芯片CC3235S和瑞昱半导体的RTL8811CU-CU-CG而进行研发。

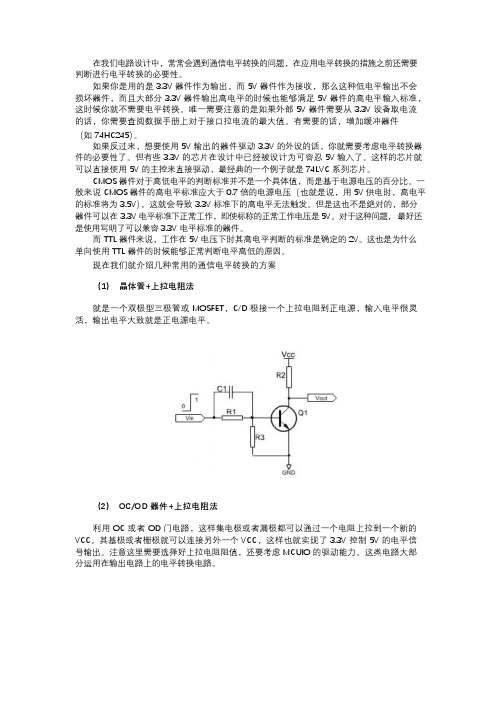

符合IEEE802.11 a/b/g/n标准和IEEE 802.11b/g/n/ac标准,具有丰富的接口和强大的处理器,可为高吞吐量性能的集成无线WLAN设备提供了一种E103-W06 E103-RTL8811CU1.1.2 E103系列WiFi+蓝牙双模模组E103系列WiFi+蓝牙双模模组内置方案较为多元化,因此符合的标准协议也较为丰富,目前拥有蓝牙 5.4/5.2/5.1/5.0+WiFi6/WiFi4等不同标准协议规范类产品,且工作在1.1.3 E103系列超低功耗WiFi模组E103系列低功耗WiFi模组工作在2.4~2.4835GHz 频段,符合IEEE 802.11b/g/n协议标准。

模块集成了透传功能,即拿即用,支持串口 AT 指令集用户通过串口即可使用网络访问的功能,广泛应用于穿戴设备、家庭自动化、家庭安防、个人保健、智能家电、配饰与遥控器、1.1.4 E103系列WiFi路由模组E103系列WiFi路由模组目前拥有两款产品,分别为E103-W20(7688)和 E103-W20(7628)。

该类模块是基于联发科 MT7688AN及 MT7628AN为核心的低成本低功耗的物联网模块。

模块引出了 MT7688AN /MT7628AN的所有接口,支持 OpenWrt 操作系统及自定义开发,具有丰富的接口和强大的处理器,可以广泛的应用于智能设备或云服务应用等,并可以自由进行1.1.5 E103系列通用型模组E103系列通用型模组不仅具有丰富的外设接口,还拥有强大的神经网络运算能力和信号处理能力,成本低,且适用于AloT 领域的多种应用场景,例如唤醒词检测和语音命令识别、E103-RTL8189 E103-W05 E103-W01-IPX E103-W01 E103-W101.1.6 E103系列WiFi mesh模组在 EBYTE 的方案中,我们公司支持WIFI Mesh支持有路由组网和无路由组网的模块为E103-W07,E103-W07是一套建立在Wi-Fi协议之上的网络协议。

亿佰特(Ebyte)-ZigBee无线模块组网典型应用(ZigBee组网应用)

ZigBee 无线模块组网典型应用1.Z igBee 技术简介ZigBee 是一种短距离,低功耗,低速率,低成本的一种无线自组网通信技术。

2.Z igBee 网络特点ZigBee 网络有如下特点:低功耗,自组网,多跳路由,高安全,抗干扰能力强…… 3.Z igBee 网络角色3.1协调器ZigBee 协调器(英文名:ZigBee Coordinate ,通常简写为:ZC)。

协调器在 ZigBee 网络中,有且只能有一个协调器,它在网络中起了网络搭建和网络维护的功能。

是整个网络的中心枢纽。

是等级最高的父节点。

3.2路由器ZigBee 路由器(英文名:ZigBee Router,通常简写为:ZR),路由器在 ZigBee 网络中既可以充当父节点,也可以充当子节点,有信息转发和辅助协调器维护网络的功能。

3.3终端ZigBee 终端(英文名:ZigBee End-Device,通常简写为:ZED),终端在 ZigBee 网络中,其功能最为简单,只能加入网络,为最末端的子节点设备。

只能与其父节点进行通信,如果两个终端之间需要通信,必须经过父节点进行多跳或者单跳通信。

是 ZigBee 网络中可允许存在的数量最多的节点,也是唯一允许低功耗的网络设备。

4.Z igBee 拓扑结构ZigBee 根据网络结构可分为三种,即:星状网络、树状网络和网状网络。

4.1星状网络ZigBee 星状网络在 ZigBee 网络中属于一种最为简单的网络拓扑结构。

包含一个协调器(中心节点)和若干个路由器和终端(附属节点)组成。

该结构如下图所示:该结构网络中,每个附属节点只能与中心节点通信,如果需要两个附属节点之间通信,必须经过中心节点进行数据转发。

4.2树状网络ZigBee 树状网络包含一个协调器,若干个路由器和终端组成。

其网络拓扑结构如下图所示:ZigBee 树状网络可以看做多个星状网络组成,每个树杈分支处(带节点的路由器)可看做组成星状网络的“中心节点”,每个字设备只能与其父节点通信,最高级的父节点为协调器。

亿佰特(Ebyte)-无线串口模块快速选型指南

无线串口模块快速选型指南首先我们来说一下什么是无线串口模块,无线模块即是通过无线电信号来传输数据的软硬件模组,串口模块即是使用串口通信协议来传输数据的软硬件模组,那么无线串口模块也就是使用串口协议来进行无线电通信的软硬件模组。

成都亿佰特电子科技有限公司是一家专注于无线数传通信应用的高科技公司,专业研发和生产各种频段各种功能无线数传模块。

下面就以该公司的产品为例来介绍如何更具自己的需求选择合适自己的无线串口模块。

1.串口模块的选型要点1.1通信频点通信频点就是无线模块在工作的时候向外辐射出去的电波频率,无线串口模块常用的频点大致可以分为170MHz、230MHz、315MHz、433MHz、490MHz、780MHz、868MHz、915MHz、2.4GHz 等。

在使用的环境中更具自身的环境需求选择不同频点的模块已避免干扰,同时不同频点在通信方面也有不同特点,比如170MHz 的模块其频率较低那么波长也就较长,那么在信号的穿透和绕射能力方面相较868MHz、2.4GHz 的模块就具有更好的通信效果。

1.2芯片方案芯片方案指的就是无线串口模组中使用的射频处理IC,不同的芯片有不同的特点,常用的有“SEMTECH”公司的SX1278、SX1276、SX1212、SX1280;“SILICON LABS”公司的SI4463、SI4438、SI4432;以及TI 公司的CC1110、CC1101、CC1310 等。

这些芯片都有其不同的特点,使用不同芯片方案的模块在射频通信方面也就具有起特点,对于我们用户的选型来说这里从这里也就大概的可以估计模块之间性能的差异以及不同的价格了。

1.3通信距离通信距离也就是无线模块最核心的参数之一,我们根据自己使用的通信距离要求选择合适模块,无线通信因为受到环境等因素的影响因此我们在模块选型的过程中需要注意的是需要预留一定的距离,比如我需要通过500 米,那么最好就不要选择指标为500 米的模块了,至少选择600 米以上的,这样才有应对环境影响的空间,也就保证了产品的适应性以及稳定性等。

亿佰特E28-2G4M27S 产品规格书说明书

E28-2G4M27S产品规格书SX1280 2.4GHz 500mW SPI 高速LoRa模块目录第一章产品概述 (2)1.1 产品简介 (2)1.2 特点功能 (2)1.3 应用场景 (2)第二章规格参数 (3)2.1 极限参数 (3)2.2 工作参数 (3)第三章机械尺寸与引脚定义 (4)第四章基本操作 (5)4.1硬件设计 (5)4.2软件编写 (5)第五章基本应用 (6)5.1 基本电路 (6)第六章常见问题 (7)6.1 传输距离不理想 (7)6.2 模块易损坏 (7)6.3 误码率太高 (7)第七章焊接作业指导 (8)7.1 回流焊温度 (8)7.2 回流焊曲线图 (8)第八章相关型号 (9)第九章天线指南 (9)9.1 天线推荐 (9)9.2天线选择 (9)修订历史 (10)关于我们 (11)第一章产品概述1.1 产品简介E28-2G4M27S是亿佰特公司设计生产的2.4GHz射频收发模块,发射功率500mW,SPI接口,具有极低的低功耗模式流耗;该模块为小体积贴片型(引脚间距1.27mm),自带高性能PCB板载天线,采用52MHz工业级高精度低温漂晶振,保证其工业特性和其稳定性能。

采用Semtech公司的SX1280射频芯片,此芯片包含多样的物理层以及多种调制方式,如LoRa、FLRC、GFSK,并可兼容蓝牙协议;特殊的调制和处理方式使得LoRa和FLRC调制的传输距离有显著提升,在原有基础上内置了功率放大器(PA)与低噪声放大器(LNA),使得最大发射功率达到500mW的同时接收灵敏度也获得进一步的提升,在整体的通信稳定性上较没有功率放大器与低噪声放大器的产品大幅度提升;出色的低功耗性能、片上DC-DC和Time-of-flight使得此芯片功功能强大,可用于智能家居、安全系统、定位追踪、无线测距、穿戴设备、智能手环与健康管理等等。

SX1280支持RSSI,用户可以根据需要实现深度的二次开发,亦集成飞行时间(Time of flight),适用于测距功能。

成都亿佰特(Ebyte)-2.4Ghz 全双工高速连传串口通信模块E39-TTL-100用户手册(nRF24L01+PA)

.一.模块介绍 (2)1.1特点简介 (2)1.2电气参数 (3)1.3系列产品 (3)1.4常见问题 (3).二.功能简述 (4)2.1引脚定义 (4)2.2连接单片机 (5)2.3模块复位 (5)2.4AUX详解 (5).三.工作模式 (6)3.1模式切换 (7)3.2半双工模式(模式0) (7)3.3全双工模式(模式1) (7)3.4预留模式(模式2) (8)3.5设置模式(模式3) (8)3.6快速通信测试 (8).四.指令格式 (9)4.1出厂默认参数 (9)4.2工作参数读取 (9)4.3版本号读取 (9)4.4复位指令 (9)4.5参数设置指令 (9).五.参数配置 (11).六.包装与焊接 (12).七.定制合作 (12).八.关于我们 (13).1.1E39-TTL-100是一款基于100mW的无线数传模块,工作在2.4~2.518GHz频段,使用串口进行数据收发,降低了无线应用的门Array槛。

其功率密度集中,传输距离远,高速率,全双工,可以双向同时通信,支持文件传输;TTL电平输出,兼容3.3V与5V的IO口电压。

E39-TTL-100的典型特点是高速传输,在多种波特率下,可以达到全双工特性(双向同时收发),不限包长,支持不间断传输,支持文件传输。

模块具有数据加密和压缩功能。

模块在空中传输的数据,具有随机性,通过严密的加解密算法,使得数据截获失去意义。

而数据压缩功能有概率减小传输时间,减小受干扰的概率,提高可靠性和传输效率。

1.21.3系列产品E39-TTL-1001.4常见问题E39-TTL-100.2.1*我司提供Altium designer封装库请前往官网下载或联系我们索取2.22.3模块复位E39-TTL-1002.4AUX详解E39-TTL-100AUX用于无线收发缓冲指示和自检指示。

它指示模块是否有数据尚未通过无线发射出去,或已经收到无线数据是否尚未通过串口全部发出,或模块正在初始化自检过程中。

亿佰特(Ebyte)-2.4GHz射频收发模块-通信距离远;具有极低的低功耗模式流耗E28系列用户使用手册

产品概述E28系列产品是2.4GHz射频收发模块,通信距离远;具有极低的低功耗模式流耗。

此模块为小体积贴片型(引脚间距1.27mm),模块自带高性能PCB板载天线。

E28系列产品采用Semtesh公司的SX1280射频芯片,此芯片包含多样的物理层以及多种调制方式,如LORA,FLRC,GFSK。

特殊的调制和处理方式使得LORA和FLRC调制的传输距离大大增加;是一款高性能物联网无线收发器,并可以兼容蓝牙协议。

出色的低功耗性能、片上DC-DC和Time-of-flight使得此芯片功功能强大,可用于智能家居、安全系统、定位追踪、无线测距、穿戴设备、智能手环与健康管理等等。

E28系列产品为硬件平台,出厂无程序,用户需要进行二次开发。

目录1.技术参数 (3)1.1.E28-2G4M12S (3)1.2.E28-2G4M20S (3)1.3.参数说明 (3)2.机械特性 (4)2.1.E28-2G4M12S (4)2.1.1.尺寸图42.1.2.引脚定义4 2.2.E28-2G4M20S (5)2.2.1.尺寸图52.2.2.引脚定义53.推荐连线图 (6)3.1.E28-2G4M12S (6)3.2.E28-2G4M20S (6)4.生产指导 (7)4.1.回流焊温度 (7)4.2.回流焊曲线图 (7)5.常见问题 (8)5.1.通信距离很近 (8)5.2.模块易损坏 (8)6.重要声明 (8)7.关于我们 (8)1.技术参数~~1.1.E28-2G4M12S1.2.E28-2G4M20S1.3.参数说明●在针对模块设计供电电路时,往往推荐保留30以上余量,有整机利于长期稳定地工作;●发射瞬间需求的电流较大但是往往因为发射时间极短,消耗的总能量可能更小;●当客户使用外置天线时,天线与模块在不同频点上的阻抗匹配程度不同会不同程度地影响发射电流的大小。

●射频芯片处于纯粹接收状态时消耗的电流称为接收电流,部分带有通信协议的射频芯片或者开发者已经加载部分自行开发的协议于整机之上,这样可能会导致测试的接收电流偏大;●处于接纯粹收状态的电流往往都是mA级的,µA级的“接收电流”需要开发者通过软件进行处理。

亿佰特(Ebyte)-E18-MS1-PCB是一款基于CC2530F256的2.4G无线模块适用于zigbee智能家居

--电气参数

E18-MS1-PCB

E18-MS1-PCB 是一款体积极小的2.4GHz 无线模块,发射功率约

2.5mW,贴片型(引脚间距1.27mm),收发一体;自带高性能PCB 板载天线。

该模块目前已经稳定量产,并适用于多种应用场景(尤其智能家居)。

E18-MS1-PCB采用美国德州仪器(TI)公司原装进口CC2530射频芯片,

芯片内部集成了8051单片机及无线收发器,并适用于ZigBee设计及2.4GHz IEEE 802.15.4协议。

模块引出单片机所有IO口,可进行多方位的开发。

该模块内带功放芯片CC2592,增加了无线通信距离。

适用于二次开发,出厂已烧录自组网程序,可直接使用,支持串口收发,

详见其他相关文档。

支持多种工作模式和功能,支持AT指令及二进制指令。

--

*我司提供Altium designer封装库请前往网站下载或联系我们索取

--

--注意事项E18-MS1-PCB

--系列产品E18-MS1-PCB。

亿佰特(Ebyte)-低功耗WiFi模块(ESP8266)智能家居物联网改造应用方案

E103-W01-IPX使用手册V1.01.模块介绍 (2)1.1.特点简介 (2)1.2.基本用法 (3)1.3.电气参数 (3)1.4.电气特性 (3)2.功能简述 (4)2.1.引脚定义 (4)2.2.模块功耗 (5)2.3.应用原理图 (5)3.快速入门 (6)3.1.模块作为Client与TCP服务器连接 (6)3.2.模块作为AP建立TCP SERVER与PC无线连接 (15)3.3.Smart Config使用 (17)3.4.PWM的使用 (18)3.5.GPIO的使用 (19)3.6.ADC的使用 (20)3.7.修改串口波特率 (20)4.组网说明 (21)4.1.组网角色 (21)4.2.组网模型 (21)5.AT指令 (23)6.定制合作 (24)7.关于我们 (25)1.模块介绍1.1.特点简介E103-W01是一款超高性价比的100mW(20dBm)串口转Wi-Fi模块,贴片小体积封装,陶瓷天线与IPX并存,工作在2.4~2.4835GHz频段。

模块可使用串口进行数据收发,降低了无线应用的门槛。

E103-W01模块是基于Espressif公司的ESP8266EX芯片研发。

模块集成了透传功能,即拿即用,支持串口AT指令集,服务器AT指令集,用户通过串口即可使用网络访问的功能,广泛应用于穿戴设备、家庭自动化、家庭安防、个人保健、智能家电、配饰与遥控器、汽车、照明、工业互联网等领域。

E103-W01模块支持标准的IEEE802.11b/g/n协议和完整的TCP/IP协议栈,支持STA/AP/STA+AP工作模式、支持SmartConfig、串口透传、IO口控制、开机透传、PWM输出、AD检测等功能,简单配置后便可以非常便利的实现网络访问功能,最大限度减少开发者的工作和项目开发时间。

典型应用:模块特点:√无线抄表√210ms开机透传,掉线自动连接√无线传感√多种波特率√智能家居√支持SmartConfig配置功能√工业遥控及遥测√支持TCPServer、TCPClient、UDP√智能楼宇及智能建筑√三种工作模式STATION、AP、STATION&AP√高压线监测√支持14mA低功耗数据接收√环境工程√支持串口透明传输√高速公路√支持多种加密方式√小型气象站√支持模块串口AT指令配置√自动化数据采集√支持可配置4路PWM输出√消费电子√内置看门狗,永不死机√智能机器人√参数记忆,掉电保存√路灯控制√1路10位精度ADC1.2.基本用法1.3.电气参数1.4.电气特性2.功能简述2.1.引脚定义2.2.模块功耗参数最小值典型值最大值单位Tx802.11b,CCK11Mbps,POUT=+17dBm165170180mA Tx802.11g,OFDM54Mbps,POUT=+15dBm135140150mA Tx802.11n,MCS7,POUT=+13dBm115120130mA Rx802.11b,1024bytes包长,-80dBm182023mA Rx802.11g,1024bytes包长,-70dBm535665mA Rx802.11n,1024bytes包长,-65dBm535665mA 部分睡眠131518mA睡眠0.80.9 1.1mA深度睡眠91011uA关机0.40.50.6uA 2.3.应用原理图注意:供电电源必须保证在3.0V~3.6V,为保证模块能稳定工作,建议外部选择电流大于300mA的LDO。

亿佰特(Ebyte)-无线模块电源设计指南

无线通信早已深入人们的生活,设计无线模块的公司也越来越多,从事射频设计的朋友也越来越多,以下是我总结的一些无线模块的电源设计注意事项分享给各位希望对各位读者有所帮助。

如果有不同意见或建议的也希望大家通过成都亿佰公司的官网微博及时与我们联系,以便我们及时的更正与修改。

以下的分享主要分为电源的性能指标以及电源电路的PCB布局两个方面。

一、电源的性能指标设计电源的主要指标有,负载调整率,电压调整率,纹波等,本文主要从电源的负载调整率,纹波两个方面讨论无线模块的电源指标设计。

1.负载调整率(LOAD REGULATION)负载调整率即电源负载的变化会引起电源输出的变化,负载增加,输出降低,相反负载减少,输出升高。

好的电源负载变化引起的输出变化减到最低,通常指标为3%~5%。

负载调整率是衡量电源好坏的指标,好的电源输出接负载时电压降小。

其负载调整率=(满载时输出电压-半载时输出电压)/额定负载时输出电压。

无线模块的电源设计过程中这一指标也是非常重要的,因为无线模块经常处于接收、发射、休眠等多种模式下其电源所带的负载时常在变化的,因此就要求模块的电源具有良好的电压调整率。

除此之外由于无线模块的特性其在开始发射信号的瞬间会需要很大电流,根据不同功率的模块其瞬态发送电流有所不同,因此设计中也应该考虑到这点给无线模块提供足够大的瞬态电流以保证信号发射的完整性与正确性。

2.纹波简单的讲:纹波就是一个直流电压中的交流成分。

直流电压本来应该是一个固定的值,但是很多时候它是通过交流电压整流、滤波后得来的,由于滤波不干净,就会有剩余的交流成分,即使是用电池供电也会因负载的波动而产生波纹。

事实上,即便是最好的基准电压源器件,其输出电压也是有波纹的。

3.纹波电压的危害:●容易在用设备中产生不期望的谐波,而谐波会产生较多的危害,并且在无线模块的通信系统中谐波会给通信的质量等带来不好的影响。

●纹波较大会降低电源的工作效率,因此也就随之提高了无线模块的整体功耗是的模块在低功耗等应用领域收到局限。

亿佰特(Ebyte)-通信电平转换指南

在我们电路设计中,常常会遇到通信电平转换的问题,在应用电平转换的措施之前还需要判断进行电平转换的必要性。

如果你是用的是3.3V器件作为输出,而5V器件作为接收,那么这种低电平输出不会损坏器件,而且大部分3.3V器件输出高电平的时候也能够满足5V器件的高电平输入标准,这时候你就不需要电平转换。

唯一需要注意的是如果外部5V器件需要从3.3V设备取电流的话,你需要查阅数据手册上对于接口拉电流的最大值。

有需要的话,增加缓冲器件(如74HC245)。

如果反过来,想要使用5V输出的器件驱动3.3V的外设的话,你就需要考虑电平转换器件的必要性了。

但有些3.3V的芯片在设计中已经被设计为可容忍5V输入了。

这样的芯片就可以直接使用5V的主控来直接驱动,最经典的一个例子就是74LVC系列芯片。

CMOS器件对于高低电平的判断标准并不是一个具体值,而是基于电源电压的百分比。

一般来说CMOS器件的高电平标准应大于0.7倍的电源电压(也就是说,用5V供电时,高电平的标准将为3.5V),这就会导致3.3V标准下的高电平无法触发。

但是这也不是绝对的,部分器件可以在3.3V电平标准下正常工作,即使标称的正常工作电压是5V。

对于这种问题,最好还是使用写明了可以兼容3.3V电平标准的器件。

而TTL器件来说,工作在5V电压下时其高电平判断的标准是确定的2V。

这也是为什么单向使用TTL器件的时候能够正常判断电平高低的原因。

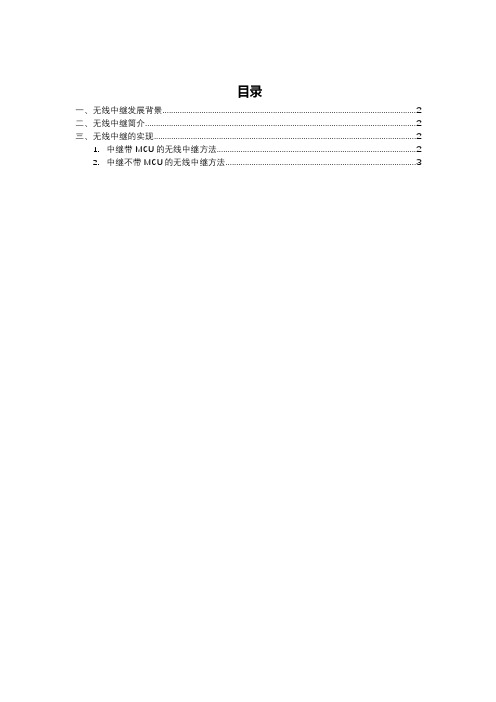

现在我们就介绍几种常用的通信电平转换的方案(1)晶体管+上拉电阻法就是一个双极型三极管或MOSFET,C/D极接一个上拉电阻到正电源,输入电平很灵活,输出电平大致就是正电源电平。

(2)OC/OD器件+上拉电阻法利用OC或者OD门电路,这样集电极或者漏极都可以通过一个电阻上拉到一个新的VCC,其基极或者栅极就可以连接另外一个VCC,这样也就实现了3.3V控制5V的电平信号输出。

注意这里需要选择好上拉电阻阻值,还要考虑MCUIO的驱动能力。

成都亿佰特(Ebyte)-物联网之NB-IoT和LoRa的优势对比

1引言物联网应用需要考虑许多因素,例如节点成本,网络成本,电池寿命,数据传输速率(吞吐率),延迟,移动性,网络覆盖范围以及部署类型等。

可以说没有一种技术可以满足IoT所有的需求。

NB-IoT和LoRa 两种技术具有不同的技术和商业特性,所以在应用场景方面会有不同。

这里会针对二者的区别进行阐述,并且对各自适合的应用场景进行说明。

NB-IoT的优势是什么?作为一项应用于低速率业务中的技术,NB-IoT的优势不难想象:•强链接:在同一基站的情况下,NB-IoT可以比现有无线技术提供50-100倍的接入数。

一个扇区能够支持10万个连接,支持低延时敏感度、超低的设备成本、低设备功耗和优化的网络架构。

举例来说,受限于带宽,运营商给家庭中每个路由器仅开放8-16个接入口,而一个家庭中往往有多部手机、笔记本、平板电脑,未来要想实现全屋智能、上百种传感设备需要联网就成了一个棘手的难题。

而NB-IoT足以轻松满足未来智慧家庭中大量设备联网需求。

•高覆盖:NB-IoT室内覆盖能力强,比LTE提升20dB增益,相当于提升了100倍覆盖区域能力。

不仅可以满足农村这样的广覆盖需求,对于厂区、地下车库、井盖这类对深度覆盖有要求的应用同样适用。

以井盖监测为例,过去GPRS的方式需要伸出一根天线,车辆来往极易损坏,而NB-IoT只要部署得当,就可以很好的解决这一难题。

•低功耗:低功耗特性是物联网应用一项重要指标,特别对于一些不能经常更换电池的设备和场合,如安置于高山荒野偏远地区中的各类传感监测设备,它们不可能像智能手机一天一充电,长达几年的电池使用寿命是最本质的需求。

NB-IoT聚焦小数据量、小速率应用,因此NB-IoT设备功耗可以做到非常小,设备续航时间可以从过去的几个月大幅提升到几年。

•低成本:与LoRa相比,NB-IoT无需重新建网,射频和天线基本上都是复用的。

以中国移动为例,900MHZ 里面有一个比较宽的频带,只需要清出来一部分2G的频段,就可以直接进行LTE和NB-IoT的同时部署。

亿佰特(Ebyte)-高速连传解决方案详解

由于目前市场上的无线模块其主控芯片和RF芯片的性能不高,稳定性不强,只能实现小数据的传输,而面对大数据时,需要分包处理,这对数据的完整性会产生影响以及一定程度上加大了数据处理的难度。

现有模块对电源方面的处理很差,使得电源对射频电路的影响很高,大大降低了模块的传输能力。

针对现有技术中存在的问题,提供一种高速连续无线传输装置,功耗低,灵敏度高,性能稳定,并且使用窄带传输,传输距离长,传输速度快。

E61-TTL-1W是一款高速型433M无线数传模块,内置高性能单片机和高速无线RF芯片,UART串口透明传输,发射功率1W。

在“连续传输方式”下不限数据包的长度,完美实现57600/38400/19200/9600……等串口波特率的连续不间断传输;“定长传输方式”下可灵活配置参数,将数据包在当前配置的空中速率下以最高效的方式传输到对方,实现低延迟/高响应。

此模块包括主控芯片、无线RF芯片和天线接口,主控芯片通过UART串口模块与上位机连接,主控芯片通过SPI总线与无线RF芯片连接,无线RF芯片的收发通路连接有第一射频开关,第一射频开关分别连接有位于发射通路上的功率放大器、位于接收通路上的低噪声放大器,功率放大器和低噪声放大器还同时连接第二射频开关,第二射频开关与天线连接,并在第二射频开关与天线连接通路上设置有五阶π型滤波器、ESD防静电保护路和隔直电容。

主控芯片和无线RF芯片分别连接有第一LDO线性电源模块,功率放大器连接有DC-DC开关电源模块,低噪声放大器连接有第二LDO线性电源模块,第一LDO线性电源模块中设置有π型滤波器。

优选地,所述的主控芯片采用STM8L151G6U6。

优选地,所述的无线RF芯片采用AX5043。

优选地,所述的π型滤波器包括电容和电感。

由于采用了上述技术方案,本实用新型的有益效果是:本实用新型的高速连续无线传输装置可集成与一个模块上,体积小,使用方便;尤其是主控芯片和无线RF芯片稳定、高性能,搭配使用,处理数据量大;射频电路经过处理后,使模块大为优化,其谐波、驻波比、接收灵敏度等都得到大幅度改善,提高了通信能力。

成都亿佰特(Ebyte)-窄带传输与LoRa扩频传输应用方案对比--------------1

一、对比型号E31(433T30D)E32(433T30D)型号E31(433T30D)E32(433T30D)频率范围425~450.5MHz410MHz~441MHz支持波特率1200~1152001200~115200灵敏度-125dBm~-127dBm -145dBm-148dBm支持空速 1.2~70kbps0.3~19.2kbps功率+29dBm~+31dBm +29.5dBm+30.5dBm天线接口SMA SMA供电电压 3.3V~5.2V 3.3V~5.2V模块尺寸43mm*24mm43mm*24mm发射电流598mA~715mA570mA~670mA调制方式(G)FSK(G)MSKA(F)SK FMPSK4-FSK(G)FSK(G)MSKLoRa TMOOK接收电流12mA~14mA19mA~22mA芯片方案AX5043/AX5243SX1278待机电流4uA~6uA4uA~6uA测试距离6000m8000m 上图为成都电子科技有限公司基于AX5043和SX1278两款芯片方案研发的极具有特色的E31系列窄带无线传输模块和E32扩频无线传输模块,上表显示的对比信息为E31系列代表E31(433T30D)(原E31-TTL-1W)和E32系列代表E32(433T30D)(原E32-TTL-1W),从对比参数不难看出两种传输方式在不同性能参数中各具特色。

E31(433T30D)内部使用ON Semiconductor公司的AX5043射频芯片,模块本身采用窄带传输方式,具有功率谱密度集中,稳定性强,抗干扰能力强以及传输距离远等特点。

同时内部软件使用了FEC前向纠错算法,具有纠错能力强,编码效率较高的特点,这种性能的好处就是在突发干扰的情况下,能够将被干扰的数据包主动进行纠正,大大的提高了通信的可靠性和传输距离。

相比扩频传输方案来说,待机电流小,空中传输速率高是其最大的优势。

E32(433T30D)内部使用SEMTECH公司的SX1278射频芯片,模块采用LoRa TM扩频调制解调技术,相比于FSK和OOK调制方式的系统其传输距离大大增加。

亿佰特(Ebyte)-E18-2G4Z27SI产品使用手册 (1)

第一章概述1.1简介E18-2G4Z27SI是一款体积极小的2.4GHz无线模块,贴片型,引脚间距 1.27mm。

该系列模块目前已经稳定量产,并适用于多种应用场景(尤其智能家居)。

E18-2G4Z27SI采用美国德州仪器(TI)公司原装进口CC2530射频芯片,芯片内部集成了8051单片机及无线收发器,并内置PA+LNA,极大的扩展通信距离、提升通信稳定性。

并适用于ZigBee设计及2.4GHz IEEE802.15.4协议。

模块引出单片机所有IO口,可进行多方位的开发。

1.2特点功能⚫实测通信距离可达2500m;⚫最大发射功率500mW,软件多级可调;⚫内置ZigBee协议栈;⚫出厂自带自组网固件,到手即用;⚫支持ADC、PWM、GPIO等外设直驱;⚫支持UART透传,简单易用;⚫内置32.768kHz时钟晶体振荡器;⚫支持全球免许可ISM2.4GHz频段;⚫丰富的资源,256KB FLASH,8KB RAM;⚫内置PA+LNA,提高了整体通信抗干扰性能;⚫具有代码预取的高性能低功耗8051微控制器内核;⚫支持2.5V~3.6V供电,大于3.3V供电均可保证最佳性能;⚫工业级标准设计,支持-40~85°C长时间使用;⚫IPEX接口,可方便连接同轴电缆或外置天线。

1.3应用场景⚫智能家居以及工业传感器等;⚫安防系统、定位系统;⚫无线遥控,无人机;⚫无线游戏遥控器;⚫医疗保健产品;⚫无线语音,无线耳机;⚫汽车行业应用。

第二章规格参数2.1极限参数2.2工作参数第三章械尺寸与引脚定义14P1.1输出单片机GPIO,PA发射控制引脚15P1.0输出单片机GPIO,PA接收控制引脚16P0.7输入/输出单片机GPIO17P0.6输入/输出单片机GPIO18P0.5输入/输出单片机GPIO19P0.4输入/输出单片机GPIO20P0.3输入/输出单片机GPIO21P0.2输入/输出单片机GPIO22P0.1输入/输出单片机GPIO23P0.0输入/输出单片机GPIO24RESET输入复位端口⚫对应IO功能,请至官网下载《E18_Software_Datasheet_CN》查阅;⚫若需二次开发,关于模块的引脚定义、软件驱动及通信协议详见TI官方《CC2530Datasheet》。

成都亿佰特(Ebyte)-无线模块超远距离传输中实现中继的方法

目录一、无线中继发展背景 (2)二、无线中继简介 (2)三、无线中继的实现 (2)1.中继带MCU的无线中继方法 (2)2.中继不带MCU的无线中继方法 (3)一、无线中继发展背景近年来,随着社会的发展和科学技术的进步,人们开始进入数字网络化的智能社会,各种各样的智能设备改变着我们的生活,而无线传输在这些智能化发展中占有不可或缺的地位。

在无线网络中,实现终端间的数据传输媒体主要有无线电波,但由于无线电波存在衰减,并且频率越高,无线电波随距离衰减越快,因此高工作频率将导致网络中基站的覆盖范围十分有限,针对这一点,在现有的无线电波的传输基础上,采用中继的方法,可以让覆盖范围变得更加广泛,提高了无线传输的应用领域。

二、无线中继简介所谓的无线中继,就是能够将无线发送方发来的无线信息转发出去,让无线目标终端能够接收到发送端的信息。

在一条链路中,无线中继可以有多个,并不是只允许一个无线中继的存在。

无线中继越多,传输的时间越长,但传输的距离越远。

在一条无线中继链路中,无线终端是可以实现双向收发的,只要无线模块既能收,又能发。

传统的能多无线模块,很多都是要么只能收,要么只能发送的;还有的虽然收发功能都具有,但是收发转换需要用户转换,使用起来很不方便。

笔者使用过成都公司的无线模块,该公司模块都是收发一体的,使用起来很方便,模块不发送数据的时候,就是接收状态,就可以接收同频段的无线信号;在模块收到用户设备通过串口发送过来的数据的时候,我们就自动切换到发射模式,将收到的数据发送出去,完全实现自动切换收发。

使用这类无线收发模块,就能够组成一个双向传输的无线中继链路,实现长距离的传输。

无线终端A第N个中继无线终端B三、无线中继的实现无线中继的实现也是很简单的,成本也相对比较低,下面以成都无线模块为例进行阐述。

成都的无线收发模块是转串口的,通过串口就可以实现数据收发,用户无线编写驱动程序,往模块串口发送数据,模块就能启动发射,接收端收到数据后,通过串口把数据打印出来,对用户来说,使用起来是很方便的,用于实现中继,也是很简单方面的。

亿佰特物联网dtu无线数传电台:新一代Lora无线模块通信技术

亿佰特物联网dtu无线数传电台:新一代Lora无线模块通信技术无线数传模块有的也称呼为无线数传电台,通常把功率小、体积小的无线数传技术设备叫做无线模块,把放射功率大、5W~25W,甚至更大功率的无线数传设备称为电台(简称:DTU)。

1、大功率无线数传电台的无线通信研发、生产于一体的模块原厂厂家,缘于我国的软件及硬件技术比一些发达国家落后,无线数传电台的系统集成技术水平还比较低。

因而无线数传电台仅仅是在水利、电力、冷水、物联网指挥农业等比较少数的四五个物联网领域开展一点实验性的、小范围的、小批量的技术应用。

发觉无线数据通信的进展前景之后,无线通讯模块研发及生产厂家,当初的管理睬还特地开拓出了223~235MHz频段的无线数据通信频段。

2)数据越发稳定:基于LoRa新一代扩频技术的研发应用,带有金属屏蔽罩,抗干扰性能强,内建多种异样处理机制,保证了模块与电台的长时光稳定运行。

3、低功耗:对于大功率遥控器来说设备的输出,设备有1路电源输出,内部与设备的供电端短接,可用于外部设备的驱动,驱动能力与电源输入容量相关。

我国在无线数据通信技术方面,尤其是lora无线通讯模块,与欧、美、日等发达国家相比,起步较晚,起码落后了20年左右,但进展较快。

无线数传电台概念在我国的形成,应当是在80年的代初期,但在囫囵80年月,我国的无线通信技术得到大幅度的提升及广泛应用。

成都亿佰特基于国家对高新技术的大力支持,在无线通信技术封面投入了很大的研发力度,目前亿佰特在物联网无线通信技术方面拥有数百项发明和有用新型专利,产品通过SRRC、FCC、CE、MIC、KC、NCC等权威认证,远销全球50多个国家和地区,获得广泛美誉。

大功率遥控器物联网无线通讯模块厂家,因为我国的软件及硬件技术还比较落后,系统集成水准还比较低。

因此数传电台也只是在水利、电力、自来水等*少数的几个领域举行一些实验性的、小范围的、小批量的应用。

看到无线数据通信的进展前景,无线通讯模块生产厂家,当初的无线电管理睬还辟出了频段223~235MHz第1页共2页。

亿佰特LoRa MESH组网模块产品功能及应用简介

亿佰特LoRa MESH组网模块产品功能及应用简介E52-400/900NW22S是一款基于LoRa扩频技术的无线串口LoRa MESH组网模块,最大输出功率为+22dBm,最高空中速率可达62.5K,最大支持波特率460800 bps。

E52-400NW22S模块工作频段范围 410.125~509.125 MHz(默认 433.125 MHz),E52-900NW22S 模块工作频段范围 850.125~929.125MHz(默认 868.125MHz)。

E52-400/900NW22S采用全新LoRa MESH组网技术,具有去中心化、自路由、网络自愈、多级路由等功能特点,适用于智能家居以及工业传感器、无线报警安全系统、楼宇自动化解决方案、智慧农业等应用场景。

LoRa MESH 组网模块特点功能LoRa MESH:采用先进的 LoRa 调制方式,具有远距离抗干扰的优点,大大提高整个 MESH 网络的覆盖范围;去中心化:整个网络只由终端节点和路由节点两种类型节点组成,不需要中心节点或协调器参与网络管理;自动路由:发起数据请求时,各路由节点能自动与周围节点发起连接,确定数据传输路径,无需协调器参与路径规划;网络自愈:当链路故障时,路由节点在几次尝试通讯失败后重新建立新的路径;多级路由:路由节点可自动将数据传输到下级路由,由自动生成的路由表控制数据的传输方向;路径优化:路由信息会随着网络中的数据传输而不断地自动更新优化,保证整个网络的稳定性;避让机制:CSMA 避让机制能大大减少空中信号碰撞的可能性;通讯方式:支持单播(Unicast)、多播(Multicast)、广播(Broadcast)和泛播(Anycast)四种通讯方式;E52-400NW22S 无线串口LORA MESH组网模块频率范围:工作于410.125~509.125MHz 频段,支持100个信道,信道间隔为1MHz;E52-900NW22S无线串口LORA MESH组网模块频率范围:工作于850.125~929.125MHz,支持80个信道,信道间隔为1MHz;多重校验:保证数据传输过程的可靠性和准确性;加密传输:数据传输过程中采用特殊的加密算法,保证数据的安全性和隐私性;高吞吐量:整个网络在时间、空间相结合,实现高并发性能;远程配置:支持远程更改整个网络的基本通讯参数。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

28GHz5G通信频段射频前端模块深度解析随着5G毫米波预期即将进入商用,行业内关键公司的研发正在顺利推进,已经完成定制组件指标划定、设计和验证。

实现未来毫米波5G系统所需的基本组件是射频前端模块(FEM)。

该模块包括发射机的最终放大级以及接收机中最前端的放大级以及发射/接收开关(Tx/Rx)以支持时分双工(TDD)。

FEM必须在发射模式下具备高线性度,并在接收模式下具备低噪声系数。

由于毫米波5G系统可能需要用户终端采用多个FEM构成相控阵架构或开关天线波束架构。

因此FEM必须采用高效、紧凑和低成本的方式实现,且最好能简单控制和监测。

本文介绍了符合以上所有要求的28GHz5G通信频段(27.5至28.35GHz)射频前端模块MMIC(单片微波集成电路)的设计、实现和验证。

该射频前端由Plextek RFI公司开发,采用WINSemiconductors(稳懋半导体)的PE-154V电压、0.15μm、增强型GaAs PHEMT工艺实现。

它采用紧凑型低成本且兼容SMT(表贴)安装的5mm x5mm二次注塑兼容QFN封装,适用于大批量、低成本的制造。

它涵盖27至29GHz,因此支持完整的28GHz5G频段。

1.设计目标FEM发射通道的设计着重于功率回退下实现高效率,以提供线性放大,这是5G通信系统提出的要求。

功率回退下的目标功率附加效率(PAE)定为6,三阶交调(IMD3)低于-35dBc(功率回退值:从1dB压缩点开始大约退回7dB)。

对应1dB压缩点(P1dB)的RF输出功率定为20dBm。

而接收通道需要在非常低的电流消耗下(最大15mA,+4V电源),实现低于4dB的噪声系数(包括开关损耗)。

射频前端MMIC的功能框图如图1所示。

发送信号路径从图的上半部分中的左侧延伸到右侧;输入端口位于标有“PA_RFin”的引脚上。

输入信号由三级功放(PA)放大,然后通过RF功率检测器和单刀双掷(SPDT)开关连接至天线。

片上定向功率检测器可监测发射出的射频输出功率,并且片上集成了温度补偿功能。

带补偿的功率检测器输出由电压“Vref”和电压“Vdet”之间的差值决定。

芯片内集成了由(低电平有效)逻辑信号“PA_ON”控制的快速开关赋能电路(图1中的PA赋能电路)。

可在发射和接收模式之间切换时,快速给PA上电和断电,从而在PA不用时达到仅使用0.1mA的电流,最大限度地提高整个系统的效率。

PA通常会工作在从压缩点回退几dB的条件下,以保持其发射的调制信号不严重失真。

设计方法是优化功率放大器工作在P1dB点回退7dB左右的性能。

为了在该工作条件下达到较优的PAE,PA将偏置在深AB类。

2.设计折中策略该设计起始于对候选单元晶体管进行器件级仿真。

这项仿真工作可以获得如器件尺寸、偏置点、目标阻抗、PA级数和驱动器比率等关键信息,为后续精细的功率放大器设计奠定了坚实的基础。

这项工作的一个重要部分在于确定如何最大限度地提高功率回退下的PAE。

一般来说,可通过降低器件静态偏置电流密度来实现。

但是该方法中电流密度可往下调的范围受限于增益和线性度约束,因为这两者都随着电流密度的降低而恶化。

功率回退条件下的PAE和增益与线性度之间有明确的折中关系。

设计中主要关心的线性度指标是在功率回退条件下,IMD3必须小于-35dBc。

如图2所示,在偏置电流降低的情况下,IMD3性能对基频负载条件特别敏感。

图2a显示了偏置为深AB类的8×50μm器件在4V、75mA/mm时的负载牵引仿真结果,并标出了P1dB下的PAE最佳点对应的负载。

该图还给出了仿真所得该最佳负载和功率回退条件下IMD3的性能,表明离-35dBc 的指标还有大约4dB的裕度。

仿真的PAE在该功率回退条件下约为15,且该效率只计入器件的作用,不包括任何输出损耗。

图2b显示了相同器件和偏置工作条件下,P1dB功率最佳点对应的负载以及IMD3等信息。

发现在相同的相对功率回退情况下,其IMD3的性能明显更差,超出指标5dB以上,而此时PAE和前一种条件相似,约为15.7。

图2:P1dB条件下最佳PAE对应的阻抗点以及对应的功率回退条件下的IMD3(a);P1dB条件下最佳功率对应的阻抗点以及对应的功率回退条件下的IMD3(b)。

进一步评估了史密斯圆图上的其他阻抗点下,功放的P1dB和功率回退两种条件下的性能。

图2a中的负载条件明显具有最好的综合性能,因此被选定用于输出级设计。

最终选择了52mA/mm的偏置电流,并选择了8x50μm器件作为输出级的基本单元,以满足功率指标要求。

并根据总的传输增益指标确定了需要三级放大。

通过依次为驱动放大级和预驱动放大级选择最佳晶体管尺寸来设计完整的三级功率放大器。

这同样需要仔细考虑设计折中,因为较大的晶体管尺寸可改善整体线性度但会降低PAE。

当所有晶体管的尺寸和偏置确定后,就可以继续进行匹配和偏置电路的详细设计。

版图设计从整个设计过程的早期阶段就需要开始考虑,以避免不引入过大的寄生效应以及确保设计的可实现性。

功放的第一和第二级使用共同的栅极偏置引线(加在引脚PA_Vg12上),而第三级设置单独的偏置引线(PA_Vg3)。

这样就可以单独优化两个电压,以对PA的线性度或PAE进行提升。

漏极供电可以类似地通过两个独立的引脚施加+4V电压在“PA_Vd12”和“PA_Vd3”上,尽管这两个引脚在PCB板上是相连的。

SPDT开关采用串并结构,该设计中的串联和并联分支中集成了多个晶体管以提高线性度1。

晶体管截止时的电容限制了关断状态下器件在高频率处的固有隔离度,在28GHz时开关晶体管的隔离度仅为几dB2。

减小晶体管尺寸可以改善固有隔离度,但会增加导通状态下的插入损耗并降低其线性度,因此不是一种可行的选择。

这里采取的方法是采用片上电感补偿来改善关断状态隔离度。

经过细致设计确保导通状态下具有较低插入损耗,以实现发射通道的高输出功率和接收通道的低噪声系数。

开关由一个比特位控制电压“Vctrl1”控制,该位设置为4V时表示发射模式、0V时表示接收模式。

“单刀双掷控制电路”(SPDT控制电路)可实现单比特控制,该电路本质上是一对二线译码器。

控制电路和SPDT本身消耗的总电流仅1mA,由“VD_SW”处施加的+4V电源提供。

接收通道的输入位于通过SPDT连接到两级LNA输入的“天线”引脚处。

接收通道的输出位于标记为“LNA_RFout”的引脚上。

与PA一样,LNA也具有快速开关赋能电路,使得LNA在不工作时仅消耗低至0.1mA的电流。

低噪声放大器设计过程的关键是找到一种消耗电流低、又具有良好噪声系数和足够线性度的设计。

重要的第一步是选择合适的晶体管尺寸。

可使用多个短叉指来减小晶体管的栅极电阻并改善噪声系数。

低噪放的两级都采用了串联感性反馈,以使最佳噪声系数所需的阻抗更接近于共轭匹配和最佳增益所需的阻抗。

低噪声放大器的第一级以噪声系数为设计优化目标,但仍需产生足够的增益才能充分降低第二级噪声系数的影响。

低噪放第二级的噪声系数并不重要,因此这级设计成比第一级有更高的增益。

设计得到的LNA仅需要+4V电源的10mA直流电流。

栅极偏置电压施加在引脚“LNA_Vg”上,而+4V漏极偏置电压加在“LNA_Vd”上。

“LNA_Vsense”引脚则提供对偏置电流的监测。

监测到的偏置电流信息可以用于控制栅极电压以补偿例如温度等环境条件的变化。

在正确偏置下,此监测引脚的电压为3.9V。

使用增强型晶体管的工艺意味着只需要正电源电压,从而使MMIC非常便于系统集成。

仔细的电磁仿真对确保各个模块良好的射频性能是非常重要的。

采用了逐步添加的方法,每次将电路的一部分加入到EM仿真中,而其余部分仍使用工艺设计套件(PDK)中的模型进行仿真。

由于集成电路用于二次注塑工艺所得塑料封装中,所以在集成电路上方注塑的化合物也需要在电磁仿真中考虑。

3.评估和测试图3是射频前端芯片的照片。

该射频前端MMIC芯片尺寸为3.38mm×1.99mm。

其焊盘/引脚位置与框图中所示的位置相似,并且它还多集成了多个接地盘,以使其完全可以进行在片射频测试(RFOW)。

它被设计为采用低成本注塑成型5mm×5mm QFN封装。

并且考虑到铸模塑料的影响,需要精心设计从芯片到PCB的射频过渡界面。

设计了定制的引线框架用于实现该过渡,并且封装体上的射频端口都被设计为接地-信号-接地(GSG)界面。

完成加工制造之后,对多块芯片进行了在片射频测试,以便在封装之前确认芯片达成了一次流片即成功的设计目标。

这里没有给出在片射频测试结果,给出的所有结果都是芯片完整封装后安装在典型PCB评估板上后测量得到的。

PCB评估板采用低成本层压板材料设计,适合大批量生产。

将封装好的射频前端模块样品组装到PCB评估板上;所有测量的性能都校准到PCB评估板上的封装引脚处,从而包含了芯片到PCB过渡结构的影响。

设计了TRL校准单元来将测量的性能校准到封装的参考面。

图4显示了TRL校准PCB板,以及一块PCB评估板的照片。

射频前端模块MMIC安装在PCB上,并以封装的射频引脚为参考面获取验证结果。

在验证过程中使用市售的多通道DAC和ADC芯片来控制和监测射频前端模块。

该射频前端模块不需要任何负电压,因为它采用的是增强型工艺。

图5给出了一个典型射频前端模块的发射通道的测量与仿真S参数的比较。

测量数据和仿真结果相当吻合。

在此模式下,LNA被关闭,SPDT控制位“Vctrl1”切换为高电平,而PA则偏置在+4V电压下约70mA总静态电流。

从27到29GHz,小信号增益(S21)为17.1dB±0.4dB。

输入反射衰减(S11)在整个频段优于18dB。

由于输出匹配是按功率回退条件下最佳PAE设计,而不是最好的S22,尽管如此测量到的S22(未给出图示)在整个频带上为8dB或更好。

以输出为参考的发射通道的三阶截取点(OIP3)以100MHz的频率间隔进行评估,以反映5G系统中的宽信道带宽。

图6是典型射频前端模块的实测OIP3与有用频率的功率之间的关系图,其功率范围从1至11dBm。

可以看出该5G频段上的OIP3约为+28dBm,有用频率功率在10dB范围内变动时,OIP3变化很小。

测量到的和仿真的OIP3与频率的关系如图7所示,具有良好的一致性。

尽管5G通信系统需要线性放大来保持调制保真度,但为了提供一个便于比较的性能指标,还是有必要测量输出P1dB和PAE。

测量所得性能如图8所示,可见P1dB在20.2dBm左右,并在饱和时上升到21dBm。

FEM的发射通道PAE约为20,仅在该频带的高段略有下降。

如上所述,该FEM的设计是为了实现从P1dB回退7dB左右时的最佳性能指标(OIP3和PAE)。