vga显示verilog代码

verilog的VGA显示控制

Verilog的VGA显示控制from : 好友博客:/blog/?uid-20-action-viewspace-itemid-591一、VGA时序下面的图是本人画了一个晚上的结果,个人认为能够比较详细的阐述VGA的信号时序VGA的时序根据不同的显示分辨率和刷新频率会有变化,具体各种类型的时序信息可以参考下面的网站这里非常详细的说明的每一种显示模式的VGA时序信息/documents/pc/vga_timing.html二、VGA电平VSYNC,HSYNC为标准TTL电平,0V~3.3VRGB的电平在0V~0.7V之间(0V为黑色,0.7V为全色)三、程序顶层框图VGA产生行同步(HSYNC),场同步信号(VSYNC),并产生每个像素的地址输入单口ROM(显存)中,ROM输出该点需要显示的颜色值四、单口ROM(显存)设计程序的显示模式为800*600,72Hz刷新频率,像素频率为50MHz每个像素需要显示的颜色存储在单口RAM中,每种颜色用8个字节表示则如果要显示800*600分辨率,则需要800*600字节(480KB)的单口ROM由于FPGA内部没有这么大的RAM,因此我把屏幕上100*100个像素组成的矩形作为一个逻辑像素(即显示同一种颜色)这样只要8*6字节(48字节),用FPGA自带的RAM是很容易实现的ROM中颜色存储地址表:将全屏划分成8*6的方格,每个方格的颜色存储在ROM中,VGA控制器不断产生行坐标(ROM水平地址)和场坐标(ROM垂直地址)最后组合成ROM实际地址输入ROM中,ROM输出该地址的颜色值,显示在LCD中五、程序设计代码1module VGA(clk,rst_n,hsync,vsync,vga_r,vga_g,vga_b);2345input clk; //50MHz67input rst_n; //复位信号89output hsync; //行同步信号1011output vsync; //场同步信号1213// R、G、B信号输出1415output[1:0] vga_r;1617output[2:0] vga_g;1819output[2:0] vga_b;2021//--------------------------------------------------2223reg[10:0] x_cnt; //行坐标(这里包括了行同步、后沿、有效数据区、前沿)2425reg[9:0] y_cnt; //列坐标(这里包括了场同步、后沿、有效数据区、前沿)2627reg[5:0] Xcoloradd;2829reg[2:0] Ycoloradd;30313233parameter3435 Left = 184,3637 PixelWidth = 100,3839 Top = 29;40414243always @ (posedge clk or negedge rst_n)4445if(!rst_n) x_cnt <= 10'd0;4647else if(x_cnt == 11'd1040) x_cnt <= 10'd0; //行计数记到104 04849else x_cnt <= x_cnt+1'b1;50515253always @ (posedge clk or negedge rst_n)//产生行地址(ROM水平地址)5455if(!rst_n) Xcoloradd <= 6'b000000;5657else if(x_cnt >= Left && x_cnt <Left + PixelWidth) Xcoloradd <= 6' b000000;5859else if(x_cnt >= Left + PixelWidth && x_cnt <Left + 2*PixelWidt h) Xcoloradd <= 6'b000001;6061else if(x_cnt >= Left + 2*PixelWidth && x_cnt <Left + 3*PixelWidt h) Xcoloradd <= 6'b000010;6263else if(x_cnt >= Left + 3*PixelWidth && x_cnt <Left + 4*PixelWidt h) Xcoloradd <= 6'b000011;6465else if(x_cnt >= Left + 4*PixelWidth && x_cnt <Left + 5*PixelWidt h) Xcoloradd <= 6'b000100;6667else if(x_cnt >= Left + 5*PixelWidth && x_cnt <Left + 6*PixelWidt h) Xcoloradd <= 6'b000101;6869else if(x_cnt >= Left + 6*PixelWidth && x_cnt <Left + 7*PixelWidt h) Xcoloradd <= 6'b000110;7071else if(x_cnt >= Left + 7*PixelWidth && x_cnt <Left + 8*PixelWidt h) Xcoloradd <= 6'b000111;7273else Xcoloradd <= 6'b110000;//背景颜色地址74757677always @ (posedge clk or negedge rst_n)7879if(!rst_n) y_cnt <= 10'd0;8081else if(y_cnt == 10'd666) y_cnt <= 10'd0; //场同步记到66 68283else if(x_cnt == 11'd1040) y_cnt <= y_cnt+1'b1;//每计数完一行,场同步就加一84858687always @ (posedge clk or negedge rst_n)//产生列地址(ROM垂直地址)8889if(!rst_n) Ycoloradd <= 3'b000;9091else if(y_cnt >= Top && y_cnt < Top + PixelWidth) Ycoloradd <= 3'b 000;9293else if(y_cnt >= Top + PixelWidth && y_cnt < Top + 2*PixelWidth) Y coloradd <= 3'b001;9495else if(y_cnt >= Top + 2*PixelWidth && y_cnt < Top + 3*PixelWidt h) Ycoloradd <= 3'b010;9697else if(y_cnt >= Top + 3*PixelWidth && y_cnt < Top + 4*PixelWidt h) Ycoloradd <= 3'b011;9899else if(y_cnt >= Top + 4*PixelWidth && y_cnt < Top + 5*PixelWidt h) Ycoloradd <= 3'b100;100101else if(y_cnt >= Top + 5*PixelWidth && y_cnt < Top + 6*PixelWidt h) Ycoloradd <= 3'b101;102103else Ycoloradd <= 3'b110;//背景颜色地址104105//--------------------------------------------------106107// signal port ROM108109110111wire[7:0] color;112113wire[5:0] coloradd;114115116117assign coloradd = {Ycoloradd,3'b000}|Xcoloradd;//将水平地址和垂直地址合成R OM实际地址118119sprom u1(coloradd,clk,color);120121122123//---------------------------------------------------124125126127wire valid; //有效数据显示区标志,就是你在液晶屏幕上可以看到的区域128129130131assign valid = (x_cnt > 10'd184) && (x_cnt < 10'd984)132133134135 && (y_cnt > 10'd29) && (y_cnt < 10'd629);136137//--------------------------------------------------138139reg hsync_r,vsync_r;140141142143always @ (posedge clk or negedge rst_n)144145if (!rst_n) begin146147 hsync_r <= 1'b0;148149 vsync_r <= 1'b0;150151 end152153else begin154155 hsync_r <= x_cnt >= 10'd120; //产生hsync信号(行同步)when x_cnt>=50,t hen hsync_r=1,else 0;低电平同步156157 vsync_r <= y_cnt >= 10'd6; //产生vsync信号(场同步)my LCD is low syn c158159 end160161assign hsync = hsync_r;162163assign vsync = vsync_r;164165166167//--------------------------------------------------168169//颜色输出170171assign vga_r[1] = valid ? color[7] : 1'b0;172173assign vga_r[0] = valid ? color[6] : 1'b0;174175176177assign vga_g[2] = valid ? color[5] : 1'b0;178179assign vga_g[1] = valid ? color[4] : 1'b0;180181assign vga_g[0] = valid ? color[3] : 1'b0;182183184185assign vga_b[2] = valid ? color[2] : 1'b0;186187assign vga_b[1] = valid ? color[1] : 1'b0;188189assign vga_b[0] = valid ? color[0] : 1'b0;190191192193endmodule194六、后记在这次程序中只在ROM中存储了一些随机的数,因此显示出来是一些小方格如果ROM做的更大,完全可以存储一幅图像,显示在LCD中不过由于由于用ROM做为显存,每次只能显示一幅静态的图像,而且没有加入字符库,不能显示字符在下次的文章中,我将使用双口RAM,加上Nios II处理器,这样可以方便的显示各种字符标签: IC design, 转载。

基于FPGA的VGA显示详解(附VHDL代码)

基于FPGA的VGA显示(后附VHDL代码)整个VGA的时序操作很简单,就是形成一个具有一定占空比的电平周期。

只是整个VGA的操作涉及到一些专有名词,理解上比较困难,一旦明白了这些是什么意思后,操作即将变得很简单。

VGA工作流程:常见的彩色显示器,一般由CRT (阴极射线管)构成,彩色是由R、G、B(红、绿、蓝)三基色组成,CRT用逐行扫描或隔行扫描的方式实现图像显示,由VGA控制模块产生的水平同步信号和垂直同步信号控制阴极射线枪产生的电子束,打在涂有荧光粉的荧光屏上,产生R、G、B三基色,合成一个彩色像素。

扫描从屏幕的左上方开始,由左至右,由上到下,逐行进行扫描,每扫完一行,电子束回到屏幕下一行的起始位置,在回扫期间,CRT对电子束进行消隐,每行结束是用行同步信号HS进行行同步;扫描完所有行,再由场同步信号VS进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,预备下一场的扫描。

行同步信号HS 和场同步信号VS是两个重要的信号。

注意点:什么时候消隐?为什么要消隐?当一行扫描完毕后然后电子枪又转到下一行的这段时间或是扫描完所有的行后电子枪回到第一行的这段时间,这两段时间都要消隐。

在消隐的时间内,数据是无效的。

这样就保证电子枪的回扫的个动作不干扰显示,因为回扫这个动作是很频繁的,若在这个时间段内数据有效,那么就回在显示屏上出现电子枪回扫的轨迹。

消隐的时候我们干什么?消隐这个动作是显示屏(CRT)执行的,我们在编程时只要注意有这么个东西就行。

同步信号(包括HS和VS)是什么?这个就相当于一个数据起始信号,表明数据马上就要开始了。

如果撇开具体的设备,那么这个信号和AD、DA中常用的Sync(同步)、CS(片选)信号相当。

该信号一般为负电平,但对于有的显示器可不关心该信号的极性,因为它内部可自动转换正负逻辑。

对于普通的VGA显示器,需要引出5个信号:R,G,B:三原色;HS:行同步信号;VS:场同步信。

FPGA基础设计之VGA显示方法(文字、图形、波形)

FPGA基础设计之VGA显示方法(文字、图形、波形)概述VGA是一种学习FPGA最常见的基础实验。

虽然现在的显示屏大多已经采用DVI和HDMI 方案,但其实VGA在另一个地方还有应用,那就是大屏的LCD。

目前4.3寸以上的TFT 基本都是VGA接口,这样在完成一个FPGA系统设计时,选择一个VGA接口的TFT用来显示便是最简单方便的方案。

现在2017年全国大学生电子设计大赛还有不到一个月,熟练的使用VGA显示各种图形、文字、波形还是很重要的,而不是停留在只能显示彩条的入门实验上。

这篇博文便致力于解决这个问题。

VGA显示驱动目前常见的电路板上的VGA接口是这样的,单独使用R、G、B三条线控制颜色:或者是这样的,增加一个电阻网络来使可以控制的颜色更加丰富:现在应该很少会看到专门使用VGA驱动芯片的了。

使用电阻网络已经能获得不错的显示效果。

FPGA需要处理的信号有行同步信号HSYNC和场同步信号VSYNC,以及R、G、B三组颜色控制信号。

在驱动VGA之前,我们首先要确定自己的显示参数,分辨率及刷新率,比如800*600@60Hz的显示方式其时序参数如下所示:不同的分辨率和刷新率有不同的参数,这个数据可以在这个网页中查到。

进下来就进行VGA的时序驱动,我的习惯是先将关键性数据用parameter定义出来://-------------------------------------------------//// 扫描参数的设定640*480 60Hz VGA//-------------------------------------------------//parameter H_SYNC_END = 96; //行同步脉冲结束时间。

新手请教verilog实现VGA显示移动小球的问题

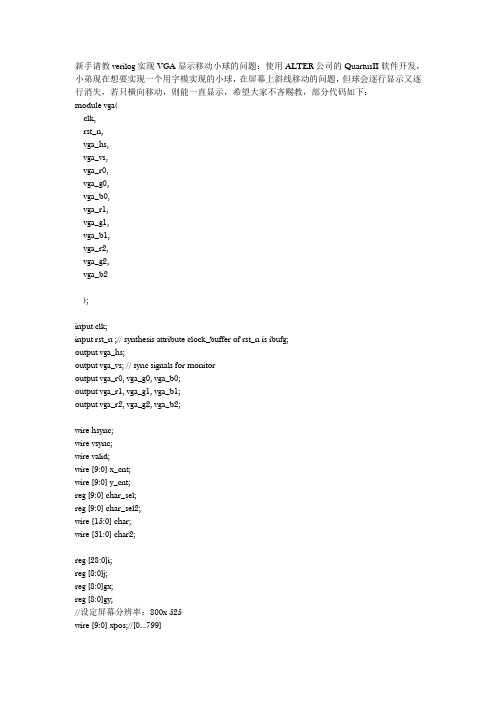

新手请教verilog实现VGA显示移动小球的问题:使用ALTER公司的QuartusII软件开发,小弟现在想要实现一个用字模实现的小球,在屏幕上斜线移动的问题,但球会逐行显示又逐行消失,若只横向移动,则能一直显示,希望大家不吝赐教,部分代码如下:module vga(clk,rst_n,vga_hs,vga_vs,vga_r0,vga_g0,vga_b0,vga_r1,vga_g1,vga_b1,vga_r2,vga_g2,vga_b2);input clk;input rst_n ;// synthesis attribute clock_buffer of rst_n is ibufg;output vga_hs;output vga_vs; // sync signals for monitoroutput vga_r0, vga_g0, vga_b0;output vga_r1, vga_g1, vga_b1;output vga_r2, vga_g2, vga_b2;wire hsync;wire vsync;wire valid;wire [9:0] x_cnt;wire [9:0] y_cnt;reg [9:0] char_sel;reg [9:0] char_sel2;wire [15:0] char;wire [31:0] char2;reg [28:0]i;reg [8:0]j;reg [8:0]gx;reg [8:0]gy;//设定屏幕分辨率:800x 525wire [9:0] xpos;//[0...799]wire [9:0] ypos;//[0...524]reg color;reg color2;reg word0;reg globe0;//reg [8:0]adr_g;assign xpos = x_cnt - 10'd180; //确定X轴像素位置assign ypos = y_cnt - 10'd35; //确定Y轴像素位置sync_gen_50m sync_gen_50m_int (.clk ( clk ),.rst_n ( rst_n ),.hsync ( hsync ),.vsync ( vsync ),.valid ( valid ),.x_cnt ( x_cnt ),.y_cnt ( y_cnt ));wire table0 = (( ypos > 10'd140 && ypos < 10'd460 )&&( xpos > 10'd160 && xpos < 10'd640 )); //显示一个方框wire line0 = (( ypos == 10'd140 || ypos == 10'd460 ) && ( xpos > 10'd160 && xpos < 10'd640 )|| ( xpos == 10'd160 || xpos == 10'd640 ) && ( ypos > 10'd140 && ypos < 10'd460 )); //方框边线wire word = word0 && color;wire globe=globe0 && color2;assign vga_r0 = valid ? (globe?1:(word ? 1'b1 : (line0 ? 1'b1 : (table0? 1'b0 : 1'b1 )))) : 1'b0;assign vga_g0 = valid ? (globe?0:(word ? 1'b1 : (line0 ? 1'b1 : (table0? 1'b0 : 1'b0 )))) : 1'b0;assign vga_b0 = valid ? (globe?0:(word ? 1'b0 : (line0 ? 1'b1 : (table0? 1'b0 : 1'b1 )))) : 1'b0;assign vga_r1 = valid ? (globe?1:(word ? 1'b1 : (line0 ? 1'b1 : (table0? 1'b0 : 1'b1 )))) : 1'b0;assign vga_g1 = valid ? (globe?0:(word ? 1'b1 : (line0 ? 1'b1 : (table0? 1'b0 : 1'b0 )))) : 1'b0;assign vga_b1 = valid ? (globe?0:(word ? 1'b0 : (line0 ? 1'b1 : (table0? 1'b0 : 1'b1 )))) : 1'b0;assign vga_r2 = valid ? (globe?1:(word ? 1'b1 : (line0 ? 1'b1 : (table0? 1'b0 : 1'b0 )))) : 1'b0;assign vga_g2 = valid ? (globe?0:(word ? 1'b1 : (line0 ? 1'b1 : (table0? 1'b0 : 1'b0 )))) : 1'b0;assign vga_b2 = valid ? (globe?0:(word ? 1'b0 : (line0 ? 1'b1 : (table0? 1'b0 : 1'b1 )))) : 1'b0;assign vga_hs = hsync;assign vga_vs = vsync;char_rom char_rom_VibesIC_inst(.addr ({char_sel[9:5],ypos[4:1]}), //字符的Y轴由16 pixel变为32 pixel.data (char)always @(posedge clk)beginword0 = ((xpos > (10'd460-j)) && (xpos < (10'd780-j)) && (ypos > 10'd96) && (ypos < 10'd128));char_sel = xpos -10'd460+j;globe0=((xpos>10'd384+gx)&&(xpos<10'd416+gx)&& //小球位置(ypos>10'd140-gy)&&(ypos<172-gy));char_sel2=xpos-10'd384; //小球X轴初始位置if(i==29'h01Ef480)begini=0;j=j+1;gx=gx-1;//小球X轴改变量gy=gy+1;//小球Y轴改变量if(j>280)j=0;if(gx==160)begin gx=384;gy=140;end //小球初始位置if(gx==0)begin gx=384;gy=140;endendelse i=i+1;endalways @(char_sel[4:1] or char)begincase (char_sel[4:1])4'h0 : color = char[15]; //将X轴对应点赋给color4'h1 : color = char[14];4'h2 : color = char[13];4'h3 : color = char[12];4'h4 : color = char[11];4'h5 : color = char[10];4'h6 : color = char[9];4'h7 : color = char[8];4'h8 : color = char[7];4'h9 : color = char[6];4'hA : color = char[5];4'hB : color = char[4];4'hC : color = char[3];4'hD : color = char[2];4'hE : color = char[1];4'hF : color = char[0];endcasechar_rom_2 char_rom_VibesIC_inst2(.addr ({char_sel2[8:5],ypos[4:0]}), //32 pixel.data (char2));always @(char_sel2[4:0] or char2)begincase (char_sel2[4:0])5'h0 : color2 = char2[31]; //将X轴对应点赋给color 5'h1 : color2 = char2[30];5'h2 : color2 = char2[29];5'h3 : color2 = char2[28];5'h4 : color2 = char2[27];5'h5 : color2 = char2[26];5'h6 : color2 = char2[25];5'h7 : color2 = char2[24];5'h8 : color2 = char2[23];5'h9 : color2 = char2[22];5'hA : color2 = char2[21];5'hB : color2 = char2[20];5'hC : color2 = char2[19];5'hD : color2 = char2[18];5'hE : color2 = char2[17];5'hF : color2 = char2[16];5'h10 : color2 = char2[15];5'h11 : color2 = char2[14];5'h12 : color2 = char2[13];5'h13 : color2 = char2[12];5'h14 : color2 = char2[11];5'h15 : color2 = char2[10];5'h16 : color2 = char2[9];5'h17 : color2 = char2[8];5'h18 : color2 = char2[7];5'h19 : color2 = char2[6];5'h1A : color2 = char2[5];5'h1B : color2 = char2[4];5'h1C : color2 = char2[3];5'h1D : color2 = char2[2];5'h1E : color2 = char2[1];5'h1F : color2 = char2[0];endcaseendendmodule。

基于Verilog的VGA显示控制电路设计

基于Verilog的VGA显示控制电路设计作者:王涌肖顺文罗春梅来源:《数字技术与应用》2019年第04期摘要:采用自上而下的设计方法实现了一个分辨率较高、显示迅速且协议简单的VGA显示控制电路。

在QUARTUS II 13.1软件开发平台上使用Verilog HDL语言来完成时序模块和彩条像素模块的描述、编译,最后在第三方仿真工具Modelsim-Altera中对其进行模拟仿真,结果显示,该设计满足系统要求,能够成功的通过VGA接口在显示器上显示图案。

关键词:Verilog HDL语言;VGA技术;QUARTUS II 13.1;Modelsim-Altera中图分类号:TN92 文献标识码:A 文章编号:1007-9416(2019)04-0150-020 引言近年来,随着数字电路设计技术的逐步发展,集成电路的发展越来越趋近于超大规模、更低功耗及超高速[1]。

Verilog HDL就是在迫切需要设计者使用EDA工具完成大规模集成电路设计发展要求的情况下应运而生的,它使用编写代码的方法来完成数字电路的设计,不管是底层的门级电路,还是高层的行为描述,都可以通过代码实现,这种方式大大的提高了数字电路的设计效率[2]。

本文就是采用Verilog_HDL语言来实现一个VGA显示控制电路。

VGA接口由于具有传输速率高,协议简单,成本低等特点,因此被广泛使用。

1 设计原理1.1 VGA时序分析VGA主要用于计算机显卡传输图像到显示器的桥梁,将显卡处理的视频图像数据实时传输到显示器上进行显示。

广义的VGA为VGA显示器,狭义的VGA为VGA分辨率的时序。

由IBM公司推出的采用RGB模拟信号的VGA视频传输标准,定义了具有60Hz刷新频率、可产生1677万种色彩的640×480像素格式。

VGA的行扫描时序情况,如图1所示。

行同步时期a、行消隐后肩b、行显示时期c、行消隐前肩d四部分组成一个完整的扫描周期。

VGA彩条信号显示控制VERILOG HDL 程序

module vga(clock50MHz,

MD,

rgb,

hs,

vs,

rst,

);

input clock50MHz;

input [1:0]MD;

output [2:0]rgb;

output hs;

output vs;

input rst;

reg hs,vs,clk;

begin

if(hcnt==h_Tg-1) hcnt<=0;

else hcnt<=hcnt+9'b1;

end

always@(posedge clk ) //clock 25MHz

begin

if(hcnt<=h_Ta-1) hs<=0; //产生场同步信号

);

initial

begin

clock50MHz<=0;

forever

#10 clock50MHz<=~clock50MHz;

else if(vcnt<=v_Ta+v_Tb+v_Tc+420-1) rgby<=3'b110;

else if(vcnt<=v_Ta+v_Tb+v_Tc+480-1) rgby<=3'b111;

else rgby<=3'b000;

if(MD==2'b00) rgb<=rgbx;//按键控制,选择条纹类型

reg[2:0] rgb,rgbx,rgby;

reg[9:0] hcnt,vcnt;

parameter h_Ta=96,h_Tb=40,h_Tc=8,h_Td=640,h_Te=8,h_Tf=8,h_Tg=800;

Verilog程序12、VGA显示字符

本地地址:E:\FPGA\vedio\vga_char\src\vga_char.v`timescale 1ns / 1ps///////////////////////////////////////////////////////////////////// /////////////// Company:// Engineer://// Create Date: 17:15:28 11/27/2010// Design Name:// Module Name: vga_char// Project Name:// Target Devices:// Tool versions:// Description:// 在液晶上显示字符// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments://///////////////////////////////////////////////////////////////////// /////////////module vga_char(clk,rst_n,vsync,hsync,r,g,b);input clk,rst_n;output vsync,hsync;output[2:0] r;output[2:0] g;output[1:0] b;reg vsync,hsync;reg[10:0] x_cnt;reg[9:0] y_cnt;///////////////////////////////////////////////////////////// ///////////////////////////////////////////////////////////////////////// 水平扫描参数的设定///////////////////////////////////////////////////////////// ///////////////////////////////////////////////////////////////parameter LinePeriod =12'd1040; //行同步周期parameter H_SyncPulse=10'd120; //?型 叫藕?parameter H_BackPorch=10'd61; //行同步后肩parameter H_ActivePix=10'd806; //行同步数据有效///////////////////////////////////////////////////////////// ///////////////////////////////////////////////////////////////////////// 垂直扫描参数的设定////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////parameter FramePeriod=10'd666;parameter V_SyncPulse=10'd6;parameter V_BackPorch=10'd21;parameter V_ActivePix=10'd604;////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////// 水平扫描计数x_cnt只负责计数从0计数计到1040////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////always @ (posedge clk or negedge rst_n)if(!rst_n) x_cnt <= 1; else if(x_cnt == LinePeriod) x_cnt <= 1;else x_cnt <= x_cnt+ 1; ////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////// 水平扫描信号vsync产生在0到120时为低电平////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////always @ (posedge clk or negedge rst_n)if(!rst_n) hsync <=1'b1;else if(x_cnt == 1) hsync <= 1'b0; //产生hsync信号else if(x_cnt ==H_SyncPulse+1) hsync <= 1'b1;////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////// 垂直扫描计数////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////always @ (posedge clk or negedge rst_n)if(!rst_n) y_cnt <= 1; else if(y_cnt == FramePeriod) y_cnt <= 1;else if(x_cnt == LinePeriod) y_cnt <= y_cnt+1;////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////// 垂直扫描信号hsync产??///////////////////////////////////////////////////////////// ///////////////////////////////////////////////////////////////always @ (posedge clk or negedge rst_n)if(!rst_n) vsync <= 1'b1;else if(y_cnt == 1) vsync <= 1'b0; //产生vsync信号else if(y_cnt ==V_SyncPulse+1) vsync <= 1'b1;wire valid; //有效显示区标志assign valid =(x_cnt >= (H_SyncPulse+H_BackPorch)) &&(x_cnt < (H_SyncPulse+H_BackPorch+H_ActivePix)) &&(y_cnt >= (V_SyncPulse+V_BackPorch)) &&(y_cnt < (V_SyncPulse+V_BackPorch+V_ActivePix));wire[9:0] x_pos=x_cnt-H_SyncPulse-H_BackPorch;wire[9:0] y_pos=y_cnt-V_SyncPulse-V_BackPorch;//字符的字模reg[7:0] vga_rgb;/* 济(0) 大(1)济{0x00,0x80}, 00800100{0x20,0x40}, 20400100{0x17,0xFE}, 17fe0100{0x12,0x08}, 12080100{0x81,0x10}, 81100100{0x40,0xA0}, 40a0fefe{0x40,0x40}, 40400100{0x11,0xB0}, 11b00100{0x16,0x0E}, 160e0280{0x21,0x10}, 21100280{0xE1,0x10}, e1100440{0x21,0x10}, 21100440{0x21,0x10}, 21108020{0x22,0x10}, 22101010{0x22,0x10}, 22102008{0x04,0x10}, 4010c006大{0x01,0x00},{0x01,0x00},{0x01,0x00},{0x01,0x00},{0x01,0x00},{0xFF,0xFE},{0x01,0x00},{0x01,0x00},{0x02,0x80},{0x02,0x80},{0x04,0x40},{0x04,0x40},{0x08,0x20},{0x10,0x10},{0x20,0x08},{0xC0,0x06},*///此时的数字取模,如是汉字要第一个汉字的第一行加上第二个汉字的第一行。

基于FPGA的游戏代码(VGA现实)

基于FPGA的游戏代码(VGA现实)//VGA显示module vga(clkin,btn_click,X,Y,red,green,blue,hsync,vsync, switch,reset,x_increment,y_increment,q,x_increment_2,y_incr ement_2,q_2,X_2,Y_2,btn_click_2,showmenu,inred,ingreen,inblue,inhsync,invsync,man1score,man2score, aiscore,music,nanyi);input clkin; //50MHzinput [2:0] btn_click; // button click: Left-Middle-Rightinput [9:0] X,Y;input [2:0] btn_click_2; // button click: Left-Middle-Rightinput [9:0] X_2,Y_2;input switch;input reset;input [8:0]x_increment;input [8:0]y_increment;input [32:0] q; //移位寄存器input [8:0]x_increment_2;input [8:0]y_increment_2;input [32:0] q_2;input showmenu;input inred;input ingreen;input inblue;input inhsync,invsync;input music,nanyi;output red,green,blue; output hsync,vsync;output [8:0]man1score; output [8:0]man2score; output [8:0]aiscore;reg red,green,blue;reg hsync,vsync;reg clk1; //25MHzreg[9:0] hcount,vcount; reg show;reg [18:0]e='d0;reg [18:0]f='d0;reg [18:0]g='d0;reg [18:0]h='d0;reg [12:0]ballx='d475; reg [12:0]bally='d275; reg [12:0]ballvx=0;reg [12:0]ballvy=0;reg [12:0]aix='d375; reg [12:0]aiy='d157; reg [12:0]aivx;reg [12:0]aivy;reg [12:0]man1x='d475; reg [12:0]man1y='d392; reg [12:0]man1vx;reg [12:0]man1vy;reg [12:0]man2x='d475;reg [12:0]man2y='d157;reg [12:0]man2vx;reg [12:0]man2vy;reg [8:0]aiscore='d0;reg [8:0]man1score='d0;reg [8:0]man2score='d0;reg visible='b1;reg restart='d0;reg [12:0]randnum;reg [12:0]temp;always@(posedge clkin) //分频beginclk1=~clk1;endparameter char_line00 = 128'h00000000000000000000000000000000,char_line01 = 128'h00000000000000000000000000000000, char_line02 = 128'h00000000000000000006000000000000, char_line03 = 128'h000E0000000018000003800000000000, char_line04 = 128'h000E000000001C000000800000001E00, char_line05 = 128'h000C000000600C0000007F80000FFF00, char_line06 = 128'h000C000007F00400007FFC0003FE0F80, char_line07 = 128'h000C00000630000003F0000001C01C00, char_line08 = 128'h000C0000062000300030780000003800,char_line09 = 128'h000C7C0006200FFC003F800000007000, char_line0a = 128'h003FFF000621FE00000000000000C000, char_line0b = 128'h0FEC0E00042780000001FC0000028000, char_line0c = 128'h060C0E0004A00200003E1C0000030000, char_line0d = 128'h060C0C0007A003000020180000018000, char_line0e = 128'h020FCC0004204320001FE00000018000, char_line0f = 128'h037F0C00042036300000008000018000, char_line10 = 128'h030C0C0004221E300001CFC000018000, char_line11 = 128'h030C180005A31C3007EE688000018000, char_line12 = 128'h030C180007A30E300648688000018000, char_line13 = 128'h010DF8000C231F300649488000018000, char_line14 = 128'h01FFB8200C2333300749488000008000, char_line15 = 128'h010C10200C23213004494E8000008000, char_line16 = 128'h000C002008234030044B4A8000018000, char_line17 = 128'h000C002008230030074A488000018000,char_line18 = 128'h000400301023FFF0044A088400018000, char_line19 = 128'h000600701067E0200844D884001F8000, char_line1a = 128'h000701F031E2002009C850C4000F8000, char_line1b = 128'h0003FFE020E0002010D0307C00038000, char_line1c = 128'h00007F004060000020A0203C00030000, char_line1d = 128'h00000000004000000000400400000000, char_line1e = 128'h00000000000000000000000000000000, char_line1f = 128'h00000000000000000000000000000000, char_line20 = 128'h00000000000000000000000000000000, char_line21 = 128'h00000000000000000000000000000000, char_line22 = 128'h00000000000E00000006000000000000, char_line23 = 128'h00000000000700000003800000000000, char_line24 = 128'h00000000000100000000800000001E00, char_line25 = 128'h00000F000000078000007F80000FFF00,char_line26 = 128'h00F07F000203FFE0007FFC0003FE0F80, char_line27 = 128'h03E0E00003FE01F003F0000001C01C00, char_line28 = 128'h1F000000060001800030780000003800, char_line29 = 128'h0100000006000000003F800000007000, char_line2a = 128'h010000000E03E000000000000000C000, char_line2b = 128'h01000FC00C7F00000001FC0000028000, char_line2c = 128'h0100FF0000060000003E1C0000030000, char_line2d = 128'h01F7D000000E08000020180000018000, char_line2e = 128'h03C1980000180C00001FE00000018000, char_line2f = 128'h1F019800007818000000008000018000, char_line30 = 128'h010********C30000001CFC000018000, char_line31 = 128'h010********E600007EE688000018000, char_line32 = 128'h010********B80000648688000018000, char_line33 = 128'h01331004006360000649488000018000, char_line34 = 128'h01C6100400C738000749488000008000, char_line35 = 128'h03861004010D9E0004494E8000008000, char_line36 = 128'h0E0C100400198F80044B4A8000018000, char_line37 = 128'h7C18180E003183F8074A488000018000, char_line38 = 128'h7030181E00C181F0044A088400018000, char_line39 = 128'h00600FFC018180000844D884001F8000, char_line3a = 128'h008007F00601800009C850C4000F8000, char_line3b = 128'h010000000001800010D0307C00038000, char_line3c = 128'h00000000001F000020A0203C00030000, char_line3d = 128'h00000000000700000000400400000000, char_line3e = 128'h00000000000600000000000000000000, char_line3f = 128'h00000000000000000000000000000000;reg[6:0] char_bit; //显示位计算 256 * 32reg[6:0] char_bit1;reg[6:0] char_bit2;reg[6:0] char_bit3;always@(posedge clk1)beginif(hcount==10'b1100011111) //799beginif(vcount==10'b1000001100)//524beginvcount<=10'b0;hcount<=10'b0;endelse beginhcount<=10'b0;vcount=vcount+1;endendelse hcount=hcount+1;endalways@(posedge clk1)beginshow=showmenu;if(show==0)beginif((hcount>10'b0000000111)&&(hcount<10'b0001101000)) //行同步宽度96个像素hsync<=1'b0;else hsync<=1'b1;endelse if(show==1) hsync<=inhsync;endalways@ (posedge clk1)beginif(show==0)beginif((vcount>10'b0000000001)&&(vcount<10'b0000000100))/ /场同步宽度2个行vsync<=1'b0;else vsync<=1'b1;endelse if(show==1) vsync<=invsync;end///////////////////////////////////////////////mainCode////////////////////////////////////////////////////////always @(posedge clkin) ////////ball's movementbegine=e+1;if (reset==1'b1)begin /////////reset!aiscore=0;man1score=0;man2score=0;visible=1;ballvx=0;ballvy=0;ballx=10'd475;bally=10'd275;endif(restart==1) begin /////////restart!visible=1;//yanshi3secondsballvx=0;ballvy=0;ballx=10'd475;bally=10'd275;restart=0;endif(e==500000)beginballx=ballx+ballvx;bally=bally+ballvy;e=0;if(ballx>=770)begin ballx=770;ballvx=-ballvx;end if(ballx<=180)begin ballx=180;ballvx=-ballvx;end if(bally>=500)begin bally=500;ballvy=-(ballvy);end if(bally<=50) begin bally=50;ballvy=-1*(ballvy);endif(ballx>375&&ballx<=575&&bally>=50&&bally<=58)beginvisible=0;ballvx=0;ballvy=0;man1score<=man1score+1;restart=1;endif(ballx>=375&&ballx<=575&&bally<=500&&bally>=492) beginvisible=0;ballvx=0;ballvy=0;if(switch==0) beginaiscore<=aiscore+1;restart=1;endelse man2score<=man2score+1;restart=1;end//if(man1score==7)beginyouwin=1;man1score=0;man2score=0;aiscore=0;end //if(aiscore==7||man2score==7)beginyoulose=1;man1score=0;man2score=0;aiscore=0;end if(switch==0) //man VS computerbeginif((ballx-aix)*(ballx-aix)+(bally-aiy)*(bally-aiy)<='d1225) beginballvx=ballvx;ballvy=-ballvy;ballx=ballx+(ballx>aix?4:(-4));bally=bally+(bally>aiy?4:(-4));endendelse //man1 vs man2begin//if((ballx-man2x)*(ballx-man2x)+(bally-man2y)*(bally-bally)<='d1255)if((ballx-X_2)*(ballx-X_2)+(bally-Y_2)*(bally-Y_2)<='d1225)begin//ballvx=aivx-ballvx;//ballvy=aivy-ballvy;ballvx=x_increment_2+(ballvx>0?ballvx:(-ballvx))*(ballx>X?1:(-1));ballvy=y_increment_2+(ballvy>0?ballvy:(-ballvy))*(bally>Y?1:(-1));ballx=ballx+(ballx>man2x?4:(-4));bally=bally+(bally>man2y?4:(-4));endendif(show==0)begin/////////////////////////////////////if((ballx-X)*(ballx-X)+(bally-Y)*(bally-Y)<='d1225)beginif(x_increment*x_increment+y_increment*y_increment>4)be gin endif((Y-bally)>'d30)//1/*beginif(ballvx==0&&ballvy==0)beginif(q[5]==0)ballvx=x_increment;elseballvx=-x_increment;ifballvy=y_increment;endelse*/ beginif(q[5]==0) ballvx=x_increment/'d8+(ballvx>0?ballvx:(-ballvx))*(ballx>X?1:(-1));//mouse rightelse ballvx=-x_increment/'d8+ (ballvx>0?ballvx:(-ballvx))*(ballx>X?1:(-1));if(q[6]==0) ballvy=-y_increment/'d8+(ballvy>0?ballvy:(-ballvy))*(bally>Y?1:(-1));//mouse upelse ballvy=y_increment/'d8+(ballvy>0?ballvy:(-ballvy))*(bally>Y?1:(-1));end// endif((bally-Y)>'d30)//2beginif(ballvx==0&&ballvy==0)beginballvx=x_increment;ballvy=y_increment;endelse beginif(q[5]==0) ballvx=x_increment/'d8+(ballvx>0?ballvx:(-ballvx))*(ballx>X?1:(-1));//mouse rightelse ballvx=-x_increment/'d8+(ballvx>0?ballvx:(-ballvx))*(ballx>X?1:(-1));if(q[6]==0) ballvy=-y_increment/'d8+(ballvy>0?ballvy:(-ballvy))*(bally>Y?1:(-1));//mouse upelse ballvy=y_increment/'d8+(ballvy>0?ballvy:(-ballvy))*(bally>Y?1:(-1));endendif(bally>=(Y-'d30)&&bally<y&&ballx bdsfid="384">X)//3 begintemp=(ballvx>0?ballvx:(-ballvx))*(ballx>X?1:(-1));ballvx=(ballvy>0?ballvy:(-ballvy))*(bally>Y?1:(-1));ballvy=temp;endif(bally<(Y+'d30)&&bally>=Y&&ballx>X)//4begintemp=(ballvx>0?ballvx:(-ballvx))*(ballx>X?1:(-1));ballvx=(ballvy>0?ballvy:(-ballvy))*(bally>Y?1:(-1));ballvy=-temp;endif(bally>=(Y-'d30)&&bally<y&&ballxbegintemp=(ballvx>0?ballvx:(-ballvx))*(ballx>X?1:(-1));ballvx=-(ballvy>0?ballvy:(-ballvy))*(bally>Y?1:(-1));ballvy=-temp;if(bally>(Y+'d30)&&bally>=Y&&ballxbegintemp=(ballvx>0?ballvx:(-ballvx))*(ballx>X?1:(-1));ballvx=(ballvy>0?ballvy:(-ballvy))*(bally>Y?1:(-1));ballvy=temp;endballx=ballx+(ballx>man1x?4:(-4));bally=bally+(bally>man1y?4:(-4));if(ballvx*ballvx+ballvy*ballvy>=2)beginballvx=ballvx;ballvy=ballvy;endendend//////////////////////endendalways@(posedge clkin) ////////ai's movementif(switch==0&&show==0)beginif(reset==1||restart==1)begin aix='d475;aiy='d157;endg=g+1;if(g==500000)g=0;aix=aix+aivx;aiy=aiy+aivy;if(aix<190)aix=190;if(aix>760)aix=760;if(a</y&&ballx</y&&ballx> iy<60) aiy=60;if(aiy>255) aiy=255;if(aixbeginif(ballvx>0)aivx=1*ballvx; if(ballvx<0)aivx=-1*ballvx; if(ballvx==0)aivx=1;endif(aix>ballx)beginif(ballvx>0)aivx=-1*ballvx; if(ballvx<0)aivx=1*ballvx; if(ballvx==0)aivx=-1; endendend////////////////////////////////////////////////Main VGA Code////////////////////////////////////////////////////////////always@(posedge clk1)beginif(show==1)begin{red,green,blue}<={inred,ingreen,inblue};end/////////////////////////////////////////////////////////////////// if(man1score==7)beginif(hcount == 10'd420) char_bit2 <= 7'd128; //先显示最高位数据 128 wei 572是X轴的起始坐标else if(hcount > 10'd420 && hcount < 10'd548) char_bit2 <= char_bit2-1'b1; //依次显示后面的数据if(hcount > 10'd420 && hcount < 10'd548) begin //////////kai shi you xicase(vcount)10'd321: if(char_line20[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd322: if(char_line21[char_bit2]){red,green,blue}<=3'b110; //红色else {red,green,blue}<=3'b010; //绿色10'd323: if(char_line22[char_bit2]) {red,green,blue}<= 3'b110; //红色10'd324: if(char_line23[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd325: if(char_line24[char_bit2]) {red,green,blue}<= 3'b110; //红seelse {red,green,blue}<= 3'b010; //绿色10'd326: if(char_line25[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd327: if(char_line26[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue} <= 3'b010; //绿色10'd328: if(char_line27[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd329: if(char_line28[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd330: if(char_line29[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd331: if(char_line2a[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd332: if(char_line2b[char_bit2]) {red,green,blue}<=3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd333: if(char_line2c[char_bit2]) {red,green,blue}<= 3'b110; //红色10'd334: if(char_line2d[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd335: if(char_line2e[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd336: if(char_line2f[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色/////-------------------------------------------------------------------10'd337: if(char_line30[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd338: if(char_line31[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd339: if(char_line32[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd340: if(char_line33[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd341: if(char_line34[char_bit2]) {red,green,blue}<= 3'b110; //红seelse {red,green,blue}<= 3'b010;//绿色//红色else {red,green,blue}<= 3'b010; //绿色10'd343: if(char_line36[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd344: if(char_line37[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd345: if(char_line38[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd346: if(char_line39[char_bit2]) {red,green,blue}<= 3'b110; //红色else{red,green,blue}<= 3'b010; //绿色10'd347: if(char_line3a[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd348: if(char_line3b[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd349: if(char_line3c[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd350: if(char_line3d[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd351: if(char_line3e[char_bit2]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色//红色else {red,green,blue}<= 3'b010; //绿色endcaseendendif(man2score==7)beginif(hcount == 10'd420) char_bit1 <= 7'd128; //先显示最高位数据 128 wei 572是X轴的起始坐标else if(hcount > 10'd420 && hcount < 10'd548) char_bit1 <= char_bit1-1'b1; //依次显示后面的数据if(hcount > 10'd420 && hcount < 10'd548) begin //////////kai shi you xicase(vcount)10'd201: if(char_line20[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd202: if(char_line21[char_bit1]){red,green,blue}<=3'b110; //红色else {red,green,blue}<=3'b010; //绿色10'd203: if(char_line22[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd204: if(char_line23[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd205: if(char_line24[char_bit1]) {red,green,blue}<= 3'b110; //红seelse {red,green,blue}<= 3'b010; //绿色10'd206: if(char_line25[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd207: if(char_line26[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue} <= 3'b010; //绿色10'd208: if(char_line27[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd209: if(char_line28[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd210: if(char_line29[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd211: if(char_line2a[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd212: if(char_line2b[char_bit1]) {red,green,blue}<=3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd213: if(char_line2c[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd214: if(char_line2d[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd215: if(char_line2e[char_bit1]) {red,green,blue}<= 3'b110;//红色else {red,green,blue}<= 3'b010; //绿色10'd216: if(char_line2f[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色/////-------------------------------------------------------------------10'd217: if(char_line30[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd218: if(char_line31[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd219: if(char_line32[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd220: if(char_line33[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd221: if(char_line34[char_bit1]) {red,green,blue}<= 3'b110; //红seelse {red,green,blue}<= 3'b010;//绿色10'd222: if(char_line35[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd223: if(char_line36[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd224: if(char_line37[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd225: if(char_line38[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd226: if(char_line39[char_bit1]) {red,green,blue}<= 3'b110; //红色else{red,green,blue}<= 3'b010; //绿色10'd227: if(char_line3a[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd228: if(char_line3b[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd229: if(char_line3c[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd230: if(char_line3d[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd231: if(char_line3e[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd232: if(char_line3f[char_bit1]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色endcaseendendif(aiscore==7)beginif(hcount == 10'd420) char_bit <= 7'd128;else if(hcount > 10'd420 && hcount < 10'd548) char_bit <= char_bit-1'b1;if(hcount > 10'd420 && hcount < 10'd548) begincase(vcount)10'd201: if(char_line00[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd202: if(char_line01[char_bit]){red,green,blue}<=3'b110; //红色else {red,green,blue}<=3'b010; //绿色10'd203: if(char_line02[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd204: if(char_line03[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd205: if(char_line04[char_bit]) {red,green,blue}<= 3'b110; //红seelse {red,green,blue}<= 3'b010; //绿色10'd206: if(char_line05[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd207: if(char_line06[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue} <= 3'b010; //绿色10'd208: if(char_line07[char_bit]) {red,green,blue}<= 3'b110;//红色else {red,green,blue}<= 3'b010; //绿色10'd209: if(char_line08[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd210: if(char_line09[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd211: if(char_line0a[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd212: if(char_line0b[char_bit]) {red,green,blue}<=3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd213: if(char_line0c[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd214: if(char_line0d[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd215: if(char_line0e[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd216: if(char_line0f[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色/////-------------------------------------------------------------------10'd217: if(char_line10[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd218: if(char_line11[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd219: if(char_line12[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd220: if(char_line13[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd221: if(char_line14[char_bit]) {red,green,blue}<= 3'b110; //红seelse {red,green,blue}<= 3'b010;//绿色10'd222: if(char_line15[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd223: if(char_line16[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd224: if(char_line17[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd225: if(char_line18[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd226: if(char_line19[char_bit]) {red,green,blue}<= 3'b110; //红色else{red,green,blue}<= 3'b010; //绿色10'd227: if(char_line1a[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd228: if(char_line1b[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd229: if(char_line1c[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd230: if(char_line1d[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd231: if(char_line1e[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色10'd232: if(char_line1f[char_bit]) {red,green,blue}<= 3'b110; //红色else {red,green,blue}<= 3'b010; //绿色endcaseendend////////////////////////////////////////////////////////////////// if(show==0&&man1score!=7&&man2score!=7&&aiscore! =7)beginif(((hcount-X)*(hcount-X)+(vcount-Y)*(vcount-Y))<='b110111111)begin{red,green,blue}<=btn_click + 1'b1;end ///////////man1else {red,green,blue}<=3'b000;if((hcount>=375)&&(hcount<=575)&&(((vcount>=40)&&( vcount<=50))||((vcount>=500)&&(vcount<=510)))) begin{red,green,blue}<=3'b001; ////////two gatesendif(hcount>=170&&hcount<=780&&((vcount>=40&&vcou nt<=42)||(vcount>=508&&vcount<=510)||vcount==275)) begin{red,green,blue}<=3'b011; ///////heng bian kuangendif(vcount>=40&&vcount<=510&&((hcount>=170&&hcou nt<=172)||(hcount>=778&&hcount<=780)))begin{red,green,blue}<=3'b011; ///////shu bian kuangendif(((hcount-475)*(hcount-475)+(vcount-275)*(vcount-275))<='b111110111111&&((hcount-475)*(hcount-475 )+(vcount-275)*(vcount-275))>='b111110000000)begin{red,green,blue}<=3'b011; ///////zhong xin yuanendif((((hcount-ballx)*(hcount-ballx)+(vcount-bally)*(vcount-bally))<='b10111111)&&(visible==1))begin{red,green,blue}<=3'b100; //////// ballendif(switch==0)beginif((hcount-aix)*(hcount-aix)+(vcount-aiy)*(vcount-aiy)<='b110111111)begin{red,green,blue}<=3'b001; ////////aiendendif(switch==1)beginif((hcount-X_2)*(hcount-X_2)+(vcount-Y_2)*(vcount-Y_2)<='b110111111)begin{red,green,blue}<=btn_click_2 + 1'b1; //////// man2 endendendendendmodule。

用verilog编写fpga的vga显示

用verilog编写fpga的vga显示(z)VGA工业标准是640x480x60Hz,主要有5个信号,即三个颜色信号R/G/B、行同步信号HS和场同步信号VS。

它是从左上角开始一行接一行的扫描,扫描完一屏后又回到左上角扫描。

标准要求是场频59.94Hz,行频31469Hz,时钟频率25.175MHz这是Altera的DE2开发板上自带的演示程序。

可以先搜一下VGA工业标准的时序图,再看这个代码就会很简单,就不注释了。

弄清楚行同步、场同步、前肩、后肩,一切都easymodule VGA_Controller( // Host SideiRed,iGreen,iBlue,oRequest,// VGA SideoVGA_R,oVGA_G,oVGA_B,oVGA_H_SYNC,oVGA_V_SYNC,oVGA_SYNC,oVGA_BLANK,oVGA_CLOCK,// Control SignaliCLK,iRST_N );`include "VGA_Param.h"// Host Sideinput [9:0] iRed;input [9:0] iGreen;input [9:0] iBlue;output reg oRequest;// VGA Sideoutput [9:0] oVGA_R;output [9:0] oVGA_G;output [9:0] oVGA_B;output reg oVGA_H_SYNC;output reg oVGA_V_SYNC;output oVGA_SYNC;output oVGA_BLANK;output oVGA_CLOCK;// Control Signalinput iCLK;input iRST_N;// Internal Registers and Wiresreg [9:0] H_Cont;reg [9:0] V_Cont;reg [9:0] Cur_Color_R;reg [9:0] Cur_Color_G;reg [9:0] Cur_Color_B;wire mCursor_EN;wire mRed_EN;wire mGreen_EN;wire mBlue_EN;assign oVGA_BLANK = oVGA_H_SYNC & oVGA_V_SYNC;assign oVGA_SYNC = 1'b0;assign oVGA_CLOCK = iCLK;assign oVGA_R = ( H_Cont>=X_START && H_Cont<X_START+H_SYNC_ACT && V_Cont>=Y_START && V_Cont<Y_START+V_SYNC_ACT )? iRed : 0;assign oVGA_G = ( H_Cont>=X_START && H_Cont<X_START+H_SYNC_ACT && V_Cont>=Y_START && V_Cont<Y_START+V_SYNC_ACT )? iGreen : 0;assign oVGA_B = ( H_Cont>=X_START && H_Cont<X_START+H_SYNC_ACT && V_Cont>=Y_START && V_Cont<Y_START+V_SYNC_ACT )? iBlue : 0;// Pixel LUT Address Generatoralways@(posedge iCLK or negedge iRST_N)beginif(!iRST_N)oRequest <= 0;elsebeginif( H_Cont>=X_START-2 && H_Cont<X_START+H_SYNC_ACT-2 &&V_Cont>=Y_START && V_Cont<Y_START+V_SYNC_ACT )oRequest <= 1;elseoRequest <= 0;endend// H_Sync Generator, Ref. 25.175 MHz Clockalways@(posedge iCLK or negedge iRST_N)if(!iRST_N)beginH_Cont <= 0;oVGA_H_SYNC <= 0;endelsebegin// H_Sync Counterif( H_Cont < H_SYNC_TOTAL )H_Cont <= H_Cont+1;elseH_Cont <= 0;// H_Sync Generatorif( H_Cont < H_SYNC_CYC )oVGA_H_SYNC <= 0;elseoVGA_H_SYNC <= 1;endend// V_Sync Generator, Ref. H_Sync always@(posedge iCLK or negedge iRST_N) beginif(!iRST_N)beginV_Cont <= 0;oVGA_V_SYNC <= 0;endelsebegin// When H_Sync Re-startif(H_Cont==0)begin// V_Sync Counterif( V_Cont < V_SYNC_TOTAL )V_Cont <= V_Cont+1;elseV_Cont <= 0;// V_Sync Generatorif( V_Cont < V_SYNC_CYC )oVGA_V_SYNC <= 0;elseoVGA_V_SYNC <= 1;endend endmodule显示器因为其输出信息量大,输出形式多样等特点已经成为现在大多数设计的常用输出设备。

VGA显示的FPGA实现方法

示器上显示一个有颜色的区域了,在这个小 节中我们再举一个简单的例子,在显示器中 显示两个镶嵌的正方形,字符等显示与其类 似,可以参考瑞芯科技其他设计示例。

例如我们可以在 xpos 与 ypos 的某一区 间给 RGB 信号赋不同的值将得到如图 2 所 示的显示效果。

而隔行扫描指电子束在扫描时每隔一 行扫一线,完成一屏后再返回来扫描剩下的 线,这与电视机的原理一样。隔行扫描的显 示器比逐行扫描闪烁得更厉害,也会让使用 者的眼睛更疲劳。目前微机所用显示器几乎 都是逐行扫描。

完成一行扫描所需时间称为水平扫描 时间,其倒数称为行频率;完成一帧(整屏) 扫描所需的时间称为垂直扫描时间,其倒数 为垂直扫描频率,又称刷新频率,即刷新一 屏的频率。常见的有 60Hz、75Hz 等,标准 VGA 显示的场频 60Hz,行频为 31.5kHz。

而与我们电脑相关的地方,就是目前的 显示器大都是采用了 RGB 颜色标准,这就 是为什么它对我们来说这么重要了。

在显示器上,是通过电子枪打在屏幕的 红、绿、蓝三色发光极上来产生色彩的,目 前的电脑一般都能显示 32 位颜色,约有一 百万种以上的颜色。如果说它所显示的颜色 还不能完全吻合自然界中的某种色彩的话, 那已经几乎是我们肉眼所不能分辩出来的 了。

显示器尺寸 显示器屏幕尺寸以对角线来度量,常用

的显示器有 14、15、17、19、21 英寸等。 显示器水平方向长度与垂直方向高度之比 一般为 4:3。

扫描频率 显示器采用光栅扫描方式,即轰击荧光

屏的电子束在 CRT 屏幕上从左到右(受水 平同步信号 HSYNC 控制)、从上到下(受 垂直同步信号 VSYNC 控制)做有规律的移 动。光栅扫描又分逐行扫描和隔行扫描。电 子束采用光栅扫描方式,从屏幕左上角一点 开始,向右逐点进行扫描,形成一条水平线; 到达最右端后,又回到下一条水平线的左 端,重复上面的过程;当电子束完成右下角 一点的扫描后,形成一帧。此后,电子束又 回到左上方起点,开始下一帧的扫描。这种 方法也就是常说的逐行扫描显示。

X431Verilog参考例程-VGA字符显示实验

1VGA 字符显示实验1、 字符取模要显示字符,首先需要获得字模数据,我们使用字模软件PCtoLCD2002(配套光盘里有,网络上也随处可下)。

该字模软件用1bit 代表一个像素点的色彩,用户可以根据需要来决定这1bit 数据(0或1)代表的色彩。

下面说明我们的设计中需要的字符是如何取模的,启动取模软件PCtoLCD2002,点击菜单栏的“模式”,选择“字符模式”。

点击菜单栏的“选项”,在弹出的对话框中设置如图1所示。

图1 字模选项配置完成点击“确定”(这里的设置主要是针对取模的方向、输出数据的格式等,很多朋友都用过,第一次使用的朋友自己多琢磨下也就明白了)。

在输入文字处输入“EDN ”,点击“生成字模”,输出字模数据如下:E(0) D(1) N(2){0x00,0x00},{0x00,0xFC},{0x42,0x48},{0x48,0x78},{0x48,0x48},{0x40,0x42},{0x42,0xFC},{0x00,0x00},/*"E",0*/{0x00,0x00},{0x00,0xF8},{0x44,0x42},{0x42,0x42},{0x42,0x42},{0x42,0x42},{0x44,0xF8},{0x00,0x00},/*"D",1*/{0x00,0x00},{0x00,0xC7},{0x62,0x62},{0x52,0x52},{0x4A,0x4A},{0x4A,0x46},{0x46,0xE2},{0x00,0x00},/*"N",2*/2、定义参数将以上字模数据定义成verilog里的参数,用于VGA的显示。

我们要显示的字符“EDN”,对应每个字符都是8*16个像素,正好是16字节的数据。

而每一个字节代表一个行即8个像素(1个字节)的数据。

EDN三个字符又是紧紧挨着的,所以我们这里将每一行的3个字节数据拼起来,便于显示时根据坐标取数据(当然使用取模软件你可以直接这么干,也免得现在需要手动拼数据)。

VGA显示的FPGA实现2

课程设计报告课程名称数字系统设计自动化院部名称电子信息工程学院(筹)专业电子信息工程班级学生姓名学号课程设计地点课程设计学时指导教师金陵科技学院教务处制课程设计报告书写要求课程设计报告原则上要求学生手写,要求书写工整。

若因课程特点需打印的,要遵照以下字体、字号、间距等的具体要求。

纸张一律采用A4的纸张。

课程设计报告书写说明课程设计报告应包含以下七部分内容:1、摘要2、目录3、前言/引言 4.正文 5. 结论 6. 参考文献7. 附录,每部分的书写要求参见具体条目要求。

填写注意事项(1)准确说明,层次清晰。

(2)尽量采用专用术语来说明事物。

(3)外文、符号、公式要准确,应使用统一规定的名词和符号。

(4)应独立完成课程设计报告的书写,严禁抄袭、复印,一经发现,以零分论处。

课程设计报告批改说明课程设计报告的批改要及时、认真、仔细,一律用红色笔批改。

课程设计报告的批改成绩采用五级计分制或百分制,具体评分标准由各院部自行制定。

课程设计报告装订要求报告批改完毕后,任课老师应将课程设计报告以自然班为单位、按学号升序排列,并附上一份该课程设计的教学大纲。

课程设计题目:通过fpga驱动vga输出,实现简单的vga显示一、摘要(所进行设计工作的主旨、缘起、目的,设计工作的主要内容、过程,采用的方法及取得的成果。

关键字(Key Words): 一般3~5个,最能代表报告内容特征,或在报告起关键作用,最能说明问题的词组)本文介绍了一种利用可编程逻辑器件实现VGA图像显示控制的方法,阐述了VGA图像显示控制器中VGA显像的基本原理以及功能演示,利用可编程器件FPGA设计VGA图像显示控制的Verilog设计方案,并在Xilink公司的Xilinx ISE软件环境下完成VGA模块的设计。

而且给出了VGA模块的设计思路和顶层逻辑框图。

最终实现VGA图像显示控制器,VGA图像控制器是一个较大的数字系统,传统的图像显示的方法是在图像数据传输到计算机,并通过显示屏显示出在传输过程中,将图像数据的CPU需要不断的信号控制,所以造成CPU的资源浪费,系统还需要依靠计算机,从而减少了系统的灵活性。

verilog显示VGA矩形框

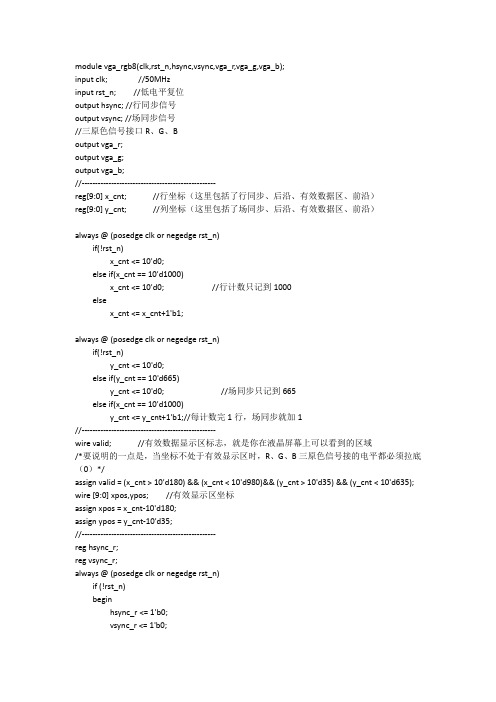

module vga_rgb8(clk,rst_n,hsync,vsync,vga_r,vga_g,vga_b);input clk; //50MHzinput rst_n; //低电平复位output hsync; //行同步信号output vsync; //场同步信号//三原色信号接口R、G、Boutput vga_r;output vga_g;output vga_b;//--------------------------------------------------reg[9:0] x_cnt; //行坐标(这里包括了行同步、后沿、有效数据区、前沿)reg[9:0] y_cnt; //列坐标(这里包括了场同步、后沿、有效数据区、前沿)always @ (posedge clk or negedge rst_n)if(!rst_n)x_cnt <= 10'd0;else if(x_cnt == 10'd1000)x_cnt <= 10'd0; //行计数只记到1000elsex_cnt <= x_cnt+1'b1;always @ (posedge clk or negedge rst_n)if(!rst_n)y_cnt <= 10'd0;else if(y_cnt == 10'd665)y_cnt <= 10'd0; //场同步只记到665else if(x_cnt == 10'd1000)y_cnt <= y_cnt+1'b1;//每计数完1行,场同步就加1//--------------------------------------------------wire valid; //有效数据显示区标志,就是你在液晶屏幕上可以看到的区域/*要说明的一点是,当坐标不处于有效显示区时,R、G、B三原色信号接的电平都必须拉底(0)*/assign valid = (x_cnt > 10'd180) && (x_cnt < 10'd980)&& (y_cnt > 10'd35) && (y_cnt < 10'd635); wire [9:0] xpos,ypos; //有效显示区坐标assign xpos = x_cnt-10'd180;assign ypos = y_cnt-10'd35;//--------------------------------------------------reg hsync_r;reg vsync_r;always @ (posedge clk or negedge rst_n)if (!rst_n)beginhsync_r <= 1'b0;vsync_r <= 1'b0;endelse beginhsync_r <= x_cnt <= 10'd50; //产生hsync信号(行同步)vsync_r <= y_cnt <= 10'd6; //产生vsync信号(场同步)endassign hsync = hsync_r;assign vsync = vsync_r;//--------------------------------------------------//显示一个矩形框wire a_dis,b_dis,c_dis,d_dis; //矩形框显示区域定位assign a_dis = ( (xpos>=200) && (xpos<=220) )&& ( (ypos>=140) && (ypos<=460) ); assign b_dis = ( (xpos>=580) && (xpos<=600) )&& ( (ypos>=140) && (ypos<=460) ); assign c_dis = ( (xpos>=220) && (xpos<=580) )&& ( (ypos>140) && (ypos<=160) ); assign d_dis = ( (xpos>=220) && (xpos<=580) )&& ( (ypos>=440) && (ypos<=460) ); //显示一个小矩形wire e_rdy; //矩形的显示有效矩形区域assign e_rdy = ( (xpos>=385) && (xpos<=415) )&& ( (ypos>=285) && (ypos<=315) ); //--------------------------------------------------//r,g,b控制液晶屏颜色显示,背景显示蓝色,矩形框显示红蓝色assign vga_r = valid ? e_rdy : 1'b0;assign vga_g = valid ? (a_dis | b_dis | c_dis | d_dis) : 1'b0;assign vga_b = valid ? ~(a_dis | b_dis | c_dis | d_dis) : 1'b0;endmodule。

fpga驱动vga接口的vhdl语言实现

fpga驱动vga接口的vhdl语言实现[转载]来自于《基于FPGA的嵌入式系统设计》我使用ep2c5的实验板作过了实验,没有问题的,可惜只能显示彩条,方格。

McMaster University有一篇介绍vga接口协议的vhdl实现介绍,可以自己下载参考。

library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity vgacore isPort ( clk : in std_logic;reset : in std_logic;md : in std_logic_vector(1 downto 0);hs : out std_logic;vs : out std_logic;r : out std_logic_vector(1 downto 0);g : out std_logic_vector(2 downto 0);b : out std_logic_vector(2 downto 0));end vgacore;architecture Behavioral of vgacore issignal sysclk : std_logic;signal hsyncb : std_logic;signal vsyncb : std_logic;signal enable : std_logic;signal hloc : std_logic_vector(9 downto 0);signal vloc : std_logic_vector(9 downto 0);signal rgbx,rgby,rgbp,rgb: std_logic_vector(7 downto 0);--定义VGASIG元件,产生同步信号进行行、场扫描,即显示驱动component vgasigPort (clock : in std_logic;reset : in std_logic;hsyncb : buffer std_logic;vsyncb : out std_logic;enable : out std_logic;Xaddr : out std_logic_vector(9 downto 0);Yaddr : out std_logic_vector(9 downto 0));end component;--定义colormap元件,确定颜色及位置信息component colormapPort (hloc : in std_logic_vector(9 downto 0);vloc : in std_logic_vector(9 downto 0);rgbx : out std_logic_vector(7 downto 0);rgby : out std_logic_vector(7 downto 0));end component;beginrgb(7) <= rgbp(7) and enable;rgb(6) <= rgbp(6) and enable;rgb(5) <= rgbp(5) and enable;rgb(4) <= rgbp(4) and enable;rgb(3) <= rgbp(3) and enable;rgb(2) <= rgbp(2) and enable;rgb(1) <= rgbp(1) and enable;rgb(0) <= rgbp(0) and enable;--产生25Mhz的像素输出频率divclk: process(clk,reset)beginif reset='0' thensysclk <= '0';elsif clk'event and clk='1' thensysclk <= not sysclk;end if;end process;--模式选择单元:本测试程序我们使用了4种模式,由KEY_B2,KEY_B3控制,当选择模式"11"时,即不按下B2,B3,VGA显示竖彩条;当选择模式"00"时,即同时按下B2,B3时,VGA显示全黑;当选择模式"01"时,即只按下B2时,VGA显示横彩条;当选择模式"10"时,即只按下B3时,VGA时显示横竖彩条。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

else if(ij==2'b10)

begin

xpos<=xpos-1;

ypos<=ypos+1;

if(ypos+WIDTH==480)

ij<=2'b11;

else if(xpos==1)

ij<=2''b11)

parameter LENGTH=128,WIDTH=128;

parameter V_TA=2;

parameter V_TB=25;

parameter V_TC=8;

parameter V_TD=480;

parameter V_TE=8;

parameter V_TF=2;

parameter V_BLANK=V_TA+V_TB+V_TC;

wire[4:0] iblue=q[4:0];

always @(posedge iclk_50)

begin iclk<=~iclk;end

assign ovga_blank=~((h_cont<H_BLANK)||(v_cont<V_BLANK));

assign ovga_clock=~iclk;

(* chip_pin="H21,D22,E22,E23,D23" *)output [4:0] ovga_r0;

(* chip_pin="C18,B17,A17,C16,B16" *)output [4:0] ovga_b0;

(* chip_pin="C12,A11,B11,A10" *)output [3:0] ovga_g0;

assign ovga_r0=5'h0;

assign ovga_g0=4'h0;

assign ovga_b0=5'h0;

always @(posedge iclk or posedge irst)

begin

if(irst)

begin

h_cont<=0;

ovga_hs<=1;

endmodule

begin

xpos<=xpos-1;

ypos<=ypos-1;

if(ypos==1)

ij<=2'b10;

else if(xpos==1)

ij<=2'b01;

end

end

vga_rom u1(.address(address),.clock(iclk),.q(q),);

ij<=2'b10;

end

else if(ij==2'b01)

begin

xpos<=xpos+1;

ypos<=ypos-1;

if(ypos==1)

ij<=2'b00;

else if(xpos+LENGTH==640)

ij<=2'b11;

begin

if((h_cont<(xpos+H_TA+H_TB+H_TC+LENGTH))&&(h_cont>=(xpos+H_TA+H_TB+H_TC))&&(v_cont<(ypos+V_TA+V_TB+V_TC+WIDTH))&&(v_cont>=(ypos+V_TA+V_TB+V_TC)))

else

v_cont<=0;

if(v_cont<=V_TA-1)

ovga_vs<=1'b0;

else

ovga_vs<=1'b1;

end

end

always @(posedge iclk)

begin

if(irst)

address<=15'h0;

else

end

end

always @(posedge ovga_hs or posedge irst)

begin

if(irst)

begin

v_cont<=0;

ovga_vs<=1;

end

else

begin

if(v_cont<V_TOTAL)

v_cont<=v_cont+1;

(* chip_pin="G20,E20,F20,H20,G21" *)output reg[4:0] ovga_r;

(* chip_pin="D19,C19,A19,B19,B18" *)output reg[4:0] ovga_b;

(* chip_pin="A14,B14,B13,C13,A12,B12" *)output reg[5:0] ovga_g;

(* chip_pin="C15" *)output ovga_blank;

(* chip_pin="B15" *)output ovga_sync;

(* chip_pin="J19" *)output reg ovga_hs;

(* chip_pin="H19" *)output reg ovga_vs;

parameter H_TC=8;

parameter H_TD=640;

parameter H_TE=8;

parameter H_TF=8;

parameter H_BLANK=H_TA+H_TB+H_TC;

parameter H_TOTAL=H_TA+H_TB+H_TC+H_TD+H_TE+H_TF;

begin

address<=address+1;

ovga_r<=ired;

ovga_g<=igreen;

ovga_b<=iblue;

end

else

begin

ovga_r<=5'h0;

ovga_g<=6'h0;

ovga_b<=5'h0;

end

end

end

reg iclk;wire vga_read;

reg[14:0] address;wire[15:0] q;

reg[10:0] h_cont,v_cont;

reg[9:0] xpos,ypos;

reg[1:0] ij;

wire[4:0] ired=q[15:11];

wire[5:0] igreen=q[10:5];

end

else

begin

if(h_cont<H_TOTAL)

h_cont<=h_cont+1'b1;

else

h_cont<=1'b0;

if(h_cont<H_TA-1)

ovga_hs=1'b0;

else

ovga_hs=1'b1;

module vga_lena(iclk_50,irst,ovga_clock,ovga_hs,ovga_vs,ovga_blank,ovga_sync,ovga_r,ovga_g,ovga_b,ovga_r0,ovga_g0,ovga_b0);

parameter H_TA=96;

parameter H_TB=40;

always @(negedge ovga_vs)

begin

if(ij==2'b00)

begin

xpos<=xpos+1;

ypos<=ypos+1;

if(ypos+WIDTH==480)

ij<=2'b01;

else if(xpos+LENGTH==640)

parameter V_TOTAL=V_TA+V_TB+V_TC+V_TD+V_TE+V_TF;

(* chip_pin="AD15" *)input iclk_50;

(* chip_pin="AA23" *)input irst;

(* chip_pin="D24" *)output ovga_clock;