基于FPGA的VGA图像显示与控制

华科基于FPGA的VGA显示实验

电子线路测试与实验报告基于FPGA的VGA显示实验姓名:专业班级:光电1208学号:U2012一、实验要求功能要求:利用Basys2实验板实现图片在VGA接口显示器上的显示。

基本要求:1)实现240*160以上像素的图片在VGA接口显示器上的显示;2)利用算法实现特定图片在VGA接口显示器上的放大、缩小旋转及其他动作的自动变换。

二、实验具体目标1.首先实现特定图片在显示器上的显示;2.图片自动旋转90度;3.实现图片的放大与缩小,同样通过一个按键实现;4.添加复位键,按下复位键后图片返回最初的状态。

三、实验原理1.VGA的显示原理在基于FPGA的VGA控制中,只需考虑行同步信号(HS),场同步信号(VS),以及红绿蓝三基色(R、G、B)这五个信号,即可实现对VGA显示的控制。

2.对图片的旋转与缩放操作对图片的旋转操作在本质上是对IP核ROM的输入地址addr进行变换的过程。

在这里,假定显示的坐标分别为x_vdn以及y_vdn,由于图片是160*40的,在正常的显示时,addr 与x_vdn以及y_vdn的对应关系应该为:addr=x_vdn+y_vdn*160即依次取像素点,图片正常显示。

要把图片顺时针旋转90度,那么相当于显示的图片是40*160的,重新考虑addr与两个坐标之间映射关系。

容易得到,此时:addr=(39-x_vdn)*160+y_vd对图片的缩放操作对图片的缩放操作则只考虑以下两种变化,即放大一倍,此时图片的大小为320*80;缩小一倍,此时图片的大小为80*20。

对于图片的放大一倍,则要考虑不同的像素点对显示信号的共用(在这里即为m信号)。

由通常的规则,按照顺序,构成一个正方形的每四个相邻的像素点共用一个m信号。

同时,在这里对x_vdn以及y_vdn的最后一位判断,并且形成不同的映射规则。

具体的映射规则在源代码中给出。

对于图片的缩小,则相对简单的多。

此时的映射关系为:addr=y_vdn*320+x_vdn*2;3.工程结构与解读如图,下图为系统的结构框图。

使用 FPGA 控制 VGA 显示

使用FPGA 控制VGA 显示

显示器因为其输出信息量大,输出形式多样等特点已经成为现在大多数

设计的常用输出设备。

在FPGA 的设计中可以使用很少的资源,就产生VGA 各种控制信号。

这个示例在RHicSP2200B FPGA 开发板/学习板上使用VGA 接口在显示器上显示了文字以及简单的图形,可以作为VGA 显示设计的参考,如果在使用这个例子的过程中有任何问题都可以通过邮件说明:有效时间包括6 列过扫描边界列,有些时序表将这几列加在后沿和前沿中表 2 垂直时序

说明:有效时间包括 4 行过扫描边界行,有些时序表中将这几行加在后沿和前沿中。

*当有效时间增加时,它超过了vsync 信号的上升沿,因此前沿为-1

在实际设计中如何通过不同的系统频率确定适当的显示模式?例如在RhicSP2200 开发板中FPGA 的系统时钟频率为50MHz。

这个时钟频率可以用来设计显示800X600 模式,为了显示器显示效果好,采用场频(刷新频率)75Hz,那么帧长可以确定为666,而行总长设计为1000 像素。

根据以上所述,我们可以设计如Examples1 类似HDL 代码,使用这段代码在Valid 有效期间对RGB 中Blue 两位赋值1,得到一个蓝色屏幕显示边界如图1 所示。

色彩原理

RGB 色彩模式是工业界的一种颜色标准,是通过对红(R)、绿(G)、蓝(B)三个颜色通道的变化以及它们相互之间的叠加来得到各式各样的颜色的,RGB 即是代表红、绿、蓝三个通道的颜色,通过三种基本颜色亮度值从0~255 不同产生出其他各种颜色,这种模式叫加色模式。

为什么叫加色模式呢,举个例。

基于FPGA的VGA图像显示

基于FPGA的VGA图像显示1、VGA显示原理VGA标准是一种计算机显示标准,最初是由IBM公司在1987 年提出的,分辨率是640*480。

VGA 接口也叫做D_Sub 接口,是显卡上输出模拟信号的接口。

目前大多数计算机与外部显示设备之间都是通过模拟VGA接口连接,计算机内部以数字方式生成的显示图像信息,被显卡中的D/A 转换器转变为R、G、B三原色信号和行、场同步信号,信号通过电缆传输到显示设备中。

常见的彩色显示器一般由阴极射线管(CRT) 构成,彩色由GRB(Green Red Blue) 基色组成。

显示采用逐行扫描的方式解决,阴极射线枪发出电子束打在涂有荧光粉的荧光屏上,产生GRB 基色,合成一个彩色像素。

扫描从屏幕的左上方开始,从左到右,从上到下,逐行扫描,每扫完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT 对电子束进行消隐,每行结束时,用行同步信号进行行同步;扫描完所有行,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,并预备进行下一次的扫描。

要实现VGA显示就要解决数据来源、数据存储、时序实现等问题,其中关键还是如何实现VGA时序。

VGA的标准参考显示时序如图1所示。

行时序和帧时序都需要产生同步脉冲(Sync a)、显示后沿(Back porch b)、显示时序段(Display interval c)和显示前沿(Front porch d)四个部分。

2、方案设计由VGA的显示原理可知,该任务的关键是VGA时序控制部分和汉字图形显示部分:(1)VGA时序控制部分,采用FPGA本地50MHz时钟,根据所需时序要求,经Verilog语言编写的计数模块分频而得到,该部分十分重要,如果产生的时序有偏差,那么就会使汉字图形无法显示或显示结果混乱;(2)汉字图形显示部分,有2种方法可以实现:第1 种是在对像素进行行计数、场计数的时候,就把字库信息直接赋值给颜色信号R、G、B,这种方法虽然简单,但是控制很不灵活,需要对汉字的显示像素一一判定对应的位置,容易出现错误,不易修改,所以本次采用的是第2 种方法,第2 种方法是使用FPGA内部的一种资源来存储汉字的字库信息,然后由程序将其提取出来作为显示信号发送到VGA 接口,以实现汉字图形的显示,这样就克服了第一种方法易出错又不易修改的缺点。

基于FPGA的VGA图形控制器

基于FPGA的VGA图形控制器设计引言VGA(视频图形阵列)作为一种标准的显示接口得到广泛的应用。

利用FPGA 芯片和EDA 设计方法,可以因地制宜,根据用户的特定需要,设计出针对性强的VGA 显示控制器,不仅能够大大降低成本,还可以满足生产实践中不断变化的用户需要,产品的升级换代方便迅速。

在本设计中采用了Altera 公司的EDA 软件工具Quartus II ,并以ACEX系列FPGA 的器件为主实现硬件平台的设计。

1 基于FPGA 的VGA 图形控制器系统框图根据自顶向下的程序设计思想,采用模块化设计,我们对VGA 图形控制器进行功能分离并按层次设计。

利用VHDL 硬件描述语言逐一对每个功能模块进行描述,并逐个通过编译仿真,最后下载到硬件平台调试。

本设计的VGA 控制器主要由以下模块组成:VGA 时序控制模块、分频模块、汉字显示模块、图像控制模块、ROM读取模块等,如图1 所示。

图1 基于FPGA 的VGA 图形控制系统框图2 主要功能模块设计2. 1 VGA 时序控制模块VGA 时序控制模块是整个显示控制器的关键部分,最终的输出信号行、场同步信号必须严格按照VGA 时序标准产生相应的脉冲信号。

对于普通的VGA 显示器,其引出线共含5 个信号: G,R ,B (3 基色信号) ,HS (行同步信号) ,VS(场同步信号)。

在5个信号时序驱动时,VGA 显示器要严格遵循“VGA工业标准”,即640 Hz ×480 Hz ×60Hz 模式。

对于VGA 显示器,每个像素点的输出频率为25. 175MHz ,因此采用50MHz 的时钟信号,经过二分频模块,得到25MHz 的输入时钟脉冲。

依据VGA 时序标准,行同步信号HS ,行周期为31. 78μs ,每显示行包括800 点,其中640 点为有效显示区,160 点为行消隐区,每行有一个脉冲,该脉冲的低电平宽度为3. 81μs (即96 个脉冲) ; 场同步信号VS ,场周期为16.683ms ,每场有525 行,其中480 行为有效显示行,45 行为场消隐区,每场有一个脉冲,该脉冲的低电平宽度为63μs (2 行)。

基于FPGA的VGA图像控制器设计与实现

VA 图像 控制 器 是一 个较 大 的数字 系 统 。采用 模块 化 设计 原 G 则和 自顶 向 下的设 计思想 ,进 行功 能分 离并按 层 次设 计 。将 V D HL 硬件 描述 语言 设计 与 原理 图设 计相 结合 ,逐 一对 每个 功 能模 块进 行仿 真 ,使顶 层 V A图像 控制 器 的模块 实 体仿真 综合 得 以顺利 通 G 过 。V A 控制 器主 要 由 以下模 块组成 :消 隐模块 ,显 示模 块 ,分 G 频模 块 ,网格 生成 模块 ,汉字 显示模 块 , 图像控 制模 块 ,动 画生 成模 块 ,LMR M 用模 块 ,EP O P— O 调 E RM调用 模块 等 。 三 、模块 设计 ( )消 隐模块 一 消 隐模 块 是整个 显示 控制 器 的关 键部 分 ,显示 模 块 、汉字 模 块 、彩 条模 块 、 网格 模块 、动画控 制 模块 、L MR M 调用 模块 等 P- O 都 由消 隐模 块控 制 ,并且 行 同步信 号 (s 和场 同步 信 号 (s都 由 H) v)

Hu Yi ana nQa

( h n d stt f i u nN r l n esyCh n d 6 5 ,hn ) C e g uI tueo Sc a oma U i ri, e g u 1 4C ia ni h v t 1 7

Ab ta t DA c n lg sr c: E t h oo yn1i tec r fmo e eeto i eintc n lg , l so o ru o ue lt r i e s h oeo d m lc ncd s eh oo yir i np wef1c mp trpaf m r g te e o n

计 算机 光盘 软件 与应 用

基于FPGA的VGA图像的显示与控制

基于FPGA的VGA图像的显示与控制作者:刘明锐李春晓来源:《西部论丛》2019年第30期摘要:随着信息时代的到来,科技发展的脚步越来越快,CCD、COMS等传统的传感器已经无法跟上信息量越来越大的视觉图像,这使得计算机在对视觉图像处理的速度方面越来越吃力了,并具有相当的延迟性,人们对图像的要求越来越高,已不再满足于黑白画面和低像素画质。

VGA的到来解决了这个问题,而FPGA则解决了VGA显示图像时的图像显示复杂、难操作问题。

此次论文我将使用FPGA芯片让图片在VGA显示器上显示。

关键词:FPGA;; VGA显示;图像处理从结构上看,CPLD是连续式布线结构,FPGA则是分段式布线结构,CPLD有一定的延迟,但它可以在配置线上进行测量,FPGA非常逐项化,而且不可预测的可能性非常高,但是其功耗要低于CPLD。

与CPLD相比,FPGA在编程方面虽然稍逊于CPLD,但CPLD却具有更好的保密性。

虽然CPLD和结构是该方法最主要的地方。

数字设备所具备的功能它也一样可以实现。

由于FPGA是拥有多种颜色的,进行编排的时候更加方便。

可编程逻辑器件(CPLD)的修改虽然是有限的,但却适用于各种修改。

因此,对选择与时序逻辑有关的系统最好还是利用FPGA实现电路的进一步发展。

1.系统功能模块的设计1.1系统整体架构系統的整体框架由时钟分频再到VGA显示和VGA驱动,最后输出到VGA显示器中。

由于图片都是由数字信号组成的,利用VGA接口把数字信号输送至显示器。

由于VGA接口是模拟信号接口,所以要利用FPGA把图片上数字信号转变为模拟信号,再通过VGA接口传输至显示器。

1.2分频模块将输入频率固定成一种适合于系统的时钟频率。

因为此实验要求显示640*480@60Hz的图片,可以计算得出该图片的场频率,即扫描一个画面所需要的时间。

即800*525*60=25.2/MHz。

通过PLL(Phase-Locked Loop 锁相环)输出稳定且高频的信号。

华科 基于FPGA的VGA显示实验

电子线路测试与实验报告基于FPGA的VGA显示实验姓名:专业班级:光电1208学号:U2012一、实验要求功能要求:利用Basys2实验板实现图片在VGA接口显示器上的显示。

基本要求:1)实现240*160以上像素的图片在VGA接口显示器上的显示;2)利用算法实现特定图片在VGA接口显示器上的放大、缩小旋转及其他动作的自动变换。

二、实验具体目标1.首先实现特定图片在显示器上的显示;2.图片自动旋转90度;3.实现图片的放大与缩小,同样通过一个按键实现;4.添加复位键,按下复位键后图片返回最初的状态。

三、实验原理1.VGA的显示原理在基于FPGA的VGA控制中,只需考虑行同步信号(HS),场同步信号(VS),以及红绿蓝三基色(R、G、B)这五个信号,即可实现对VGA显示的控制。

2.对图片的旋转与缩放操作对图片的旋转操作在本质上是对IP核ROM的输入地址addr进行变换的过程。

在这里,假定显示的坐标分别为x_vdn以及y_vdn,由于图片是160*40的,在正常的显示时,addr与x_vdn以及y_vdn的对应关系应该为:addr=x_vdn+y_vdn*160即依次取像素点,图片正常显示。

要把图片顺时针旋转90度,那么相当于显示的图片是40*160的,重新考虑addr与两个坐标之间映射关系。

容易得到,此时:addr=(39-x_vdn)*160+y_vd对图片的缩放操作对图片的缩放操作则只考虑以下两种变化,即放大一倍,此时图片的大小为320*80;缩小一倍,此时图片的大小为80*20。

对于图片的放大一倍,则要考虑不同的像素点对显示信号的共用(在这里即为m信号)。

由通常的规则,按照顺序,构成一个正方形的每四个相邻的像素点共用一个m信号。

同时,在这里对x_vdn以及y_vdn的最后一位判断,并且形成不同的映射规则。

具体的映射规则在源代码中给出。

对于图片的缩小,则相对简单的多。

此时的映射关系为:addr=y_vdn*320+x_vdn*2;3.工程结构与解读如图,下图为系统的结构框图。

基于fpga的vga图像显示控制器设计__本科毕业设计论文

基于FPGA的VGA图像显示控制器设计第1页一.实验简介本实验介绍了一种利用可编程逻辑器件实现VGA图像显示控制的方法,阐述了VGA 图像显示控制器中VGA显像的基本原理以及功能演示,利用可编程器件FPGA设计VGA 图像显示控制的VHDL设计方案,并在Altera公司的QuartusII软件环境下完成VGA 模块的设计。

而且给出了VGA模块的设计思路和顶层逻辑框图。

最终实现VGA图像显示控制器,VGA图像控制器是一个较大的数字系统,传统的图像显示的方法是在图像数据传输到计算机,并通过显示屏显示出在传输过程中,将图像数据的CPU需要不断的信号控制,所以造成CPU的资源浪费,系统还需要依靠计算机,从而减少了系统的灵活性。

FPGA芯片和EDA设计方法的使用,可根据用户的需求,为设计提供了有针对性的VGA显示控制器,不需要依靠计算机,它可以大大降低成本,并可以满足生产实践中不断改变的需要,产品的升级换代和方便迅速。

二.任务要求2.1课题要求设计一个VGA 图像显示控制器。

1.显示模式为640×480×60Hz 模式;2.用拨码开关控制R、G、B(每个2 位),使显示器可以显示64 种纯色;3.在显示器上显示横向彩条信号(至少6 种颜色);4.在显示器上显示纵向彩条信号(至少8 种颜色);5.在显示器上显示自行设定的图形、图像等。

2.2设计目标根据课题要求,实验中将目标进行了细化,叙述如下:1.设定4种显示模式:横彩模式、纵彩模式、纯色模式、用户模式;第2页2.拨码开关最低两位SW1~SW0控制4种模式的切换;3.拨码开关高6位SW7~SW2每两位分别控制RGB显示64种纯色;4.横向和纵向彩条均设置为8种内置的颜色;5.用户模式中分3种子模式:1)子模式1是沿固定轨迹运动模式,固定图形沿水平方向运动,行运动到边界后折回到下一行继续水平运动;2)子模式2是反弹球模式,固定图形在矩形屏幕做内直线运动,到边界后沿反射角方向反弹,周而复始;3)子模式3是受控运动模式,使用上下左右4个按键控制固定图形在屏幕内的运动方向;4)子模式间的切换由一个单独的按键进行控制,按键按下后顺序切换子模式。

基于FPGA的PS2与VGA控制显示设计

摘要伴随着嵌入式系统的迅速发展,VGA(视频图形阵列)作为一种标准的显示接口得到广泛的应用,PS/2接口也广泛的应用于鼠标和键盘。

文中在依据VGA显示的原理和PS/2鼠标通信协议的基础上,在讨论EDA软件工具平台下的FPGA设计流程的前提下,基于模块化、层次化的设计思想,利用VHDL作为逻辑描述的手段,在Altera公司的QuarmsII软件环境下完成VGA模块和PS/2接口模块的设计。

本设计在利用VGA模块和PS/2接口模块的基础上,实现了鼠标控制VGA显示,完成了一个小游戏的设计,并给出了顶层逻辑框图和各个模块的设计思路。

通过软件和FPGA 的结合,可以将VGA接口要显示的数据直接送到显示器,保证了PS/ 2 接口收发数据的精确性和可移植性, 加快了数据的处理速度,节约了硬件成本。

关键字FPGA/VHDL/VGA /PS/2Design of PS/2 and VGA Display Control Based on FPGAABSTRACTAs the fast development of embeded system,As a standard display interface,VGA has been widely used, PS / 2 module is also widely used in the mouse and keyboard.In this article,according to the principle of VGA display and the analysis of the communication protocol of mouse,completed the design of VGA module based on QuartuslI softerware environment and the design idea about modularization、hiberarchy while using VHDL as a means of logic description as well as discussed the process of the design of FPGA based on EDA softerware platform.Also gave the ideas of VGA module and PS/2 module design and the top logic diagram of this modular.This design is based on VGA module and PS / 2 interface modules. It fulfills the mouse-control VGA display, and completes the design of a simple game. It also gives a top-level logic block diagram and the design of each module. Through the combination of certain software and FPGA, it is possible to send data which will be displayed by VGA interface directly to the monitor. It ensures the accuracy and the possibility of transplant when adopting the PS / 2 transceiver interface. Meanwhile, it speeds up the data processing rate and cut down hardware costs.KEY WORDS FPGA,VHDL,VGA ,PS/2目录中文摘要.................................... 错误!未定义书签。

基于FPGA的VGA显示

`timescale 1ns / 1ps/////////////////////////////////////////////////////////////////// /////////////// Company:// Engineer://// Create Date:// Design Name:// Module Name:// Project Name:// Target Device:// Tool versions:// Description://// Dependencies://// Revision:// Revision 0.01 ‐ File Created// Additional Comments:///////////////////////////////////////////////////////////////////// /////////////module vga_dis(clk,rst_n,hsync,vsync,vga_r,vga_g,vga_b);input clk; //50MHzinput rst_n; //低电平复位output hsync; //行同步信号output vsync; //场同步信号output vga_r;output vga_g;output vga_b;//‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐reg[10:0] x_cnt; //行坐标reg[9:0] y_cnt; //列坐标always @ (posedge clk or negedge rst_n)if(!rst_n) x_cnt <= 11'd0;else if(x_cnt == 11'd1039) x_cnt <= 11'd0; else x_cnt <= x_cnt+1'b1;always @ (posedge clk or negedge rst_n)if(!rst_n) y_cnt <= 10'd0;else if(y_cnt == 10'd665) y_cnt <= 10'd0;else if(x_cnt == 11'd1039) y_cnt <= y_cnt+1'b1;//‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐wire valid; //有效显示区标志assign valid = (x_cnt >= 11'd187) && (x_cnt < 11'd987)&& (y_cnt >= 10'd31) && (y_cnt < 10'd631);wire[9:0] xpos,ypos; //有效显示区坐标assign xpos = x_cnt‐11'd187;assign ypos = y_cnt‐10'd31;//‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐reg hsync_r,vsync_r; //同步信号产生always @ (posedge clk or negedge rst_n)if(!rst_n) hsync_r <= 1'b1;else if(x_cnt == 11'd0) hsync_r <= 1'b0; //产生hsync信号 else if(x_cnt == 11'd120) hsync_r <= 1'b1;always @ (posedge clk or negedge rst_n)if(!rst_n) vsync_r <= 1'b1;else if(y_cnt == 10'd0) vsync_r <= 1'b0; //产生vsync信号else if(y_cnt == 10'd6) vsync_r <= 1'b1;assign hsync = hsync_r;assign vsync = vsync_r;//‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐//显示一个矩形框wire a_dis,b_dis,c_dis,d_dis; //矩形框显示区域定位assign a_dis = ( (xpos>=200) && (xpos<=220) )&& ( (ypos>=140) && (ypos<=460) );assign b_dis = ( (xpos>=580) && (xpos<=600) )&& ( (ypos>=140) && (ypos<=460) );assign c_dis = ( (xpos>=220) && (xpos<=580) )&& ( (ypos>140) && (ypos<=160) );assign d_dis = ( (xpos>=220) && (xpos<=580) )&& ( (ypos>=440) && (ypos<=460) );//显示一个小矩形wire e_rdy; //矩形的显示有效矩形区域assign e_rdy = ( (xpos>=385) && (xpos<=415) )&& ( (ypos>=285) && (ypos<=315) );//‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐//r,g,b控制液晶屏颜色显示,背景显示蓝色,矩形框显示红蓝色assign vga_r = valid ? e_rdy : 1'b0;assign vga_g = valid ? (a_dis | b_dis | c_dis | d_dis) : 1'b0; assign vga_b = valid ? ~(a_dis | b_dis | c_dis | d_dis) : 1'b0;endmodule。

基于FPGA的VGA显示控制设计

引言基于FPGA的VGA显示控制设计1 引言1.1 选题背景CRT显示器作为一种通用型显示设备,如今已广泛应用于我们的工作和生活中。

与嵌入式系统中常用的显示器件相比,它具有显示面积大、色彩丰富、承载信息量大、接口简单等优点,如果将其应用到嵌入式系统中,可以显著提升产品的视觉效果。

如今随着液晶显示器的出现,越来越多的数字产品开始使用液晶作为显示终端。

但基于VGA标准的显示器仍是目前普及率最高的显示器[1]。

若驱动此类显示器,需要很高的扫面频率,以及极短的处理时间,正是由于这些特点,所以可以用FPGA来实现对VGA 显示器的驱动。

本次专业课程设计即选用FPGA来实现VGA图片的显示。

随着FPGA的不断发展及其价格的不断下降,FPGA的可编程逻辑设计的应用优势逐渐显现出来。

现在,越来越多的嵌入式系统选择了基于FPGA的设计方案。

在基于FPGA的大规模嵌入式系统设计中,为实现VGA显示功能,既可以使用专用的VGA接口芯片如SPX7111A等,也可以设计和使用基于FPGA的VGA接口软核。

虽然使用VGA 专用芯片具有更稳定的VGA时序和更多的显示模式可供选择等优点,但设计和使用VGA接口软核更具有以下优势:(1)使用芯片更少,节省板上资源,减小布线难度;(2)当进行高速数据传输时,具有更小的高频噪声干扰;(3)FPGA(现场可编程门阵列)设计VGA接口可以将要显示的数据直接送到显示器,节省了计算机的处理过程,加快了数据的处理速度,节约了硬件成本。

1.2 目的和意义显示绘图阵列(video graphic array,VGA)接口,他作为一种标准的显示接口得到了广泛的应用。

VGA接口大多应用在显示器与显卡之间;同时还可以用用在擦二色等离子电视输入图像的模数转换上;VGA接口同样也是LCD液晶显示设备的标准接口[2]。

可编程逻辑器件随着微电子制造工艺的发展取得了长足的进步[3]。

早期的器件只能存储少量的数据,完成简单的逻辑功能;发展到现在,可以完成复杂的逻辑功能,速度更块,规模更大,功耗更低。

电子信息工程专业基于FPGA的SD卡图像的VGA显示毕业设计论文

本科毕业设计(论文) 论文题目:基于FPGA的SD卡图像的VGA显示摘要基于FPGA的SD卡图像的VGA显示,是利用可编程逻辑器件将图像的数据通过VGA 线实现图像的显示控制的,详细说明了在显示控制器中VGA的基本功能作用和其工作原理。

此次设计是在Xilinx公司的ise 14.7软件环境下,使用 Verilog语言来编写程序模块设计,实现SD卡图像的VGA显示控制设计。

要在最终的电脑显示屏上获得图像显示,需通过开发板上电,先读取SD卡中的图像数据并把它存储在DDR3中,然后再将DDR3的图像数据通过VGA线显示到的屏幕上。

传统的图像显示是将数据传送到计算机上,在显示屏上直接显示。

在此过程中,需要信号不断控制图片的数据,这将很大程度上造成CPU资源的浪费,而且系统也脱离不了计算机,造成显示控制的灵活性降低。

但是伴随可编程逻辑器件(FPGA)技术的发展,设计者采用EDA设计方法便可以实现针对性的VGA显示控制,可以脱离计算机来控制系统,并且能够满足实践生产的需要,大大降低了投入成本,产品的更新换代更加迅速方便,推动了行业的发展。

关键词:可编程逻辑器件;VGA ;显示控制AbstractSD card based on FPGA image of VGA display, is the use of programmable logic devices of the image data through the VGA line image display control, in VGA display controller is described in detail the basic functions and its working principle.In Xilinx ise 14.7 software environment, use Verilog language to write the SD card image of VGA display control design, completed the FPGA modular design.Achieve VGA display control, need to electricity, on the development board to read SD card of the image data and store it in DDR3, then continuously read DDR3 image data through the VGA line show on the screen.The traditional image display is to transfer the data to computer, displayed on the screen, in this process, the image data the CPU needs constant control signal, it will largely wastes the CPU resources, but also from the computer system, which reduces the display control flexibility.But along with the development of the programmable logic device (FPGA) technology, the designers use EDA design method can realize the VGA display of the targeted control, can from computer to control system, and can meet the needs of practical production, greatly reduces the cost, upgrading of products is more convenient quickly, promote the development of the industry.Keywords:Programmable logic devices ; VGA ;display control目录前言 (1)第1章 VGA概述 (2)1.1 VGA显示技术的发展概况 (2)1.2 VGA显示接口 (3)1.3 VGA显示原理 (4)1.4 VGA时序 (5)第2章 FPGA简介及设计流程 (8)2.1 FPGA简介 (8)2.2 FPGA设计流程 (8)2.3 Verilog简介 (111)2.4 Xilinx ise14.7简介 (122)第3章设计方案 (14)3.1 设计的主要内容 (144)3.2 设计原理 (155)第4章系统实现 (16)4.1 VGA显示控制模块 (16)4.2 MIG IP控制器 (19)4.2.1 MIG IP介绍 (19)4.2.2 MIG IP的生成 (21)4.3 Image2Lcd和winhex工具的使用 (256)4.4 SD卡顶层设计模块 (269)4.5 顶层设计 (34)4.6 程序下载和设计结果 (345)4.6.1 IMPACT软件进行程序的烧写 (345)4.6.2 设计结果 (347)第5章结束语 (39)参考文献 (41)致谢 (42)附录 (43)前言随着现代化科技的发展,信息化时代的到来,以计算机为核心的电子信息技术正在迅速的发展,各种各样的电子产品进入大众的视野,人们很大一部分的视觉信息都说是通过各种电子显示产品获得的,所以对电子显示设备的需求也越来越多,在众多因素的影响与要求下,对电子技术的要求也越来越高,某种程度上来讲,也促进了电子显示技术的飞速发展。

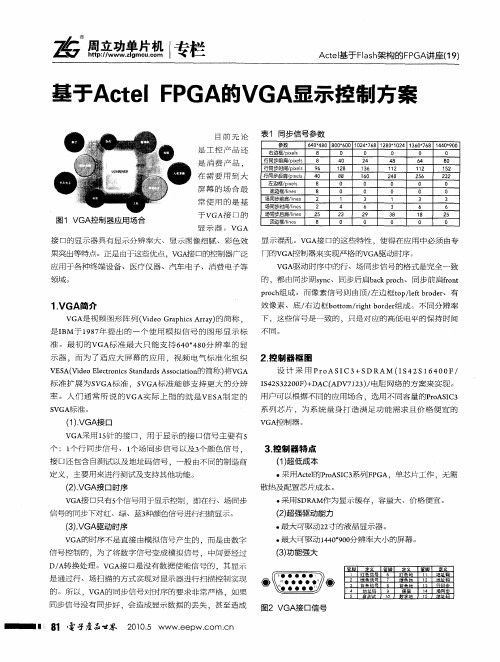

基于Actel FPGA的VGA显示控制方案

显 示 混 乱 。V A 口 的 这 些 特 性 ,使 得 在 应 用 中 必 须 由专 G 接

A j 器 G 马动 果 突 出等 特 点 。正 是 由于 这 些优 点 ,V A E的控 制 器广 泛 门 自 G  ̄ I 来 实现 严格 的v A 区 时 序 。 G ̄ 3

应 用 于 各 种 终 端 设 备 、 医疗 仪 器 、汽 车 电 子 、 消 费 电 子 等

1VGA 介 . 简

V A是视频 图形 阵 ̄( ie ahc Ar y的简称 , G V d oGrp is r ) a

效 像 素 、底 / 边  ̄ b t m/ih odr 成 。不 同 分辨 率 右 ot r t re组 o g b 下 ,这 些 信 号 是 一 致 的 ,只 是 对 应 的 高 低 电平 的保 持 时 间

右边框/ i l px s e 行同步前肩/i l p es x 行同步时I p es ' il  ̄/ x

行同步 ̄ / f l px s e 左边框/i l p es x 底边框/n s l e i 场同步前肩/ n s l e i 场同步时间/n s l e i 场周步后肩/ n s l e i 顶边框/n s l e i

率 。人们 通 常所 说 的V GA实 际 上 指 的 就 是 VE A ̄ 定 的 用 户 可 以根 据 不 同 的应 用场 合 选 用 不 同 容 量 的 Po I S 1 rASC3

S G 标准。 V A

系 列 芯 片 ,为 系 统 量 身 打 造 满 足 功 能 需 求 且 价 格 便 宜 的 V A G  ̄ I 。 J 器

散热及配置芯片成本。

・

采 用 S A 作 为 显 示 缓 存 ,容 量 大 、价 格 便 宜 。 DR M

课程设计-基于FPGA的VGA图像显示设计(图像旋转、放大、单步步进移动和屏保移动)

电子信息工程专业综合设计(报告)(课程设计)题目基于FPGA的VGA图像显示设计(图像旋转、放大、单步步进移动和屏保移动)二级学院电子信息与自动化学院专业电子信息工程班级学生姓名学号指导教师时间 2011.12.26-2012.01.13基于FPGA的VGA图像显示设计及应用摘要:VGA(视频图形阵列)作为一种标准的显示接口得到广泛的应用。

本文依据VGA显示原理,介绍了利用 FPGA 实现对VGA图形控制器VHDL设计方法。

详细描述了各硬件模块的工作原理及实现途径,并给出了软件设计思路及部分代码。

关键词:VGA;FPGA;VHDL0. 引言随着可编程逻辑器件的不断发展及其价格的不断下降,EDA 开发软件的不断完善,可编程逻辑设计的应用优势逐渐显示出来,特别是大规模可编程器件。

而FPGA 具有功能强大,开发过程投资小、周期短等特点,成为当今硬件设计的首选方式之一。

VGA(视频图形阵列)作为一种标准的显示接口得到广泛地应用。

利用 FPGA 芯片和 EDA设计方法,可以灵活地根据用户需求,设计出针对性强的 VGA 显示控制器,不仅降低了生产成本也可以快速地对产品进行升级换代。

本文设计采用 Quartus II 9.0软件工具,并以 Altera公司的 Cyclone 系列 FPGA 的器件EP1C12F324C8为主实现硬件平台的设计。

1.方案设计及工作原理1.1方案设计采用模块化设计方法,我们对 VGA 图形控制器按功能进行层次划分。

本设计的VGA控制器主要由以下模块组成:VGA 时序控制模块、ROM 内存地址控制模块、1.2工作原理根据VGA的显示协议,可以选择不同的显示分辨率。

本设计选择的是800*600的分辨率。

根据相应协议,在“VGA时序控制模块”对行扫描信号HS和场扫描信号VS进行相应的时序控制(具体控制详细信息见“VGA驱动原理”资料文档)。

“ROM内存地址控制模块”根据“按键扫描控制模块”获得的图片显示首坐标xx、yy信息和“VGA时序控制模块”传送过来的hcnt(列计数器值)、vcnt(行计数器值)及相关控制信号计算出正确的内存地址,从rom中取出所需要的像素点的三基色数据。

课程设计-基于fpga的vga图形显示大学论文

电子信息工程专业综合设计(报告)(课程设计)题目基于FPGA的VGA图形显示二级学院电气与电子工程学院专业电子信息工程班级学生姓名学号同组姓名指导教师时间基于FPGA的VGA图形显示摘要:本次的题目是基于FPGA的VGA图形显示,实现VGA图像显示与控制。

本文介绍的主要内容围绕着显示特定图片,且图片可受控制的相关原理与方法展开。

根据VGA显示原理,利用VHDL作为逻辑描述手段,设计了一种基于现场可编程器件FPGA的VGA接口控制器。

实现VGA图像显示控制器是通过Altera公司的QuartusII软件环境下对VGA模块的设计和顶层逻辑框图设计。

FPGA的嵌入式系统中能代替VGA的专用显示芯片,节约硬件成本,节省计算机处理时间,加快数据处理速度并具有显示面积大,色彩丰富、承载信息量大、接口简单等优点。

除此以外FPGA芯片和EDA设计方法的使用,可根据用户的需求,为设计提供了有针对性的VGA显示控制器,可不需要依靠计算机,它可以大大降低成本,并可以满足生产实践中不断改变的需要。

关键字:FPGA VGA 图像控制器一、前言本次课程设计主要是通过Altera公司的QuartusII软件环境下对VGA模块的设计和顶层逻辑框图设计。

VGA是IBM于1987年提出的一个使用模拟信号的电脑显示标准。

在性能上,VGA将16色模式的分辨率提高到了640×480,同时VGA新提供了一种具有320×200分辨率、256种颜色的图形模式,且所显示的每一种颜色都可从262144(18位)种颜色中选择,VGA的这种色彩显示能力对微机图形/图象软件的发展起到了很大的促进作用先后分别经历了EGA, EGA, VGA, SVGA, XGA, SXGA, UXGA, QXGA, WQXGA, QSXGA, WQSXGA, QUXGA, WQUXGA, 1080P。

目前大多数计算机与外部显示设备之间都是通过模拟VGA接口连接,计算机内部以数字方式生成的显示图像信息,被显卡中的数字/模拟转换器转变为R,G,B三原色信号和行、场同步信号,信号通过电缆传输到显示设备中。

基于FPGA的VGA图形显示

电子信息工程专业综合设计(报告)(课程设计)题目基于FPGA的VGA图形显示二级学院电气与电子工程学院专业电子信息工程班级学生学号同组指导教师时间基于FPGA的VGA图形显示摘要:本次的题目是基于FPGA的VGA图形显示,实现VGA图像显示与控制。

本文介绍的主要容围绕着显示特定图片,且图片可受控制的相关原理与方法展开。

根据VGA显示原理,利用VHDL 作为逻辑描述手段,设计了一种基于现场可编程器件FPGA的VGA接口控制器。

实现VGA图像显示控制器是通过Altera公司的QuartusII软件环境下对VGA模块的设计和顶层逻辑框图设计。

FPGA的嵌入式系统中能代替VGA的专用显示芯片,节约硬件成本,节省计算机处理时间,加快数据处理速度并具有显示面积大,色彩丰富、承载信息量大、接口简单等优点。

除此以外FPGA 芯片和EDA设计方法的使用,可根据用户的需求,为设计提供了有针对性的VGA显示控制器,可不需要依靠计算机,它可以大大降低成本,并可以满足生产实践中不断改变的需要。

关键字:FPGA VGA 图像控制器一、前言本次课程设计主要是通过Altera公司的QuartusII软件环境下对VGA模块的设计和顶层逻辑框图设计。

VGA是IBM于1987年提出的一个使用模拟信号的电脑显示标准。

在性能上,VGA 将16色模式的分辨率提高到了640×480,同时VGA新提供了一种具有320×200分辨率、256种颜色的图形模式,且所显示的每一种颜色都可从262144(18位)种颜色中选择,VGA的这种色彩显示能力对微机图形/图象软件的发展起到了很大的促进作用先后分别经历了EGA, EGA, VGA, SVGA, XGA, SXGA, UXGA, QXGA, WQXGA, QSXGA, WQSXGA, QUXGA, WQUXGA, 1080P。

目前大多数计算机与外部显示设备之间都是通过模拟VGA接口连接,计算机部以数字方式生成的显示图像信息,被显卡中的数字/模拟转换器转变为R,G,B三原色信号和行、场同步信号,信号通过电缆传输到显示设备中。

课程设计-基于FPGA的VGA图像显示设计(图像旋转、放大、单步步进移动和屏保移动)

电子信息工程专业综合设计(报告)(课程设计)题目基于FPGA的VGA图像显示设计(图像旋转、放大、单步步进移动和屏保移动)二级学院电子信息与自动化学院专业电子信息工程班级学生姓名学号指导教师时间 2011.12.26-2012.01.13基于FPGA的VGA图像显示设计及应用摘要:VGA(视频图形阵列)作为一种标准的显示接口得到广泛的应用。

本文依据VGA显示原理,介绍了利用 FPGA 实现对VGA图形控制器VHDL设计方法。

详细描述了各硬件模块的工作原理及实现途径,并给出了软件设计思路及部分代码。

关键词:VGA;FPGA;VHDL0. 引言随着可编程逻辑器件的不断发展及其价格的不断下降,EDA 开发软件的不断完善,可编程逻辑设计的应用优势逐渐显示出来,特别是大规模可编程器件。

而FPGA 具有功能强大,开发过程投资小、周期短等特点,成为当今硬件设计的首选方式之一。

VGA(视频图形阵列)作为一种标准的显示接口得到广泛地应用。

利用 FPGA 芯片和 EDA设计方法,可以灵活地根据用户需求,设计出针对性强的 VGA 显示控制器,不仅降低了生产成本也可以快速地对产品进行升级换代。

本文设计采用 Quartus II 9.0软件工具,并以 Altera公司的 Cyclone 系列 FPGA 的器件EP1C12F324C8为主实现硬件平台的设计。

1.方案设计及工作原理1.1方案设计采用模块化设计方法,我们对 VGA 图形控制器按功能进行层次划分。

本设计的VGA控制器主要由以下模块组成:VGA 时序控制模块、ROM 内存地址控制模块、1.2工作原理根据VGA的显示协议,可以选择不同的显示分辨率。

本设计选择的是800*600的分辨率。

根据相应协议,在“VGA时序控制模块”对行扫描信号HS和场扫描信号VS进行相应的时序控制(具体控制详细信息见“VGA驱动原理”资料文档)。

“ROM内存地址控制模块”根据“按键扫描控制模块”获得的图片显示首坐标xx、yy信息和“VGA时序控制模块”传送过来的hcnt(列计数器值)、vcnt(行计数器值)及相关控制信号计算出正确的内存地址,从rom中取出所需要的像素点的三基色数据。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的VGA图像显示与控制

课程要求:采用verilog语言,基于FPGA的VGA图像显示,即能够在显示器上实现动态彩色图像的显示。

VGA显示接口的理论分析:硬件采用CycloneII系列的EP2C20Q240C8N,它含有240个引脚。

对于VGA的显示器遵循800*600@75模式,其中800是指每行中显示的像素的个数,而600是指屏幕每一列所包含的像素的个数。

VGA工业标准规定了具体地,在扫描过程中的时序图如下:

行扫描时序图

场扫描时序图

每场信号对应625个行周期,其中600行为图像显示行,每场有场同步信号,该脉冲宽度为3个行周期的负脉冲;每行显示行包括1056个点时钟,其中800点为有效显示区,每行有一个行同步信号的负脉冲,该脉冲宽度为80个点时钟。

这样我们可以知道,行频为625*75=46857Hz。

需要的点时钟的频率为:625*1056*75=49.5MHz约为50MHz。

由上图可知,实际上在真正的实现过程中,每一行扫描所花的时间实际上比显示一行的像素所花的时间多了1056-800=256个像素点。

同理,每一场的扫描时间多了625-600=25个行时间。

设计思路:

我们采用BmpToMif工具把BMP格式的图像转换为.mif文件。

利用QuartusII7.2自带的MegaWizard Plug-In Manager产生一个ROM存储器,并用其来初始时.mif 文件。

即将图像文件写入到存储器里面。

然后利用编程来控制图像的显示。

设计步骤:

1、工程创建:创建一个Project取名字为vga,在创建工程的向导中选着CycloneII

系列的EP2C20Q240C8。

2、代码书写:新建一个Verilog HDL File编写程序代码如下:

`timescale 1ns/1ps

module tupian (clk,rst_n,hsync,vsync,vga_r,vga_g,vga_b,addr);

input clk,rst_n;

output hsync,vsync,vga_r,vga_g,vga_b;

reg hsync,vsync;

output [14:0] addr;

reg [14:0] addr;

reg [10:0] x_cnt; //行坐标

reg [9:0] y_cnt; //列坐标

parameter h_Ta=80,h_Tb=128,h_Tc=32,h_Td=800,h_Te=8,h_Tf=8,h_Tg=1056; parameter v_Ta=3, v_Tb=14,v_Tc=7,v_Td=600,v_Te=0.8,v_Tf=0.2,v_Tg=625;

//------------------- 行场的计数-------------------

always @(posedge clk)

begin

if(x_cnt == h_Tg-1) x_cnt<=0;

else x_cnt<=x_cnt+1;

end

always @(posedge clk)

begin

if(y_cnt==v_Tg-1) y_cnt<=0;

else if ( x_cnt == h_Tg-1 )

y_cnt<=y_cnt+1;

end

//-------------------同步信号产生-------------------

always @(posedge clk)

begin

if(x_cnt<=h_Ta-1) hsync<=0;

else hsync<=1;

end

always @(posedge clk)

begin

if(y_cnt <= v_Ta -1) vsync <= 0;

else vsync <=1;

end

//---------------有效显示区坐标--------------------

wire valid;

assign valid = (x_cnt >= 11'd187) && (x_cnt <= 11'd987) && (y_cnt >= 10'd31) && (y_cnt <= 10'd631);

wire [9:0] xpos;

wire [9:0] ypos;

assign xpos = x_cnt-11'd187;

assign ypos = y_cnt-10'd31;

//-----------------显示图像-----------------------

reg[27:0] k;

always @ (posedge clk )

begin

if(k<=67108864)

begin

if((ypos >= 9'd100 && ypos <= 9'd229)&&(xpos >= 10'd65 && xpos <= 10'd192))

addr <= (ypos-100)*128 + (xpos-65);

else addr<=0;

end

else

begin

if((ypos >= 9'd100 && ypos <= 9'd229)&&(xpos >= 10'd573 && xpos <= 10'd700))

addr <= (ypos-100)*128 + (xpos-65);

else addr<=0;

end

if(k>134217728) k=0;

else k=k+1;

end

endmodule

编写好程序后,点击保存,将文件起名为tupian,并将其设置为顶层文件。

点击start compilation按钮,进行汇编。

3、为tupian.v产生Symbol file(符号文件):

编译完成后,点击File菜单——Create/Update——Create symbol files for current file。

4、新建原理图文件,并导入产生的符号文件:

点击菜单File——new——Block Diagram/Schematic File,双击原理图的空白处,将Project目录下的刚产生的符号文件引入到原理图。

如下图:

5、创建ROM并用它存储要显示的图片文件:

1)采用BmpToMif工具将BMP格式的图片转换为.mif文件如下图,打开软件,打开要转换的图片,颜色类型选为彩色(8)色,点击生成Mif文件。

给生产的文件起一个名字。

2)利用Quartus II7.2自带的MegaWizard Plug-In Manager产生一个ROM并将图片引入进去。

双击原理图空白处,点击MegaWizard Plug-In Manager——选择Creat a new custom megafunction variation,在安装的插件中找到Memory Compiler,选择ROM:1-PORT,选择Verilog语言,并为输出的文件起一个名字。

如设置如下:

点击Next,在弹出的窗口中,设置输出总线为3位,并为其分配的存储空间能够存储图片总的像素点的大小。

其他默认。

设置如下:

点击Next,前面一直默认,走到page 5 of 7,即第五步,点击Browse,将之前产生的.mif文件加入进来。

如下图:

点击Next,直至完成。

6、将tupian 符号文件和刚生成的Rom进行连线。

如下图:

7、引脚的绑定和设置

1)点击菜单Assignments——pin,为各引脚绑定如下:

2)将绑定的管脚设置为I/O复用:

点击菜单Assignments——Device——点击Device and Pin Options,切换到标签Dual-Purpose Pins,将nCEO的值设置为常规的I/O口。

如下图:

8、将原理图文件设置成为顶层文件,然后点击编译运行,运行后,引脚绑定如

下:

9、将编译生成的.sof文件下载到硬件里:

实验结果:

实验效果如下图,彩色图片能够在两个位置进行动态显示,可以在代码中控制。