PLL锁相环的设置

PLL锁相环时钟设定

PLL锁相环时钟设定未配置锁相环时(OSCCLK_PLLSEL=0):总线频率=外部晶振频率(OSCCLK)/2配置锁相环时(OSCCLK_PLLSEL=1): 系统时钟由锁相环提供,总线频率=倍频后频率(PLLCLK)/2时钟频率计算方法Fvco=2*Fosc*(SYNDIN+1)/(REFDIV+1)Fpll=Fvco/(2*POSTDIV)当POSTDIV=0时,Fpll=FvcoFbus=Fpll/2CRGFLG_LOCK==1时,说明PLLCLK稳定,可输出。

锁相环从设定到稳定需要时间,故期间应加几条空语句。

例程:void CLK_Init(void) {CLKSEL=0x00; //选择OSCCLK为系统时钟源16M PLLCTL_PLLON=1; //开启锁相环,锁相环电路允许//频率设定80M时SYNR = 0xc0 | 0x09;REFDV = 0x80 | 0x01;POSTDIV = 0x00; // PLLCLOCK=2*osc*(1+SYNR)/(1+REFDV)=160MHz; _asm(nop);_asm(nop);while(!CRGFLG_LOCK); // 时钟频率已稳定,锁相环频率锁定CLKSEL_PLLSEL=1; //使能锁相环时钟}PWM模块PWME:PWM允许寄存器,置1时允许输出。

PWMPOL:极性寄存器。

置1时首先输出高电平。

2、3、6、7、置1时clock SB 作为时钟源,置0时clock B作为时钟源PWMCAE:居中对齐允许寄存器,只有当通道输出禁止时才能设置此寄存器置1时为居中对齐,置0时左对齐PWMSCLA:比例因子寄存器A;用于提供clock SA的比例因子Clock SA的时钟频率= clock A/(2*PWMSCLA)当PWMSCLA为0时比例因子默认为256. CLOCKSB 计算方法类似,寄存器为PWMSCLB。

PWMCNTx:通道计数寄存器,一般设置值为0x00;PWMPERx:周期寄存器;左对齐时周期计算方法:PWMxPeriod=指定时钟周期乘以PWMPERx的值居中对齐时=指定时钟周期乘PWMPERx的值再乘2;PWMDTYx:占空比寄存器。

Altera-QuartusII 中的PLL锁相环配置简述

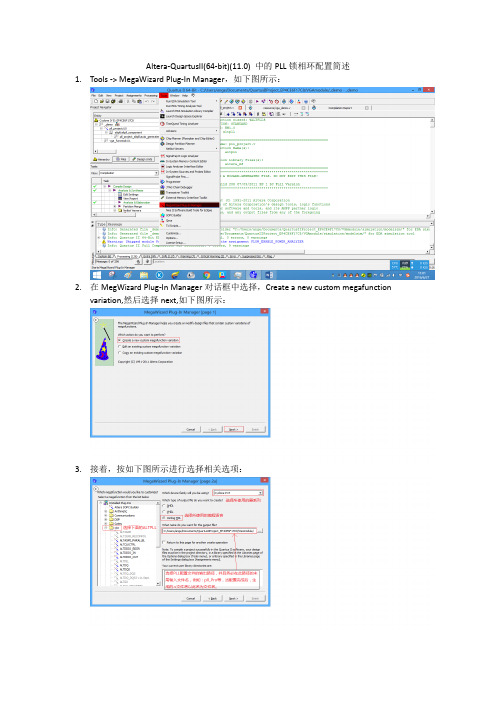

Altera-QuartusII(64-bit)(11.0)中的PLL锁相环配置简述

1.Tools ->MegaWizard Plug-In Manager,如下图所示:

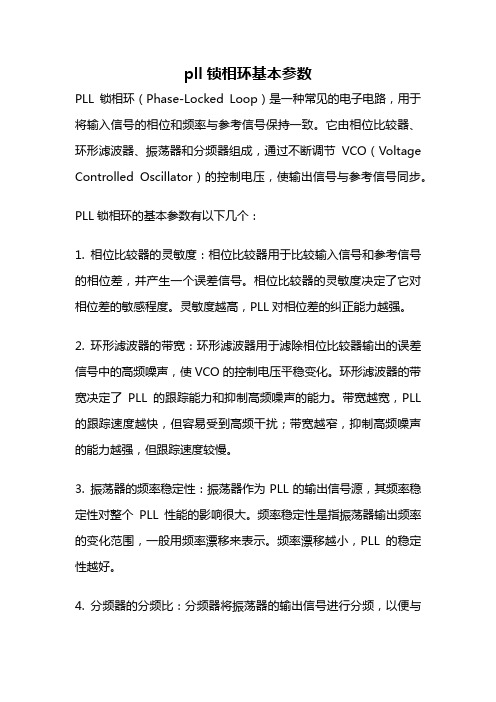

2.在MegWizard Plug-In Manager对话框中选择,Create a new custom megafunction variation,

然后选择next,如下图所示:

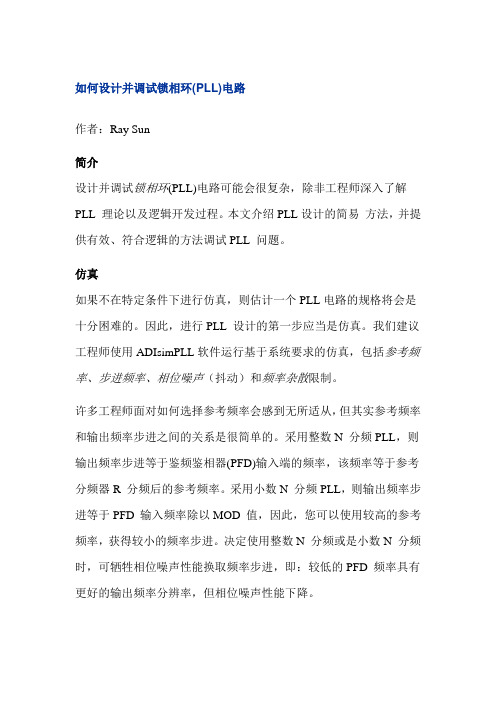

3.接着,按如下图所示进行选择相关选项:

4.此时会出现一个新的对话框,然后在新的对话框中进行如下设置:

5.接下来在Input/Lock选项页做如下设置:

6.接下来就是几个Next,相当于在第一个选项卡Parameter Settings的剩余设置全部跳过,

进入到PLL Reconfiguration也是点击Next跳过,进入到Output Clocks选项卡中进行如下设置:

7.根据需要的时钟输出个数,分别确定需要的clk的参数,设置好过后点击Next,到EDA

选项卡,点击Next到最后一个Summary选项卡,进行如下设置:

8.在新建的工程中调用它的方法与模块例化一样,亦即例化PLL模块。

说明:在工程文件

中添加以上生成的文件中的一个即可,那个文件是:pll_Pro.v,例化好了过后进行编译,通过编译过后在Project Navigator可以看到如图所示效果,说明PLL模块的配置与调用成功。

快速锁定锁相环的设计与分析

快速锁定锁相环的设计与分析一、FPLL的基本原理话说回来快速锁定锁相环(FPLL)这个家伙可不简单。

它是一种用于同步和锁定信号的电子设备,广泛应用于通信系统、雷达系统等领域。

那么FPLL到底是怎么工作的呢?咱们就来慢慢道来吧!首先我们要知道FPLL的基本原理就是利用一个环形反馈网络来实现信号的锁定。

这个环形网络由多个相位比较器和一个低通滤波器组成,其中相位比较器的作用是将输入信号与参考信号进行比较,从而得到误差信号。

然后误差信号经过低通滤波器处理后,再被送回到相位比较器中,形成一个闭环回路。

这样一来输入信号与参考信号之间的差异就会被不断修正,最终实现锁定。

说起来可能有点晦涩难懂,但是咱们可以用一个简单的例子来帮助大家理解。

假设我们有两个小朋友,小明和小红,他们想要一起做一件事情,但是他们的速度不一样。

这时候我们就可以利用FPLL来帮助他们同步。

我们先让小明跑一圈,然后让小红跑同样的距离。

接下来我们把小明跑的距离作为参考信号,然后让小红在相同的时间内跑完剩下的距离。

通过不断地比较和调整,我们就能让小明和小红的速度保持一致了。

1. 锁相环的工作原理锁相环是一种在数字通信和信号处理中常见的同步技术,其基本工作原理就是通过比较两个信号的相位差,来实现对一个信号的锁定。

听起来有点复杂?没关系咱们就把它比作是一个“手电筒”的游戏。

想象一下你有一个手电筒,上面有两个开关,一个是“开”,一个是“关”。

当你打开“开”的开关时手电筒就会发出光;而当你打开“关”的开关时手电筒就不会发光。

现在我们假设你把这个手电筒连接到一个电路上,并且在电路中加入一个噪声源。

噪声源会随机地改变“开”和“关”的状态也就是说,它会随机地让手电筒亮或灭。

那么问题来了,你怎么才能确定哪个开关对应着“亮”,哪个开关对应着“灭”呢?这就是锁相环的基本工作原理,通过不断地比较和调整,它就能锁定一个信号,使得我们能够准确地接收和处理这个信号。

这也是为什么锁相环在许多重要的领域里都有着广泛的应用,比如无线通信、雷达、GPS等等。

pll锁相环基本参数

pll锁相环基本参数PLL锁相环(Phase-Locked Loop)是一种常见的电子电路,用于将输入信号的相位和频率与参考信号保持一致。

它由相位比较器、环形滤波器、振荡器和分频器组成,通过不断调节VCO(Voltage Controlled Oscillator)的控制电压,使输出信号与参考信号同步。

PLL锁相环的基本参数有以下几个:1. 相位比较器的灵敏度:相位比较器用于比较输入信号和参考信号的相位差,并产生一个误差信号。

相位比较器的灵敏度决定了它对相位差的敏感程度。

灵敏度越高,PLL对相位差的纠正能力越强。

2. 环形滤波器的带宽:环形滤波器用于滤除相位比较器输出的误差信号中的高频噪声,使VCO的控制电压平稳变化。

环形滤波器的带宽决定了PLL的跟踪能力和抑制高频噪声的能力。

带宽越宽,PLL 的跟踪速度越快,但容易受到高频干扰;带宽越窄,抑制高频噪声的能力越强,但跟踪速度较慢。

3. 振荡器的频率稳定性:振荡器作为PLL的输出信号源,其频率稳定性对整个PLL性能的影响很大。

频率稳定性是指振荡器输出频率的变化范围,一般用频率漂移来表示。

频率漂移越小,PLL的稳定性越好。

4. 分频器的分频比:分频器将振荡器的输出信号进行分频,以便与参考信号相比较。

分频比的选择与输入信号和参考信号的频率关系密切,合适的分频比可以使PLL的锁定范围更广。

PLL锁相环在许多领域都有广泛的应用,例如通信系统、数据存储、音视频处理等。

以通信系统为例,PLL锁相环可以用于时钟恢复、频率合成和时钟同步等功能。

在时钟恢复中,输入信号经过相位比较器和环形滤波器处理后,控制VCO的输出,使其频率和相位与输入信号保持一致;在频率合成中,输入信号经过分频器和相位比较器处理后,控制VCO的输出,使其频率为输入信号的整数倍;在时钟同步中,参考信号和本地时钟通过相位比较器进行比较,通过调节VCO的控制电压,使本地时钟与参考信号同步。

除了以上基本参数外,PLL锁相环还有一些扩展参数,例如锁定时间和失锁检测等。

c语言中锁相环程序语句

c语言中锁相环程序语句摘要:C语言中锁相环程序语句概述与实例解析一、锁相环(PLL)的基本原理1.锁相环的组成2.锁相环的工作原理二、C语言中实现锁相环的程序语句1.锁相环参数设置2.锁相环初始化3.锁相环控制算法4.锁相环状态监测与调整三、实例分析1.简易锁相环电路2.基于C语言的锁相环控制程序3.程序运行效果与分析四、锁相环的应用领域及发展趋势1.锁相环在通信系统中的应用2.锁相环在控制系统中的应用3.锁相环技术的发展趋势正文:一、锁相环(PLL)的基本原理1.锁相环的组成锁相环(Phase Locked Loop,简称PLL)主要由相位比较器、放大器、滤波器和解调器等部分组成。

这些部分协同工作,实现对输入信号相位的锁定。

2.锁相环的工作原理锁相环的工作原理主要是通过相位比较器比较输入信号和本地信号的相位差,然后根据相位差的大小调整本地信号的频率,使得输入信号与本地信号的相位差逐渐减小,最终实现相位锁定。

二、C语言中实现锁相环的程序语句1.锁相环参数设置在C语言中,可以通过定义寄存器变量和设置相应的数值来配置锁相环的参数,例如:```c// 设置锁相环参数reg_lpc = 0x1234; // 设置低通滤波器参数reg_vco_ctrl = 0x5678; // 设置VCO控制参数reg_divider = 0x9ABC; // 设置分频器参数```2.锁相环初始化初始化锁相环时,需要对各个模块进行启动和设置:```c// 初始化锁相环void init_pll(){// 初始化低通滤波器lpf_init();// 初始化VCO控制模块vco_ctrl_init();// 初始化分频器divider_init();}```3.锁相环控制算法在C语言中,可以实现锁相环的控制算法,例如:```c// 更新VCO频率void update_vco_frequency(uint16_t vco_ctrl_data) {// 根据VCO控制数据更新VCO频率vco_update_frequency(vco_ctrl_data);}// 锁相环状态监测与调整void monitor_and_adjust_pll_state(){// 读取锁相环状态uint16_t pll_state = pll_read_state();// 根据状态进行调整if (pll_state == PLL_LOCKED){// 锁定状态,调整VCO频率update_vco_frequency(reg_vco_ctrl);}else if (pll_state == PLL_UNLOCKED){// 未锁定状态,启动锁相环init_pll();}}四、锁相环的应用领域及发展趋势1.锁相环在通信系统中的应用锁相环技术在通信系统中广泛应用于频率合成、本振生成、频率变换等环节,为实现系统的高稳定性和精确度提供保障。

如何设计并调试锁相环

如何设计并调试锁相环(PLL)电路作者:Ray Sun简介设计并调试锁相环(PLL)电路可能会很复杂,除非工程师深入了解PLL 理论以及逻辑开发过程。

本文介绍PLL设计的简易方法,并提供有效、符合逻辑的方法调试PLL 问题。

仿真如果不在特定条件下进行仿真,则估计一个PLL电路的规格将会是十分困难的。

因此,进行PLL 设计的第一步应当是仿真。

我们建议工程师使用 ADIsimPLL 软件运行基于系统要求的仿真,包括参考频率、步进频率、相位噪声(抖动)和频率杂散限制。

许多工程师面对如何选择参考频率会感到无所适从,但其实参考频率和输出频率步进之间的关系是很简单的。

采用整数N 分频PLL,则输出频率步进等于鉴频鉴相器(PFD)输入端的频率,该频率等于参考分频器R 分频后的参考频率。

采用小数N 分频PLL,则输出频率步进等于PFD 输入频率除以MOD 值,因此,您可以使用较高的参考频率,获得较小的频率步进。

决定使用整数N 分频或是小数N 分频时,可牺牲相位噪声性能换取频率步进,即:较低的PFD 频率具有更好的输出频率分辨率,但相位噪声性能下降。

例如,表1 显示若要求具有固定频率输出以及极大的频率步进,则应首选整数N 分频PLL(如 ADF4106),因为它具有更佳的总带内相位噪声。

相反,若要求具有较小的频率步进,则应首选小数N 分频PLL(如ADF4153),因为它的总噪声性能优于整数N 分频PLL。

相位噪声是一个基本的PLL 规格,但数据手册无法针对所有可能的应用指定性能参数。

因此,先仿真,然后进行实际硬件的测试就变得极为关键。

表1. 相位噪声确定PLL 的选择甚至在真实条件下通过ADIsimPLL 仿真PLL 电路时,结果也可能是不够的,除非真实参考以及压控振荡器(VCO)的模型文件已包含在内。

如果未包含在内,则仿真器将使用理想参考和VCO 进行仿真。

若要求高仿真精度,则花在编辑VCO 和基准电压源库文件上的时间将会是值得的。

锁相环PLL设计调试小结

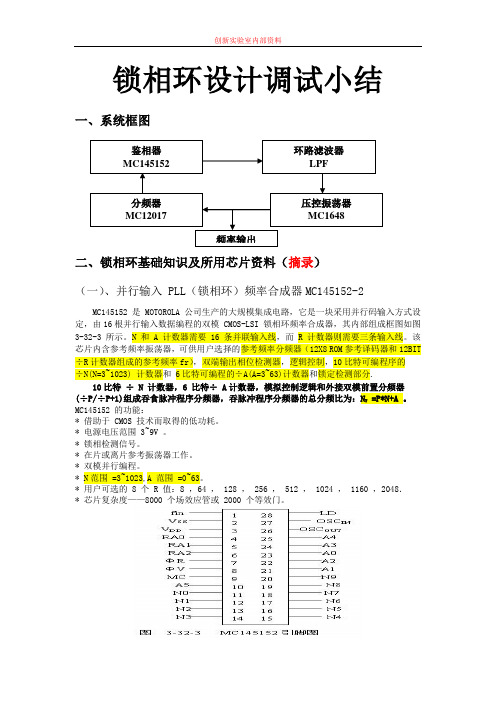

锁相环设计调试小结一、系统框图二、锁相环基础知识及所用芯片资料(摘录)(一)、并行输入 PLL (锁相环)频率合成器MC145152-2MC145152 是 MOTOROLA 公司生产的大规模集成电路,它是一块采用并行码输入方式设定,由16根并行输入数据编程的双模 CMOS-LSI 锁相环频率合成器,其内部组成框图如图 3-32-3 所示。

N 和 A 计数器需要 16 条并联输入线,而 R 计数器则需要三条输入线。

该芯片内含参考频率振荡器,可供用户选择的参考频率分频器(12X8 ROM 参考译码器和12BIT ÷R 计数器组成的参考频率fr ),双端输出相位检测器,逻辑控制,10比特可编程序的÷N(N=3~1023) 计数器和 6比特可编程的÷A(A=3~63)计数器和锁定检测部分.10比特 ÷ N 计数器,6 比特÷ A 计数器,模拟控制逻辑和外接双模前置分频器(÷P /÷P +1)组成吞食脉冲程序分频器,吞脉冲程序分频器的总分频比为:N T =P*N+A 。

MC145152 的功能:* 借助于 CMOS 技术而取得的低功耗。

* 电源电压范围 3~9V 。

* 锁相检测信号。

* 在片或离片参考振荡器工作。

* 双模并行编程。

* N 范围 =3~1023,A 范围 =0~63。

*用户可选的 8 个 R 值:8 ,64 , 128 , 256 , 512 , 1024 , 1160 ,2048. * 芯片复杂度——8000 个场效应管或 2000 个等效门。

鉴相器MC145152 环路滤波器 LPF压控振荡器 MC1648分频器MC12017频率输出引脚说明:N0-N9 (11-20 ):÷ N 计数器的编程输入端。

当÷ N 计数器的计数为0 时,这N个输入供给预置÷ N 计数器的数据。

N0 为最低位,N9 为最高位。

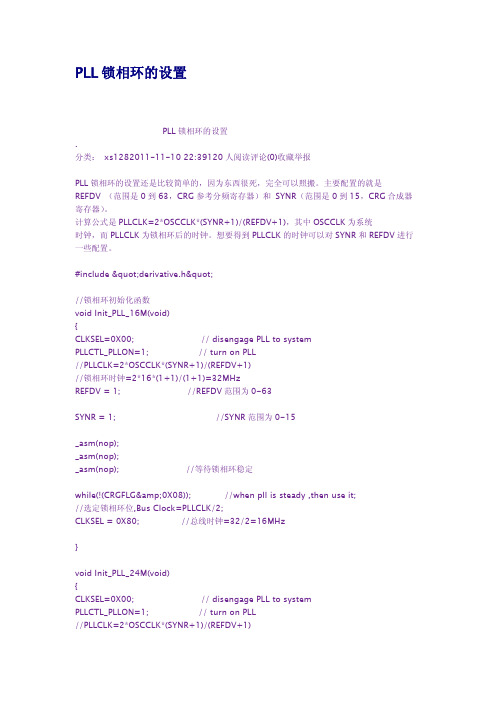

PLL锁相环的设置

PLL锁相环的设置PLL锁相环的设置.分类:xs1282011-11-1022:39120人阅读评论(0)收藏举报PLL锁相环的设置还是比较简单的,因为东西很死,完全可以照搬。

主要配置的就是REFDV(范围是0到63,CRG参考分频寄存器)和SYNR(范围是0到15,CRG合成器寄存器)。

计算公式是PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1),其中OSCCLK为系统时钟,而PLLCLK为锁相环后的时钟。

想要得到PLLCLK的时钟可以对SYNR和REFDV进行一些配置。

#include"derivative.h"//锁相环初始化函数void Init_PLL_16M(void){CLKSEL=0X00;//disengage PLL to systemPLLCTL_PLLON=1;//turn on PLL//PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)//锁相环时钟=2*16*(1+1)/(1+1)=32MHzREFDV=1;//REFDV范围为0~63SYNR=1;//SYNR范围为0~15_asm(nop);_asm(nop);_asm(nop);//等待锁相环稳定while(!(CRGFLG&0X08));//when pll is steady,then use it;//选定锁相环位,Bus Clock=PLLCLK/2;CLKSEL=0X80;//总线时钟=32/2=16MHz}void Init_PLL_24M(void){CLKSEL=0X00;//disengage PLL to systemPLLCTL_PLLON=1;//turn on PLL//PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)REFDV=1;//REFDV范围为0~63SYNR=2;//SYNR范围为0~15_asm(nop);_asm(nop);_asm(nop);//等待锁相环稳定while(!(CRGFLG&0X08));//when pll is steady,then use it; //选定锁相环位,Bus Clock=PLLCLK/2;CLKSEL=0X80;//总线时钟=48/2=24MHz}void Init_PLL_32M(void){CLKSEL=0X00;//disengage PLL to system PLLCTL_PLLON=1;//turn on PLL//PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)//锁相环时钟=2*16*(3+1)/(1+1)=64MHzREFDV=1;//REFDV范围为0~63SYNR=3;//SYNR范围为0~15_asm(nop);_asm(nop);_asm(nop);//等待锁相环稳定while(!(CRGFLG&0X08));//when pll is steady,then use it; //选定锁相环位,Bus Clock=PLLCLK/2;CLKSEL=0X80;//总线时钟=64/2=32MHz}void Init_PLL_48M(void){CLKSEL=0X00;//disengage PLL to system PLLCTL_PLLON=1;//turn on PLL//PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)REFDV=1;//REFDV范围为0~63SYNR=5;//SYNR范围为0~15_asm(nop);_asm(nop);_asm(nop);//等待锁相环稳定while(!(CRGFLG&0X08));//when pll is steady,then use it; //选定锁相环位,Bus Clock=PLLCLK/2;CLKSEL=0X80;//总线时钟=96/2=48MHz}void Init_PLL_64M(void){CLKSEL=0X00;//disengage PLL to system PLLCTL_PLLON=1;//turn on PLL//PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)//锁相环时钟=2*16*(7+1)/(1+1)=128MHzREFDV=1;//REFDV范围为0~63SYNR=7;//SYNR范围为0~15_asm(nop);_asm(nop);_asm(nop);//等待锁相环稳定while(!(CRGFLG&0X08));//when pll is steady,then use it; //选定锁相环位,Bus Clock=PLLCLK/2;CLKSEL=0X80;//总线时钟=48/2=64MHz}void Init_PLL_72M(void){CLKSEL=0X00;//disengage PLL to system PLLCTL_PLLON=1;//turn on PLL//PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)//锁相环时钟=2*16*(8+1)/(1+1)=144MHzREFDV=1;//REFDV范围为0~63SYNR=8;//SYNR范围为0~15_asm(nop);_asm(nop);_asm(nop);//等待锁相环稳定while(!(CRGFLG&0X08));//when pll is steady,then use it; //选定锁相环位,Bus Clock=PLLCLK/2;CLKSEL=0X80;//总线时钟=144/2=72MHz}void Init_PLL_80M(void){CLKSEL=0X00;//disengage PLL to system PLLCTL_PLLON=1;//turn on PLL//PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)//锁相环时钟=2*16*(9+1)/(1+1)=160MHzREFDV=1;//REFDV范围为0~63SYNR=9;//SYNR范围为0~15_asm(nop);_asm(nop);_asm(nop);//等待锁相环稳定while(!(CRGFLG&0X08));//when pll is steady,then use it; //选定锁相环位,Bus Clock=PLLCLK/2;CLKSEL=0X80;//总线时钟=160/2=80MHz}void Init_PLL_88M(void){CLKSEL=0X00;//disengage PLL to system PLLCTL_PLLON=1;//turn on PLL//PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)//锁相环时钟=2*16*(10+1)/(1+1)=176MHzREFDV=1;//REFDV范围为0~63SYNR=10;//SYNR范围为0~15_asm(nop);_asm(nop);_asm(nop);//等待锁相环稳定while(!(CRGFLG&0X08));//when pll is steady,then use it; //选定锁相环位,Bus Clock=PLLCLK/2;CLKSEL=0X80;//总线时钟=176/2=88MHz}void Init_PLL_96M(void){CLKSEL=0X00;//disengage PLL to system PLLCTL_PLLON=1;//turn on PLL//PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)//锁相环时钟=2*16*(11+1)/(1+1)=192MHzREFDV=1;//REFDV范围为0~63SYNR=11;//SYNR范围为0~15_asm(nop);_asm(nop);_asm(nop);//等待锁相环稳定while(!(CRGFLG&0X08));//when pll is steady,then use it; //选定锁相环位,Bus Clock=PLLCLK/2;CLKSEL=0X80;//总线时钟=192/2=96MHz}void Init_PLL_104M(void){CLKSEL=0X00;//disengage PLL to system PLLCTL_PLLON=1;//turn on PLL//PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)//锁相环时钟=2*16*(12+1)/(1+1)=208MHzREFDV=1;//REFDV范围为0~63SYNR=12;//SYNR范围为0~15_asm(nop);_asm(nop);_asm(nop);//等待锁相环稳定while(!(CRGFLG&0X08));//when pll is steady,then use it;//选定锁相环位,Bus Clock=PLLCLK/2;CLKSEL=0X80;//总线时钟=208/2=104MHz}void Init_PLL_120M(void){CLKSEL=0X00;//disengage PLL to system PLLCTL_PLLON=1;//turn on PLL//PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)//锁相环时钟=2*16*(14+1)/(1+1)=240MHzREFDV=1;//REFDV范围为0~63SYNR=14;//SYNR范围为0~15_asm(nop);_asm(nop);_asm(nop);//等待锁相环稳定while(!(CRGFLG&0X08));//when pll is steady,then use it; //选定锁相环位,Bus Clock=PLLCLK/2;CLKSEL=0X80;//总线时钟=240/2=120MHz}。

EDA技术-VHDL-5.13嵌入式锁相环PLL应用实验

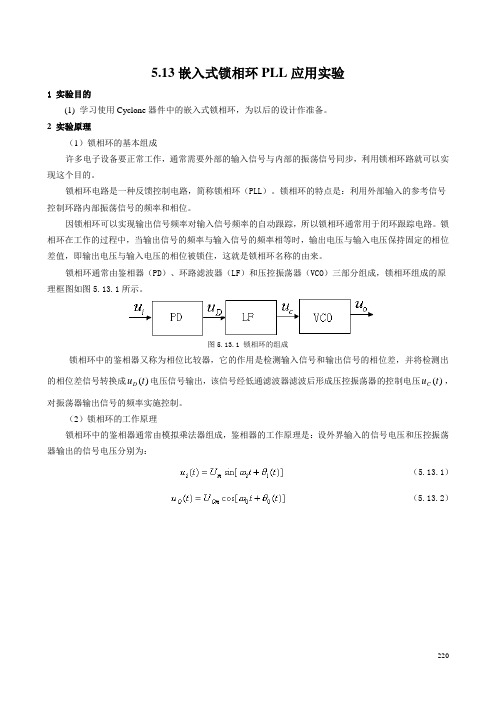

2205.13嵌入式锁相环PLL 应用实验1 实验目的(1) 学习使用Cyclone 器件中的嵌入式锁相环,为以后的设计作准备。

2 实验原理(1)锁相环的基本组成许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环电路是一种反馈控制电路,简称锁相环(PLL )。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

锁相环通常由鉴相器(PD )、环路滤波器(LF )和压控振荡器(VCO )三部分组成,锁相环组成的原理框图如图5.13.1所示。

图5.13.1 锁相环的组成锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成)(t u D 电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压)(t u C ,对振荡器输出信号的频率实施控制。

(2)锁相环的工作原理锁相环中的鉴相器通常由模拟乘法器组成,鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为:(5.13.1)(5.13.2)221式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。

则模拟乘法器的输出电压D u 为:(5.13.3)用低通滤波器LF 将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压)(t u C 。

即)(t u C 为:(5.13.4)式中的i ω为输入信号的瞬时振荡角频率,)(t i θ和)(0t θ分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为:即(5.13.5)则,瞬时相位差D θ为:(5.13.6) 对两边求微分,可得频差的关系式为(5.13.7)上式等于零,说明锁相环进入相位锁定的状态,此时输出和输入信号的频率和相位保持恒定不变的状态,)(t u C 为恒定值。

PLL(锁相环)电路原理及设计 [收藏]

![PLL(锁相环)电路原理及设计 [收藏]](https://img.taocdn.com/s3/m/ca8d027601f69e3143329497.png)

PLL(锁相环)电路原理及设计[收藏]PLL(锁相环)电路原理及设计在通信机等所使用的振荡电路,其所要求的频率范围要广,且频率的稳定度要高。

无论多好的LC振荡电路,其频率的稳定度,都无法与晶体振荡电路比较。

但是,晶体振荡器除了可以使用数字电路分频以外,其频率几乎无法改变。

如果采用PLL(锁相环)(相位锁栓回路,PhaseLockedLoop)技术,除了可以得到较广的振荡频率范围以外,其频率的稳定度也很高。

此一技术常使用于收音机,电视机的调谐电路上,以及CD唱盘上的电路。

一PLL(锁相环)电路的基本构成PLL(锁相环)电路的概要图1所示的为PLL(锁相环)电路的基本方块图。

此所使用的基准信号为稳定度很高的晶体振荡电路信号。

此一电路的中心为相位此较器。

相位比较器可以将基准信号与VCO (Voltage Controlled Oscillator……电压控制振荡器)的相位比较。

如果此两个信号之间有相位差存在时,便会产生相位误差信号输出。

(将VCO的振荡频率与基准频率比较,利用反馈电路的控制,使两者的频率为一致。

)利用此一误差信号,可以控制VCO的振荡频率,使VCO的相位与基准信号的相位(也即是频率)成为一致。

PLL(锁相环)可以使高频率振荡器的频率与基准频率的整数倍的频率相一致。

由于,基准振荡器大多为使用晶体振荡器,因此,高频率振荡器的频率稳定度可以与晶体振荡器相比美。

只要是基准频率的整数倍,便可以得到各种频率的输出。

从图1的PLL(锁相环)基本构成中,可以知道其是由VCO,相位比较器,基准频率振荡器,回路滤波器所构成。

在此,假设基准振荡器的频率为fr,VCO的频率为fo。

在此一电路中,假设frgt;fo时,也即是VC0的振荡频率fo比fr低时。

此时的相位比较器的输出PD 会如图2所示,产生正脉波信号,使VCO的振荡器频率提高。

相反地,如果frlt;fo时,会产生负脉波信号。

(此为利用脉波的边缘做二个信号的比较。

【原创】锁相环PLL制作与调试要点

一、MC145152(鉴相器)MC145152-2 芯片是摩托罗拉公司生产的锁相环频率合成器专用芯片。

它是 MC145152-1 芯片的改进型。

主要具有下列主要特征:(1)它与双模(P/(P+1))分频器同时使用,有一路双模分频控制输出 MC。

当 MC 为低电平时,双模分频器用(P+1)去除;当 MC 为高电平时,双模分频器用模数 P 去除。

(2)它有 A 计数器和 N 计数器两个计数器。

它们与双模(P/(P+1))分频器提供了总分频值(NP+A)。

其中,A、N 计数器可预置。

N 的取值范围为 3~1023,A 的取值范围为 0~63。

A 计数器计数期间,MC 为低电平;N 计数器计数(N-A)期间,MC 为高电平。

(3)它有一个参考振荡器,可外接晶体振荡器。

(4)它有一个R计数器,用来给参考振荡器分频,R计数器可预置,R的取值范围:8,64,128,256,512,1024,1160,2048。

设置方法通过改变RA0、RA1、RA2的不同电平,接下来会讲到。

(5)它有两路鉴相信号输出,其中,ФR、ФV 用来输出鉴相误差信号,LD 用来输出相位锁定信号。

MC145152-2 的供电电压为 3.0 V~9.0 V,采用 28 脚双列封装形式。

MC145152-2的原理框图如图 1 所示MC145152-2 的工作原理:参考振荡器信号经 R 分频器分频后形成 fR 信号。

压控振荡器信号经双模P/(P +1)分频器分频,再经 A、N 计数器分频器后形成 fV 信号,fV=fVCO/(NP+A)。

fR 信号和 fV 信号在鉴相器中鉴相,输出的误差信号(φR、φV)经低通滤波器形成直流信号,直流信号再去控制压控振荡器的频率。

当整个环路锁定后,fV=fR 且同相,fVCO=(NP+A)fV=(NP+A)fR,便可产生和基准频率同样稳定度和准确度的任意频率。

原理框图如右图:管脚描述:Pin 1频率输入 (fin) 输入到上升沿触发÷N和÷A计数器。

锁相环路(PLL)电路设计实例

软件实现PLL的代码示例

01

```systemverilog

02

// 定义PLL模块

03

module pll(input wire clk_in, output reg clk_out);

软件实现PLL的代码示例

01

parameter FREF = 100e3; // 参考频率

02

parameter N = 10; // 分频比

相位保持一致。

电荷泵型PLL的电路实现

电荷泵由两个开关和两个电容 组成,一个开关用于充电,另

一个用于放电。

当输入信号与VCO输出信号 的相位存在误差时,电荷泵 的开关会根据误差信号的极 性进行切换,从而在电容上

积累或释放电荷。

电容上的电荷量会转换为电压 信号,该电压信号通过低通滤 波器平滑后,用于调整VCO的

频率。

电荷泵型PLL的性能分析

01

电荷泵型PLL具有较高的带宽和较快的响应速度,因此适用于高 速数据传输和无线通信等应用。

02

由于电荷泵型PLL采用电荷传输方式,因此对电源噪声和电磁干

扰较为敏感,需要采取相应的措施进行抑制。

电荷泵型PLL的另一个优点是易于集成,因此适合于大规模生产

03

和应用。

04

软件实现PLL的代码示例

assign clk_out = div_by_n;

always @(posedge clk_in) begin phase_error <= #1 ($posedge clk_in ? 32'hFFFFFFFF : phase_error 1);

软件实现PLL的代码示例

PLL电路设计实例:模拟型 PLL

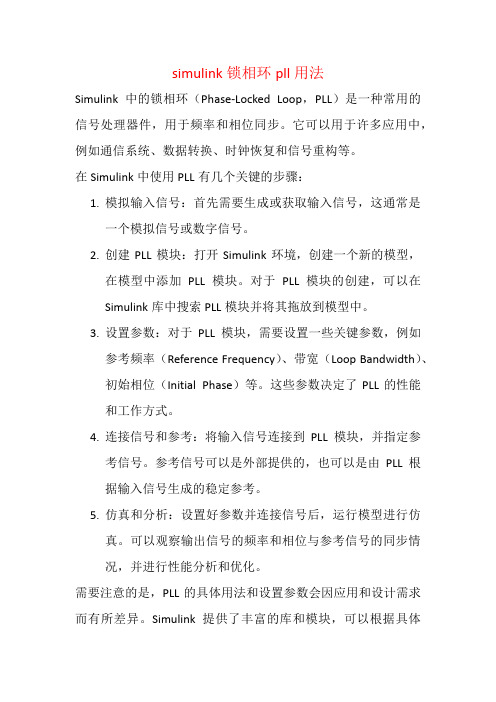

simulink锁相环pll用法

simulink锁相环pll用法

Simulink中的锁相环(Phase-Locked Loop,PLL)是一种常用的信号处理器件,用于频率和相位同步。

它可以用于许多应用中,例如通信系统、数据转换、时钟恢复和信号重构等。

在Simulink中使用PLL有几个关键的步骤:

1.模拟输入信号:首先需要生成或获取输入信号,这通常是

一个模拟信号或数字信号。

2.创建PLL模块:打开Simulink环境,创建一个新的模型,

在模型中添加PLL模块。

对于PLL模块的创建,可以在

Simulink库中搜索PLL模块并将其拖放到模型中。

3.设置参数:对于PLL模块,需要设置一些关键参数,例如

参考频率(Reference Frequency)、带宽(Loop Bandwidth)、初始相位(Initial Phase)等。

这些参数决定了PLL的性能

和工作方式。

4.连接信号和参考:将输入信号连接到PLL模块,并指定参

考信号。

参考信号可以是外部提供的,也可以是由PLL根

据输入信号生成的稳定参考。

5.仿真和分析:设置好参数并连接信号后,运行模型进行仿

真。

可以观察输出信号的频率和相位与参考信号的同步情

况,并进行性能分析和优化。

需要注意的是,PLL的具体用法和设置参数会因应用和设计需求而有所差异。

Simulink提供了丰富的库和模块,可以根据具体

应用需求选择和配置适当的PLL模块。

还可以通过自定义模块或编写MATLAB脚本来实现更高级的PLL功能。

pll的参数

PLL的参数介绍相位锁定环(Phase-Locked Loop,简称PLL)是一种广泛应用于通信、控制系统中的电路。

它可以将输入信号的相位和频率调整到与参考信号相匹配,实现信号的同步和频率转换。

PLL的参数设置对于系统的性能和稳定性至关重要。

本文将介绍PLL的参数及其影响,并提供一些常见的设置方法和技巧。

1. 相位检测器参数相位检测器(Phase Detector,简称PD)用于比较输入信号和参考信号的相位差,并产生控制信号。

常见的相位检测器包括边沿触发相位检测器(Edge-Triggered Phase Detector,简称ETPD)和恒幅相位检测器(Amplitude-Insensitive Phase Detector,简称AIPD)。

以下是一些常见的相位检测器参数:1.1 灵敏度相位检测器的灵敏度决定了它对相位差的响应程度。

灵敏度越高,相位检测器对相位差的响应越快。

然而,过高的灵敏度可能导致相位锁定环的震荡和不稳定。

因此,在实际应用中需要根据系统的要求和稳定性进行合适的调整。

1.2 噪声抑制比噪声抑制比是相位检测器抑制输入信号中的噪声的能力。

较高的噪声抑制比可以提高系统的抗噪性能。

一些常见的提高噪声抑制比的方法包括使用滤波器和引入环路滤波器。

2. 频率控制电压参数频率控制电压(Voltage Controlled Oscillator,简称VCO)是PLL中的一个关键部件,它通过控制输入信号的频率来实现与参考信号的同步。

以下是一些常见的VCO参数:2.1 频率范围频率范围是VCO可以工作的频率范围。

在选择VCO时,需要根据系统的要求和应用场景来确定合适的频率范围。

2.2 频率线性度频率线性度是指VCO输出频率与控制电压之间的线性关系。

较好的频率线性度可以提高PLL的性能和稳定性。

3. 倍频器参数倍频器(Multiplier)用于将VCO输出的频率倍增到所需的频率。

以下是一些常见的倍频器参数:3.1 倍频比倍频比是指倍频器将输入频率乘以的倍数。

PLL的详细使用

什么是锁相环呢?MCU的支撑电路一般需要外部时钟来给MCU提供时钟信号,而外部时钟的频率可能偏低,为了使系统更加快速稳定运行,需要提升系统所需要的时钟频率。

这就得用到锁相环了。

例如MCU用的外部晶振是16M的无源晶振,则可以通过锁相环PLL把系统时钟倍频到24M,从而给系统提供更高的时钟信号,提高程序的运行速度。

51单片机,A VR单片机内部没有锁相环电路,其系统时钟直接由外部晶振提供。

而XS128内部集成了锁相环电路,其系统时钟既可由外部晶振直接提供,也可以通过锁相环倍频后提供,当然,还有由XS128内部的时钟电路来提供(当其它来源提供的系统时钟不稳定时,内部时钟电路就起作用了,也就是自时钟模式)。

锁相环作为一个提供系统时钟的模块,是一个基本的模块,几乎每次编程序都得用到。

下面记一下怎样配置锁相环来设定想要的系统时钟。

锁相环PLL、自时钟模式和前面说的实时中断RTI、看门狗COP都属于系统时钟与复位CRG中的模块,固前面用到的寄存器,这里有些会再用到。

在程序中配置锁相环的步骤如下:第一、禁止总中断;第二、寄存器CLKSEL的第七位置0,即CLKSEL_PLLSEL=0。

选择时钟源为外部晶振OSCCLK,在PLL程序执行前,内部总线频率为OSCCLK/2。

CLKSEL_PLLSEL=0时,系统时钟由外部晶振直接提供,系统内部总线频率=OSCCLK/2(OSCCLK为外部晶振频率)。

CLKSEL_PLLSEL=1时,系统时钟由锁相环提供,此时系统内部总线频率=PLLCLK/2 (PLLCLK为锁相环倍频后的频率)。

第三、禁止锁相环PLL,即PLLCTL_PLLON=0。

当PLLCTL_PLLON=0时,关闭PLL电路。

当PLLCTL_PLLON=1时,打开PLL电路。

第四、根据想要的时钟频率设置SYNR和REFDV两个寄存器。

SYNR和REFDV两个寄存器专用于锁相环时钟PLLCLK的频率计算,计算公式是:PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1) 其中,PLLCLK为PLL模块输出的时钟频率;OSCCLK为晶振频率;SYNR、REFDV分别为寄存器SYNR、REFDV中的值。

锁相环调试流程

锁相环调试流程锁相环(Phase-Locked Loop,简称PLL)是一种用于提供稳定的时钟和频率的电路。

在电子系统中,锁相环常用于时钟恢复、频率合成、时钟同步等应用场景。

为了确保锁相环正常工作,需要进行调试和优化。

本文将详细介绍锁相环调试的流程和步骤。

1. 确定基本参数在进行锁相环调试之前,首先需要确定一些基本参数,包括输入信号频率范围、输出信号频率范围、参考时钟频率等。

这些参数将决定锁相环的设计和优化方向。

2. 设计锁相环电路根据确定的基本参数,设计锁相环电路。

常见的锁相环电路包括比例积分器(PI)控制器、低通滤波器、振荡器等模块。

根据具体应用需求,还可以添加其他功能模块。

3. 搭建实验平台准备好所需的硬件设备和软件工具,并搭建实验平台。

硬件设备包括信号发生器、示波器、频谱分析仪等仪器;软件工具包括仿真软件和调试工具。

4. 初步测试将锁相环电路连接到实验平台上,进行初步测试。

输入一个稳定的参考时钟信号,观察输出信号的频率和相位。

如果输出信号与预期不符,需要检查电路连接是否正确,并调整基本参数。

5. 稳定性分析通过改变输入信号的频率和幅度,观察锁相环的稳定性。

稳定性分析可以通过观察输出信号的抖动情况来评估。

如果抖动较大或频率范围不稳定,可能需要调整锁相环参数或改进电路设计。

6. 频率合成和时钟恢复测试根据锁相环的具体应用场景,进行频率合成和时钟恢复的测试。

对于频率合成,输入一个参考时钟信号,并观察输出信号的频率和相位;对于时钟恢复,输入一个失真或噪声较大的时钟信号,并观察输出信号是否能够恢复为稳定的时钟。

7. 相位裕度测量在某些应用场景下,锁相环需要具有一定的相位裕度。

通过改变输入信号的相位,并观察输出信号与输入信号之间的相位差来评估相位裕度。

如果相位差超过预期范围,可能需要调整锁相环参数或改进电路设计。

8. 参数优化根据测试结果,对锁相环的参数进行优化。

常见的优化方法包括调整比例积分器(PI)控制器的参数、改变低通滤波器的截止频率等。

【原创】锁相环PLL制作与调试要点.

基于MC145152+MC12022+MC1648L+LM358 的锁相环电路一、MC145152(鉴相器)MC145152-2 芯片是摩托罗拉公司生产的锁相环频率合成器专用芯片。

它是MC145152-1 芯片的改进型。

主要具有下列主要特征:(1)它与双模(P/(P+1))分频器同时使用,有一路双模分频控制输出MC。

当MC 为低电平时,双模分频器用(P+1)去除;当MC 为高电平时,双模分频器用模数P 去除。

(2)它有 A 计数器和N 计数器两个计数器。

它们与双模(P/(P+1))分频器提供了总分频值(NP+A)。

其中,A、N 计数器可预置。

N 的取值范围为3~1023,A 的取值范围为0~63。

A 计数器计数期间,MC 为低电平;N 计数器计数(N-A)期间,MC 为高电平。

(3)它有一个参考振荡器,可外接晶体振荡器。

(4)它有一个R计数器,用来给参考振荡器分频,R计数器可预置,R的取值范围:8,64,128,256,512,1024,1160,2048。

设置方法通过改变RA0、RA1、RA2的不同电平,接下来会讲到。

(5)它有两路鉴相信号输出,其中,ФR、ФV 用来输出鉴相误差信号,LD 用来输出相位锁定信号。

MC145152-2 的供电电压为3.0 V~9.0 V,采用28 脚双列封装形式。

MC145152-2的原理框图如图1 所示MC145152-2 的工作原理:参考振荡器信号经R 分频器分频后形成fR 信号。

压控振荡器信号经双模P/(P+1)分频器分频,再经A、N 计数器分频器后形成fV 信号,fV=fVCO/(NP+A)。

fR 信号和fV 信号在鉴相器中鉴相,输出的误差信号(φR、φV)经低通滤波器形成直流信号,直流信号再去控制压控振荡器的频率。

当整个环路锁定后,fV=fR 且同相,fVCO=(NP+A)fV=(NP+A)fR,便可产生和基准频率同样稳定度和准确度的任意频率。

原理框图如右图:管脚描述:Pin 1频率输入(fin) 输入到上升沿触发÷N和÷A计数器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

//锁相环时钟=2*16*(1+1)/(1+1)=32MHz

_asm(nop);

_asm(nop); //等待锁相环稳定

while(!(CRGFLG&0X08)); //when pll is steady ,then use it;

//选定锁相环位,Bus Clock=PLLCLK/2;

CLKSEL = 0X80; //总线时钟=32/2=16MHz

}

void Init_PLL_24M(void)

{

CLKSEL=0X00; // disengage PLL to system

CLKSEL = 0X80; //总线时钟=48/2=64MHz

}

void Init_PLL_72M(void)

{

CLKSEL=0X00; // disengage PLL to system

REFDV = 1; //REFDV范围为0~63

SYNR = 1; //SYNR范围为0~15

_asm(nop);

_asm(nop);

REFDV = 1; //REFDV范围为0~63

SYNR = 3; //SYNR范围为0~15

_asm(nop);

_asm(nop); //等待锁相环稳定

while(!(CRGFLG&0X08)); //when pll is steady ,then use it;

//选定锁相环位,Bus Clock=PLLCLK/2;

_asm(nop);

_asm(nop); //等待锁相环稳定

while(!(CRGFLG&0X08)); //when pll is steady ,then use it;

//选定锁相环位,Bus Clock=PLLCLK/2;

CLKSEL = 0X80; //总线时钟=48/2=24MHz

}

void Init_PLL_32M(void)

{

CLKSEL=0X00; // disengage PLL to system

CLKSEL = 0X80; //总线时钟=96/2=48MHz

}

void Init_PLL_64M(void)

{

CLKSEL=0X00; // disengage PLL to system

REFDV = 1; //REFDV范围为0~63

SYNR = 7; //SYNR范围为0~15

_asm(nop);

void Init_PLL_16M(void)

{

CLKSEL=0X00; // disengage PLL to system

PLLCTL_PLLON=1; // turn on PLL

PLL锁相环的设置

.

分类: xs1282011-11-10 22:39120人阅读评论(0)收藏举报

PLL锁相环的设置还是比较简单的,因为东西很死,完全可以照搬。主要配置的就是

REFDV (范围是0到63,CRG参考分频寄存器)和 SYNR(范围是0到15,CRG合成器

寄存器)。

PLLCTL_PLLON=1; // turn on PLL

//PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)

//锁相环时钟=2*16*(3+1)/(1+1)=64MHz

PLLCTL_PLLON=1; // turn on PLL

//PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)

//锁相环时钟=2*16*(8+1)/(1+1)=144MHz

REFDV = 1; //REFDV范围为0~63

SYNR = 5; //SYNR范围为0~15

_asm(nop);

_asm(nop);

_asm(nop); //等待锁相环稳定

while(!(CRGFLG&0X08)); //when pll is steady ,then use it;

//选定锁相环位,Bus Clock=PLLCLK/2;

PLLCTL_PLLON=1; // turn on PLL

//PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)

//锁相环时钟=2*16*(2+1)/(1+1)=48MHz

CLKSEL = 0X80; //总线时钟=144/2=72MHz

}

void Init_PLL_80M(void)

{

CLKSEL=0X00; // disengage PLL to system

_asm(nop);

_asm(nop); //等待锁相环稳定

while(!(CRGFLG&0X08)); //when pll is steady ,then use it;

//选定锁相环位,Bus Clock=PLLCLK/2;

REFDV = 1; //REFDV范围为0~63

SYNR = 2; //SYNR范围为0~15

_asm(nop);

_asm(nop);

PLLCTL_PLLON=1; // turn on PLL

//PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)

//锁相环时钟=2*16*(5+1)/(1+1)=96MHz

REFDV = 1; //REFDV范围为0~63

SYNR = 8; //SYNR范围为0~15

_asm(nop);

_asm(nop); //等待锁相环稳定

while(!(CRGFLG&0X08)); //when pll is steady ,then use it;

//选定锁相环位,Bus Clock=PLLCLK/2;

PLLCTL_PLLON=1; // turn on PLL

//PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)

//锁相环时钟=2*16*(7+1)/(1+1)=128MHz

Байду номын сангаас CLKSEL = 0X80; //总线时钟=64/2=32MHz

}

void Init_PLL_48M(void)

{

CLKSEL=0X00; // disengage PLL to system

计算公式是PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1),其中OSCCLK为系统

时钟,而PLLCLK为锁相环后的时钟。想要得到PLLCLK的时钟可以对SYNR和REFDV进行

一些配置。

#include "derivative.h"

//锁相环初始化函数