双极型模拟集成电路

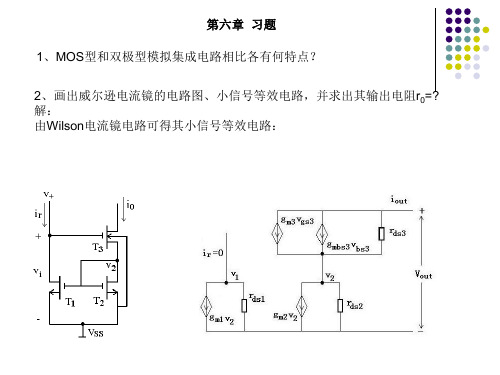

第六章习题解答

g m1 g m3 gm2

rds1

rds3

g m rds1 rds3 设g m1 g m2 g m3 g m

3 、 已 知 如 下 图 所 示 运 放 , 其 中 MOS 管 器 件 参 数 : Kn=25A/V2,Kp=10A/V2, n=p==0.04V-1, 则:

(1)、根据图中所示电路结构判断宜选N阱还是P阱工艺实现集成?简述理由。 (2)、若VDD=5V,VSS=-5V,求运放的静态功耗Pdiss和小信号电压增益AV(忽略 输出级产生的负载)。

gds5 p Ids5 0.04 40 1.6S

g ds8 n I ds8 0.04 40 1.6S

将以上各值代入增益表达式中,可求出该电路小 信号增益:

Av

109.5 74.8 2.4 2 1.6 2

533.2

解:

(1) 应采用P阱CMOS工艺。理由: 由电路拓扑可知,该电路为无缓冲二级放大器,差分放大器作输入级,为消除

输入NMOS管的衬底偏置效应导致的阈值电压漂移,应使其VBS=0。如将NMOS管 做在p型衬底上,则衬底必须接最低电位Vss,而NMOS差分对的共同源端电位至少 比Vss高一个饱和压降Vdsat7,必有VBS<0,显然有衬偏效应。因此应考虑将NMOS 差分对做在P阱中,利用阱的电位浮动技术,将其B、S短接,确保VBS=0。

Av

gm2 gds2 gds4

gm5 gds8 gds5

gm2

2 W L

2

kn

I ds2

ห้องสมุดไป่ตู้

2 4 25 60 109.5S

gm5

2

W L

5

k

p

I ds5

2 7 10 40 74.8S

第六章 模拟集成电路84751

1= 2 = ,

r r r be1= be2 = be,

IbQ1= IbQ2,

IcQ1= IcQ2,

Ube1= Ube2,

Uc1= Uc2,

信号输入方式

双端输入:输入信号接在两个输入端间

单端输入:输入信号接在一个输入端与地间,另一端接地

差放输出方式

双端输出(平衡输出):输出取自两个集电极之间

单端输出(不平衡输出):输出取自一个集电极与地间

共模信号:

是指在差放两个输

入端接入两个幅度

相等、极性相同的

信号, 记为:

Uic1 ,Uic2

Uic1 = Uic2 = Uic

Ie1

Ie2

图6-10(a)共模电路

1 共模电压增益Auc

双端输出时,由于电路对称,

AUc Uoc Uic

(Uoc1

Uoc2 ) Uic

0

单端输出时,

图6-10 (b)共模输入等效电路

Uo

2 差模输入电阻 rid

不论单端输入还是双端输入,

rid均为基本放大电路的两倍

r id U idIid 2 (R b h i) e

3 差模输出电阻rod

双端输出时, rod =2Rc//(2 /hoe) 当1/ hoe >>Rc时,rod 2Rc

图6-8(b)差模输入等效电路

(三)对共模信号的抑制作用

Ic1 Ie1 Ie1s Se1 1 Ic2 Ie2 Ies2 Se2 2 IoIc22Ic12Ir

图6-20(b) 比例恒流源

(三)微电流源(Wildar电流源)

U b1eU b2 eIe2R2

U b1eU Tln Ie1(/Ie1 s)

集成电路中的双极性和CMOS工艺

集成电路是将多个器件及其之间的连线制作在同一个 基片上,使器件结构和分立元件有所不同,即产生寄生的 有源器件和无源器件。寄生效应对电路的性能有一定的影 响,下图是做在一个基片上的两个双极性晶体管,它们之 间会相互影响,因此各个元件之间的隔离是集成电路中必 须考虑的问题。

(3)集成电路中进行隔离的方法

N阱光刻:

涂胶 光源

腌膜对准

曝光

显影

刻蚀(等离子体刻蚀)

去胶

N阱掺杂:

P+

N-well

P掺杂(离子注入)

去除氧化膜

3、光刻2---有源区光刻

N-well

SiO2隔离岛

N-well

N+ P-Si

N+

P+

N-well

P+

淀积二氧化硅与氮化硅 光刻有源区 场区氧化 去除有源区的氮化硅与二氧化硅

E P+ n+

B

C

S

C

B

E

n+

p

n+

n

n+ P+ n+

n

p

n+

P+

P-Si

二、双极性工艺流程

典型的pn结隔离工艺是实现集成电路制造的最 原始工艺,迄今为止产生的双极型集成电路制造 工艺都是在此基础上为达到特定的目的增加适当 的工序来完成的。这里以pn结隔离的npn晶体管的 形成过程为例,介绍双极型集成电路的制造工艺。

在光刻接触孔后,若 采用金属铝作为电极引 线,则需要进行铝的淀 积。

9:第六次光刻----反刻铝

此次反刻的目的是 在不需要铝线的地方 将上步工艺中淀积的 铝刻蚀掉。

双极型集成电路器件具有速度高、驱动 能力强、模拟精度高的特点,但是随着集 成电路发展到系统级的集成,其规模越来 越大,却要求电路的功耗减少,而双极型 器件在功耗和集成度方面无法满足这些方 面的要求。CMOS电路具有功耗低、集成度 高和抗干扰能力强的特点,下面就对CMOS 进行简要讲解。

集成电路的分类有几种

集成电路的分类有几种集成电路的分类有几种 (一)按功能结构分类 集成电路按其功能、结构的不同,可以分为模拟集成电路、数字集成电路和数/模混合集成电路三大类。

模拟集成电路又称线性电路,用来产生、放大和处理各种模拟信号(指幅度随时间边疆变化的信号。

例如半导体收音机的音频信号、录放机的磁带信号等),其输入信号和输出信号成比例关系。

而数字集成电路用来产生、放大和处理各种数字信号(指在时间上和幅度上离散取值的信号。

例如VCD、DVD重放的音频信号和视频信号)。

(二)按制作工艺分类 集成电路按制作工艺可分为半导体集成电路和薄膜集成电路。

薄膜集成电路又分类厚膜集成电路和薄膜集成电路。

(三)按集成度高低分类 集成电路按集成度高低的不同可分为小规模集成电路、中规模集成电路、大规模集成电路、超大规模集成电路、特大规模集成电路和巨大规模集成电路。

(四)按导电类型不同分类 集成电路按导电类型可分为双极型集成电路和单极型集成电路,他们都是数字集成电路。

双极型集成电路的制作工艺复杂,功耗较大,比如TTL类型。

单极型集成电路的制作工艺简单,功耗也较低,易于制成大规模集成电路,有CMOS、NMOS、PMOS等类型。

(五)按用途分类 集成电路按用途可分为电视机用集成电路、音响用集成电路、影碟机用集成电路、录像机用集成电路、电脑(微机)用集成电路、电子琴用集成电路、通信用集成电路、照相机用集成电路、遥控集成电路、语言集成电路、报警器用集成电路及各种专用集成电路。

(六)按应用领域分 集成电路按应用领域可分为标准通用集成电路和专用集成电路。

(七)按外形分 集成电路按外形可分为圆形(金属外壳晶体管封装型,一般适合用于大功率)、扁平型(稳定性好,体积小)和双列直插型。

数字集成电路的分类

数字集成电路的分类数字集成电路有多种分类方法,以下是几种常用的分类方法。

1.按结构工艺分按结构工艺分类,数字集成电路可以分为厚膜集成电路、薄膜集成电路、混合集成电路、半导体集成电路四大类。

图如下所示。

世界上生产最多、使用最多的为半导体集成电路。

半导体数字集成电路(以下简称数字集成电路)主要分为TTL、CMOS、ECL三大类。

ECL、TTL为双极型集成电路,构成的基本元器件为双极型半导体器件,其主要特点是速度快、负载能力强,但功耗较大、集成度较低。

双极型集成电路主要有TTL(Transistor-Transistor Logic)电路、ECL(Emitter Coupled Logic)电路和I2L(Integrated Injection Logic)电路等类型。

其中TTL电路的性能价格比最佳,故应用最广泛。

ECL,即发射极耦合逻辑电路,也称电流开关型逻辑电路。

它是利用运放原理通过晶体管射极耦合实现的门电路。

在所有数字电路中,它工作速度最高,其平均延迟时间tpd可小至1ns。

这种门电路输出阻抗低,负载能力强。

它的主要缺点是抗干扰能力差,电路功耗大。

MOS电路为单极型集成电路,又称为MOS集成电路,它采用金属-氧化物半导体场效应管(Metal Oxide Semi-conductor Field Effect Transistor,缩写为MOSFET)制造,其主要特点是结构简单、制造方便、集成度高、功耗低,但速度较慢。

MOS集成电路又分为PMOS(P-channel Metal Oxide Semiconductor,P沟道金属氧化物半导体)、NMOS(N-channel Metal Oxide Semiconductor,N沟道金属氧化物半导体)和CMOS(Complement Metal Oxide Semiconductor,复合互补金属氧化物半导体)等类型。

MOS电路中应用最广泛的为CMOS电路,CMOS数字电路中,应用最广泛的为4000、4500系列,它不但适用于通用逻辑电路的设计,而且综合性能也很好,它与TTL电路一起成为数字集成电路中两大主流产品。

模拟集成电路按照用途分类

模拟集成电路按照用途分类

集成电路还可以按照以下几种方法进行分类:

(1)按结构和功能分类: 分为数据转换器、线性和非线性放大器、电子开关和多路转 换器、稳压电源调节器及驱动器、传感器等。其中数据转换 电路既包括数字/模拟混合信号处理功能的电路,也包括纯 模拟信号产生、放大和处理的电路,因此可将这些电路归入 模拟电路。 (2)按集成度分类: 如前所述,根据每个芯片所包含的元器件数,分为小规模、 中规模、大规模、超大规模和极大规模集成电路。 (3)按导电类型分类: 分为双极型和单极型集成电路,以双极型晶体管为基础的单 片集成电路即为双极型集成电路,以MOS管为主组成的集成 电路即为单极型集成电路。

(2)仪用放大电路 是一类专门提供给仪器仪表使用的模拟集成电路,其实质也 是运算放大器,但结构比较特殊,一般由几个运算放大器组 合而成。

模拟集成电路按照用途分类

(3)稳压集成电路 用以声解码电路、音频前置放大电路、音频功率放大集 成电路、环绕声处理、电平驱动、电子音量控制、延时混响 集成电路等,常用于收音机、录音机、扩音机等。

模拟电子技术

模拟电子技术

模拟集成电路按照用途分类

按照用途的不同,常见的模拟集成电路可分为以下几类:

(1)集成运算放大电路(简称运放) 是多级差分放大电路集成而成的高增益直接耦合放大电路, 其内部通常包含输入级、中间放大级和输出级三部分。运算 放大电路用于模拟信号的运算和处理,也用来产生各种模拟 信号,由于其用途广泛,又分为:通用型运算放大电路、低 功耗运算放大电路、低噪声运算放大电路、高速运算放大电 路、高压运算放大电路等多种。

双极型电路

双极型电路

在半导体内,多数载流子和少数载流子两种极性的载流子(空穴和电子)都参与有源元件的导电,如通常的NPN或PNP双极型晶体管。

以这类晶体管为基础的单片集成电路,称为双极型集成电路。

以通常的NPN或PNP型双极型晶体管为基础的单片集成电路。

它是1958年世界上最早制成的集成电路。

双极型集成电路主要以硅材料为衬底,在平面工艺基础上采用埋层工艺和隔离技术,以双极型晶体管为基础元件。

按功能可分为数字集成电路和模拟集成电路两类。

在数字集成电路的发展过程中,曾出现了多种不同类型的电路形式,典型的双极型数字集成电路主要有晶体管-晶体管逻辑电路(TTL),发射极耦合逻辑电路(ECL),集成注入逻辑电路(I2L)。

TTL电路形式发展较早,工艺比较成熟。

ECL电路速度快,但功耗大。

I2L电路速度较慢,但集成密度高。

同金属-氧化物-半导体集成电路相比,双极型集成电路速度快,广泛地应用于模拟集成电路和数字集成电路。

双极型集成电路是最早制成集成化的电路,出现于1958年。

双极型集成电路主要以硅材料为衬底,在平面工艺基础上采用埋层工艺和隔离

技术,以双极型晶体管为基础元件。

它包括数字集成电路和线性集成电路两类。

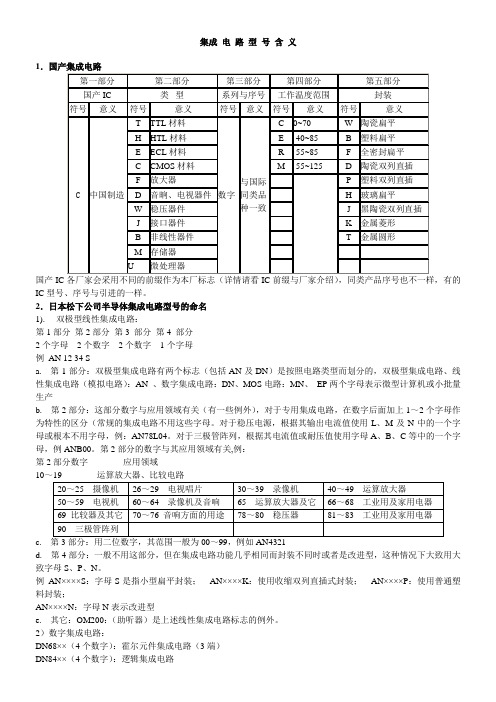

集成电路型号含义

集成电路型号含义1.国产集成电路第一部分第二部分第三部分第四部分第五部分国产IC类型系列与序号工作温度范围封装符号意义符号意义符号意义符号意义符号意义C 中国制造T TTL材料数字与国际同类品种一致C0~70W陶瓷扁平H HTL材料E-40~85B塑料扁平E ECL材料R-55~85F全密封扁平C CMOS材料M-55~125D陶瓷双列直插F放大器P塑料双列直插D音晌、电视器件H玻璃扁平W稳压器件J黑陶瓷双列直插J接口器件K金属菱形B非线性器件T金属圆形M存储器U 微处理器国产IC各厂家会采用不同的前缀作为本厂标志(详情请看IC前缀与厂家介绍),同类产品序号也不一样,有的IC型号、序号与引进的一样。

2.日本松下公司半导体集成电路型号的命名1). 双极型线性集成电路:第1部分第2部分第3 部分第4 部分2个字母2个数字2个数字1个字母例AN 12 34 Sa.第1部分:双极型集成电路有两个标志(包括AN及DN)是按照电路类型而划分的,双极型集成电路、线性集成电路(模拟电路):AN 、数字集成电路:DN、MOS电路:MN、EP两个字母表示微型计算机或小批量生产b.第2部分:这部分数字与应用领域有关(有一些例外),对于专用集成电路,在数字后面加上1~2个字母作为特性的区分(常规的集成电路不用这些字母。

对于稳压电源,根据其输出电流值使用L、M及N中的一个字母或根本不用字母,例:AN78L04。

对于三极管阵列,根据其电流值或耐压值使用字母A、B、C等中的一个字母,例ANB00。

第2部分的数字与其应用领域有关,例:第2部分数字应用领域10~19 运算放大器、比较电路20~25 摄像机26~29 电视唱片30~39 录像机40~49 运算放大器50~59 电视机60~64 录像机及音响65 运算放大器及它66~68 工业用及家用电器69 比较器及其它70~76 音响方面的用途78~80 稳压器81~83 工业用及家用电器90 三极管阵列c.第3部分:用二位数字,其范围一般为00~99,例如AN4321d.第4部分:一般不用这部分,但在集成电路功能几乎相同而封装不同时或者是改进型,这种情况下大致用大致字母S、P、N。

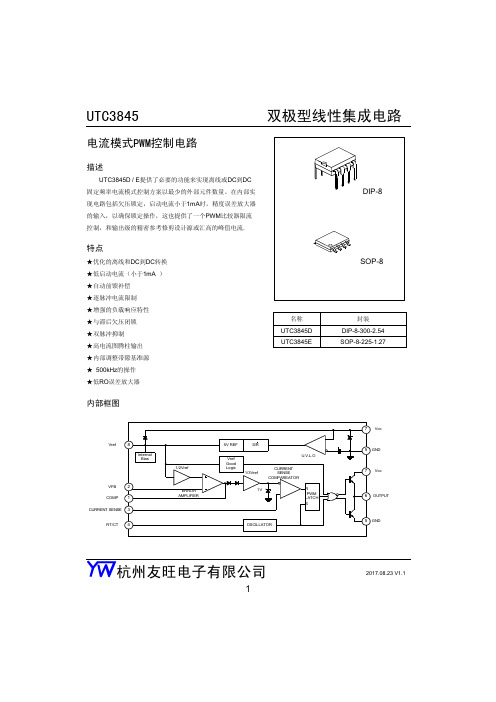

UTC3845双极型线性集成电路说明书

UTC3845 双极型线性集成电路1电流模式PWM 控制电路描述UTC3845D / E 提供了必要的功能来实现离线或DC 到DC 固定频率电流模式控制方案以最少的外部元件数量。

在内部实现电路包括欠压锁定,启动电流小于1mA 时,精度误差放大器的输入,以确保锁定操作,这也提供了一个PWM 比较器限流控制,和输出级的精密参考修剪设计源或汇高的峰值电流.特点★优化的离线和DC 到DC 转换 ★低启动电流(小于1mA ) ★自动前馈补偿 ★逐脉冲电流限制 ★增强的负载响应特性 ★与滞后欠压闭锁 ★双脉冲抑制 ★高电流图腾柱输出 ★内部调整带隙基准源 ★ 500kHz 的操作 ★低RO 误差放大器DIP-8SOP-8内部框图Vref VFB COMPCURRENT SENSERT/CT VccOUTPUTVccUTC3845双极型线性集成电路注1: Ta>25︒C,P D降额8mW/︒C.2UTC3845双极型线性集成电路3UTC3845 双极型线性集成电路4注2:这些参数仅供参考.注3测量的参数跳变点的闩锁 Vpin 2=0. 注4:增益:ΔVpin 1ΔVpin 3A=;0 ≤Vpin 3≤ 0.8V注5:调整Vcc 高于前启动阈值 15V.UTC3845 双极型线性集成电路5环路增益实验室测试电路VrefVccError Amp Adjust高峰值电流与容性负载,需要完善的接地处理技术.时间安排旁路电容应连接紧密,在的单点接地.晶体管和5kΩ的电位器用于样品振荡器波形并应用一个可调节的斜坡到引脚3到引脚5 。

欠压锁定VonVoffIccVcc在欠压锁定,输出驱动器偏置高阻抗状态。

6脚应该是一个泄放电阻,以防止启动电源开关,输出漏电流分流到地。

误差放大器配置误差放大器可以进出0.5mA 。

UTC3845双极型线性集成电路电流检测电路峰值电流(Is) 由以下公式决定:Ismax=10V/Rs.需要一个小的RC滤波器抑制开关转变。

集成电路的分类

集成电路的分类

1 集成电路

集成电路是一种由半导体集成电路封装在一个单独的芯片中,用来完成指定功能的电子设备。

集成电路芯片上有多个电路元件,如晶体管、双极型管和集成器件等,可以用有限的芯片替代一大堆的传统元件,大大降低电路的体积和重量。

2 集成电路的分类

1.按应用功能分类:功能较简单的集成电路, return数字与模拟集成电路,记忆集成电路,控制与驱动集成电路,接口集成电路,显示集成电路,通信集成电路,无线集成电路等,都可以根据实际应用需要组合使用。

2.按封装类型分类:DIP(双列外接管)、QFP(型推脚)、BGA(球形焊盘)等类型,可以满足不同封装空间的要求。

3.按处理类型分类:这是指集成电路的工作能力,包括标准处理器、精简处理器、多处理器和单片机等多种处理器。

4.按子系统分类:主要是把集成电路分为输入子系统、存储子系统、运算子系统和控制子系统,它们可以组合成不同的系统。

3 总结

集成电路是半导体集成电路封装在一个单独的芯片上,用来完成指定功能的电子设备,按应用功能、封装类型、处理类型和子系统分

类可以将集成电路划分为许多种类,既方便了电子产品的设计和研发,也更加高效。

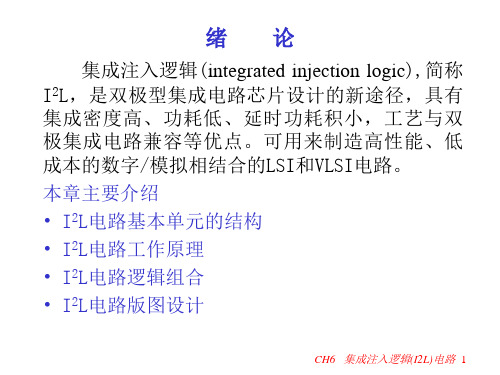

集成注入逻辑I2L电路课件.ppt

CH6 集成注入逻辑(I2L)电路 12

6.3.2 I2L电路分析

IC1=a4IP 式中a3,a4为Q3、Q4的共基极电流增益。

CH6 集成注入逻辑(I2L)电路 13

-VP IP

Q3

A IB1

+VP IP

Q4

Q1 B IC1

C Q2

图6.5 两级I2L门电路

若有N0个负载,则前一级所吸收的后级注入电流 为

IC1=N0(a4IP)

(6.1)

CH6 集成注入逻辑(I2L)电路 14

对于多集电极结构晶体管,因为基区几何形状是 长条结构,因此rB一般较大,为了减小rB对电流增 益的影响,改善各集电极电流增益的不均匀性,可 采用如下办法: (1) 将集电极引线孔排列方向和注入条平行,如图 6.3(a)所示,这样基极引线孔到各集电区的距离均 匀分布,可提高各集电区的电流增益及其均匀性。

的 电 流 IP 全 部 流 向 QN2 管 的 基 极 , QN2 管 导 通 ,

VB=VBE ≈0.7V。如果IP足够大,就可使QN2处于深

饱和,其各输出端的饱和压降近似为QN2管的本征

饱和压降(VCES≈VCES0)。所以当I2L电路的输入为

高电平VOH时,其QN2管各集电极的输出为低电平,

且

p 深饱和

2 p 临界饱和

即

a 2a

4

3

所以 I 2 L 电路正常工作的条件为

第八章双极型集成电路1

2020/7/13

47

接触孔和通孔

金属2

金属1

金属1

通

孔

接触 孔

金属2

2020/7/13

48

补充2:芯片封装工艺

2020/7/13

49

(1)封装工序流程

2020/7/13

50

(2)管芯分割工艺

2020/7/13

51

(3)芯片粘贴

2020/7/13

52

(4)引线键合

2020/7/13

53

(5)模压(塑封) (6)封装分类

• 氮化硅的化学气相淀积:中等温度(780~ 820℃)的LPCVD或低温(300℃) PECVD方法 淀积

2020/7/13

41

3、物理气相淀积(PVD)

• 蒸发:在真空系统中,金属原子获得足够的 能量后便可以脱离金属表面的束缚成为蒸汽 原子,淀积在晶片上。按照能量来源的不同 ,有灯丝加热蒸发和电子束蒸发两种

• 热分解淀积法

2020/7/13

32

进行干氧和湿氧氧化的氧化炉示意图

2020/7/13

33

2020/7/13

34

2、化学气相淀积(CVD)

• 化学气相淀积(Chemical Vapor Deposition):通 过气态物质的化学反应在衬底上淀积一层薄膜材 料的过程

• CVD技术特点:

– 具有淀积温度低、不消耗衬底材料、薄膜成分 和厚度易于控制、均匀性和重复性好、台阶覆 盖优良、适用范围广、设备简单等一系列优点

• 作为集成电路的隔离介质材料

• 作为电容器的绝缘介质材料

• 作为多层金属互连层之间的介质材料

• 作为对器件和电路进行钝化的钝化层 材料

集成电路的分类

集成电路的分类

集成电路的分类

1.按制造工艺和结构分类

可分为:半导体集成电路、膜集成电路、混合集成电路。

通常所说的集成

电路指的就是半导体集成电路。

膜集成电路又可分为薄膜和厚膜两类。

膜集

成电路和混合集成电路一般用于专用集成电路,通常称为模块。

2.按半导体工艺分类

⑴双极型集成电路

在硅片上制作双极型晶体管所生产的集成电路。

⑵MOS集成电路

在硅片制作MOS场效应管所生产的集成电路。

⑶双极型—MOS集成电路(BIMOS)

常将MOS电路作输入电路,双极型晶体管作输出电路,构成BIMOS集成电路。

3.按集成度分类

集成度是指一块硅片上含有元件数目。

表1-14给出了早期对集成度的分类:

表1-14 按集成度分类。

双极型晶体管集成电路

双极型晶体管集成电路好嘞,今天咱们聊聊双极型晶体管集成电路。

这听起来有点复杂,对吧?不过别担心,咱们慢慢来,像喝茶一样,轻松愉快。

你想象一下,在你的电子设备里,像手机、电视、电脑,这些小小的部件是如何在后台默默工作,提供给我们各种各样的功能。

双极型晶体管,就是它们其中一个非常重要的角色。

这东西就像是电子世界里的小小“开关”,能控制电流的流动,让我们用电的时候,心里更踏实。

它就像是个精明的店家,生意好坏全靠他来决定。

要是没有它,电子设备可能就要变得很笨拙,甚至不能正常工作。

想象一下,如果没有双极型晶体管,我们的生活会变得多么无趣。

可能你想看个电影,结果却发现没有信号,简直像是生活失去了色彩。

双极型晶体管可以将微弱的信号放大,就像是在黑暗的房间里开了一盏明亮的灯,让你看到更多的细节,真是神奇得很。

双极型晶体管还有个超厉害的功能,就是它能同时进行开关和放大,简直是个多面手,哪个电子设备都少不了它的身影。

而且你知道吗,这个晶体管的工作原理其实很简单。

它的核心是一个PN结构,两个半导体材料相结合,形成了一个奇妙的“组合拳”。

你可以把它想象成两位老朋友,一个是P型半导体,另一个是N型半导体。

它们就像是两条河流,彼此交汇,产生了电流。

电流在这之间游走,像鱼儿在水中自由自在。

真的是神奇的设计。

再加上控制电压的变化,就能实现各种各样的功能,太酷了。

在集成电路中,双极型晶体管更是扮演了举足轻重的角色。

它们小得像蚂蚁,但却能让整个电路工作得稳稳当当。

想象一下,如果电路里没有它,其他元件就像是一盘散沙,完全无法发挥作用。

可是有了它,整个电路就像是一场精彩的乐队演出,和谐又动听。

各种乐器各司其职,双极型晶体管就像是指挥,调动着所有的乐器,让音乐响彻云霄。

真的,集成电路就像一幅精美的画卷,每一笔都至关重要,而双极型晶体管就是那最亮眼的色彩。

说到这里,你可能会问,双极型晶体管是不是很难搞?其实不然,虽然它的名字听起来挺高大上的,但使用它其实很简单。

双极型集成电路

双极型集成电路双极型集成电路,简称双极型IC,是一种晶体管集成电路,其特征是只有两对对极:负极(集电极)和正极(发射极)。

它以一种传统的放大方式,经常与双极型放大器、单稳放大器、一步放大器配套使用,广泛应用在电子设备和功能性元件电路中。

双极型IC的特点在于只有两对对极,而且由晶体管构成,所以它是半导体器件中一种重要的产品,也是电子器件制造的重要组成部分。

双极型IC可以完成一些复杂的功能,比如比较、空间位置检测、模拟信号处理和数字信号处理等。

双极型的晶体管装置可以进行非常复杂的处理,因此双极型IC在许多电子设备中得到广泛应用,比如电脑、手机、数码摄像机、游戏机等。

双极型集成电路模块是半导体封装的重要产品,它利用半导体封装技术,将数据、电源和信号线装载到一个封装模块中,进行多层的封装。

它的优势在于封装物的体积小,性能稳定,使用广泛,可以简化原有的电路,减少电路的故障,从而提高整个系统的可靠性。

此外,双极型集成电路的制造工艺也十分重要,一般来讲,当双极型集成电路组成比较复杂时,就需要采用更加精细、先进的制造工艺,比如利用贴片技术,单片机技术,及其他微系统技术,确保双极型集成电路的性能达到设计要求。

在量产双极型IC时,还要注意对其进行测试,以确保其性能满足设计要求。

除了本身的生产厂商外,还需要第三方的检测机构进行测试,检查双极型IC的可靠性、可用性和可编程等性能参数。

双极型集成电路是一种重要的晶体管装置,也是电子设备的重要组成部分。

它的特点是只有两对对极,并且由晶体管构成,配合双极型放大器、单稳放大器、一步放大器等电子设备,可以完成复杂的功能。

在双极型集成电路的制造过程中,除了采用先进的制造工艺之外,还需要重视测试工作,以保证可靠性和可用性。

双极型集成电路工艺

双极型集成电路工艺(详案)各位同学:大家好!本节课将给大家介绍双极型集成电路的制造方法和过程,也就是制作工艺。

首先我们作一些必要的知识准备,来复习一下集成电路的相关知识。

广义的集成电路通俗的讲就是我们常说的芯片,它是将若干电子元件制作在一块单晶硅片上,并用金属或多晶硅互联线将它们连结起来的具有一定功能的电路,这些半导体电子元件包括:双极型晶体管、场效应管、二极管、电阻、电感、电容等。

世界上第一块IC 是由仙童半导体公司的Robert Noyce 和德州仪器公司的Jack Kilby 于是1959年分别独自发明的。

集成电路按照不同的标准可以有很多分类。

最常见的是按照处理信号的连续性来分类,可分为模拟集成电路和数字集成电路,模拟集成电路处理的是时间连续的模拟信号,而数字集成电路处理的则是时间与幅度取值都离散的数字信号。

还有一种分类方法是按构成集成电路的有源元件的种类来划分的,若构成电路的有源元件只有双极型晶体管,则为双极型集成电路;若构成电路的有源元件只有MOS 管(场效应晶体管),则为MOS 集成电路;若电路中既有双极型晶体管,又有MOS 管,则为BiCMOS 集成电路。

以上我们简单介绍了集成电路的划分,生产每一种集成电路都需要相应的制造工艺,比如双极型集成电路需要双极型集成电路工艺,MOS 集成电路需要MOS 工艺,而BiCMOS 集成电路则需要的相应的BiCMOS 工艺等等。

双极型集成电路工艺是所有集成电路工艺中最早发明的,尽管受到CMOS 工艺的巨大挑战,它仍然在高速、模拟、功率等类型的电路中占有很重要的地位。

双极型集成电路工艺按其所采用的隔离类型可分为两类,一类是采用介质隔离,也即在器件之间制备P-N 结作电隔离区,一类采用自然隔离。

采用介质隔离双极型集成电路工艺制作的电路有TTL(晶体管—晶体管逻辑) 电路、ECL(射极耦合逻辑)电路、STTL (肖特基晶体管—晶体管逻辑)电路等,而I 2 采用P-N 结作介质隔离的双极工艺按照制作的晶体管结构又可进一步细分为三种类型,即标准的埋入集电极晶体管工艺(SBC ),集电极扩散隔离晶体管工艺(CDI ),三重扩散晶体管工艺(3D )。

双极型集成电路的可靠性设计

2 1 过 流或短 路保护 .

热应力、 射线辐射应力、 生物及化学环境应力等苛

刻 的环 境条 件 。因此 , 可靠 性 已成 为军用 双极 型

过流或短路保护就是在输 出管的负载电流超 过额定值或短路时, 限制或减小输出管的电流, 使 输出管的功耗免于过载, 进而对芯片进行保护。

对一般 放大器 而 言 , 接负 载不能太 小 , 出 电流 外 输

集成电路最重要的参数指标之一。 为了提高电路 的可靠性 , 中的保护电路必 其 不可少。本文着重介绍了双极型模拟集成电路中 的过压保护 、 过流保护或短路保护、 过热保护等保

不能很大 , 防止因功耗电流过大而烧毁。 如图 1 所示, 为甲乙类放大器输 出级 , 中, 其 D 和 D 的作用是克服输出交越失真。 如果忽略 Q 、 假设 R = 流过其 ,Q , R =R, 上的电流为 I 则晶体管 Q 或 Q 的功耗 : 。 , 。 :

第3 O卷第 1期 2 1 3月 0 2年

螽

瓣嚣

Vo _ 0 No 1 l3 .

Ma. r 201 2

Jc I HENGDl ANLU ToN6X UN

双 极 型 集 成 电路 的 可 靠 性 设 计

白 涛

( 方通用 电子 集 团有 限公 司微 电子部 苏州 256 ) 北 1 13

中的质量控制及可靠性保证等方面。 标准上通常将可靠性定义为 : 产品在规定 的

条 件 下 和 规 定 的时 间 内 , 成 规定 功 能 的能 力 。 完

通常在芯片的设计过程中, 会加人各种保护电路

来提高电源芯片的自我保护能力。就是当电路出

现过压、 欠压、 过流、 过热等非正常状态时, 电路会 自动关闭 , 进入保护模式 ; 等电路恢复正常时 , 保 护电路停止工作 , 不影响电路的正常工作状态, 这 大大提高了芯片的安全、 可靠性。下面分别介绍

集成电路的检测与识别

2、数字集成电路的电路参数 (1)电压参数

符号 UOH U0L UIH UIH

名称 高电平输出电压 低电平输出电压 高电平输入电压 低电平输入电压

74系列 ≥2.4 ≤0.4 ≥2 ≤0.8

74LS系列 ≥2.7 ≤0.4 ≥2 ≤0.8

4000系列 ≥4.95 ≤0.05 ≥3.5 ≤1.5

74HC系列 ≥4.95 ≤0.05 ≥3.5 ≤1

四、集成电路的引脚识别

集成电路的封装形式有晶体管式封装、扁平封装和直插式 封装。集成电路的引脚排列次序有一定规律,一般是从外 壳顶部向下看,从左下角按逆时针方向读数,其中第一脚 附近一般有参考标志,如缺口、凹坑、斜面、色点等。引 脚排列的一般顺序为:

1 缺口 在集成电路的一端有一半圆形或方形的缺口。 2凹坑、色点或金属片 在集成电路一角有一凹坑、色点或 金属片。 3斜面、切角 在集成电路一角或散热片上有一斜面切角。

集成电路的检测与识别

一、 集成电路的类型和封装

1、类型 集成电路按功能可分为模拟集成电路和数字集成电路。模拟集成电路主 要有运算放大器、功率放大器、集成稳压电路、自动控制集成电路和信 号处理集成电路等;数字集成电路按结构不同可分为双极型和单极型电 路。其中,双极型电路有:DTL TTL ECL HTL等;单极型有:JFET NMOS PMOS CMOS四种。

系列 TTL系列

MOS系列

子系列 TTL LSTTL COMS HCOMS ACTMOS

名称

普通系列

低功耗TTL 互补场效应管型

高速CMOS

先进的高速CMOS电 路,“T”表示与TTL 电平兼容

型号 74/54 74/54LS 40/45 74HC 74ACT

简述双极型集成电路的工艺流程

简述双极型集成电路的工艺流程双极型集成电路的工艺流程那可真是个有趣的事儿呢!一、衬底准备。

咱得先有个合适的衬底呀。

这就好比盖房子得先有块好地基一样。

衬底材料的选择可重要啦,一般会选硅这样的材料。

然后呢,要对衬底进行一些处理,让它表面干净又平整。

这就像是给地基夯实、找平一样,要把那些杂质呀、不平整的地方都弄好,这样后续的工序才能顺利进行呢。

二、外延生长。

接着就是外延生长这个环节啦。

这一步就像是给我们的“小房子”添砖加瓦呢。

通过化学气相沉积的方法,在衬底上生长出一层很薄的硅外延层。

这层外延层的质量直接影响到后面电路的性能哦。

它的厚度呀、掺杂浓度呀都得精确控制。

要是这一步没做好,就像房子的墙壁砌歪了,后面的电路可就不好使啦。

三、氧化。

氧化这个步骤也很关键。

我们要在硅表面形成一层二氧化硅膜。

这层膜就像是给我们的电路穿上了一层保护衣。

它可以起到隔离、绝缘的作用呢。

这个过程就像是给小宝贝穿上了一件防护服,让它在后面的工序里不会受到外界的干扰。

而且这层二氧化硅膜还能在光刻等工序里当“遮挡板”,是不是很神奇呀?四、光刻。

光刻可有意思啦。

这就像是用一把超级精细的小刻刀,按照我们预先设计好的图案,在二氧化硅膜或者硅片上刻出各种形状。

就像我们在饼干上用模具印出各种可爱的形状一样。

光刻技术要非常精准,因为那些刻出来的形状就是我们电路里的各种元件的形状啦,比如说晶体管的形状呀,线路的形状呀。

要是刻错了,那就像画一幅画结果线条画歪了,整个电路就不能按照我们预想的那样工作了。

五、掺杂。

掺杂就像是给我们的电路注入不同的“魔法元素”。

通过离子注入或者扩散的方法,把一些特定的杂质原子引入到硅片里。

这些杂质原子会改变硅的电学性质,让它能形成不同类型的半导体区域,就像把普通的石头变成了有魔法的宝石一样。

不同的掺杂区域相互配合,就能构成双极型集成电路里的各种晶体管、二极管等元件啦。

六、金属化。

最后就是金属化这个步骤啦。

我们要在硅片上形成金属连线,把各个元件连接起来。

双极型集成电路制造工艺

双极型集成电路(Bipolar)制造工艺双极集成电路基础有源器件:双极晶体管无源器件:电阻、电容、电感等双极IC:数字集成电路、模拟和微波集成电路特点:速度快、稳定性好、负载能力强新型双极晶体管:异质结双极晶体管多晶硅发射极双极晶体管B E C•埋层•外延层•隔离区•基区•发射区和集电区•金属化PN结隔离的NPN晶体管•钝化层•几个概念–有源区:硅片上用于制造元器件的区域–场区:没有制作元器件的区域•埋层•外延层•隔离区•基区•发射区和集电区•金属化•钝化层介质(厚氧化层)隔离的NPN晶体管如何制造双极晶体管?双极晶体管是基于平面工艺,在硅表面加工制造出来的元器件隔离方法:PN结隔离、PN结对通隔离、介质—PN结混合隔离、全介质沟槽隔离PN结隔离PN结对通隔离轻掺杂的外晶体管延层PNP晶体管(横向PNP和衬底PNP)C EN C EB B P PP P横向PNP晶体管B EP CN+N+ N-epiP-subs衬底PNP晶体管pn结隔离SBC结构工艺流程pn结隔离SBC结构工艺流程n+埋层的设计n+埋层的两个作用①减小晶体管收集区串联电阻②减弱寄生PNP管效应考虑二个要点①选固溶度大的杂质以减小埋层的电阻率②选扩散系数小的杂质以减小后续高温工艺中n+埋层向外延层的扩散外延生长的设计外延层电阻率隔离区的设计z确保p+隔离扩散穿透整个n型外延层,和p型衬底相通z隔离扩散过程中外延层的下推距离集电极深接触的设计①进一步降低集电极串联电阻②集电极欧姆接触穿透外延层和埋层相连③使用“磷穿透”工艺两个不利因素:①增加工艺的复杂性n+②加大集电极和基区之间的距离基区形成的设计考虑z为提高电流放大倍数β值和减小基区渡越时间,要求基区宽度W小,基区的掺杂浓度N低b b太低时,在较高工作电压下,集电结和发射结z Nb空间电荷区容易相连会造成穿通现象,而且低Nb 也会加大基区电阻.小到一定限度,也要求提高基区的浓度防止基z Wb区穿通依据实际情况折衷考虑。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第一节

集成化元、器件及其特点

集成差分放大电路

第二节

第三节

电流模电路

功率输出级电路 集成运算放大器

第四节

第五节

第一节 集成化元器件及其特点

一 集成电路工艺简介

以制造NPN管的工艺流程为例

1. 平面工艺

选择隔离槽

P型硅片

氧化

光刻

隐埋层扩散

外延和氧化

隔离扩散

2 电路元件制造工艺

当(1+hfe)2Re>>(Rb+hie)时, •可见:Ree越大共模增益越小。

Rc AUc (单) 2 Re

2 共模输入电阻

Ri Ric Ric ( I ic1 I ic2 ) Rb hie (1 h fe )2 Re / 2 2

3 共模抑制比CMRR

定义:差放的差模增益与共模增益之比值的绝对值

移用来补偿另一只管子产生的漂移,从而抑制漂移。

4.这种对称性在集成工艺中较易实现。因此,集成电路中 广泛使用差分电路。

2. 集成化电阻阻值越大占用硅片面积越大,一般避免用大电 阻,尽量用晶体管代替电阻、电容。 3. 单个元件的精度不高,受温度影响大,但同一晶片上相邻 元件在制作尺寸和温度上有同向偏差,对称性好,故大量采 用差放电路及增益取决于电阻比值的负反馈放大器。 4. 集成电路中寄生参量的存在会引起元件间的寄生耦合,影 响电路稳定,使电路产生寄生振荡。

偏置电阻? •静态参数一致: •为什么电路中没有

IbQ1= IbQ2, •隔直电容? IcQ1= IcQ2, Ube1= Ube2, Uc1= Uc2,

•双端输出时:静态输出为 0

•信号输入方式

双端输入:输入信号接在两个输入端间。 单端输入:输入信号接在一个输入端与地间,另一端接地。 •差放输出方式 双端输出(平衡输出): 输出取自两个集电极之间。

常用的两种形式

4. 电阻:(一般有两种)

(1)金属膜电阻:温度特性好 (2)扩散电阻,按结构分:

基区电阻: 50-100K =±20%

=±20% 发射区电阻: 1-1000 (电阻率低) 窄基区电阻: 电阻率高 10-1000K

虽集成化电阻阻值误差大,但为同向偏差,匹配误差 小(小于3%)

选择基区 选择发射区 选择电极 引线窗口 选择要去 除的铝层

基区扩散

发射路的封装

(a)双列直插式

(b)圆壳式

二、 集成化元器件

1. NPN晶体管

在P型硅片衬底上扩散N+隐埋层,生长N型外延层,扩散P 型基区,N+型发射区和集电区 扩散P型基区

隔离岛

隐埋层

3. 二极管

晶体管制作时,只要开路或短路某一PN结即得(如图):

单端输出(不平衡输出):

输出取自一个集电极与地间。

双端输入双端输出差放

(二)对差模信号的放大作用

差模信号:是指在差放两个输入端接入两个幅度相等、极性 相反的信号,记为,Uid1 、Uid2 Uid1 = - Uid2 = Uid •当输入差模信号时:(动态) 由于电路的对称性有:

Ie1= -Ie2

5. 电容

MOS电容: 利用SiO2保护层作绝缘介质,用金属板和半导体作电容极板。

电容量与氧化物厚度成反比,与极板面积成正比,单位面积

电容量不大,但漏电较小、击穿电压较高。

二 集成化元器件特点

1. 集成电路工艺不能制作电感,超过100pF的大电容因占用 面积大也不易制作,故集成电路中不采用阻容耦合,而采用 直接耦合。

•其等效电路如图所示。

•由差模输入等效电路可求得:

1 共模电压增益Auc

双端输出时,由于电路对称,

与单边电路的 增益相同

U oc U oc1 U oc 2 AUc 0 U ic U ic

•单端输出时: 图6-10 (b)共模输入等效电路

h fe Rc U oc1 U oc 2 AUc (单)= U ic U ic Rb hie (1 h fe )2Re

第二节 集成差分放大电路

一、差分放大电路的工作原理: (一)差分放大 电路的组成:

由对称的两个基 本放大电路通过 射极公共电阻Ree 耦合构成。

•对称指两个三极管特性一致、电路参数相等: Rb1= Rb2 = Rb, 问题? Rc1= Rc2 = Rc, 1= 2 = , •为什么单边电路没有 hie1= hie2 = hie,

(三)对共模信号的抑制作用

共模信号:是指在差放两个输入端接入两个幅度相等、极性相同 的信号。 记为:Uic1 .Uic2 ; Uic1 = Uic2 = Uic •在共模信号下: Ie=Ie1+Ie2=2Ie1=2Ie2 URe=2Ie1Re=2Ie2Re •交流通路中等效为每个管子发

射极接入一 个2Re的电阻。

;

+ +

Uc1

Uc2

故 URe=0(交流接地) • 又因为:Uc1= -Uc2 故RL的中点呈地电位,即等 效为每管外接负载为RL/2。

URe

Ie1 Ie2

双端输入双端输出差放

•据此,可画出差放在差模输入情况下的交流等效电路(如图)

•由差模输入等效电路可求得:

1. 差模电压增益Aud: 双端输入双端输出时: 与单边电路的 增益相同

即 或 CMMR=|AUd/AUc| CMMR(dB)=20lg |AUd/AUc|

•双端输出时, CMMR可以认为等于无穷大 •单端输出时 CMMR(单)= |AUd(单)/AUc(• 单 )|

结论:

•差放对共模信号的抑制作用有重要的意义: 1.对电源扰动、及温度变化,在直接耦合放大电路中被逐 级放大,从而引起较大输出误差。(零点漂移) 2.对差放电路这些现象会引起两管同时产生同样的漂移, 这种大小相等、极性相同的漂移电压就是共模电压。 3.差放电路是利用电路对称的特点,将一个管子产生的漂

A Ud

U c1 U c 2 2U c1 U id1 U id 2 2Uid

' hfeRL Rb hie

' 其中 RL Rc //( RL / 2)

2. 差模输入电阻 Rid:

Rid 2Uid I id 2( Rb hie )

3. 差模输出电阻Rod: 双端输出时,Rod =2Rc//(2 /hoe) 2Rc; (当1/ hoe >>Rc时)