期中测试题部分参考答案

初一期中测试题及答案

初一期中测试题及答案一、选择题(每题2分,共20分)1. 下列哪个选项是正确的?A. 地球是平的B. 地球是圆的C. 地球是三角形的D. 地球是正方形的答案:B2. 哪个国家是联合国的创始会员国之一?A. 中国B. 巴西C. 俄罗斯D. 印度答案:A3. 以下哪个是光合作用的原料?A. 二氧化碳和水B. 氧气和水C. 二氧化碳和氧气D. 氧气和氮气答案:A4. 世界上最长的河流是?A. 尼罗河B. 亚马逊河C. 黄河D. 长江5. 以下哪个是植物细胞特有的结构?A. 叶绿体B. 线粒体C. 细胞壁D. 细胞膜答案:A6. 以下哪个是哺乳动物的特征?A. 有鳞片B. 有羽毛C. 有乳腺D. 有翅膀答案:C7. 以下哪个是化学变化?A. 水的沸腾B. 铁的生锈C. 冰的融化D. 木材的燃烧答案:B8. 以下哪个是物理变化?A. 铁的生锈B. 木材的燃烧C. 糖的溶解D. 酒精的挥发答案:C9. 以下哪个是力的平衡状态?B. 匀速直线运动C. 变速直线运动D. 曲线运动答案:A10. 以下哪个是光的折射现象?A. 影子的形成B. 镜子的反射C. 彩虹的产生D. 透镜成像答案:C二、填空题(每题2分,共20分)1. 地球的赤道周长大约是_______千米。

答案:400002. 联合国的总部设在_______。

答案:纽约3. 光合作用的产物是_______和_______。

答案:氧气,葡萄糖4. 世界上最大的沙漠是_______。

答案:撒哈拉沙漠5. 植物细胞中负责能量转换的细胞器是_______。

答案:线粒体6. 哺乳动物的生殖方式是_______。

答案:胎生7. 铁生锈是一种_______变化。

答案:化学8. 糖的溶解是一种_______变化。

答案:物理9. 力的平衡状态包括_______和_______。

答案:静止,匀速直线运动10. 光的折射现象中,光线从一种介质进入另一种介质时,其传播方向会发生_______。

五年级上册数学期中测试卷附参考答案(完整版)

五年级上册数学期中测试卷一.选择题(共6题,共12分)1.下面各式的结果大于18.4的算式是()。

A.18.4×0.99B.18.4÷0.99C.18.4÷1.992.把10米长的绳子剪成每段长2.5米的小段(绳子不折叠)。

一共要剪()次。

A.4B.5C.33.下列算式中,与5.6÷0.04的结果相等的式子是()。

A.0.56÷0.04B.5.6÷0.4C.560÷44.第二列第四行,用数对(2,4)来表示,第六列第一行,可以用()来表示。

A.(1,6)B.(6,1)C.(0,6)5.我们能用()表示一些物体的位置。

A.方向B.距离C.数对6.下面的数是循环小数的是()。

A.1.7474…B.15.438438438C.0.7777二.判断题(共6题,共12分)1.28.6×101-28.6=28.6×(101-1)应用了乘法分配律。

()2.大于0而小于1的两个小数,它们的积比原来每个数都小。

()3.教室里李军的位置用数对表示是(5,6),那么他同桌的位置可以用(5,5)表示。

()4.动物园中熊猫馆的位置是(5,7),说明熊猫馆位置是5列7行。

()5.一个大于0的数的1.2倍一定比这个数大。

()6.数对(6,7)与数对(7,6)表示的是同一位置。

()三.填空题(共6题,共21分)1.学校运来10吨煤,烧了8天后还剩4吨,平均每天烧煤()吨。

2.根据36×3=108,直接写出下面各式的结果。

0.36×3=()0.36×0.3=() 3.6×0.03=()360×0.3=() 3.6×0.3=()0.36×30=()3.两个因数的积是36,其中一个因数是48,另一个因数是()。

4.解决实际问题。

少先队员采集树种.第一组5人采集7千克,第二组6人采集7千克,第三组8人采集9千克,三个组平均每人采集的树种各是多()千克。

人教版四年级上册数学期中测试卷及参考答案(满分必刷)

人教版四年级上册数学期中测试卷一.选择题(共6题, 共12分)1.480796300中的“8”表示()。

A.8个亿B.8个百万C.8个千万2.最大的九位数与最小的十位数相差()。

A.1B.1千C.1万3.下面最接近十亿的数是()。

A.九亿九千万B.九亿九千零九万C.九亿零九万4.用一个15倍的放大镜观察30度的角, 这个角是()。

A.450度B.75度C.30度5.省略万位后面的尾数, 近似值是50万的数是()。

A.47500B.506800C.4993006.由4个“5”和2个“0”组成的一个“零”也不读出来的数是()。

A.550550B.505550C.500555二.判断题(共6题, 共12分)1.777中的三个7表示的意思是一样的。

()2.709080000000 读作: 七千零九十亿零八千万。

()3.某景区在今年春节期间共接待旅游人数达到四千四百九十六万人次, 这是一个近似数。

()4.“1”是自然数(0除外)的单位, 任何自然数都是由“1”组成的。

()5.一个七位数比一个八位数小1。

()6.用一个放大10倍的放大镜看一个12°的角, 看到的角是120°。

()三.填空题(共10题, 共27分)1.数一数, 下图中有()条线段。

2._____时整, 时针和分针成平角;钟面上3时整, 时针和分针成_____角。

3.有_____个锐角, _____个直角, _____个钝角, 一共有_____个角。

4.9时整, 时钟的时针与分针所成的角是________度, 是________角。

5.小马虎写一个六位数, 将最高位上的6写成9, 所得的六位数比原来的数大()。

6.亿级包括()、()、()、()这四个数位。

7.已知: ∠1= 52°, 求其余3个角的度数。

∠2=()°;∠3=()°;∠4=()°。

8.写出下而横线上的数。

(1)我国新疆的塔克拉玛干沙漠的面积是三十三万七千平方千米, 相当于8个瑞士。

2024小学教科版科学四年级上册期中测试卷含参考答案

小学教科版科学四年级上册期中测试卷一、填空题(每题2 分,共20 分)1. 声音是由物体()产生的。

2. 声音可以在()、()、()中传播。

3. 不同的物体传播声音的本领()。

4. 人的耳朵分为()、()、()三部分。

5. ()是一种发声仪器,用来调试乐器和测试音高。

6. 尺子伸出桌面越短,振动速度越(),发出的声音越()。

7. 风向可以用()来测量。

8. 降雨量的多少可以用()来测量。

9. 气象学家通常把云分为()、()、()三类。

10. 我们可以通过()、()、()等天气特征来描述天气。

二、选择题(每题1 分,共30 分)1. 用同样的力敲打长短不同的两根铁管,长铁管发出的声音()。

A. 高B. 低C. 强D. 弱2. 用相同的力拨动钢尺,钢尺伸出桌面的长度越长,振动的频率()。

A. 越高B. 越低C. 不变D. 无法确定3. 把闹钟放在玻璃罩内,抽去空气,只能看见闹钟的铃在动,却听不见声音,这是因为()。

A. 玻璃罩能隔音B. 声音不能在真空中传播C. 闹钟不会响了D. 耳朵有问题4. 声音在下列物体中传播速度最快的是()。

A. 空气B. 水C. 钢铁D. 木头5. 关于声音的说法正确的是()。

A. 声音在真空中也能传播B. 只要物体振动,我们就能听到声音C. 声音是由物体振动产生的D. 声音只能在空气中传播6. 下列关于耳的各部分结构功能描述错误的是()。

A. 耳郭收集声波B. 鼓膜将声波转化为振动C. 听小骨将振动传递到内耳D. 听觉神经将声音信号转化为电信号7. 用不同的力敲击同一个音叉,声音的()不同。

A. 高低B. 强弱C. 音色D. 以上都不对8. 风声是由()产生的。

A. 空气的振动B. 树叶的振动C. 风的流动D. 以上都不对9. 下列天气符号中,表示阴天的是()。

A. B. C. D.10. 测量气温的仪器是()。

A. 风向标B. 雨量器C. 温度计D. 湿度计11. 一天中气温最高的时候一般在()。

人教版小学四年级数学上册期中测试卷(附参考答案)

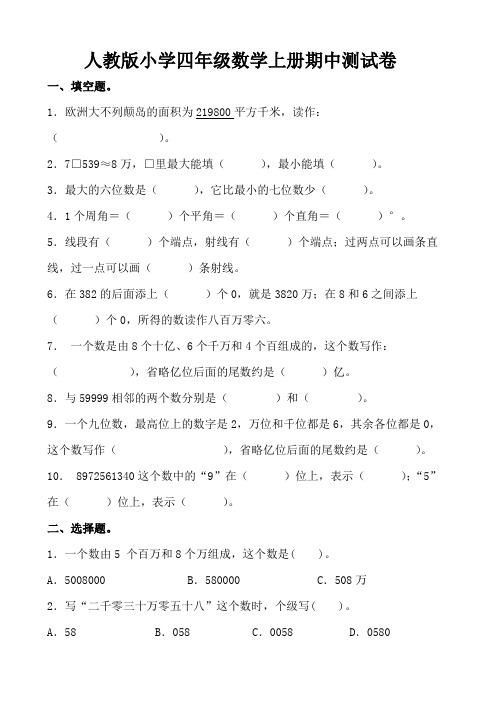

人教版小学四年级数学上册期中测试卷一、填空题。

1.欧洲大不列颠岛的面积为219800平方千米,读作:()。

2.7□539≈8万,□里最大能填(),最小能填()。

3.最大的六位数是(),它比最小的七位数少()。

4.1个周角=()个平角=()个直角=()°。

5.线段有()个端点,射线有()个端点;过两点可以画条直线,过一点可以画()条射线。

6.在382的后面添上()个0,就是3820万;在8和6之间添上()个0,所得的数读作八百万零六。

7.一个数是由8个十亿、6个千万和4个百组成的,这个数写作:(),省略亿位后面的尾数约是()亿。

8.与59999相邻的两个数分别是()和()。

9.一个九位数,最高位上的数字是2,万位和千位都是6,其余各位都是0,这个数写作(),省略亿位后面的尾数约是()。

10. 8972561340这个数中的“9”在()位上,表示();“5”在()位上,表示()。

二、选择题。

1.一个数由5 个百万和8个万组成,这个数是( )。

A.5008000 B.580000 C.508万2.写“二千零三十万零五十八”这个数时,个级写( )。

A.58 B.058 C.0058 D.05803.一个八位数,它的最高位是()A.百万位B.千万位C.亿位4.687450000中的“8”表示()A.8个万B.8个千万C.8个亿5.十万位、百万位、千万位、亿位…是()A.数位B.计数单位C.位数6.一个长方形广场长3500米,宽200米,这个广场的占地面积是()公顷。

A.7000 B.70 C.77.下面三个按键,( )是计算器上的开机键。

A.MC B.CE C.ON8.与79999相邻的两个数是()。

A.8000和7998 B.80000和79998 C.99999和100001 9.在8和9之间,添上()个0,这个数就是八百万零九。

A.4 B.5 C.610.用一副三角尺不能画出的角是( )。

期中综合测试题及参考答案

期中综合测试满分(120分)听力部分(共20分)(略)笔试部分(共100分)I.单项选择(每题1分,共15分)( )21. 含有相同音素的一组字母是______。

A. A, H, YB. C, G, TC. J, L, MD. O, U, W( )22. We have four classes ______ the morning.A. ofB. atC. onD. In( )23. —Is that your father?—No. It’s my uncle, my mother’s _____.A. sonB. sisterC. brotherD. daughter( )24. —Can you ______ my English tapes to me, Mom? —OK!A. callB. takeC. haveD. bring( )25. —Is that ______ volleyball?—Yes. Bill likes playing ______ volleyball. ______ volleyball is his.A. the; a; /B. /; the; /C. /; the; TheD. a; /; The( )26. —Excuse ______. Is this ______ book?—Yes, thanks.A. me; myB. I; yourC. me; yourD. I; my( )27. —What fruit does Jenny ______?—She ______ apples.A. like; likeB. like; likesC. likes; likeD. likes; likes( )28. —How are you, Nancy?—I’m not ______. And I can’t eat ______ every day.A. OK; goodB. well; goodC. well; fineD. fine; well( )29. —Does Bob have vegetables for dinner?—______. But his sister has some carrots.A. Yes, he hasB. No, he hasn’tC. Yes, he doesD. No, he doesn’t( )30. —Let’s _________ some chicken. —Great! I like chicken.A. likeB. hasC. to haveD. eat( )31. —Where ______ your food?—I only have two hamburgers. They ____ on the table.A. is; isB. is; areC. are; isD. are; are( )32. I have a computer, ______ I don’t play computer games on it.A. alsoB. onlyC. butD. and( )33. My grandmother needs ______ carrots and ______ broccoli.A. a; manyB. lots of; someC. some; aD. a lot of; many( )34. —______ do you spell your family name?—C-L-A-R-K, Clark.A. HowB. WhatC. WhereD. What color( )35. —Your jacket looks nice.—___________.A. No, thanksB. Yes, pleaseC. It isn’t niceD. Thank youII.完形填空(每题1分, 共10分)I have a nice family. Only 36 people are in it. They’re my 37 , my mother and me. Here is a 38 of my family. This is my father. He likes dogs (狗) and he has a white 39 . The name of it is Tony. Look! Tony is next to (挨着) my father 40 the photo. Look at my mother. She41 to cook (烹调). She cooks 42 food for us every day. This is me. I’m 11. I’m in a good 43 .I like English and our English classes are 44. I like playing sports and I like 45 sports games on TV.My family is nice and I like it.( )36. A. two B. three C. four D. five( )37. A. aunt B. brother C. sister D. father( )38. A. map B. book C. name D. photo( )39. A. it B. one C. this D. that( )40. A. on B. of C. in D. at( )41. A. calls B. thanks C. likes D. takes( )42. A. first B. healthy C. last D. Boring( )43. A. club B. family C. picture D. School( )44. A. boring B. dear C. interesting D. Difficult( )45. A. playing B. having C. meeting D. watchingIII.阅读理解(每小题2分, 共30分)AI’m Wang Ping. I’m in Beijing. I like healthy food. I have milk (牛奶) and fruit for breakfast; rice (米饭), chicken and vegetables for lunch; vegetables, fruit and salad for dinner. Here is what my friends like eating. Let’s have a look!Zhang Jian(inBeijing)Like:Li Ming(inShanghai)Like:Zheng Hui(inBeijing)Like:根据材料内容,选择正确答案。

人教版数学六年级上册期中测试卷及参考答案(完整版)

人教版数学六年级上册期中测试卷一.选择题(共8题, 共16分)1.一个游泳池可装180吨水, 甲管单独注要10小时注满水池, 乙管单独注要9小时注满水池。

现两管同时注, 几小时可注满水池?列式为()。

A.180÷10+180÷9B.180÷() C.1÷()2.因为×=1 , 所以()。

A.是倒数B.和互为倒数 C.和都是倒数3.饲养场养白兔51只, 占兔子总数的, 要求()可以列式为“”。

A.黑兔只数B.兔子总数C.无法确定4.看图列式, 正确的是()。

A. B. C.5.小明家在小丽家的南偏西40°方向上, 小丽家在小明家的()方向。

A.北偏东40°B.东偏南40°C.东偏北40°6.下面互为倒数的两个数是()。

A.和0.6B.1.25和0.8C.和7.图书馆有科技书150本, 科技书的本数比故事书的本数多, 故事书有()本。

A.180B.150C.1258.小方每天上学先向北偏东40°方向走200米, 再向正东方向走300米到学校, 他每天放学先向正西方向走300米, 再向()方向走200米到家。

A.北偏东40°B.南偏西40°C.西偏南40°二.判断题(共8题, 共16分)1.真分数的倒数大于1, 假分数的倒数小于1。

()2.一个不等于0的数乘假分数的积一定大于这个数。

()3.a、b都不为0, 如果a×=b÷, 那么a<b。

()4.把b米长的水管切成一样长的几段, 切了4次, 每段长(b×)米。

()5.2千克的食盐, 吃去, 还剩1千克。

()6.把8t煤平均分成5份, 每份是t。

()7.乘的积在和之间。

()8.一捆书有15本, 其中是科技书, 科技书有10本。

()三.填空题(共8题, 共18分)1.在括号内填上“>”“<”或“=”。

2024小学教科版科学五年级上册期中测试卷附参考答案

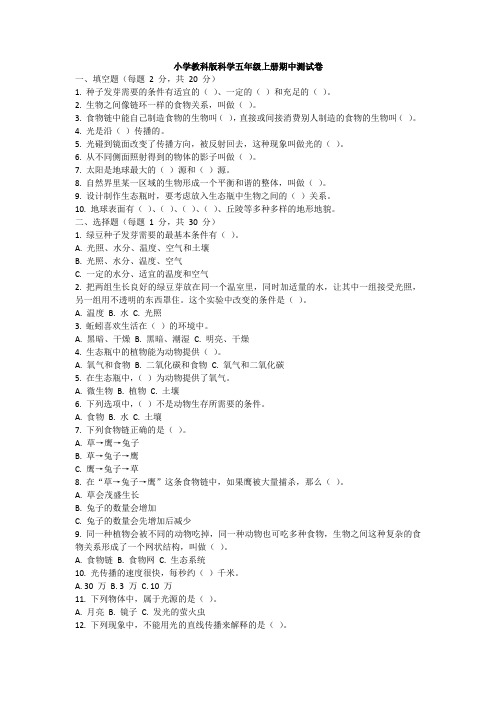

小学教科版科学五年级上册期中测试卷一、填空题(每题2 分,共20 分)1. 种子发芽需要的条件有适宜的()、一定的()和充足的()。

2. 生物之间像链环一样的食物关系,叫做()。

3. 食物链中能自己制造食物的生物叫(),直接或间接消费别人制造的食物的生物叫()。

4. 光是沿()传播的。

5. 光碰到镜面改变了传播方向,被反射回去,这种现象叫做光的()。

6. 从不同侧面照射得到的物体的影子叫做()。

7. 太阳是地球最大的()源和()源。

8. 自然界里某一区域的生物形成一个平衡和谐的整体,叫做()。

9. 设计制作生态瓶时,要考虑放入生态瓶中生物之间的()关系。

10. 地球表面有()、()、()、()、丘陵等多种多样的地形地貌。

二、选择题(每题1 分,共30 分)1. 绿豆种子发芽需要的最基本条件有()。

A. 光照、水分、温度、空气和土壤B. 光照、水分、温度、空气C. 一定的水分、适宜的温度和空气2. 把两组生长良好的绿豆芽放在同一个温室里,同时加适量的水,让其中一组接受光照,另一组用不透明的东西罩住。

这个实验中改变的条件是()。

A. 温度B. 水C. 光照3. 蚯蚓喜欢生活在()的环境中。

A. 黑暗、干燥B. 黑暗、潮湿C. 明亮、干燥4. 生态瓶中的植物能为动物提供()。

A. 氧气和食物B. 二氧化碳和食物C. 氧气和二氧化碳5. 在生态瓶中,()为动物提供了氧气。

A. 微生物B. 植物C. 土壤6. 下列选项中,()不是动物生存所需要的条件。

A. 食物B. 水C. 土壤7. 下列食物链正确的是()。

A. 草→鹰→兔子B. 草→兔子→鹰C. 鹰→兔子→草8. 在“草→兔子→鹰”这条食物链中,如果鹰被大量捕杀,那么()。

A. 草会茂盛生长B. 兔子的数量会增加C. 兔子的数量会先增加后减少9. 同一种植物会被不同的动物吃掉,同一种动物也可吃多种食物,生物之间这种复杂的食物关系形成了一个网状结构,叫做()。

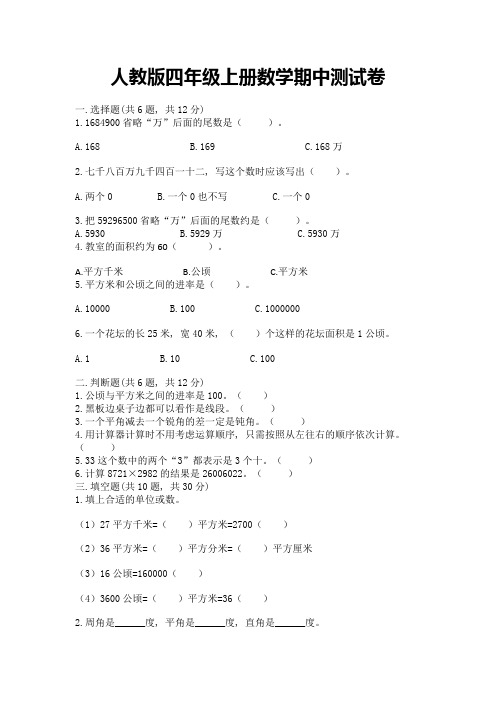

人教版四年级上册数学期中测试卷及参考答案(完整版)

人教版四年级上册数学期中测试卷一.选择题(共6题, 共12分)1.1684900省略“万”后面的尾数是()。

A.168B.169C.168万2.七千八百万九千四百一十二, 写这个数时应该写出()。

A.两个0B.一个0也不写C.一个03.把59296500省略“万”后面的尾数约是()。

A.5930B.5929万C.5930万4.教室的面积约为60()。

A.平方千米B.公顷C.平方米5.平方米和公顷之间的进率是()。

A.10000B.100C.10000006.一个花坛的长25米, 宽40米, ()个这样的花坛面积是1公顷。

A.1B.10C.100二.判断题(共6题, 共12分)1.公顷与平方米之间的进率是100。

()2.黑板边桌子边都可以看作是线段。

()3.一个平角减去一个锐角的差一定是钝角。

()4.用计算器计算时不用考虑运算顺序, 只需按照从左往右的顺序依次计算。

()5.33这个数中的两个“3”都表示是3个十。

()6.计算8721×2982的结果是26006022。

()三.填空题(共10题, 共30分)1.填上合适的单位或数。

(1)27平方千米=()平方米=2700()(2)36平方米=()平方分米=()平方厘米(3)16公顷=160000()(4)3600公顷=()平方米=36()2.周角是______度, 平角是______度, 直角是______度。

3.数一数。

图中有()条线段、()个锐角、()个直角、()个钝角。

4.一个九位数最高位上是8, 最低位上是5, 万位上是6, 其余各位上都是0, 这个数是________, 读作________, 四舍五入到万位约是________。

5.晚上九点时针和分针成()角, 5点时针和分针成()角。

6.比7厘米短3厘米的是()厘米的线段。

7.9时整, 分针和时针组成的角是(), 6时整, 分针和时针组成的角是()。

8.周角是_____度的角, 直角是_____度的角;周角的一半是_____角。

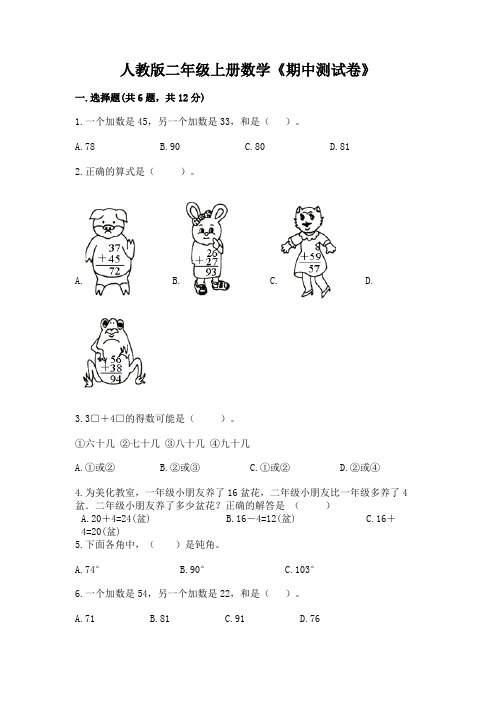

人教版二年级上册数学《期中测试卷》附参考答案(完整版)

人教版二年级上册数学《期中测试卷》一.选择题(共6题,共12分)1.一个加数是45,另一个加数是33,和是()。

A.78B.90C.80D.812.正确的算式是()。

A. B. C. D.3.3□+4□的得数可能是()。

①六十几②七十几③八十几④九十几A.①或②B.②或③C.①或②D.②或④4.为美化教室,一年级小朋友养了16盆花,二年级小朋友比一年级多养了4盆.二年级小朋友养了多少盆花?正确的解答是()A.20+4=24(盆)B.16-4=12(盆)C.16+4=20(盆)5.下面各角中,()是钝角。

A.74°B.90°C.103°6.一个加数是54,另一个加数是22,和是()。

A.71B.81C.91D.76二.判断题(共6题,共12分)1.判断一个角是锐角还是钝角,可以用三角尺上的直角比一比。

()2.角的大小同边的长短有关。

()3.三角板上的3个角有锐角、直角和钝角。

()4.一个加数是3,另一个加数是35,和是85。

()5.学校操场环形跑道长200厘米。

()6.1米和100厘米不一样长。

()三.填空题(共8题,共37分)1.食堂买了西红柿35个,做菜用了一些,还剩9个,用去________个。

2.填上合适的数。

(1)14=□-□(2)26-□=16+□(3)7+25=□-83.横线上应该填几?47+16=______3 9+64=______3 44+53=______740+29=______9 33+18=______1 39+27=______64.在横线上填上>、<或=。

(1)44+28______72 (2)84-29______65 (3)80______5+755.一辆公共汽车从车站开出时车上有24人,到第一站下去6人,这时车上有________人,又上来8人,现在车上有________人。

6.你的身高是________米________厘米。

讲台的长大约是________米。

初一历史期中测试题及参考解答

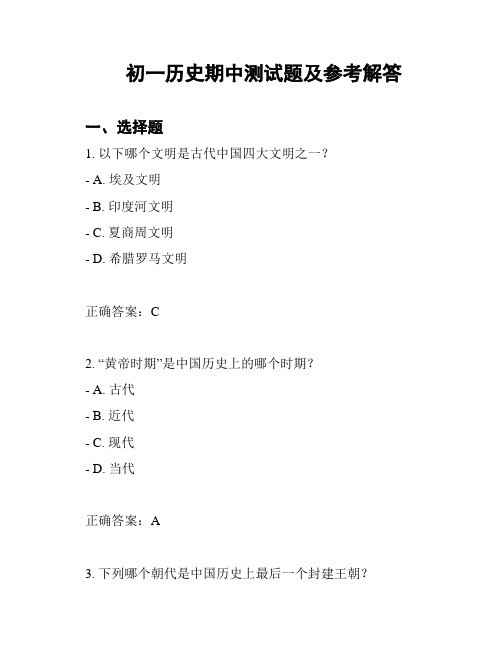

初一历史期中测试题及参考解答一、选择题1. 以下哪个文明是古代中国四大文明之一?- A. 埃及文明- B. 印度河文明- C. 夏商周文明- D. 希腊罗马文明正确答案:C2. “黄帝时期”是中国历史上的哪个时期?- A. 古代- B. 近代- C. 现代- D. 当代正确答案:A3. 下列哪个朝代是中国历史上最后一个封建王朝?- A. 唐朝- B. 宋朝- C. 清朝- D. 明朝正确答案:C二、判断题1. 孔子是中国古代著名的思想家和教育家。

- 正确/错误正确答案:正确2. 《周易》是中国古代的一部兵法著作。

- 正确/错误正确答案:错误3. 《三国演义》是中国古代的一部历史小说。

- 正确/错误正确答案:正确三、简答题1. 请简要介绍一下中国古代的封建社会。

参考答案:中国古代的封建社会是指以封建制度为基础的社会形态。

在封建社会中,君主拥有最高权力,掌握土地和资源的分配,而地主贵族则享有特权。

社会上的人们按照封建等级进行划分,分为君主、贵族、士人、农民和奴隶等不同的阶层。

封建社会注重礼仪和忠诚,封建制度对社会的政治、经济和文化发展产生了深远影响。

2. 请简要介绍一下中国古代的科举制度。

参考答案:中国古代的科举制度是一种选拔官员的考试制度。

根据科举制度,国家每隔一定年限举行一次科举考试,考试内容主要包括经义、史学和文学等科目。

通过考试的人有机会成为官员,享受特权和地位。

科举制度在中国历史上长期存在,对于选拔人才和维护社会稳定起到了积极作用。

3. 请简要介绍一下中国古代的丝绸之路。

参考答案:丝绸之路是中国古代的一条重要贸易路线。

这条贸易路线起始于中国的长安(今天的西安),经过中亚、西亚,最终抵达地中海地区。

丝绸之路的名称源自于中国丝绸的贸易,但实际上,这条贸易路线上还流通着许多其他商品和文化。

丝绸之路不仅促进了中国与西方国家之间的贸易往来,也促进了东西方文化的交流和融合,对于推动世界的经济和文化发展起到了重要作用。

小学一年级上册数学期中测试卷附参考答案【完整版】

小学一年级上册数学期中测试卷一.选择题(共6题,共12分)1.()扇子大,()扇子小。

A.①②B.②①2.()是正方体。

A. B. C.3.水最多的是()。

A. B. C.4.下面物体哪个少?()A. B.5.数一数,图中表示()。

A. 4B. 5C. 7D. 86.我来帮助小羊。

小羊肖恩想看到冰箱的门,他应该在哪个面看?()A.后面B.左面C.前面D.右面二.判断题(共6题,共12分)1.3个苹果和第三个苹果一多样。

( )2.2+1的和与1+2的和相等。

()3.比5大1的数是4,比5小1的数是6。

()4.如图:☆○△□,☆在最前面。

()5.蜜蜂在小狗的上面,小狗在小猴的右面。

()6.狐狸在梅花鹿的后面。

()三.填空题(共6题,共21分)1.估一估哪个杯子里装的水最多,再按从多到少的顺序排一排。

()2.我走路靠()边走,汽车靠()边行。

3.第1盆有3朵花,第2盆有()朵花;有2朵花的是第()盆,它左边的一盆有()朵花;第()盆花的朵数最多。

4.在○里填“+”,或“-”。

3○2=1 5○2=3 2○1=34○1=5 3○1=2 5○4=15.在横线上填上“+”或“-”。

3 ________ 2=54 ________ 1=3 2 ________ 2=4 3 ________ 0=3 2 ________ 1=1 4 ________ 1=5 6.对下列图形进行分类,填写序号:平面图形:________立体图形:________四.计算题(共2题,共11分)1.看图列式计算。

3+□=□(个)2.看图列算式。

1. 2.五.作图题(共2题,共12分)1.圈一圈,涂一涂。

把右边的7个图形圈起来。

从右边数起,把第7个图形涂上颜色。

2.数一数,画一画。

(1)一共有()只动物。

(2)从左往右数,排第(),排第()。

(3)给从左往右数排第3的动物涂上颜色。

(4)把从左往右数排第5的动物圈起来。

六.解答题(共6题,共29分)1.数一数,一共有多只小兔?(1)在这些兔子中,有______只是,有______只是。

人教版五年级上册数学期中测试卷及参考答案(完整版)

人教版五年级上册数学期中测试卷一.选择题(共6题,共12分)1.5.8÷0.001与5.8×1000的结果比较()。

A.相等B.积大C.商大2.计算小数除法,如果要求得数保留三位小数,计算时应算到小数点后面第()位。

A.二B.三C.四3.在计算6.7×10.1时,要使计算简便,应运用()。

A.乘法分配律B.乘法交换律C.乘法结合律4.与0.37×15结果相同的算式是()。

A.0.37×1.5B.3.7×1.5C.0.37 ×71505.8.98÷0.01与8.98×100的结果相比较()。

A.商较大B.积较大C.相等6.计算2.5×9.9的简便方法是()。

A.(10-1)×2.5B.(10-0.1)×2.5C.(9.9+0.1)×2.5二.判断题(共6题,共12分)1.两个自然数相除,当除不尽时,商是循环小数。

()2.数对(5,3)和数对(3,4)这两个位置在同一列。

()3.0.7×0.7的积保留一位小数约是0.5。

()4.要使商不变,被除数和除数都要同时乘或除以同一个数。

()5.两个比1小的数相乘,积比任何一个因数都要小。

()6.21×0.1,就是把21缩小为原来的十分之一。

()三.填空题(共8题,共31分)1.3.154保留一位小数是(),精确到百分位是()。

2.在○里填上“>”“<”或“=”。

3.26×10○32.6 3.2×0.99○3.24.08×1.2○4.08 0.21×5○0.25×15.73×1.7○5.73 0.53×6.9○6.93.在○里填上“>”“<”或“=”。

72×0.9○7.2 43.4÷1.2○43.4 3.2÷0.01○3.2×0.015.8×2.4○5.8 18.7÷0.9○18.7 8.23×4.5○82.3×454.3.14加5.6与1.2的积,和是多少?列式是()。

人教版五年级上册语文期中测试卷及参考答案(完整版)

人教版五年级上册语文期中测试卷及参考

答案(完整版)

一、选择题

1. 下列词语中,不属于同一类别的一项是()。

A. 河流

B. 山脉

C. 森林

D. 花朵

参考答案:D

2. 阅读短文,回答问题。

小明的妈妈从工作中回来,拿出一个盒子,告诉小明:“这里有一双新鞋子,你试试看。

”小明兴高采烈地试了一下,发现它们很舒服。

“谢谢妈妈!”小明高兴地对妈妈说。

小明的妈妈开心地笑了,说:“好孩子,你喜欢就好。

”

问题:小明妈妈带回来的是什么?

参考答案:一双新鞋子

二、填空题

1. 人的鼻子用来()。

参考答案:嗅觉

2. 动物的种类非常()。

参考答案:丰富

三、简答题

1. 简述中国的四大发明之一——造纸术的历史。

参考答案:造纸术是中国古代的一项伟大发明,最早出现在东

汉时期。

通过将纸浆倒入漏斗状的木质模具中,使水分流失,然后

晾晒干燥即可得到纸张。

2. 请用自己的话简述《聪明的一休》这个故事。

参考答案:《聪明的一休》是一篇寓言故事。

故事中的一休是

一个机智聪明的小和尚,他通过巧妙的办法解决了许多问题和困难,展示了他的智慧和机智。

以上是《人教版五年级上册语文期中测试卷及参考答案(完整版)》的部分内容。

> 注意:此文档中的题目和参考答案仅供参考,具体以教师的讲解和评分标准为准。

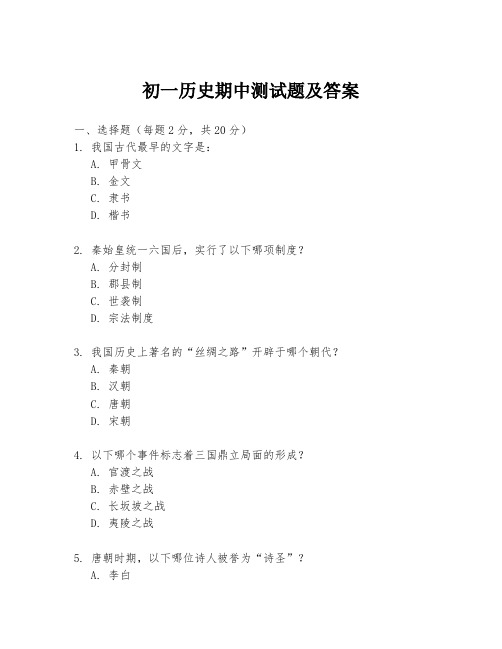

初一历史期中测试题及答案

初一历史期中测试题及答案一、选择题(每题2分,共20分)1. 我国古代最早的文字是:A. 甲骨文B. 金文C. 隶书D. 楷书2. 秦始皇统一六国后,实行了以下哪项制度?A. 分封制B. 郡县制C. 世袭制D. 宗法制度3. 我国历史上著名的“丝绸之路”开辟于哪个朝代?A. 秦朝B. 汉朝C. 唐朝D. 宋朝4. 以下哪个事件标志着三国鼎立局面的形成?A. 官渡之战B. 赤壁之战C. 长坂坡之战D. 夷陵之战5. 唐朝时期,以下哪位诗人被誉为“诗圣”?A. 李白B. 杜甫C. 白居易D. 王维二、填空题(每空1分,共10分)6. 我国历史上第一个奴隶制国家是________。

7. 秦始皇统一六国后,统一了货币、度量衡和________。

8. 唐朝时期,长安城是当时世界上最大的城市之一,也是________的中心。

9. 我国古代四大发明包括造纸术、印刷术、火药和________。

10. 明朝时期,郑和下西洋,最远到达了________。

三、简答题(每题5分,共10分)11. 简述汉武帝时期推行的“罢黜百家,独尊儒术”政策的意义。

12. 简述唐朝时期对外交往的特点。

四、材料分析题(每题10分,共20分)13. 阅读以下材料,分析唐朝时期对外交往的开放性及其对后世的影响。

材料一:唐朝时期,长安城内居住着来自世界各地的商人和使节。

材料二:唐朝时期,中国与日本、新罗等国家的文化交流频繁,如鉴真东渡日本传播佛教。

14. 阅读以下材料,分析明朝时期郑和下西洋的历史意义。

材料一:郑和下西洋,最远到达了非洲东海岸。

材料二:郑和的航海活动促进了中国与海外各国的经济文化交流。

五、论述题(共20分)15. 论述中国古代科技成就对世界文明的贡献。

答案:一、选择题1-5 A B B B B二、填空题6. 夏朝7. 书写8. 经济和文化9. 指南针10. 非洲东海岸三、简答题11. 汉武帝推行的“罢黜百家,独尊儒术”政策,加强了中央集权,统一了思想文化,促进了儒家思想的传播和发展,对后世产生了深远的影响。

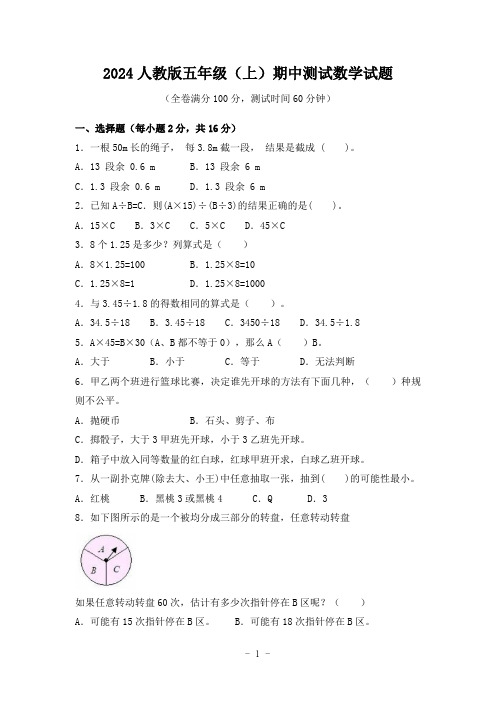

2024人教版五年级(上)期中测试数学试题(附参考答案)

2024人教版五年级(上)期中测试数学试题(全卷满分100分,测试时间60分钟)一、选择题(每小题2分,共16分)1.一根50m长的绳子,每3.8m截一段,结果是截成 ( )。

A.13 段余 0.6 m B.13 段余 6 mC.1.3 段余 0.6 m D.1.3 段余 6 m2.已知A÷B=C.则(A×15)÷(B÷3)的结果正确的是( )。

A.15×C B.3×C C.5×C D.45×C3.8个1.25是多少?列算式是()A.8×1.25=100 B.1.25×8=10C.1.25×8=1 D.1.25×8=10004.与3.45÷1.8的得数相同的算式是()。

A.34.5÷18 B.3.45÷18 C.3450÷18 D.34.5÷1.85.A×45=B×30(A、B都不等于0),那么A()B。

A.大于 B.小于 C.等于 D.无法判断6.甲乙两个班进行篮球比赛,决定谁先开球的方法有下面几种,()种规则不公平。

A.抛硬币 B.石头、剪子、布C.掷骰子,大于3甲班先开球,小于3乙班先开球。

D.箱子中放入同等数量的红白球,红球甲班开求,白球乙班开球。

7.从一副扑克牌(除去大、小王)中任意抽取一张,抽到( )的可能性最小。

A.红桃 B.黑桃3或黑桃4 C.Q D.38.如下图所示的是一个被均分成三部分的转盘,任意转动转盘如果任意转动转盘60次,估计有多少次指针停在B区呢?()A.可能有15次指针停在B区。

B.可能有18次指针停在B区。

C.可能有20次指针停在B区。

D.可能有25次指针停在B区。

二、判断题(每小题1分,共6分)1.25的20倍与250的2倍相等。

()2.4.06÷3.3的商是1.2,余数是1。

人教版五年级上册数学期中测试卷附参考答案【完整版】

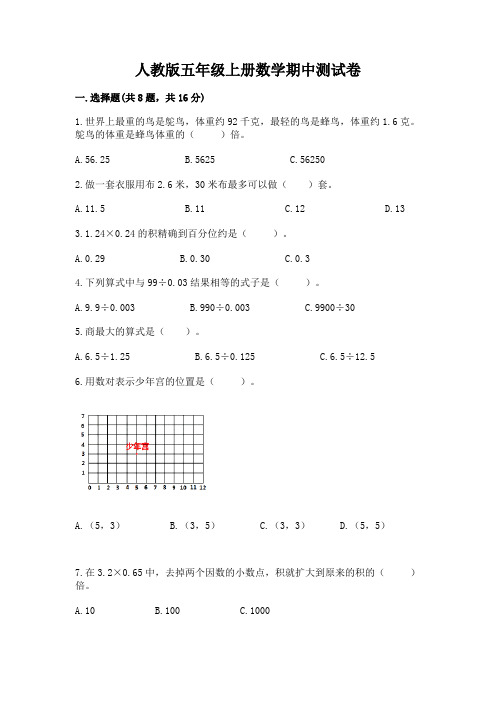

人教版五年级上册数学期中测试卷一.选择题(共8题,共16分)1.世界上最重的鸟是鸵鸟,体重约92千克,最轻的鸟是蜂鸟,体重约1.6克。

鸵鸟的体重是蜂鸟体重的()倍。

A.56.25B.5625C.562502.做一套衣服用布2.6米,30米布最多可以做()套。

A.11.5B.11C.12D.133.1.24×0.24的积精确到百分位约是()。

A.0.29B.0.30C.0.34.下列算式中与99÷0.03结果相等的式子是()。

A.9.9÷0.003B.990÷0.003C.9900÷305.商最大的算式是()。

A.6.5÷1.25B.6.5÷0.125C.6.5÷12.56.用数对表示少年宫的位置是()。

A.(5,3)B.(3,5)C.(3,3)D.(5,5)7.在3.2×0.65中,去掉两个因数的小数点,积就扩大到原来的积的()倍。

A.10B.100C.10008.与0.8×0.15的积相等的算式是()。

A.0.8×1.5B.0.08×15C.0.08×1.5二.判断题(共8题,共16分)1.若A×4=360,则A×40=3600。

()2.一个不为0的数除以0.58,商小于被除数。

()3.1.28÷0.2的商与1.28×5的积相等。

()4.被除数乘0.6,除数除以0.6,商不变。

()5.小数除以小数,得数一定是小数。

()6.计算小数除法时,商的小数点与被除数的个位对齐。

()7.一个数除以0.01,也就是把这个数扩大100倍。

()8.7.57575755757是循环小数。

()三.填空题(共8题,共39分)1.通常情况下,竖排叫做(),横排叫做()。

确定第几列一般从()往()数,确定第几行一般从()往()数。

数对的第()个数字代表行,第()个数字代表列。

人教版六年级上册数学期中测试卷及参考答案(考试直接用)

人教版六年级上册数学期中测试卷一.选择题(共6题,共12分)1.下面各组数中,互为倒数的一组是()。

2.商店和学校都在广场的正南方,商店离广场500米,学校离广场200米,那么学校离商店()米。

A.300米B.500米C.700米3.篮球的价格比足球低,则足球价格是篮球价格的()。

A. B. C.4.下面()中两个数的积在和之间。

A.×B.×C.×55.小明家在小英家的北偏东40°方向上,则小英家在小明家的()方向上。

A.北偏东40°B.北偏西40°C.南偏东40°D.南偏西40°6.某班女生人数的等于男生人数的,那么男生人数()女生人数。

A.小于B.大于C.等于二.判断题(共6题,共12分)1.小优邮票的等于小华邮票的,小优的邮票一定多。

()2.小华面向正北方,顺时针原地旋转90°后小华面向正东方。

()3.×>。

()4.甲数等于乙数的,甲数比乙数小。

()5.5m的与7m的同样长。

()6.×就是求的是多少。

()三.填空题(共8题,共12分)1.快递员送快递,从一楼到二楼王老师家用了分钟,用同样的速度从一楼到五楼的李老师家要用________分钟。

2.一批货物重120吨,第一次运走全部的,第二次运走余下的,这批货物还剩()吨。

3.停车场停有15辆大客车,停有小客车的辆数比大客车多,停车场上小客车比大客车多(),小客车有()。

4.地球的表面积大约是51000万平方千米,其中约是海洋,其余的是陆地.地球上海洋的面积大约是(),陆地的面积大约是()。

5.我们计划铺设一条长2280米的地下管道,今天是第一天开工,就完成了全长的。

我们今天一共铺设了()米的管道。

6.根据×3=写出两道除法算式:()、()。

7.六(1)班学生人数在50~60之间,已知女生人数是男生人数的,那么女生有()人。

8.看图回答问题。

小学一年级上册数学期中测试卷附参考答案(完整版)

小学一年级上册数学期中测试卷一.选择题(共6题,共12分)1.最轻的小动物是()。

A. B. C.2.下图中哪个是圆柱?( )A. B. C.3.下面3个盒子里原来有几个果子不知道,如果往盒里各放1个、2个、3个果子,3个盒里的果子数就一样多了。

原来第()个盒里的果子最少。

A. B. C.4.最大的是()。

①② ③A.①B.②C.③5.硬币的上下两个面是()。

A.长方形B.圆形C.正方形6.哪根绳子最长?( )A. B. C.二.判断题(共6题,共12分)1.我的左面是小红,所以小红在我的右面。

()2.站在水边,人的倒影与人上下相反,左右相同。

()3.图中有3个小正方体。

()4.比多1个。

()5.乒乓球、足球、篮球的形状都是球。

()6.羽毛球是球体。

()三.填空题(共10题,共34分)1.教室里,讲桌在我的________面,我用________手写字。

2.填一填。

①3+()=3 ②()+4=5 ③0+()=53.图中有________ 双手套,有________ 只手套。

4.数数看。

________个圆柱________个球________个正方体。

5.100米赛跑中,第2名在第1名的()面,在第3名的()面。

6.看图,填一填各种图形的名称。

________ ________________ ________7.按顺序填数。

8.(1)小鸭在小猫的()面,猴在小鸡的()面。

(2)羽毛球拍和羽毛球在皮球的()面。

(3)小狗在第二层的最()面。

9.小明坐在第4行,小红坐在第3行,小明在小红的________面。

黑板在小明的________面,日光灯在小明的________面,讲台在小明的________面。

10.看图填空:四.计算题(共1题,共4分)1.看谁算得又对又快.(1)4+0=(2)4-2=(3)2+1=(4)0+3=(5)2-0=(6)5-2=(7)5-3=(8)1+4=五.作图题(共1题,共10分)1.圈一圈,涂一涂。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

注意:填空题必须抄题目,其他的三道题可以不抄题目。

一、填空题

1.冯·诺依曼结构的特点是_存储程序_。

2.主机由CPU和_主存储器_组成。

3.计算机系统由_硬件_系统和__软件__系统组成。

4.计算机系统的层次结构中,位于硬件之外的所有层次统称为__虚拟机器__。

5.计算机的存储器系统是指_Cache、主存储器和辅助存储器_。

6.设机器字长为32位,存储容量为16MB,若按双字编址,其寻址范围是_2M_。

7.存取速度最快的器件是_寄存器_。

8.若信息码字为11100011,生成多项式G(x)=x5+x4+x+1,则计算出的CRC校验码为1110001111010。

9.按照数据传送方式的不同,总线可分为_串行总线_和__并行总线___。

10. _单向总线只能将信息从总线的一端传到另一端,不能反向传输。

11. 在单机系统中,CPU向存储器写信息,通常采用_不互锁_类型的联络方式。

12.在多机系统中,某个CPU需访问共享存储器(仅所有CPU访问的存储器),通常采

用_半互锁_类型的联络方式实现通信。

13.存储器可分为主存和__辅存_,程序必须存于_主存_内,CPU才能执行其中的指令。

14. 一个32位的个人计算机,一个字节(Byte)由__8___位(bit)组成。

15.总线同步通信影响总线效率的原因是_必须按最慢速度的部件来设计公共时钟周期_。

16. _分离式_通信充分地利用了总线的有效占用,总线上所有模块都成为_主_模块。

17.在多级存储体系中,Cache的主要功能是_提高存储速度__,虚拟存储器的主要功能

是_扩大存储容量。

18.动态半导体存储器的刷新一般有_集中式_、_分散式_和__异步式_。

19.若RAM芯片内有1024个单元,用单译码方式,地址译码器有_1024_条输出线;

用双译码方式,地址译码器有__32___条输出线。

20.高速缓冲存储器中保存的信息是主存信息的_活跃块的副本__。

二、判断题(如果错误,请纠正)

1.存储程序的基本含义是将编好的程序和原始数据事先存入主存中。

√

2.计算机“运算速度”指标的含义是指每秒钟能执行多少条操作系统的命令。

×指的是每秒执行多少条指令或每秒执行多少次浮点运算。

3.一个16K×32位的存储器,其地址线和数据线的总和是46。

√

4.在同步通信中,一个总线周期的传输过程是:先传输数据,再传输地址。

×先地址后数据。

5.计算机存储数据的基本单位是字节(Byte)。

×位(bit)

6.邮局对信件进行自动分拣,使用的计算机技术是模式识别。

√

7.在三种集中式总线控制中,独立请求方式对电路故障最敏感。

×链式查询。

8.磁盘的盘面上有很多半径不同的同心圆,这些同心圆称为柱面。

×磁道

9.存取周期是指启动一次存储器操作到完成该操作所需的时间。

×

启动一次存储器操作到完成该操作所需的时间称为存取时间。

10. CPU访问主存储器的时间是由存储体的容量决定的,存储容量越大访问存储器所需

要时间就越长。

×CPU范围主存储器的时间与存储体的容量无关。

11.用1024×1芯片组成8KB存储器,CPU提供地址线A0~A15,其中A0为高位,则加

到各芯片地址端的地址线是A0~A9。

×

因为A0为高位,A15是低位,加到各芯片地址端的是地址线的低10位,为A6~A15。

12.一般情况下,ROM和RAM在存储体中是统一编址的。

√

13.集中刷新方式在刷新时间内并不影响CPU的读写操作。

×

集中刷新方式在刷新期间,CPU不能访问内存。

14. 在程序的执行过程中,Cache与主存的地址映射是由硬件自动完成的。

√

15. 用户编程的地址称为虚地址,通常虚地址的范围要比实地址大得多。

√

三、问答题

1.计算机的硬件是由哪些部件组成的?它们各自有哪些功能?

计算机的硬件由运算器、存储器、控制器、输入设备和输出设备五大基本部件组成。

它们各自的功能如下。

输入设备:把人们编好的程序和原始数据送到计算机中去,并且将它们转换成计算

机内部所能识别和接受的信息方式。

输出设备:将计算机的处理结果以人或其他设备所能接受的形式送出计算机。

存储器:用来存放程序和数据。

运算器:对信息进行处理和运算。

控制器:按照人们预先确定的操作步骤,控制整个计算机的各部件有条不紊地自动

工作。

2.某总线在一个总线周期中可并行传送8个字节数据,假设一个总线周期等于一个时钟周期,总线的时钟频率是66MHz,求总线的带宽。

8B/T =8B×f=8B×66MHz=528MBps

3.什么是总线判优?为什么需要总线判优?

总线判优是当总线上各个主设备同时要求占用总线时,通过总线控制器,按一定的

优先等级顺序确定某个主设备可以占有总线。

因为总线传输的特点是在某一时刻,只允许一个部件向总线发送信息,如果有两个以上的部件同时向总线发送信息,势

必导致信号冲突传输无效,故需用判优来解决。

4.什么是总线标准?为什么要定制总线标准?

总线标准是国际公布或推荐的互联各个模块的标准,这个标准为各模块互联提供一

个标准界面,这个界面对它两端的模块都是透明的,即界面的任一方只需根据总线

标准的要求完成自身一方接口的功能,而不必考虑对方与界面的接口方式。

指定总线标准使系统设计简化,便于模块生产批量化,确保其性能稳定,质量可靠,

实现可移化,便于维护等,较好地解决了系统、模块、设备与总线之间不适应、不

通用及不匹配等问题。

四、综合题

1.求有效信息位为01101110的海明校验码。

2.CPU执行一段程序,Cache完成存取的次数为1900次,主存完成存取的次数为100次,已知Cache存取周期为50ns,主存存取周期为250ns。

求:Cache-主存系统的命中率、平均访问时间和效率。

命中率为1900/(1900+100)=0.95

平均访问时间=50ns×0.95+250ns×(1-0.95)=60ns

设访问缓存的时间为t,访问主存的时间为5t,则:

效率=访问缓存时间/平均访问时间×100%=t/(0.95×t+(1-0.95) ×5t) ×100%=83.3%

3.已知地址总线A15~A0,其中A0是最低位。

用ROM芯片(4K×4)和RAM芯片(2K×8)组成一个半导体存储器,按字节编址。

该存储器ROM区的容量为16KB,RAM的容量为10KB。

问:(1)组成该存储器需要用多少块ROM芯片和RAM芯片?

(2)该存储器一共需要多少根地址线?ROM芯片、RAM芯片各需连入哪几根地址线?(3)需设置多少个片选信号,分别写出各片选信号的逻辑式。

4.某微机的寻址范围为64KB,其存储器选择器信号为M,接有8片8KB的存储器,试回答下列问题:(1)画出选片译码逻辑图;

(2)写出每片RAM的寻址范围;

(3)如果运行时发现不论往哪片存储器存放8KB数据,以A000H起始地址的存储芯片都有相同的数据,分析故障原因。

(4)若发现译码器中的地址线A13与CPU断线,并搭接到高电平的故障,问结果如何?5.设某主机容量32MB,cache容量为8KB。

每字块8个字,每字32位。

设计一个八路组相联映射的cache组织。

(1) 画出主存地址字段中各段的位数。

(2) 设Cache初态为空,CPU依次从主存0,1,2,…,99号单元中读出100个字(主存一次读出一个字),并重复8次,问命中率是多少?

(3)若cache速度是主存速度的4倍,试问有cache和无cache相比,速度提高多少倍?

(4)系统的效率是多少?。