数电实验考试 verilogHDL语言及参考程序

数字电路应用之Verilog HDL语言常用经典程序例题(Quartus II软件)

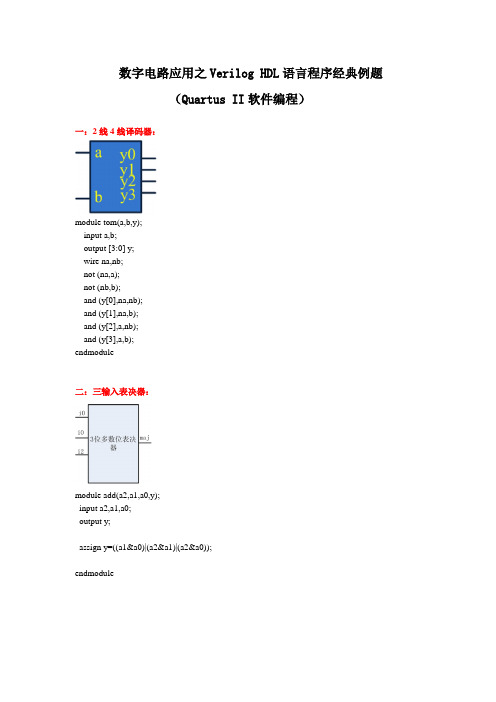

数字电路应用之Verilog HDL语言程序经典例题(Quartus II软件编程)一:2线4线译码器:module tom(a,b,y);input a,b;output [3:0] y;wire na,nb;not (na,a);not (nb,b);and (y[0],na,nb);and (y[1],na,b);and (y[2],a,nb);and (y[3],a,b);endmodule二:三输入表决器:module add(a2,a1,a0,y);input a2,a1,a0;output y;assign y=((a1&a0)|(a2&a1)|(a2&a0));endmodule三:3线8线译码器:module fulladd(a2,a1,a0,y);input a2,a1,a0;output [7:0] y;assign y[0]= ~( ~a2 & ~a1 & ~a0); assign y[1]= ~( ~a2 & ~a1 & a0); assign y[2]= ~( ~a2 & a1 & ~a0); assign y[3]= ~( ~a2 & a1 & a0); assign y[4]= ~( a2 & ~a1 & ~a0); assign y[5]= ~( a2 & ~a1 & a0); assign y[6]= ~( a2 & a1 & ~a0); assign y[7]= ~( a2 & a1 & a0);endmodule四:BIN2BCD码制转换:module fulladd(y,d,e);input [6:0] y;output [3:0] d,e;assign d=y/10;assign e=y%10;endmodule五:4位比较器:module tom(y,x,d);input [3:0] y,x;output [2:0] d;assign d[2]=(x>y)?1:0;assign d[1]=(x==y)?1:0;assign d[0]=(x<y)?1:0;endmodule六:四位全加器:法一:(调用程序法)module fulladd4(sum,c_in,c_out,a,b); output [3:0] sum;output c_out;input [3:0] a,b;input c_in;wire c1,c2,c3;fulladd fa0(sum[0],c1,a[0],b[0],c_in); fulladd fa1(sum[1],c2,a[1],b[1],c1); fulladd fa2(sum[2],c3,a[2],b[2],c2); fulladd fa3(sum[3],c_out,a[3],b[3],c3); endmodule//程序调用module fulladd(sum, c_out, a, b, c_in); output sum, c_out;input a, b, c_in;wire s1, c1, c2;xor (s1, a, b);and (c1, a, b);xor (sum, s1, c_in);and (c2, s1, c_in);xor (c_out, c2, c1);endmodule法二:(通用法)module fulladd4(A,B,Cin,SUM,Cout); input [3:0] A,B;input Cin;output [3:0] SUM;output Cout;assign {Cout,SUM}=A+B+Cin; endmodule七:七段显示译码器:法一:module bbc(a,d,g);input [3:0] a;output [6:0] d;output [3:0] g;reg [6:0] d;assign g=4'b0001;always @(a)begincase(a)4'b0000 :d=7'b100_0000;4'b0001 :d=7'b111_1001;4'b0010 :d=7'b010_0100;4'b0011 :d=7'b011_0000;4'b0100 :d=7'b001_1001;4'b0101 :d=7'b001_0010;4'b0110 :d=7'b000_0010;4'b0111 :d=7'b111_1000;4'b1000 :d=7'b000_0000;4'b1001 :d=7'b001_0000;default :d=7'b000_0000;endcaseendendmodule法二:module bbc(a,d,g);input [3:0] a;output [6:0] d;output [3:0] g;reg [6:0] d;assign g=4'b0001;always @(a)beginif (a==4'b0000) d=7'b100_0000;else if (a==4'b0001) d=7'b111_1001;else if (a==4'b0010) d=7'b010_0100;else if (a==4'b0011) d=7'b011_0000;else if (a==4'b0100) d=7'b001_1001;else if (a==4'b0101) d=7'b001_0010;else if (a==4'b0110) d=7'b000_0010;else if (a==4'b0111) d=7'b111_1000;else if (a==4'b1000) d=7'b000_0000;else if (a==4'b1001) d=7'b001_0000;else d=7'b000_0000; endendmodule八:8—3优先编码器:法一:module qq (y,d,g);input [7:0] y;output [2:0] d;output [3:0] g;reg [2:0] d;assign g=4'b0001;always @ ybeginif (y[7]==1) d=3'b111;else if (y[6]==1) d=3'b110;else if (y[5]==1) d=3'b101;else if (y[4]==1) d=3'b100;else if (y[3]==1) d=3'b011;else if (y[2]==1) d=3'b010;else if (y[1]==1) d=3'b001;else if (y[0]==1) d=3'b000;endendmodule法二:module encoder(none_on,outcode,a, b, c, d, e, f, g, h); output[2:0] outcode;output none_on;input a, b, c, d, e, f, g, h;reg[3:0] outtemp;assign {none_on, outcode} = outtemp;always @(a or b or c or d or e or f or g or h)begincasex ({a, b, c, d, e, f, g, h})8'B????_???1 : outtemp=4'b0_111;8'B????_??10 : outtemp=4'b0_110;8'B????_?100 : outtemp=4'b0_101;8'B????_1000 : outtemp=4'b0_100;8'B???1_0000 : outtemp=4'b0_011;8'B??10_0000 : outtemp=4'b0_010;8'B?100_0000 : outtemp=4'b0_001;8'B1000_0000 : outtemp=4'b0_000;8'B0000_0000 : outtemp=4'b1_000;endcaseendendmodule九:计数器:module bbc(clk,set,reset,d,y);input set,reset,clk;input [3:0] d;output [7:0] y;reg [7:0] y;always@(posedge clk or negedge reset or posedge set) if(~reset) y<=8'b0;else if (set) y[3:0]<=d[3:0];else y<=y+1'b1;endmodule十:移位寄存器:module asd (clk,set,reset,d,y,cin);input clk,set,reset,cin;input [3:0] d;output [7:0] y;reg [7:0] y;always@(posedge clk)beginif(~reset) y=0;else if(set)beginy[7:4]=y[3:0] ;y[3:0]=d[3:0];endelsebeginy=y<<1;y[0]=cin;endendendmodule十一:4位乘法:法一:module bbc(y,a,b);input [3:0] a;input [3:0] b;output [7:0] y;reg [7:0] y;reg[7:0] temp_a;reg[3:0] temp_b;integer i;always @(a or b)beginy=0;temp_a=a;temp_b=b;beginfor(i=0;i<=3;i=i+1)beginif(temp_b[0]) y=y+temp_a;temp_a=temp_a<<1;temp_b=temp_b>>1;endendendendmodule法二:module qq(outcome,a,b);output [8:1] outcome;input [4:1] a,b;reg [8:1] outcome;integer i;always@(a or b)beginoutcome=0;for(i=1;i<=4;i=i+1)if (b[1]) outcome=outcome + (a<<(i-1)); endendmodule十二:数码管跑马灯:module asd(cr,clk,a,b,c,d,e,f,g);input cr,clk;output a,b,c,d,e,f,g;reg a,b,c,d,e,f,g;integer i=0;always @ (posedge clk or negedge cr)beginif(~cr)begin{a,b,c,d,e,f,g}=7'b111_1111;i=0;endelse if(clk)begini=i+1;if(i==1) {a,b,c,d,e,f,g}=7'b011_1111;if(i==2) {a,b,c,d,e,f,g}=7'b101_1111;if(i==3) {a,b,c,d,e,f,g}=7'b110_1111;if(i==4) {a,b,c,d,e,f,g}=7'b111_0111;if(i==5) {a,b,c,d,e,f,g}=7'b111_1011;if(i==6) {a,b,c,d,e,f,g}=7'b111_1101;if(i==7) {a,b,c,d,e,f,g}=7'b111_1110;if(i==8) {a,b,c,d,e,f,g}=7'b000_0000;if(i==9)begin{a,b,c,d,e,f,g}=7'b111_1111;i=0;endendendendmodule十三:LED跑马灯:module add(cr,clk,y);input cr,clk;output [7:0] y;reg [7:0] y;integer i;always@(posedge clk or negedge cr) beginif(~cr)beginy=0;i=-1;endelse if (clk)begini=i+1;y=0;y[i]=1;beginif(i==7)i=-1;endendendendmodule。

VerilogHDL实验报告

VerilogHDL实验报告实验一Modelsim仿真软件的使用一、实验目的(1)熟悉Modelsim 软件(2)掌握Modelsim 软件的编译、仿真方法(3)熟练运用Modelsim 软件进行HDL 程序设计开发二、实验内容1、实验要求用Verilog HDL 程序实现一个异或门,Modelism仿真,观察效果。

2、步骤1、建立工程2、添加文件到工程3、编译文件4、查看编译后的设计单元5、将信号加入波形窗口6、运行仿真3、方法moduleyihuo (a,b,c);inputa,b;output c;assign c=a^b;endmodule测试程序:module t_yihuo;reg a,b; wire c;initial begin a=0; forever #20 a=~a; end initial begin b=0; forever #30 b=~b; endyihuou1(a,b,c);endmodule二、实验结果波形图:三、分析和心得通过这次的实验,我基本熟悉Modelsim软件,掌握了Modelsim软件的编译、仿真方法。

同时在编写程序的过程中,加深了我对课上所讲的HDL的语法的认识。

实验二简单组合电路设计一、实验目的(1)掌握基于Modelsim的数字电路设计方法(2)熟练掌握HDL 程序的不同实现方法二、实验内容1、实验要求设计一个三人表决器(高电平表示通过),实验内容如下:(1)三个人,一个主裁判,两个副裁判;(2)规则:只要主裁判同意,输出结果为通过;否则,按少数服从多数原则决定是否通过。

使用 Verilog HDL 程序实现上述实验内容,并使用modelsim 仿真。

2、方法module test(a,b,c,s);inputa,b,c;output s;assign s=c|(b&a);endmodulemodulet_test;rega,b,c;wire s;initialbegina=0;forever#10 a=~a;endinitialbeginb=0;forever #20 b=~b;endinitialbeginc=0;forever#40 c=~c;endtest u1(a,b,c,s);endmodule三、实验结果四、分析和心得通过本次实验,我掌握基于Modelsim的简单数字电路设计方法,且尝试了用不同方法实现功能,三人表决器可以通过testbench测试程序实现,也可以利用always模块实现,可见程序的设计思想是很重要的。

veriloghdl程序大全

1.简单门电路的设计二输入与非门module nand_2(y,a,b);output y;input a,b;nand(y,a,b);endmodule二输入异或门module nand_2(y,a,b);output y;input a,b;reg y;always @(a,b)begincase({a,b})2’b00:y=1;2’b01:y=1;2’b10:y=1;2’b11:y=0;default:y=’bx;endcaseendendmodule二输入三态门module eda_santai(dout,din,en); output dout;input din,en;reg dout;alwaysif (en) dout<=din;else dout<=’bz;endmodule3-8译码器的设计module yimaqi(S1,S2,S3,A,Y); input S1;wire S1;input S2;wire S2;input S3;wire S3;input [2:0]A;wire [2:0]A;output[7:0]Y;reg [7:0]Y;reg s;always@(S,S1,S2,S3)begins<=S2|S3;Y <=8'b1111_1111;else if(S)Y <=8'b1111_1111;elsecase(A)3'b000:Y<=11111110;3'b001:Y<=11111101;3'b010:Y<=11111011;3'b011:Y<=11110111;3'b100:Y<=11101111;3'b101:Y<=11011111;3'b110:Y<=10111111;3'b111:Y<=01111111;endcaseendendmodule2.8-3编码器的设计module banjiaqi(a,b,count,sum);input a;wire a;input b;wire b;output count;wire count;output sum;wire sum;assign {count,sum}=a+b;endmodule4. D触发器的设计module Dchufaqi ( Q ,CLK ,RESET ,SET ,D ,Qn ); input CLK ;wire CLK ;input RESET ;wire RESET ;input SET ;wire SET ;input D ;wire D ;output Q ;reg Q ;output Qn ;wire Qn ;assign Qn = ~Q ;always @ ( posedge CLK or negedge SET or negedge RESET ) beginif ( !RESET)Q <= 0 ;else if ( ! SET)Q <= 1;else Q <= D;endendmodule5. 1位半加法器的设计module banjiafaqi(a,b,sum,count);input a;wire a;input b;wire b;output sum;wire sum;output count;wire count;assign {count,sum}=a+b;endmodule6. 4位计数器的设计module sihisjishuqi(CLK,RESET,out);input CLK;wire CLK;input RESET;wire RESET;output[3:0] out;reg[3:0] out;always @ ( posedge CLK or negedge RESET )beginif(!RESET)out<=4'b0000;elsebeginout<=out+1;if(out==4'b1010)out<=4'b0000;endendendmodule7.分频时序逻辑电路的设计module eda_fp_even(clk_out,clk_in,rst); input clk_in;input rst;wire rst;output clk_out;reg clk_out;reg [1:0]cnt;parameter N=6;always @(posedge clk_in or negedge rst) beginif(!rst)beginclk_out<=0;cnt<=0;endelsebegincnt<=cnt+1;if(cnt==N/2-1)beginclk_out=!clk_out;cnt<=0;endendendendmodule8.7段显示译码器的设计module eda_scan_seven(clk,dig,y,rst); input clk;wire clk;input rst;wire rst;output[7:0] dig;wire[7:0] dig;output [7:0]y;wire [7:0]y;reg clkout;reg [19:0]cnt;reg [2:0]wei;reg [3:0]duan;reg [6:0]Y_r;reg [7:0]dig_r;assign y = {1'b1,(~Y_r[6:0])};assign dig =~dig_r;parameter period= 1000000;always@(posedge clk or negedge rst) beginif(!rst)cnt<=0;else begincnt<=cnt+1;if(cnt==(period>>1)-1)clkout<=#1 1'b1;else if(cnt==period-1)beginclkout<=#1 1'b0;cnt<=#1 1'b0;endendendalways@(posedge clkout or negedge rst ) beginif(!rst)wei<=0;elsewei<=wei+1;endalways @(wei) //数码管选择begincase ( wei )3'b000 :begindig_r <= 8'b0000_0001;duan <= 1;end3'b001 :begindig_r <= 8'b0000_0010;duan<= 3;end3'b010 :begindig_r <= 8'b0000_0100;duan<= 5;end3'b011 :begindig_r <= 8'b0000_1000;duan <= 7;end3'b100 :begindig_r <= 8'b0001_0000;duan<= 9;end3'b101 :begindig_r <= 8'b0010_0000;duan<= 11;end3'b110 :begindig_r <= 8'b0100_0000;duan <= 13;end3'b111 :begindig_r <= 8'b1000_0000;duan<= 15;endendcaseendalways @ ( duan ) //译码begincase ( duan )0: Y_r = 7'b0111111; // 01: Y_r = 7'b0000110; // 12: Y_r = 7'b1011011; // 23: Y_r = 7'b1001111; // 34: Y_r = 7'b1100110; // 45: Y_r = 7'b1101101; // 56: Y_r = 7'b1111101; // 67: Y_r = 7'b0100111; // 78: Y_r = 7'b1111111; // 89: Y_r = 7'b1100111; // 910: Y_r = 7'b1110111; // A11: Y_r = 7'b1111100; // b12: Y_r = 7'b0111001; // c13: Y_r = 7'b1011110; // d14: Y_r = 7'b1111001; // E15: Y_r = 7'b1110001; // Fdefault: Y_r = 7'b0000000;endcaseendendmodule9.数据选择器的设计module eda_8xuanyi (A,D0,D1,D2,D3,D4,D5,D6,D7,G,Y); input D0,D1,D2,D3,D4,D5,D6,D7,G;input [2:0]A;wire [2:0]A;output Y;reg Y;always @(A, G)beginif (G==0)Y<=0;elsecase(A)3'b000:Y=D0;3'b001:Y=D1;3'b010:Y=D2;3'b011:Y=D3;3'b100:Y=D4;3'b101:Y=D5;3'b110:Y=D6;3'b111:Y=D7;endcaseendendmodule10.数据锁存器的设计module e da_suocunqi(q,d,oen,g); output[7:0] q;//数据输出端input[7:0] d;//数据输入端input oen,g;//三态控制端reg[7:0] q;always @(*)beginif (oen)beginq<="z";endelsebeginif(g)q<=d;elseq<=q;endendendmodule11.数据寄存器的设计module eda_jicunqi(r,clk,d,y); input r,clk;input [7:0]d;wire [7:0]d;output [7:0]y;reg [7:0]y;always @ (posedge clk or negedge r) beginif(!r)y<=8'b00000000;elsey<=d;endendmodule12.顺序脉冲发生器的设计module eda_shunxu(clk,clr,q);input clk,clr;output [7:0]q;reg [7:0]q;always @ ( posedge clk or posedge clr ) beginif ( clr==1)beginq<=8'b00000000; //赋初值endelsebeginif(q==0)q<=8'b00000001;elseq<=q<<1; //给初值进行移位endendendmodule13.1位全加法器的设计module quanjiaqi(a,b,sum,count,cin); input a;wire a;input b;wire b;input cin;wire cin;output sum;wire sum;output count;wire count;assign{sum,count}=a+b+cin; endmodule15.键控Led灯的设计module eda_led(led,key);input key;output led;reg led_out;assign led<=led_out;always@(key)beginif(key)led_out<=1;else if(!key)led_out<=0;endendmodule16.双向移位寄存器的设计module eda_yiweijicunqi( left_right ,load ,clr ,clk ,DIN ,DOUT );input left_right ;wire left_right ;input load ;wire load ;input clr ;wire clr ;input clk ;wire clk ;input [3:0] DIN ;wire [3:0] DIN ;output [3:0] DOUT ;wire [3:0] DOUT ;reg [3:0] data_r;assign DOUT = data_r ;always @ (posedge clk or posedge clr or posedge load)//敏感变量,看真值表beginif(clr==1)data_r <= 0;//判断是否清零else if (load )data_r<=DIN;//判断是否装载数据//判断进行左移位还是右移位elsebeginif(left_right)data_r<=DIN<<1;elsedata_r<=DIN>>1;endendendmodule17.8-3优先编码器的设计module youxianbianma( A ,I ,GS ,EO ,EI ); input [7:0] I ;wire [7:0] I ;input EI ;wire EI ;output [2:0] A ;reg [2:0] A ;output GS ;reg GS ;output EO ;reg EO ;always @ ( I or EI )if ( EI )beginA <= 3'b111;GS <= 1;EO <= 1;endelse if (I==8'b11111111)beginA <= 3'b111;GS <= 1;EO <= 0;endelse if ( I==8'b11111110 )beginA <= 3'b111;GS <= 0;EO <= 1;endelse if ( I==8'b1111110x )beginA <= 3'b110;GS <= 0;EO <= 1;endelse if ( I==8'b111110xx )beginA <= 3'b101;GS <= 0;EO <= 1;endelse if ( I==8'b11110xxx )beginA <= 3'b100;GS <= 0;EO <= 1;endelse if ( I==8'b1110xxxx )beginA <= 3'b011;GS <= 0;EO <= 1;endelse if ( I==8'b110xxxxx )beginA <= 3'b010;GS <= 0;EO <= 1;endelse if ( I==8'b10xxxxxx )beginA <= 3'b001;GS <= 0;EO <= 1;endelse if ( I==8'b0xxxxxxx )beginA <= 3'b000;GS <= 0;EO <= 1;endendmodule18.数据分配器的设计module shujufenpeiqi(y0,y1,y2,y3,din,a); output y0,y1,y2,y3;//4??êy?Yí¨μàinput din;//êy?Yê?è?input [1:0] a;reg y0,y1,y2,y3;always @(din,a)beginy0=0;y1=0;y2=0;y3=0; //3?ê??ˉ£á?case(a)00:y0=din;01:y1=din;02:y2=din;03:y3=din;endcase end endmodule。

Verilog HDL 实验报告

Verilog实验报告班级:学号:姓名:实验1 :用 Verilog HDL 程序实现直通线1 实验要求:(1) 编写一位直通线的 Veirlog HDL 程序.(2) 编写配套的测试基准.(3) 通过 QuartusII 编译下载到目标 FPGA器件中进行验证.(4) 建议用模式 52 试验程序:module wl(in,out);input in;output out;wire out;assign out=in;endmodule3 测试基准:`include “wl.v”module wl_tb;reg in_tb;wire out_tb;initialbeginin_tb =0;#100 in_tb =1;#130 in_tb =0;endendmodule4 仿真图形:实验2 :用 Verilog HDL 程序实现一位四选一多路选择器1实验要求:(1) 编写一位四选一多路选择器的 Veirlog HDL 程序.(2) 编写配套的测试基准.(3) 通过 QuartusII 编译下载到目标 FPGA器件中进行验证.(4)建议用模式 52 试验程序:module mux4_to_1 (out,i0,i1,i2,i3,s1,s0);output out;input i0,i1,i2,i3;input s1, s0;reg out;always @ (s1 or s0 or i0 or i1 or i2 or i3)begincase ({s1, s0})2'b00: out=i0;2'b01: out=i1;2'b10: out=i2;2'b11: out=i3;default: out=1'bx;endcaseendendmodule3 测试基准:`include "mux4_to_1.v"module mux4_to_1_tb1;reg ain,bin,cin,din;reg[1:0] select;reg clock;wire outw;initialbeginain=0;bin=0;cin=0;din=0;select=2'b00;clock=0;endalways #50 clock=~clock;always @(posedge clock)begin#1 ain={$random} %2;#3 bin={$random} %2;#5 cin={$random} %2;#7 din={$random} %2;endalways #1000 select[0]=!select[0];always #2000 select[1]=!select[1];mux4_to_1 m(.out(outw),.i0(ain),.i1(bin),.i2(cin),.i3(din),.s1(select[1]),.s0(select[0])); endmodule4 仿真图形:实验3:用 Verilog HDL 程序实现十进制计数器1实验要求:(1) 编写十进制计数器的 Veirlog HDL 程序. 有清零端与进位端, 进位端出在输出为 9 时为高电平.(2) 编写配套的测试基准.(3) 通过 QuartusII 编译下载到目标 FPGA器件中进行验证.(4) 自行选择合适的模式2 实验程序:module counter_10c (Q, clock, clear, ov);output [3:0] Q;output ov;input clock, clear;reg [3:0] Q;reg ov;initial Q=4'b0000;always @ (posedge clear or negedge clock)beginif (clear)Q<=4'b0;else if (Q==8)beginQ<=Q+1;ov<=1'b1;endelse if (Q==9)beginQ<=4'b0000;ov<=1'b0;endelsebeginQ<=Q+1;ov<=1'b0;endendendmodule3 测试基准:`include"./counter_10c.v"module counter_10c_tb;wire[3:0] D_out;reg clk,clr;wire c_out;reg[3:0] temp;initialbeginclk=0;clr=0;#100 clr=1;#20 clr=0;endalways #20 clk=~clk;counter_10c m_1(.Q(D_out),.clear(clr),.clock(clk),.ov(c_out)); endmodule4 仿真波形:实验4 :用 Verilog HDL 程序实现序列检测器1 实验要求:、(1) 编写序列检测器的 Veirlog HDL 程序. 检测串行输入的数据序列中是否有目标序列5'b10010, 检测到指定序列后, 用一个端口输出高电平表示.(2) 编写配套的测试基准.(3) 通过 QuartusII 编译下载到目标 FPGA器件中进行验证.(4) 自行选择合适的模式2试验程序:module e15d1_seqdet( x, z, clk, rst);input x,clk, rst;output z;reg [2:0] state;wire z;parameter IDLE = 3 'd0,A = 3'd1,B = 3'd2,C = 3'd3,D = 3'd4,E = 3'd5,F = 3'd6,G = 3'd7;assign z =(state==D && x==0)?1:0;always @(posedge clk or negedge rst)if(!rst)beginstate<=IDLE;endelsecasex(state)IDLE: if(x==1)state<=A;else state<=IDLE;A: if (x==0)state<=B;else state<=A;B: if (x==0)state<=C;else state<=F;C: if(x==1)state<=D;else state<=G;D: if(x==0)state<=E;else state<=A;E: if(x==0)state<=C;else state<=A;F: if(x==1)state<=A;else state<=B;G: if(x==1)state<=F;else state <=G;default: state<=IDLE;endcaseendmodule3测试基准:`include"e15d1_seqdet.v"`timescale 1ns/1ns`define halfperiod 20module e15d1_seqdet_tb;reg clk, rst;reg [23:0] data;wire z;reg x;initialbeginclk =0;rst =1;#2 rst =0;#30 rst =1;data= 20 'b1100_1001_0000_1001_0100;#(`halfperiod*1000) $stop;endalways #(`halfperiod) clk=~clk;always @ (posedge clk)begin#2 data={data[22:0],data[23]};x=data[23];ende15d1_seqdet m(.x(x),.z(z),.clk(clk),.rst(rst)); endmodule4仿真波形:。

Verilog HDL数字设计实训教程第1章 Verilog HDL数字设计实训基础

图1-2 按键电路连接图和管脚对应图

1.1 实训平台

4个LED灯:

图1-3 LED电路连接图和管脚对应图

1.1 实训平台

2个数码管:

图1-4 数码管电路连接图和管脚对应图

1块液晶:

1.1 实训平台

图1-5 液晶电路连接图和管脚对应图

1个UART:

1.1 实训平台

图1-6 UART电路连接图和管脚对应图

if(p==N-1) begin p=0; clk_p=~clk_p; end else p=p+1; end always @(negedge clk) begin

if(q==N-1) q=0; else q=q+1;

if(p==(N-1)/2) clk_q=~clk_q; end assign clk_N=clk_p^clk_q; endmodule

图1-39 设置USB硬件端口

QuartusII设计流程

5.引脚锁定和硬件验证

图1-40 下载界面

QuartusII设计流程

5.引脚锁定和硬件验证

图1-41 选择下载文件

QuartusII设计流程

5.引脚锁定和硬件验证

图1-42 led灯闪烁的效果

1.3 分频器设计

分频器电路是非常有用的一种电路, 分频的方法很多,最常见的是利用加 法计数器对时钟信号进行分频。

begin if(p==N/2-1) begin p=0; clk_N=~clk_N; end else p=p+1;

end endmodule

图1-44 任意偶数分频仿真波形

1.3 分频器设计

【例1-5】 可设置参数的任意整数分频器:占空比可变。 module divf_parameter(rst,clk,en,clkout); input rst,clk,en; output clkout; integer temp; //最大值为2的32次方 parameter N=7,M=3; //N为分频系数,M/N为占空比 always @(posedge clk)

数电仿真Modelsim设计实验报告VerilogHDL语言

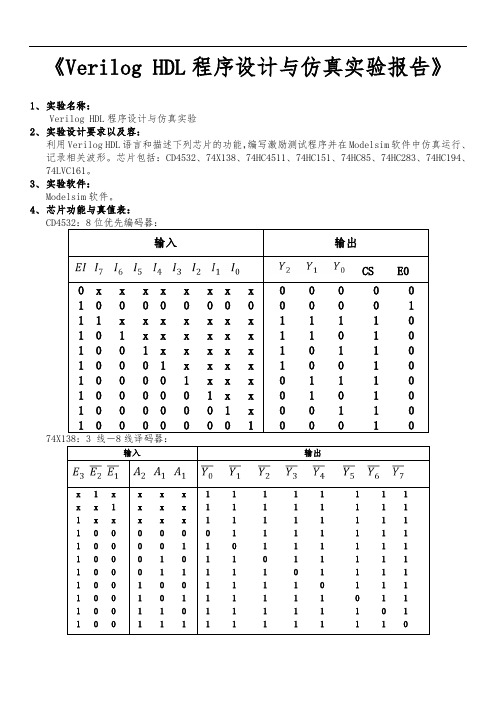

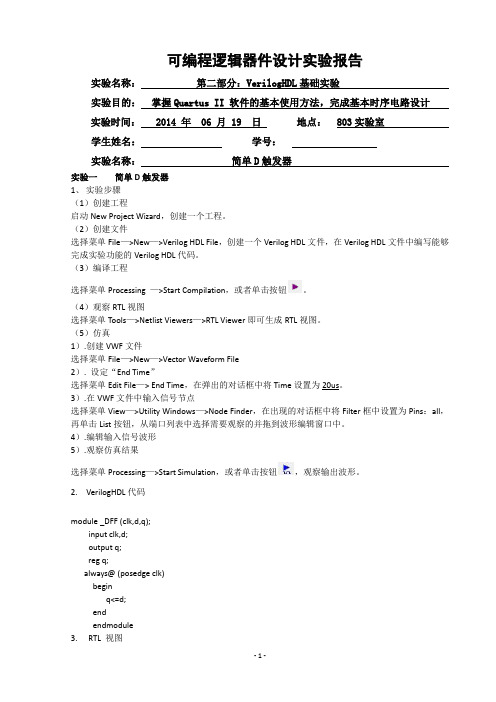

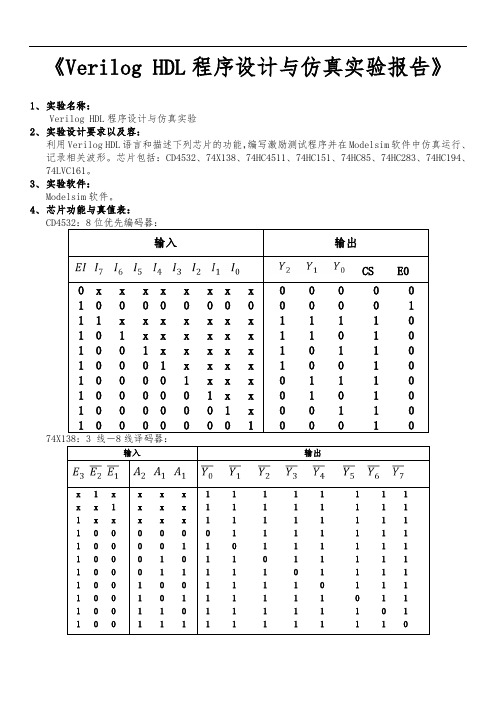

《Verilog HDL程序设计与仿真实验报告》1、实验名称:Verilog HDL程序设计与仿真实验2、实验设计要求以及容:利用Verilog HDL语言和描述下列芯片的功能,编写激励测试程序并在Modelsim软件中仿真运行、记录相关波形。

芯片包括:CD4532、74X138、74HC4511、74HC151、74HC85、74HC283、74HC194、74LVC161。

3、实验软件:Modelsim软件。

4、芯片功能与真值表:输入输出CS E00 x x x x x x x x1 0 0 0 0 0 0 0 01 1 x x x x x x x1 0 1 x x x x x x1 0 0 1 x x x x x1 0 0 0 1 x x x x1 0 0 0 0 1 x x x1 0 0 0 0 0 1 x x1 0 0 0 0 0 0 1 x1 0 0 0 0 0 0 0 10 0 0 0 00 0 0 0 11 1 1 1 01 1 0 1 01 0 1 1 01 0 0 1 00 1 1 1 00 1 0 1 00 0 1 1 00 0 0 1 0输入输出x 1 xx x 11 x x1 0 01 0 01 0 01 0 01 0 01 0 01 0 01 0 0x x xx x xx x x0 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 11 1 1 1 1 1 1 11 1 1 1 1 1 1 11 1 1 1 1 1 1 10 1 1 1 1 1 1 11 0 1 1 1 1 1 11 1 0 1 1 1 1 11 1 1 0 1 1 1 11 1 1 1 0 1 1 11 1 1 1 1 0 1 11 1 1 1 1 1 0 11 1 1 1 1 1 1 074HC4511:七段显示译码器:十进制或功能输入输出字形LE a b c d e f g0 1 2 3 4 5 6 7 8 9101112131415 01111111111111111111111111111111100 0 00 0 0 100 1 000 1 10 1 0 00 1 0 10 1 1 00 1 1 110 0 01 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 11 1 1 1 1 1 00 1 1 0 0 0 01 1 0 1 1 0 11 1 1 1 0 0 10 1 1 0 0 1 11 0 1 1 0 1 10 0 1 1 1 1 01 1 1 0 0 0 01 1 1 1 1 1 11 1 1 1 0 1 10 0 0 0 0 0 00 0 0 0 0 0 00 0 0 0 0 0 00 0 0 0 0 0 00 0 0 0 0 0 00 0 0 0 0 0 0123456789熄灭熄灭熄灭熄灭熄灭熄灭灯测试x x 0 x x x x 1 1 1 1 1 1 1 8 灭灯x 0 1 x x x x 0 0 0 0 0 0 0 熄灭锁存 1 1 1 x x x x * *输入输出使能选择Y1 0 0 0 0 0 0 0 x x x0 0 00 0 10 1 00 1 11 0 01 0 11 1 00 10 1 1 174HC85:4位数值比较器:74HC283:4位二进制全加器:输入输出功能清零控制信号时钟串行输入并行输入CR CP 右移左移LHHHHx xL LL HL HH Lxx↑↑↑x xx xL xH xx Lx x x xx x x xx x x xx x x xx x x xL L L LLHH H H LH H↑↑x Hx xx x x x74LVC161:4位二进制同步计数器:输入输出清零CR 预支PE使能C E P C E T时钟CP预支数据输入进位TCL H H H H xLHHHx xx xL xx LH Hx↑xx↑x x x xx x x xx x x xx x x xL L L L保持保持保持L##L#5、实验具体设计:CD4532-8位优先编码器:模块设计代码:module CD4532(EI,I,Y,GS,EO);//8位优先编码器input EI;input [7:0] I;output reg [2:0] Y;output reg GS,EO;always (EI,I)beginif(EI==0) begin Y=3'd0; GS=0; EO=0; endelse//当EI=1时,实现优先编码器的功能beginGS=1; EO=0;//当编码器输入信号有效时,设定GS、EO的输出值if(I[7]) Y=3'd7; else//根据I的高位情况对Y的输出进行控制if(I[6]) Y=3'd6; elseif(I[5]) Y=3'd5; elseif(I[4]) Y=3'd4; elseif(I[3]) Y=3'd3; elseif(I[2]) Y=3'd2; elseif(I[1]) Y=3'd1; elseif(I[0]) Y=3'd0;elsebegin Y=3'd0; GS=0; EO=1; end//当编码器输入信号无效时,设定GS、EO的输出值 endendendmodule对应testbench设计代码:`timescale 1ns/1ns //设定仿真时间间隔单位,之后的testbench中这句代码功能类似module CD4532_tb;reg [7:0] D_in;// 设定testbench输入数据类型为reg型 reg EI_in;wire [2:0] Q_result;// / 设定testbench输出数据类型为wire型wire GS_result,EO_result;initialbeginEI_in=0;//初始化相关数据的值D_in=8'b0000_0001;#80 EI_in=1;#80 $stop();//上一个语句执行完毕后的80个时间单位后仿真终止endalways #10 //每隔10个时间单位执行一次beginif(D_in==8'b1000_0000)D_in=8'b0000_0001;elseD_in=(D_in<<1);endCD4532 U1(.EI(EI_in),.I(D_in),.Y(Q_result),.GS(GS_result),.EO(EO_result)); endmodule74X138-3 线-8线译码器:模块设计代码:module _74X138(A,EN,Y);//3 线-8线译码器,输出为低电平有效input [2:0] A;input EN;//使能端output reg [7:0] Y;integer k;always (A,EN)beginY=8'b1111_1111;for(k=0;k<=7;k=k+1)beginif((EN==1)&&(A==k))Y[k]=0;//EN=1时根据输入的A进行译码elseY[k]=1;//使能无效时或输入无效endendendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74X138_tb;reg [2:0] A_in;reg EI_in;wire [7:0] Y_result;initialbeginEI_in=0;A_in=3'b000;#80 EI_in=1;#160 $stop();endalways #10beginif(A_in==3'b111)A_in=3'b000;elseA_in=A_in+1;end_74X138 U1(.A(A_in),.EN(EI_in),.Y(Y_result));endmodule74HC4511-七段显示译码器:模块设计代码:module _74HC4511(D,LE,BL,LT,a,b,c,d,e,f,g);//七段显示译码器input [3:0] D;//输入信号端口input LE,BL,LT;//控制信号output reg a,b,c,d,e,f,g;always(LE,BL,LT,D)beginif(LT==0) {a,b,c,d,e,f,g}=7'b111_1111;//显示器全亮else if(BL==0) {a,b,c,d,e,f,g}=7'b000_0000;//显示器全灭else if(LE==0) {a,b,c,d,e,f,g}={a,b,c,d,e,f,g};//显示器保持当前显示elsecase(D)//根据输入的8421BCD码进行译码4'd0: {a,b,c,d,e,f,g}=7'b111_1110;//04'd1: {a,b,c,d,e,f,g}=7'b011_0000;//14'd2: {a,b,c,d,e,f,g}=7'b110_1101;//24'd3: {a,b,c,d,e,f,g}=7'b111_1001;//34'd4: {a,b,c,d,e,f,g}=7'b011_0011;//44'd5: {a,b,c,d,e,f,g}=7'b101_1011;//54'd6: {a,b,c,d,e,f,g}=7'b001_1111;//64'd7: {a,b,c,d,e,f,g}=7'b111_0000;//74'd8: {a,b,c,d,e,f,g}=7'b111_1111;//84'd9: {a,b,c,d,e,f,g}=7'b111_1011;//9default:{a,b,c,d,e,f,g}=7'b000_0000;//非8421BCD码输入时,不译码 endcaseendendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74HC4511_tb;reg [3:0] D_in;reg LE_in,BL_in,LT_in;wire A,B,C,D,E,F,G;initialbegin//开始为全亮LE_in=1;//保持,低电平有效BL_in=1;//全灭,低电平有效LT_in=0;//全亮,低电平有效D_in=4'b0000;#100 begin LE_in=1; BL_in=0; LT_in=1; end//全灭#100 begin LE_in=1; BL_in=1; LT_in=1; end//正常显示 #100 begin LE_in=0; BL_in=1; LT_in=1; end//保持#100 $stop();endalways #10beginif(D_in==4'd9)D_in=4'b0000;elseD_in=D_in+1;end_74HC4511 U1(D_in,LE_in,BL_in,LT_in,A,B,C,D,E,F,G); endmodule74HC151-八选一数据选择器:模块设计代码:module _74HC151(S,D,E,Y0,Y1);//八选一数据选择器input [2:0] S;//控制信号input [7:0] D;//输入信号input E;//使能端output reg Y0,Y1;//Y0,Y1分别为同相和反相输出信号always(E,S,D)beginif(~E)begin Y0=0; Y1=1; end//不工作,输出默认信号elsebegincase(S)//根据控制信号选择不同通道的输入信号作为输出3'b000: begin Y0=D[0]; Y1=~Y0; end//03'b001: begin Y0=D[1]; Y1=~Y0; end//13'b010: begin Y0=D[2]; Y1=~Y0; end//23'b011: begin Y0=D[3]; Y1=~Y0; end//33'b100: begin Y0=D[4]; Y1=~Y0; end//43'b101: begin Y0=D[5]; Y1=~Y0; end//53'b110: begin Y0=D[6]; Y1=~Y0; end//63'b111: begin Y0=D[7]; Y1=~Y0; end//7default: begin Y0=0; Y1=~Y0; end//若控制信号不符合要求则输出默认信号endcaseendendendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74HC151_tb;reg [2:0] S_in;reg [7:0] D_in;reg E_in;wire Y0_result,Y1_result;initialbeginE_in=0;S_in=3'b000;D_in=8'b0010_0110;#80 E_in=1;#80 D_in=8'b1001_1110;#80 E_in=0;#80 $stop();endalways #10beginif(S_in==3'b111)S_in=3'b000;elseS_in=S_in+1;end_74HC151 U1(S_in,D_in,E_in,Y0_result,Y1_result);Endmodule74HC85-4位数值比较器:模块设计代码:module _74HC85(A,B,I0,I1,I2,Fab0,Fab1,Fab2);//4位数值比较器,以下均为高电平有效 input [3:0] A,B;//输入信号input I0,I1,I2;//低位比较结果,依次为低位A=B,A<B,A>Boutput reg Fab0,Fab1,Fab2;//输出信号Fab0,Fab1,Fab2依次为A=B,A<B,A>B.reg F000,F001,F002,F110,F111,F112,F220,F221,F222,F330,F331,F332;//中间节点,依次对应Ai=Bi,Ai<Bi,Ai>Bi.i为位数(0~3)always(A,B,I0,I1,I2)beginif(A[3]>B[3])//比较第4位begin F330=0; F331=0; F332=1; endelse if(A[3]<B[3])begin F330=0; F331=1; F332=0; endelsebegin F330=1; F331=0; F332=0; endif(A[2]>B[2])//比较第3位begin F220=0; F221=0; F222=1; endelse if(A[2]<B[2])begin F220=0; F221=1; F222=0; endelsebegin F220=1; F221=0; F222=0; endif(A[1]>B[1])//比较第2位begin F110=0; F111=0; F112=1; endelse if(A[1]<B[1])begin F110=0; F111=1; F112=0; endelsebegin F110=1; F111=0; F112=0; endif(A[0]>B[0])//比较第1位begin F000=0; F001=0; F002=1; endelse if(A[0]<B[0])begin F000=0; F001=1; F002=0; endelsebegin F000=1; F001=0; F002=0; end//输出结果如下if((F000&&F110&&F220&&F330)&&I0)//低位进位信号出错begin Fab2=0; Fab1=0; Fab0=1; endelse if((F000&&F110&&F220&&F330)&&(~I0&&I1&&I2))//低位进位信号出错begin Fab2=0; Fab1=0; Fab0=0; endelse if((F000&&F110&&F220&&F330)&&(~I0&&~I1&&~I2))//低位进位信号出错begin Fab2=1; Fab1=1; Fab0=0; endelse//低位进位信号正常beginFab2=F332||F330&&F222||F330&&F220&&F112||F330&&F220&&F110&&F002||F330&&F220&&F110&&F000&&I2;Fab1=F331||F330&&F221||F330&&F220&&F111||F330&&F220&&F110&&F001||F330&&F220&&F110&&F000&&I1;Fab0=F330&&F220&&F110&&F000&&I0;endendendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74HC85_tb;reg [3:0] A_in,B_in;reg I0_in,I1_in,I2_in;wire Fab0_result,Fab1_result,Fab2_result;initialbeginI0_in=0;I1_in=0;I2_in=0;A_in=4'b1010;B_in=4'b0111;#10 begin I0_in=1; I1_in=0; I2_in=0; end//低位A=B#10 begin I0_in=0; I1_in=1; I2_in=0; end//低位A<B#10 begin I0_in=0; I1_in=0; I2_in=1; end//低位A>B#10 begin I0_in=0; I1_in=0; I2_in=0; //低位归位A_in=4'b0100; B_in=4'b1001; end#10 begin I0_in=1; I1_in=0; I2_in=0; end//低位A=B#10 begin I0_in=0; I1_in=1; I2_in=0; end//低位A<B#10 begin I0_in=0; I1_in=0; I2_in=1; end//低位A>B#10 begin I0_in=0; I1_in=0; I2_in=0; //低位归位A_in=4'b0010; B_in=4'b0010; end#10 begin I0_in=1; I1_in=0; I2_in=0; end//低位A=B#10 begin I0_in=0; I1_in=1; I2_in=0; end//低位A<B#10 begin I0_in=0; I1_in=0; I2_in=1; end//低位A>B#10 $stop();end_74HC85 U1(A_in,B_in,I0_in,I1_in,I2_in,Fab0_result,Fab1_result,Fab2_result); endmodule74HC283-4位二进制全加器:模块设计代码:module _74HC283(A,B,Ci,Co,S);//4位二进制全加器input Ci;//低位进位信号input [3:0] A,B;//输入信号output reg [3:0] S;//输出结果output reg Co;//高位进位信号Co=C[3]reg [3:0] C,G,P;integer k;always(A,B,Ci)beginfor(k=0;k<4;k=k+1)beginG[k]=A[k]&&B[k];P[k]=A[k]&&~B[k]||~A[k]&&B[k];endC[0]=G[0]||P[0]&&Ci;C[1]=G[1]||P[1]&&C[0];C[2]=G[2]||P[2]&&C[1];C[3]=G[3]||P[3]&&C[2];S[0]=P[0]&&~Ci||~P[0]&&Ci;S[1]=P[1]&&~C[0]||~P[1]&&C[0];S[2]=P[2]&&~C[1]||~P[2]&&C[1];S[3]=P[3]&&~C[2]||~P[3]&&C[2];Co=C[3];endendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74HC283_tb;reg [3:0] A_in,B_in;reg Ci_in;//低位进位信号wire [3:0] S_out;//本位相加结果wire Co_out;//高位进位信号initialbeginCi_in=0;A_in=4'b1010;B_in=4'b0111;#10 begin A_in=4'b0011; B_in=4'b1111; end#10 begin A_in=4'b0101; B_in=4'b1001; end#10 begin A_in=4'b1111; B_in=4'b0010; end#10 $stop();endalways #5beginCi_in=~Ci_in;//循环改变低位进位信号end_74HC283 U1(A_in,B_in,Ci_in,Co_out,S_out);endmodule74HC194-4位双向移位寄存器:模块设计代码:module _74HC194(S0,S1,Dsl,Dsr,CP,CR,D,Q);//4位双向移位寄存器_P339 input S0,S1;//输入端口input Dsr,Dsl;//串行数据输入input CP,CR;//时钟和清零input [3:0] D;//并行数据输入output reg [3:0] Q;//输出结果always(posedge CP, negedge CR)beginif(~CR) Q<=4'b0000;//异步清零elsecase({S1,S0})2'b00:Q<=Q;//输出保持不变2'b01:Q<={Q[2:0],Dsr};//右移,低位移向高位2'b10:Q<={Dsl,Q[3:1]};//左移,高位移向低位2'b11:Q<=D;//并行置数endcaseendendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74HC194_tb;reg [3:0] D_in;//并行数据输入reg S0_in,S1_in;//控制信号输入端口reg Dsr_in,Dsl_in;//串行数据输入reg CP_in,CR_in;//时钟和清零,清零为低电平有效wire [3:0] Q_out;//输出结果initialbeginCP_in=1;CR_in=1;S0_in=1;S1_in=1;//开始先输入串行数据Dsr_in=0;Dsl_in=0;D_in=4'b0110;#243 CR_in=~CR_in;#20 $stop();endalways #5beginCP_in=~CP_in;//周期为10ns的时钟信号endalways #15//循环调整控制输入信号,周期60nsbegincase({S1_in,S0_in})2'b00:begin S1_in=0; S0_in=1; end2'b01:begin S1_in=1; S0_in=0; end2'b10:begin S1_in=1; S0_in=1; end2'b11:begin S1_in=0; S0_in=0; endendcaseendalways #10//循环调整串行数据输入信号,周期40nsbegincase({Dsr_in,Dsl_in})2'b00:begin Dsr_in=0; Dsl_in=1; end2'b01:begin Dsr_in=1; Dsl_in=0; end2'b10:begin Dsr_in=1; Dsl_in=1; end2'b11:begin Dsr_in=0; Dsl_in=0; endendcaseend_74HC194 U1(S0_in,S1_in,Dsl_in,Dsr_in,CP_in,CR_in,D_in,Q_out);endmodule74LVC161-4位二进制同步计数器:模块设计代码:module _74LVC161(CEP,CET,PE,CP,CR,D,TC,Q);//4位二进制同步计数器_P340 input CEP,CET,PE,CP,CR;//输入端口input [3:0] D;//并行数据输入output TC;//进位输出output reg [3:0] Q;//输出结果wire CE;assign CE=CEP&CET;//CE=1时计数器计数assign TC=CET&PE&(Q==4'b1111);//产生进位输出信号always(posedge CP, negedge CR)beginif(~CR) Q<=4'b0000;//异步清零else if(~PE) Q<=D;//PE=0,同步输入数据else if(CE)beginif((TC==1)&&(Q==4'b1111))Q<=4'b0000;//计数器计满后自动归零elseQ<=Q+1'b1;//加1计数endelse Q<=Q;//保持输出不变endendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74LVC161_tb;reg CEP_in,CET_in,PE_in,CP_in,CR_in;//输入端口reg [3:0] D_in;//并行数据输入wire TC_out;//进位输出wire [3:0] Q_out;//输出结果initialbeginCEP_in=0;CET_in=1;PE_in=0;CP_in=1;CR_in=1;D_in=4'b1101;#10 begin PE_in=1;D_in=4'b1001; end#20 begin CEP_in=1; CET_in=1; end#220 begin PE_in=0; end#23 CR_in=~CR_in;#20 $stop();endalways #5beginCP_in=~CP_in;//周期为10ns的时钟信号end_74LVC161 U1(CEP_in,CET_in,PE_in,CP_in,CR_in,D_in,TC_out,Q_out);endmodule6、输出仿真波形以及相关数据:CD4532-8位优先编码器:以下波形由上至下依次是:D_in, EI_in, Q_result, GS_result, EO_result;74X138-3 线-8线译码器:以下波形由上至下依次是:A_in, EI_in, Y_result;74HC4511-七段显示译码器:以下波形由上至下依次是:D_in, LE_in, LT_in, A, B, C, D, E, F, G;74HC151-八选一数据选择器:以下波形由上至下依次是:S_in, D_in, E_in, Y0_result, Y1_result;74HC85-4位数值比较器:以下波形由上至下依次是:A_in, B_in, I0_in, I1_in, I2_in, Fab0_result, Fab1_result, Fab2_result;74HC283-4位二进制全加器:以下波形由上至下依次是:A_in, B_in, S_out, Co_out;74HC194-4位双向移位寄存器:以下波形由上至下依次是:D_in, S0_in, S1_in,Dsr_in, Dsl_in, CP_in, CR_in, Q_out;74LVC161-4位二进制同步计数器:以下波形由上至下依次是:CEP_in, CET_in, PE_in, CP_in, CR_in, D_in, T_out, Q_out;7、仿真结果分析:仿真输出波形符合预期,与芯片的功能表描述的功能相符。

verilog hdl实验报告

verilog hdl实验报告《Verilog HDL实验报告》Verilog HDL(硬件描述语言)是一种用于描述电子系统的硬件的语言,它被广泛应用于数字电路设计和硬件描述。

本实验报告将介绍Verilog HDL的基本概念和使用方法,并通过实验展示其在数字电路设计中的应用。

实验目的:1. 了解Verilog HDL的基本语法和结构2. 掌握Verilog HDL的模块化设计方法3. 熟悉Verilog HDL的仿真和综合工具的使用实验内容:1. Verilog HDL的基本语法和结构Verilog HDL是一种硬件描述语言,其语法和结构类似于C语言。

它包括模块定义、端口声明、信号赋值等基本元素。

在本实验中,我们将学习如何定义Verilog模块,并使用端口声明和信号赋值描述数字电路的行为。

2. Verilog HDL的模块化设计方法Verilog HDL支持模块化设计,可以将复杂的电路分解为多个模块,每个模块描述一个子电路的行为。

在本实验中,我们将学习如何设计和实现Verilog模块,并将多个模块组合成一个完整的数字电路。

3. Verilog HDL的仿真和综合工具的使用Verilog HDL可以通过仿真工具进行功能验证,也可以通过综合工具生成实际的硬件电路。

在本实验中,我们将使用Verilog仿真工具对设计的数字电路进行功能验证,并使用综合工具生成对应的硬件电路。

实验步骤:1. 学习Verilog HDL的基本语法和结构2. 设计一个简单的数字电路,并实现Verilog模块描述其行为3. 使用仿真工具对设计的数字电路进行功能验证4. 使用综合工具生成对应的硬件电路实验结果:通过本实验,我们学习了Verilog HDL的基本概念和使用方法,并成功设计和实现了一个简单的数字电路。

我们使用仿真工具对设计的数字电路进行了功能验证,并使用综合工具生成了对应的硬件电路。

实验结果表明,Verilog HDL在数字电路设计中具有重要的应用价值。

数字电子技术基础Verilog语言编程设计习题

数字电子技术基础Verilog语言编程设计习题Verilog语言是数字电子技术中广泛应用的硬件描述语言,本文将介绍一些基础的Verilog编程设计习题。

通过完成这些习题,读者能够加深对数字电子技术和Verilog语言的理解,并提高Verilog编程的能力。

一、多输入多输出逻辑门设计习题1. 设计一个四位全加器,实现任意两个四位二进制数的相加运算功能。

module full_adder(input [3:0] A,input [3:0] B,input Cin,output [3:0] S,output Cout);wire [3:0] sum;assign sum[0] = A[0] ^ B[0] ^ Cin;assign sum[1] = A[1] ^ B[1] ^ (A[0] & B[0]) ^ Cin;assign sum[2] = A[2] ^ B[2] ^ (A[1] & B[1]) ^ (A[0] & B[0]) ^ Cin;assign sum[3] = A[3] ^ B[3] ^ (A[2] & B[2]) ^ (A[1] & B[1]) ^ (A[0] & B[0]) ^ Cin;assign S = sum;assign Cout = (A[3] & B[3]) ^ (A[2] & B[2]) ^ (A[1] & B[1]) ^ (A[0] & B[0]) ^ Cin;endmodule2. 设计一个八位比较器,判断两个八位二进制数是否相等。

module comparator(input [7:0] A,input [7:0] B,output EQ);wire [7:0] difference;assign difference = A ^ B;assign EQ = (difference[7] | difference[6] | difference[5] | difference[4] | difference[3] | difference[2] | difference[1] | difference[0])==0;endmodule二、时序逻辑电路设计习题1. 设计一个六位计数器,实现每秒钟加一功能。

数字系统设计与Verilog HDL实验报告(二)

《数字系统设计与Verilog HDL》实验报告(二)班级:自动1003班姓名:**学号:********实验二、四位并串转换电路一、实验目的1、了解及掌握时序电路的基本结构常用数字电路;2、通过ModelSim软件编写时序电路的程序进行仿真和调试。

二、实验内容1、熟悉时序电路中时钟的同步与异步用法;2、编写一个四位并串转换设计程序以及测试该模块的测试程序,要求如下:(1)输入一个四位二进制数pin;(2)每个时钟周期按从左往右的顺序输出一位pin的二进制位的数。

三、实验步骤及源程序新建工程及文件,分别添加设计程序及测试程序,进行编译及纠错,编译通过后运行程序仿真进行调试得出结果。

设计模块:module para_to_serial4(pin,clk,reset,sout);input [3:0] pin;input clk,reset;output sout;reg sout;reg [3:0] data;always @(posedge clk or negedge reset)beginif(~reset)beginsout<=1'b0;data<=pin;endelsebegindata<={data[2:0],data[3]};sout<=data[3];endendendmodule测试模块:`timescale 1ns/1nsmodule test_para_to_ser;wire sout;reg [3:0] pin;reg clk,reset;para_to_serial4 test1(pin,clk,reset,sout);initialbeginclk=1'b0;reset=1'b0;#5 reset=1'b1;#300 $stop;endinitialpin=4'b1001;always#5 clk=~clk;endmodule四、实验结果五、实验心得体会这次试验相对于上次有了一定的难度,由于这门课程刚开始学习,我还不能很好地从宏观把握这门课程,对这门课程的认识和理解还不够深刻,所以做实验时遇到了一些困难,虽然找了一些参考资料,有一定的帮助,但最后还是有点纠结,最终在和同学的交流中才比较深刻的对实验有了了解。

实验二、Verilog HDL输入方法

实验二十六进制7段数码显示译码器设计

一、实验目的:

1、了解利用EDA 软件及开发系统进行可编程器件设计的一般流程;

2、掌握基本组合电路的Verilog/VHDL文本设计方法,及进行下载验证。

学习7段数码显示译码器的Verilog/VHDL硬件设计。

二、实验原理

译码器即是把输入的数据转换成对应的输出码。

例如:BCD 数至7 段显示译码器,要执行的操作就是把一个 4 位的BCD 码转换成7 个显示段码输出,以便在7 段数码管上显示出这个十进制数。

对如图2-1 所示7 段共阴数码管,要设计该译码器的必须条件,就是要列出输入码与输出码之间的对应关系即真值表。

如表2-1 所示,根据真值表可以直接用查表法来设计,应用Verilog/VHDL译码程序在FPGA中来实现。

该程序可按照教材中例3-2的case 语句表述方法。

如果要考虑表示小数点的发光管,需要增加段h,然后将LED7S 改为8位输出。

三、实验原理框图

四、实验任务

1、应用case 语句等编写Verilog/VHDL 七段显示器译码程序。

2、进行编辑、编译、综合、适配、仿真,给出所有信号的仿真波形(要求:用输入总线的方式给出输出信号的仿真波形)

3、硬件测试:选用LEDC,进行引脚锁定及硬件测试、验证译码器的工作状态和性能。

五、实验报告

1、预习报告:写出该实验的基本设计思路及源程序;

2、实验报告:写出经调试通过的实验程序及实验步骤、软件编译及仿真

分析、硬件测试和实验过程、程序分析报告、仿真波形图及结果分析。

Verilog_HDL教程

Verilog_HDL教程

1.简介

Verilog HDL是由美国电气和电子工程师协会(IEEE)于1984年开

发的一种硬件描述语言。

它是一种面向数据流的语言,主要用于描述数字

逻辑电路的行为和结构。

Verilog HDL可以用于设计和仿真各种数字电路,如计算机处理器、存储器、控制逻辑和通信接口等。

2.基本语法

下面是Verilog HDL的基本语法元素:

2.1模块

模块是Verilog HDL中的最基本的构建单元。

每个模块都有一个名称

和一个端口列表。

端口可以是输入或输出,也可以是双向的。

2.2数据类型

2.3信号赋值

可以使用赋值运算符(=)将值赋给变量或信号。

还可以使用阻塞或

非阻塞赋值运算符来实现顺序或并发的赋值操作。

3.设计结构

4.运算符

5.仿真和验证

总结:

本教程简要介绍了Verilog HDL的基本语法和用法。

Verilog HDL是一种被广泛应用于数字电路设计的硬件描述语言。

通过学习本教程,您将能够开始使用Verilog HDL进行数字电路的设计和验证。

数电实验考试 verilogHDL语言及参考程序

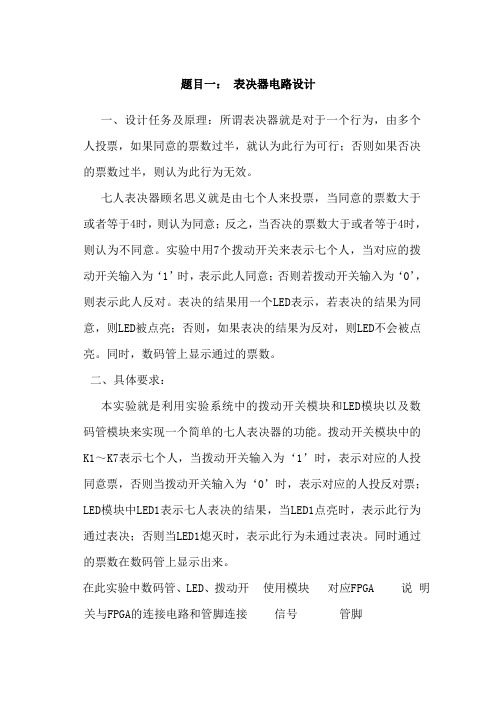

题目一:表决器电路设计一、设计任务及原理:所谓表决器就是对于一个行为,由多个人投票,如果同意的票数过半,就认为此行为可行;否则如果否决的票数过半,则认为此行为无效。

七人表决器顾名思义就是由七个人来投票,当同意的票数大于或者等于4时,则认为同意;反之,当否决的票数大于或者等于4时,则认为不同意。

实验中用7个拨动开关来表示七个人,当对应的拨动开关输入为‘1’时,表示此人同意;否则若拨动开关输入为‘0’,则表示此人反对。

表决的结果用一个LED表示,若表决的结果为同意,则LED被点亮;否则,如果表决的结果为反对,则LED不会被点亮。

同时,数码管上显示通过的票数。

二、具体要求:本实验就是利用实验系统中的拨动开关模块和LED模块以及数码管模块来实现一个简单的七人表决器的功能。

拨动开关模块中的K1~K7表示七个人,当拨动开关输入为‘1’时,表示对应的人投同意票,否则当拨动开关输入为‘0’时,表示对应的人投反对票;LED模块中LED1表示七人表决的结果,当LED1点亮时,表示此行为通过表决;否则当LED1熄灭时,表示此行为未通过表决。

同时通过的票数在数码管上显示出来。

在此实验中数码管、LED、拨动开关与FPGA的连接电路和管脚连接使用模块信号对应FPGA管脚说明在以前的实验中都做了详细说明,这里不在赘述。

端口名S1 按键开关S1 R16 表示1号抢答者S2 按键开关S2 P14 表示2号抢答者S3 按键开关S3 P16 表示3号抢答者S4 按键开关S4 P15 表示4号抢答者S5 按键开关S5 M15 表示5号抢答者S6 按键开关S6 N16 表示6号抢答者S7 按键开关S7 N15 表示7号抢答者DOUT0 LED模块D1 L14 表决结果亮为通过LEDAG0 数码管模块A段N4 抢答成功者号码显示LEDAG1 数码管模块B段G4LEDAG2 数码管模H4块C段参考答案:module liu(s,dout0,ledag);input [6:0]s;output dout0;output [6:0]ledag;reg [6:0]led;reg [2:0]k;reg clk_en;reg dout;always @(s)begink<=s[1]+s[2]+s[3]+s[4]+s[5]+s[6]+s[0];if(k>=4)begindout<=1;endelsebegindout<=0;endendalways@(k)begincase (k)3'd0:led<=7'b0111111;3'd1:led<=7'b0000110;3'd2:led<=7'b1011011;3'd3:led<=7'b1001111;3'd4:led<=7'b1100110;3'd5:led<=7'b1101101;3'd6:led<=7'b1111101;3'd7:led<=7'b0000111;default:led<=7'b0000000;endcaseendassignledag=led;assigndout0=dout;endmodule题目二:数字电子实验设计题目:彩灯循环电路设计一、设计任务及原理:所谓彩灯循环就是对于一组彩灯(16盏),通过不同的工作模式可按照一定的规律来点亮或者熄灭。

数电仿真Modelsim设计实验报告-Verilog-HDL语言

¥《Verilog HDL程序设计与仿真实验报告》1、实验名称:Verilog HDL程序设计与仿真实验2、实验设计要求以及内容:利用Verilog HDL语言和描述下列芯片的功能,编写激励测试程序并在Modelsim软件中仿真运行、记录相关波形。

芯片包括:CD4532、74X138、74HC4511、74HC151、74HC85、74HC283、74HC194、74LVC161。

3、实验软件:Modelsim软件。

4、?5、芯片功能与真值表:!74HC85:4位数值比较器:、74HC283:4位二进制全加器:6、实验具体设计:CD4532-8位优先编码器:模块设计代码:moduleCD4532(EI,I,Y,GS,EO);I(EI_in),.I(D_in),.Y(Q_result),.GS(GS_result),.EO(EO_result));、endmodule74X138-3 线-8线译码器:模块设计代码:module _74X138(A,EN,Y);(A_in),.EN(EI_in),.Y(Y_result));endmodule74HC4511-七段显示译码器:《模块设计代码:module _74HC4511(D,LE,BL,LT,a,b,c,d,e,f,g);reg F000,F001,F002,F110,F111,F112,F220,F221,F222,F330,F331,F332;//中间节点,依次对应Ai=Bi,Ai<Bi,Ai>为位数(0~3)always@(A,B,I0,I1,I2)beginif(A[3]>B[3])//比较第4位begin F330=0; F331=0; F332=1; endelse if(A[3]<B[3])begin F330=0; F331=1; F332=0; end)elsebegin F330=1; F331=0; F332=0; endif(A[2]>B[2])//比较第3位begin F220=0; F221=0; F222=1; endelse if(A[2]<B[2])begin F220=0; F221=1; F222=0; endelsebegin F220=1; F221=0; F222=0; end*if(A[1]>B[1])//比较第2位begin F110=0; F111=0; F112=1; endelse if(A[1]<B[1])begin F110=0; F111=1; F112=0; endelsebegin F110=1; F111=0; F112=0; endif(A[0]>B[0])//比较第1位begin F000=0; F001=0; F002=1; end%else if(A[0]<B[0])begin F000=0; F001=1; F002=0; endelsebegin F000=1; F001=0; F002=0; end//输出结果如下if((F000&&F110&&F220&&F330)&&I0)//低位进位信号出错begin Fab2=0; Fab1=0; Fab0=1; endelse if((F000&&F110&&F220&&F330)&&(~I0&&I1&&I2))//低位进位信号出错}begin Fab2=0; Fab1=0; Fab0=0; endelse if((F000&&F110&&F220&&F330)&&(~I0&&~I1&&~I2))//低位进位信号出错begin Fab2=1; Fab1=1; Fab0=0; endelse//低位进位信号正常beginFab2=F332||F330&&F222||F330&&F220&&F112||F330&&F220&&F110&&F002||F330&&F220&&F110&&F000&&I2;Fab1=F331||F330&&F221||F330&&F220&&F111||F330&&F220&&F110&&F001||F330&&F220&&F110&&F000&&I1;Fab0=F330&&F220&&F110&&F000&&I0;end>endendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74HC85_tb;reg [3:0] A_in,B_in;reg I0_in,I1_in,I2_in;wire Fab0_result,Fab1_result,Fab2_result;¥initialbeginI0_in=0;I1_in=0;I2_in=0;A_in=4'b1010;B_in=4'b0111;#10 begin I0_in=1; I1_in=0; I2_in=0; end//低位A=B、#10 begin I0_in=0; I1_in=1; I2_in=0; end//低位A<B#10 begin I0_in=0; I1_in=0; I2_in=1; end//低位A>B#10 begin I0_in=0; I1_in=0; I2_in=0; //低位归位A_in=4'b0100; B_in=4'b1001; end#10 begin I0_in=1; I1_in=0; I2_in=0; end//低位A=B#10 begin I0_in=0; I1_in=1; I2_in=0; end//低位A<B#10 begin I0_in=0; I1_in=0; I2_in=1; end//低位A>B#10 begin I0_in=0; I1_in=0; I2_in=0; //低位归位~A_in=4'b0010; B_in=4'b0010; end#10 begin I0_in=1; I1_in=0; I2_in=0; end//低位A=B#10 begin I0_in=0; I1_in=1; I2_in=0; end//低位A<B#10 begin I0_in=0; I1_in=0; I2_in=1; end//低位A>B#10 $stop();end_74HC85 U1(A_in,B_in,I0_in,I1_in,I2_in,Fab0_result,Fab1_result,Fab2_result); endmodule—74HC283-4位二进制全加器:模块设计代码:module _74HC283(A,B,Ci,Co,S);//4位二进制全加器input Ci;//低位进位信号input [3:0] A,B;//输入信号output reg [3:0] S;//输出结果output reg Co;//高位进位信号Co=C[3]>reg [3:0] C,G,P;integer k;always@(A,B,Ci)beginfor(k=0;k<4;k=k+1)beginG[k]=A[k]&&B[k];P[k]=A[k]&&~B[k]||~A[k]&&B[k];]endC[0]=G[0]||P[0]&&Ci;C[1]=G[1]||P[1]&&C[0];C[2]=G[2]||P[2]&&C[1];C[3]=G[3]||P[3]&&C[2];S[0]=P[0]&&~Ci||~P[0]&&Ci;S[1]=P[1]&&~C[0]||~P[1]&&C[0];S[2]=P[2]&&~C[1]||~P[2]&&C[1];~S[3]=P[3]&&~C[2]||~P[3]&&C[2];Co=C[3];endendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74HC283_tb;reg [3:0] A_in,B_in;【reg Ci_in;//低位进位信号wire [3:0] S_out;//本位相加结果wire Co_out;//高位进位信号initialbeginCi_in=0;A_in=4'b1010;B_in=4'b0111;(#10 begin A_in=4'b0011; B_in=4'b1111; end#10 begin A_in=4'b0101; B_in=4'b1001; end#10 begin A_in=4'b1111; B_in=4'b0010; end #10 $stop();endalways #5beginCi_in=~Ci_in;//循环改变低位进位信号{end_74HC283 U1(A_in,B_in,Ci_in,Co_out,S_out);endmodule74HC194-4位双向移位寄存器:模块设计代码:module _74HC194(S0,S1,Dsl,Dsr,CP,CR,D,Q);//4位双向移位寄存器_P339 input S0,S1;//输入端口,input Dsr,Dsl;//串行数据输入input CP,CR;//时钟和清零input [3:0] D;//并行数据输入output reg [3:0] Q;//输出结果always@(posedge CP, negedge CR)beginif(~CR) Q<=4'b0000;//异步清零else<case({S1,S0})2'b00:Q<=Q;//输出保持不变2'b01:Q<={Q[2:0],Dsr};//右移,低位移向高位2'b10:Q<={Dsl,Q[3:1]};//左移,高位移向低位2'b11:Q<=D;//并行置数endcaseendendmodule?对应testbench设计代码:`timescale 1ns/1nsmodule _74HC194_tb;reg [3:0] D_in;//并行数据输入reg S0_in,S1_in;//控制信号输入端口reg Dsr_in,Dsl_in;//串行数据输入reg CP_in,CR_in;//时钟和清零,清零为低电平有效wire [3:0] Q_out;//输出结果¥initialbeginCP_in=1;CR_in=1;S0_in=1;S1_in=1;//开始先输入串行数据Dsr_in=0;Dsl_in=0;&D_in=4'b0110;#243 CR_in=~CR_in;#20 $stop();endalways #5beginCP_in=~CP_in;//周期为10ns的时钟信号end)always #15//循环调整控制输入信号,周期60nsbegincase({S1_in,S0_in})2'b00:begin S1_in=0; S0_in=1; end2'b01:begin S1_in=1; S0_in=0; end2'b10:begin S1_in=1; S0_in=1; end2'b11:begin S1_in=0; S0_in=0; endendcase(endalways #10//循环调整串行数据输入信号,周期40nsbegincase({Dsr_in,Dsl_in})2'b00:begin Dsr_in=0; Dsl_in=1; end2'b01:begin Dsr_in=1; Dsl_in=0; end2'b10:begin Dsr_in=1; Dsl_in=1; end2'b11:begin Dsr_in=0; Dsl_in=0; end|endcaseend_74HC194 U1(S0_in,S1_in,Dsl_in,Dsr_in,CP_in,CR_in,D_in,Q_out);endmodule74LVC161-4位二进制同步计数器:模块设计代码:module _74LVC161(CEP,CET,PE,CP,CR,D,TC,Q);//4位二进制同步计数器_P340 ]input CEP,CET,PE,CP,CR;//输入端口input [3:0] D;//并行数据输入output TC;//进位输出output reg [3:0] Q;//输出结果wire CE;assign CE=CEP&CET;//CE=1时计数器计数assign TC=CET&PE&(Q==4'b1111);//产生进位输出信号always@(posedge CP, negedge CR)beginif(~CR) Q<=4'b0000;//异步清零else if(~PE) Q<=D;//PE=0,同步输入数据else if(CE)beginif((TC==1)&&(Q==4'b1111))Q<=4'b0000;//计数器计满后自动归零elseQ<=Q+1'b1;//加1计数endelse Q<=Q;//保持输出不变endendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74LVC161_tb;reg CEP_in,CET_in,PE_in,CP_in,CR_in;//输入端口reg [3:0] D_in;//并行数据输入wire TC_out;//进位输出wire [3:0] Q_out;//输出结果initialbeginCEP_in=0;CET_in=1;PE_in=0;CP_in=1;CR_in=1;D_in=4'b1101;#10 begin PE_in=1;D_in=4'b1001; end#20 begin CEP_in=1; CET_in=1; end#220 begin PE_in=0; end#23 CR_in=~CR_in;#20 $stop();endalways #5beginCP_in=~CP_in;//周期为10ns的时钟信号end_74LVC161 U1(CEP_in,CET_in,PE_in,CP_in,CR_in,D_in,TC_out,Q_out);endmodule7、输出仿真波形以及相关数据:CD4532-8位优先编码器:以下波形由上至下依次是:D_in, EI_in, Q_result, GS_result, EO_result;74X138-3 线-8线译码器:以下波形由上至下依次是:A_in, EI_in, Y_result;74HC4511-七段显示译码器:以下波形由上至下依次是:D_in, LE_in, LT_in, A, B, C, D, E, F, G;74HC151-八选一数据选择器:以下波形由上至下依次是:S_in, D_in, E_in, Y0_result, Y1_result;74HC85-4位数值比较器:以下波形由上至下依次是:A_in, B_in, I0_in, I1_in, I2_in, Fab0_result, Fab1_result, Fab2_result;74HC283-4位二进制全加器:以下波形由上至下依次是:A_in, B_in, S_out, Co_out;74HC194-4位双向移位寄存器:以下波形由上至下依次是:D_in, S0_in, S1_in,Dsr_in, Dsl_in, CP_in, CR_in, Q_out;74LVC161-4位二进制同步计数器:以下波形由上至下依次是:CEP_in, CET_in, PE_in, CP_in, CR_in, D_in, T_out, Q_out;8、仿真结果分析:仿真输出波形符合预期,与芯片的功能表描述的功能相符。

VerilogHDL基础实验可编程实验报告

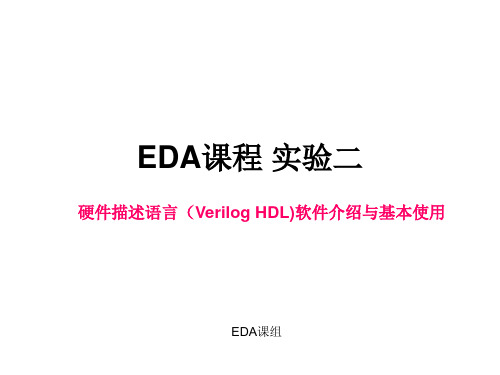

可编程逻辑器件设计实验报告实验名称:第二部分:VerilogHDL基础实验实验目的:掌握Quartus II 软件的基本使用方法,完成基本时序电路设计实验时间: 2014 年 06 月 19 日地点: 803实验室学生姓名:学号:实验名称:简单D触发器实验一简单D触发器1、实验步骤(1)创建工程启动New Project Wizard,创建一个工程。

(2)创建文件选择菜单File—>New—>Verilog HDL File,创建一个Verilog HDL文件,在Verilog HDL文件中编写能够完成实验功能的Verilog HDL代码。

(3)编译工程选择菜单Processing —>Start Compilation,或者单击按钮。

(4)观察RTL视图选择菜单Tools—>Netlist Viewers—>RTL Viewer即可生成RTL视图。

(5)仿真1).创建VWF文件选择菜单File—>New—>Vector Waveform File2). 设定“End Time”选择菜单Edit File—> End Time,在弹出的对话框中将Time设置为20us。

3).在VWF文件中输入信号节点选择菜单View—>Utility Windows—>Node Finder,在出现的对话框中将Filter框中设置为Pins:all,再单击List按钮,从端口列表中选择需要观察的并拖到波形编辑窗口中。

4).编辑输入信号波形5).观察仿真结果选择菜单Processing—>Start Simulation,或者单击按钮,观察输出波形。

2. VerilogHDL代码module _DFF (clk,d,q);input clk,d;output q;reg q;always@ (posedge clk)beginq<=d;endendmodule3. RTL 视图4.仿真波形实验二同步置数的D触发器1.实验步骤(1)创建工程启动New Project Wizard,创建一个工程。

数电仿真Modelsim设计实验报告VerilogHDL语言

《Verilog HDL程序设计与仿真实验报告》1、实验名称:Verilog HDL程序设计与仿真实验2、实验设计要求以及容:利用Verilog HDL语言和描述下列芯片的功能,编写激励测试程序并在Modelsim软件中仿真运行、记录相关波形。

芯片包括:CD4532、74X138、74HC4511、74HC151、74HC85、74HC283、74HC194、74LVC161。

3、实验软件:Modelsim软件。

4、芯片功能与真值表:输入输出CS E00 x x x x x x x x1 0 0 0 0 0 0 0 01 1 x x x x x x x1 0 1 x x x x x x1 0 0 1 x x x x x1 0 0 0 1 x x x x1 0 0 0 0 1 x x x1 0 0 0 0 0 1 x x1 0 0 0 0 0 0 1 x1 0 0 0 0 0 0 0 10 0 0 0 00 0 0 0 11 1 1 1 01 1 0 1 01 0 1 1 01 0 0 1 00 1 1 1 00 1 0 1 00 0 1 1 00 0 0 1 0输入输出x 1 xx x 11 x x1 0 01 0 01 0 01 0 01 0 01 0 01 0 01 0 0x x xx x xx x x0 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 11 1 1 1 1 1 1 11 1 1 1 1 1 1 11 1 1 1 1 1 1 10 1 1 1 1 1 1 11 0 1 1 1 1 1 11 1 0 1 1 1 1 11 1 1 0 1 1 1 11 1 1 1 0 1 1 11 1 1 1 1 0 1 11 1 1 1 1 1 0 11 1 1 1 1 1 1 074HC4511:七段显示译码器:十进制或功能输入输出字形LE a b c d e f g0 1 2 3 4 5 6 7 8 9101112131415 01111111111111111111111111111111100 0 00 0 0 100 1 000 1 10 1 0 00 1 0 10 1 1 00 1 1 110 0 01 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 11 1 1 1 1 1 00 1 1 0 0 0 01 1 0 1 1 0 11 1 1 1 0 0 10 1 1 0 0 1 11 0 1 1 0 1 10 0 1 1 1 1 01 1 1 0 0 0 01 1 1 1 1 1 11 1 1 1 0 1 10 0 0 0 0 0 00 0 0 0 0 0 00 0 0 0 0 0 00 0 0 0 0 0 00 0 0 0 0 0 00 0 0 0 0 0 0123456789熄灭熄灭熄灭熄灭熄灭熄灭灯测试x x 0 x x x x 1 1 1 1 1 1 1 8 灭灯x 0 1 x x x x 0 0 0 0 0 0 0 熄灭锁存 1 1 1 x x x x * *输入输出使能选择Y1 0 0 0 0 0 0 0 x x x0 0 00 0 10 1 00 1 11 0 01 0 11 1 00 10 1 1 174HC85:4位数值比较器:74HC283:4位二进制全加器:输入输出功能清零控制信号时钟串行输入并行输入CR CP 右移左移LHHHHx xL LL HL HH Lxx↑↑↑x xx xL xH xx Lx x x xx x x xx x x xx x x xx x x xL L L LLHH H H LH H↑↑x Hx xx x x x74LVC161:4位二进制同步计数器:输入输出清零CR 预支PE使能C E P C E T时钟CP预支数据输入进位TCL H H H H xLHHHx xx xL xx LH Hx↑xx↑x x x xx x x xx x x xx x x xL L L L保持保持保持L##L#5、实验具体设计:CD4532-8位优先编码器:模块设计代码:module CD4532(EI,I,Y,GS,EO);//8位优先编码器input EI;input [7:0] I;output reg [2:0] Y;output reg GS,EO;always (EI,I)beginif(EI==0) begin Y=3'd0; GS=0; EO=0; endelse//当EI=1时,实现优先编码器的功能beginGS=1; EO=0;//当编码器输入信号有效时,设定GS、EO的输出值if(I[7]) Y=3'd7; else//根据I的高位情况对Y的输出进行控制if(I[6]) Y=3'd6; elseif(I[5]) Y=3'd5; elseif(I[4]) Y=3'd4; elseif(I[3]) Y=3'd3; elseif(I[2]) Y=3'd2; elseif(I[1]) Y=3'd1; elseif(I[0]) Y=3'd0;elsebegin Y=3'd0; GS=0; EO=1; end//当编码器输入信号无效时,设定GS、EO的输出值 endendendmodule对应testbench设计代码:`timescale 1ns/1ns //设定仿真时间间隔单位,之后的testbench中这句代码功能类似module CD4532_tb;reg [7:0] D_in;// 设定testbench输入数据类型为reg型 reg EI_in;wire [2:0] Q_result;// / 设定testbench输出数据类型为wire型wire GS_result,EO_result;initialbeginEI_in=0;//初始化相关数据的值D_in=8'b0000_0001;#80 EI_in=1;#80 $stop();//上一个语句执行完毕后的80个时间单位后仿真终止endalways #10 //每隔10个时间单位执行一次beginif(D_in==8'b1000_0000)D_in=8'b0000_0001;elseD_in=(D_in<<1);endCD4532 U1(.EI(EI_in),.I(D_in),.Y(Q_result),.GS(GS_result),.EO(EO_result)); endmodule74X138-3 线-8线译码器:模块设计代码:module _74X138(A,EN,Y);//3 线-8线译码器,输出为低电平有效input [2:0] A;input EN;//使能端output reg [7:0] Y;integer k;always (A,EN)beginY=8'b1111_1111;for(k=0;k<=7;k=k+1)beginif((EN==1)&&(A==k))Y[k]=0;//EN=1时根据输入的A进行译码elseY[k]=1;//使能无效时或输入无效endendendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74X138_tb;reg [2:0] A_in;reg EI_in;wire [7:0] Y_result;initialbeginEI_in=0;A_in=3'b000;#80 EI_in=1;#160 $stop();endalways #10beginif(A_in==3'b111)A_in=3'b000;elseA_in=A_in+1;end_74X138 U1(.A(A_in),.EN(EI_in),.Y(Y_result));endmodule74HC4511-七段显示译码器:模块设计代码:module _74HC4511(D,LE,BL,LT,a,b,c,d,e,f,g);//七段显示译码器input [3:0] D;//输入信号端口input LE,BL,LT;//控制信号output reg a,b,c,d,e,f,g;always(LE,BL,LT,D)beginif(LT==0) {a,b,c,d,e,f,g}=7'b111_1111;//显示器全亮else if(BL==0) {a,b,c,d,e,f,g}=7'b000_0000;//显示器全灭else if(LE==0) {a,b,c,d,e,f,g}={a,b,c,d,e,f,g};//显示器保持当前显示elsecase(D)//根据输入的8421BCD码进行译码4'd0: {a,b,c,d,e,f,g}=7'b111_1110;//04'd1: {a,b,c,d,e,f,g}=7'b011_0000;//14'd2: {a,b,c,d,e,f,g}=7'b110_1101;//24'd3: {a,b,c,d,e,f,g}=7'b111_1001;//34'd4: {a,b,c,d,e,f,g}=7'b011_0011;//44'd5: {a,b,c,d,e,f,g}=7'b101_1011;//54'd6: {a,b,c,d,e,f,g}=7'b001_1111;//64'd7: {a,b,c,d,e,f,g}=7'b111_0000;//74'd8: {a,b,c,d,e,f,g}=7'b111_1111;//84'd9: {a,b,c,d,e,f,g}=7'b111_1011;//9default:{a,b,c,d,e,f,g}=7'b000_0000;//非8421BCD码输入时,不译码 endcaseendendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74HC4511_tb;reg [3:0] D_in;reg LE_in,BL_in,LT_in;wire A,B,C,D,E,F,G;initialbegin//开始为全亮LE_in=1;//保持,低电平有效BL_in=1;//全灭,低电平有效LT_in=0;//全亮,低电平有效D_in=4'b0000;#100 begin LE_in=1; BL_in=0; LT_in=1; end//全灭#100 begin LE_in=1; BL_in=1; LT_in=1; end//正常显示 #100 begin LE_in=0; BL_in=1; LT_in=1; end//保持#100 $stop();endalways #10beginif(D_in==4'd9)D_in=4'b0000;elseD_in=D_in+1;end_74HC4511 U1(D_in,LE_in,BL_in,LT_in,A,B,C,D,E,F,G); endmodule74HC151-八选一数据选择器:模块设计代码:module _74HC151(S,D,E,Y0,Y1);//八选一数据选择器input [2:0] S;//控制信号input [7:0] D;//输入信号input E;//使能端output reg Y0,Y1;//Y0,Y1分别为同相和反相输出信号always(E,S,D)beginif(~E)begin Y0=0; Y1=1; end//不工作,输出默认信号elsebegincase(S)//根据控制信号选择不同通道的输入信号作为输出3'b000: begin Y0=D[0]; Y1=~Y0; end//03'b001: begin Y0=D[1]; Y1=~Y0; end//13'b010: begin Y0=D[2]; Y1=~Y0; end//23'b011: begin Y0=D[3]; Y1=~Y0; end//33'b100: begin Y0=D[4]; Y1=~Y0; end//43'b101: begin Y0=D[5]; Y1=~Y0; end//53'b110: begin Y0=D[6]; Y1=~Y0; end//63'b111: begin Y0=D[7]; Y1=~Y0; end//7default: begin Y0=0; Y1=~Y0; end//若控制信号不符合要求则输出默认信号endcaseendendendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74HC151_tb;reg [2:0] S_in;reg [7:0] D_in;reg E_in;wire Y0_result,Y1_result;initialbeginE_in=0;S_in=3'b000;D_in=8'b0010_0110;#80 E_in=1;#80 D_in=8'b1001_1110;#80 E_in=0;#80 $stop();endalways #10beginif(S_in==3'b111)S_in=3'b000;elseS_in=S_in+1;end_74HC151 U1(S_in,D_in,E_in,Y0_result,Y1_result);Endmodule74HC85-4位数值比较器:模块设计代码:module _74HC85(A,B,I0,I1,I2,Fab0,Fab1,Fab2);//4位数值比较器,以下均为高电平有效 input [3:0] A,B;//输入信号input I0,I1,I2;//低位比较结果,依次为低位A=B,A<B,A>Boutput reg Fab0,Fab1,Fab2;//输出信号Fab0,Fab1,Fab2依次为A=B,A<B,A>B.reg F000,F001,F002,F110,F111,F112,F220,F221,F222,F330,F331,F332;//中间节点,依次对应Ai=Bi,Ai<Bi,Ai>Bi.i为位数(0~3)always(A,B,I0,I1,I2)beginif(A[3]>B[3])//比较第4位begin F330=0; F331=0; F332=1; endelse if(A[3]<B[3])begin F330=0; F331=1; F332=0; endelsebegin F330=1; F331=0; F332=0; endif(A[2]>B[2])//比较第3位begin F220=0; F221=0; F222=1; endelse if(A[2]<B[2])begin F220=0; F221=1; F222=0; endelsebegin F220=1; F221=0; F222=0; endif(A[1]>B[1])//比较第2位begin F110=0; F111=0; F112=1; endelse if(A[1]<B[1])begin F110=0; F111=1; F112=0; endelsebegin F110=1; F111=0; F112=0; endif(A[0]>B[0])//比较第1位begin F000=0; F001=0; F002=1; endelse if(A[0]<B[0])begin F000=0; F001=1; F002=0; endelsebegin F000=1; F001=0; F002=0; end//输出结果如下if((F000&&F110&&F220&&F330)&&I0)//低位进位信号出错begin Fab2=0; Fab1=0; Fab0=1; endelse if((F000&&F110&&F220&&F330)&&(~I0&&I1&&I2))//低位进位信号出错begin Fab2=0; Fab1=0; Fab0=0; endelse if((F000&&F110&&F220&&F330)&&(~I0&&~I1&&~I2))//低位进位信号出错begin Fab2=1; Fab1=1; Fab0=0; endelse//低位进位信号正常beginFab2=F332||F330&&F222||F330&&F220&&F112||F330&&F220&&F110&&F002||F330&&F220&&F110&&F000&&I2;Fab1=F331||F330&&F221||F330&&F220&&F111||F330&&F220&&F110&&F001||F330&&F220&&F110&&F000&&I1;Fab0=F330&&F220&&F110&&F000&&I0;endendendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74HC85_tb;reg [3:0] A_in,B_in;reg I0_in,I1_in,I2_in;wire Fab0_result,Fab1_result,Fab2_result;initialbeginI0_in=0;I1_in=0;I2_in=0;A_in=4'b1010;B_in=4'b0111;#10 begin I0_in=1; I1_in=0; I2_in=0; end//低位A=B#10 begin I0_in=0; I1_in=1; I2_in=0; end//低位A<B#10 begin I0_in=0; I1_in=0; I2_in=1; end//低位A>B#10 begin I0_in=0; I1_in=0; I2_in=0; //低位归位A_in=4'b0100; B_in=4'b1001; end#10 begin I0_in=1; I1_in=0; I2_in=0; end//低位A=B#10 begin I0_in=0; I1_in=1; I2_in=0; end//低位A<B#10 begin I0_in=0; I1_in=0; I2_in=1; end//低位A>B#10 begin I0_in=0; I1_in=0; I2_in=0; //低位归位A_in=4'b0010; B_in=4'b0010; end#10 begin I0_in=1; I1_in=0; I2_in=0; end//低位A=B#10 begin I0_in=0; I1_in=1; I2_in=0; end//低位A<B#10 begin I0_in=0; I1_in=0; I2_in=1; end//低位A>B#10 $stop();end_74HC85 U1(A_in,B_in,I0_in,I1_in,I2_in,Fab0_result,Fab1_result,Fab2_result); endmodule74HC283-4位二进制全加器:模块设计代码:module _74HC283(A,B,Ci,Co,S);//4位二进制全加器input Ci;//低位进位信号input [3:0] A,B;//输入信号output reg [3:0] S;//输出结果output reg Co;//高位进位信号Co=C[3]reg [3:0] C,G,P;integer k;always(A,B,Ci)beginfor(k=0;k<4;k=k+1)beginG[k]=A[k]&&B[k];P[k]=A[k]&&~B[k]||~A[k]&&B[k];endC[0]=G[0]||P[0]&&Ci;C[1]=G[1]||P[1]&&C[0];C[2]=G[2]||P[2]&&C[1];C[3]=G[3]||P[3]&&C[2];S[0]=P[0]&&~Ci||~P[0]&&Ci;S[1]=P[1]&&~C[0]||~P[1]&&C[0];S[2]=P[2]&&~C[1]||~P[2]&&C[1];S[3]=P[3]&&~C[2]||~P[3]&&C[2];Co=C[3];endendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74HC283_tb;reg [3:0] A_in,B_in;reg Ci_in;//低位进位信号wire [3:0] S_out;//本位相加结果wire Co_out;//高位进位信号initialbeginCi_in=0;A_in=4'b1010;B_in=4'b0111;#10 begin A_in=4'b0011; B_in=4'b1111; end#10 begin A_in=4'b0101; B_in=4'b1001; end#10 begin A_in=4'b1111; B_in=4'b0010; end#10 $stop();endalways #5beginCi_in=~Ci_in;//循环改变低位进位信号end_74HC283 U1(A_in,B_in,Ci_in,Co_out,S_out);endmodule74HC194-4位双向移位寄存器:模块设计代码:module _74HC194(S0,S1,Dsl,Dsr,CP,CR,D,Q);//4位双向移位寄存器_P339 input S0,S1;//输入端口input Dsr,Dsl;//串行数据输入input CP,CR;//时钟和清零input [3:0] D;//并行数据输入output reg [3:0] Q;//输出结果always(posedge CP, negedge CR)beginif(~CR) Q<=4'b0000;//异步清零elsecase({S1,S0})2'b00:Q<=Q;//输出保持不变2'b01:Q<={Q[2:0],Dsr};//右移,低位移向高位2'b10:Q<={Dsl,Q[3:1]};//左移,高位移向低位2'b11:Q<=D;//并行置数endcaseendendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74HC194_tb;reg [3:0] D_in;//并行数据输入reg S0_in,S1_in;//控制信号输入端口reg Dsr_in,Dsl_in;//串行数据输入reg CP_in,CR_in;//时钟和清零,清零为低电平有效wire [3:0] Q_out;//输出结果initialbeginCP_in=1;CR_in=1;S0_in=1;S1_in=1;//开始先输入串行数据Dsr_in=0;Dsl_in=0;D_in=4'b0110;#243 CR_in=~CR_in;#20 $stop();endalways #5beginCP_in=~CP_in;//周期为10ns的时钟信号endalways #15//循环调整控制输入信号,周期60nsbegincase({S1_in,S0_in})2'b00:begin S1_in=0; S0_in=1; end2'b01:begin S1_in=1; S0_in=0; end2'b10:begin S1_in=1; S0_in=1; end2'b11:begin S1_in=0; S0_in=0; endendcaseendalways #10//循环调整串行数据输入信号,周期40nsbegincase({Dsr_in,Dsl_in})2'b00:begin Dsr_in=0; Dsl_in=1; end2'b01:begin Dsr_in=1; Dsl_in=0; end2'b10:begin Dsr_in=1; Dsl_in=1; end2'b11:begin Dsr_in=0; Dsl_in=0; endendcaseend_74HC194 U1(S0_in,S1_in,Dsl_in,Dsr_in,CP_in,CR_in,D_in,Q_out);endmodule74LVC161-4位二进制同步计数器:模块设计代码:module _74LVC161(CEP,CET,PE,CP,CR,D,TC,Q);//4位二进制同步计数器_P340 input CEP,CET,PE,CP,CR;//输入端口input [3:0] D;//并行数据输入output TC;//进位输出output reg [3:0] Q;//输出结果wire CE;assign CE=CEP&CET;//CE=1时计数器计数assign TC=CET&PE&(Q==4'b1111);//产生进位输出信号always(posedge CP, negedge CR)beginif(~CR) Q<=4'b0000;//异步清零else if(~PE) Q<=D;//PE=0,同步输入数据else if(CE)beginif((TC==1)&&(Q==4'b1111))Q<=4'b0000;//计数器计满后自动归零elseQ<=Q+1'b1;//加1计数endelse Q<=Q;//保持输出不变endendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74LVC161_tb;reg CEP_in,CET_in,PE_in,CP_in,CR_in;//输入端口reg [3:0] D_in;//并行数据输入wire TC_out;//进位输出wire [3:0] Q_out;//输出结果initialbeginCEP_in=0;CET_in=1;PE_in=0;CP_in=1;CR_in=1;D_in=4'b1101;#10 begin PE_in=1;D_in=4'b1001; end#20 begin CEP_in=1; CET_in=1; end#220 begin PE_in=0; end#23 CR_in=~CR_in;#20 $stop();endalways #5beginCP_in=~CP_in;//周期为10ns的时钟信号end_74LVC161 U1(CEP_in,CET_in,PE_in,CP_in,CR_in,D_in,TC_out,Q_out);endmodule6、输出仿真波形以及相关数据:CD4532-8位优先编码器:以下波形由上至下依次是:D_in, EI_in, Q_result, GS_result, EO_result;74X138-3 线-8线译码器:以下波形由上至下依次是:A_in, EI_in, Y_result;74HC4511-七段显示译码器:以下波形由上至下依次是:D_in, LE_in, LT_in, A, B, C, D, E, F, G;74HC151-八选一数据选择器:以下波形由上至下依次是:S_in, D_in, E_in, Y0_result, Y1_result;74HC85-4位数值比较器:以下波形由上至下依次是:A_in, B_in, I0_in, I1_in, I2_in, Fab0_result, Fab1_result, Fab2_result;74HC283-4位二进制全加器:以下波形由上至下依次是:A_in, B_in, S_out, Co_out;74HC194-4位双向移位寄存器:以下波形由上至下依次是:D_in, S0_in, S1_in,Dsr_in, Dsl_in, CP_in, CR_in, Q_out;74LVC161-4位二进制同步计数器:以下波形由上至下依次是:CEP_in, CET_in, PE_in, CP_in, CR_in, D_in, T_out, Q_out;7、仿真结果分析:仿真输出波形符合预期,与芯片的功能表描述的功能相符。

数电实验考试verilogHDL语言及参考程序

题目一:表决器电路设计一、设计任务及原理:所谓表决器就是对于一个行为;由多个人投票;如果同意的票数过半;就认为此行为可行;否则如果否决的票数过半;则认为此行为无效..七人表决器顾名思义就是由七个人来投票;当同意的票数大于或者等于4时;则认为同意;反之;当否决的票数大于或者等于4时;则认为不同意..实验中用7个拨动开关来表示七个人;当对应的拨动开关输入为‘1’时;表示此人同意;否则若拨动开关输入为‘0’;则表示此人反对..表决的结果用一个LED表示;若表决的结果为同意;则LED被点亮;否则;如果表决的结果为反对;则LED不会被点亮..同时;数码管上显示通过的票数..二、具体要求:本实验就是利用实验系统中的拨动开关模块和LED模块以及数码管模块来实现一个简单的七人表决器的功能..拨动开关模块中的K1~K7表示七个人;当拨动开关输入为‘1’时;表示对应的人投同意票;否则当拨动开关输入为‘0’时;表示对应的人投反对票;LED模块中LED1表示七人表决的结果;当LED1点亮时;表示此行为通过表决;否则当LED1熄灭时;表示此行为未通过表决..同时通过的票数在数码管上显示出来..在此实验中数码管、LED、拨动开关与FPGA的连接电路和管脚连接在以前的实验中都做了详细说明;这里不在赘述.. 端口名使用模块信号对应FPGA管脚说明S1 按键开关S1 R16 表示1号抢答者S2 按键开关S2 P14 表示2号抢答者S3 按键开关S3 P16 表示3号抢答者S4 按键开关S4 P15 表示4号抢答者S5 按键开关S5 M15 表示5号抢答者S6 按键开关S6 N16 表示6号抢答者S7 按键开关S7 N15 表示7号抢答者DOUT0 LED模块D1 L14 表决结果亮为通过LEDAG0数码管模块A段N4 抢答成功者号码显示LEDAG1数码管模块B段G4LEDAG2数码管模块C段H4参考答案:module lius;dout0;ledag;input 6:0s;output dout0;output 6:0ledag;reg 6:0led;reg 2:0k;reg clk_en;reg dout;always sbegink<=s1+s2+s3+s4+s5+s6+s0;ifk>=4begindout<=1;endelsebegindout<=0;endendalwayskbegincase k3'd0:led<=7'b0111111;3'd1:led<=7'b0000110;3'd2:led<=7'b1011011;3'd3:led<=7'b1001111;3'd4:led<=7'b1100110;3'd5:led<=7'b1101101;3'd6:led<=7'b1111101;3'd7:led<=7'b0000111;default:led<=7'b0000000;endcaseendassignledag=led;assigndout0=dout;endmodule题目二:数字电子实验设计题目:彩灯循环电路设计一、设计任务及原理:所谓彩灯循环就是对于一组彩灯16盏;通过不同的工作模式可按照一定的规律来点亮或者熄灭..我们所要求的彩灯循环电路共分4个节拍;四个节拍按照一定的顺序依次循环执行..二、具体要求:系统设有一个复位键;当按下复位键后;系统从第一节拍开始执行直到第四节拍结束;然后从第一节拍重新开始新的循环..第一节拍:16盏灯Q1~Q16从Q1开始依次点亮;直到Q16为止..每盏灯点亮的时间间隔为一秒;即Q1点亮后;间隔一秒后Q2点亮;然后依次点亮..下面类似间隔时间都为1秒第二节拍:在第一节拍的基础上;16盏灯Q1~Q16从Q16开始依次熄灭;直到Q1为止..每盏灯熄灭的时间间隔为一秒;即Q16熄灭后;间隔一秒后Q15熄灭;然后依次熄灭直到全部熄灭为止..下面类似间隔时间都为1秒第三节拍: 16盏灯Q1~Q16从两端开始依次点亮;即Q1、Q16先点亮;然后Q2、Q15再点亮;直到全部16盏等点亮为止..每盏灯点亮的时间间隔为一秒..第四节拍:在第三节拍的基础上;16盏灯Q1~Q16从中间开始依次熄灭;即Q8、Q9先熄灭;然后Q7、Q10再熄灭;直到全部16盏灯熄灭为止..每盏灯熄灭的时间间隔为一秒..在此实验中数码管、LED、拨动开关与FPGA 的连接电路和管脚连接在以前的实验中都做了详细说明;这里不在赘述.. 端口名使用模块信号对应FPGA管脚说明S1 按键开关S1 R16 表示复位按键Q1 Q1 L14 Q2 Q2 M14Q3 Q3 N14Q4 Q4 N13Q5 Q5 P12 参考答案:module liu2clk;ret;led;input clk;ret;output16:1 led;wire ret_en;reg 16:1led1;reg 5:0i;j;k;l;m;reg 31:0cout;reg clk_en;assignret_en=ret;alwaysposedge clk or negedge ret_enbeginif~ret_enbeginled1<=16'b0000000000000000;i<=0;endelsebeginifclk_enbeginj<=0;k<=0;i<=i+1;ifi<=16begin//dex<=i;//l<=0;//m<=0;led1i<=1;//led1i-j<=0;endelse ifi>16&&i<=32beginj<=k2+1;k<=k+1;led1i-j<=0;//dex<=dex-1;endelse ifi>32&&i<=40begin//dex<=dex+1;//l<=2m+17;led1i-32<=1;led149-i<=1;endelse ifi>40&&i<=48beginled1i-32<=0;led149-i<=0;//dex<=dex-1;endelsebegini<=0;led1<=16'b0000000000000000;endendendendassignled=led1;endmodule题目三:汽车尾灯控制电路设计一、设计任务及原理:假设汽车尾部左右两侧各有3个指示灯;1汽车正常运行时;指示灯全灭..2左转弯时;左侧3个指示灯按照左循环顺序点亮1HZ..3 右转弯时;右侧3个指示灯按照右循环顺序点亮1HZ..4临时刹车时;所有指示灯同时闪烁1HZ..二、具体要求:尾灯与汽车运行状态表开关控制运行状态左尾灯右尾灯S1 S0 D1 D2 D3 D4 D5 D60 0 正常运行灯灭灯灭0 1 左转弯按照D3;D2;D1顺序循环点亮灯灭1 0 右转弯灯灭按照D4;D5;D6顺序循环点亮1 1 临时停车1HZ频率同时闪烁1HZ频率同时闪烁在此实验中数码管、LED、拨动开关与FPGA的连接电路和管脚连接在以前的实验中都做了详细说明;这里不在赘述..端口名使用模块信对应FPGA管号脚S1 按键开关S1 R16S2 按键开关S2 P14D1 LED模块D1 L14D2 LED模块D2 M14D3 LED模块D3 N14D4 LED模块D4 N13D5 LED模块D5 P12D6 LED模块D6 N12 脉冲源50MHZ CP J3 参考程序:module lwfclk;ledag;s;input clk;input 1:0s;output5:0ledag;reg5:0led;reg1:0i;j;k;reg31:0cout;reg clk_en;alwaysposedge clkbeginifclk_enbeginifs==2'b00begini<=0;j<=0;k<=0;led<=6'b000000;endelse ifs==2'b01beginled<=6'b000000;k<=0;j<=0;i<=i+1;ifi==2'b01beginled<=6'b001000;endifi==2'b10beginled<=6'b010000;endifi==2'b11beginled<=6'b100000;i<=0;endendelse ifs==2'b10beginled<=6'b000000;k<=0;i<=0;j<=j+1;ifj==2'b01beginled<=6'b000100;endifj==2'b10beginled<=6'b000010;endifj==2'b11beginled<=6'b000001;j<=0;endendelse ifs==2'b11beginled<=6'b000000;i<=0;j<=0;k<=k+1;ifk==2'b01beginled<=6'b000000;endifk==2'b10beginled<=6'b111111;k<=0;endendendendassignledag=led;endmodule题目四:数字电子实验设计题目:抢答器电路设计一、设计任务及原理:抢答器在各类竞赛性质的场合得到了广泛的应用;它的出现;消除了原来由于人眼的误差而未能正确判断最先抢答的人的情况..抢答器的原理比较简单;首先必须设置一个抢答允许标志位;目的就是为了允许或者禁止抢答者按按钮;如果抢答允许位有效;那么第一个抢答者按下的按钮就将其清除;同时记录按钮的序号;也就是对应的按按钮的人;这样做的目的是为了禁止后面再有人按下按钮的情况..总的说来;抢答器的实现就是在抢答允许位有效后;第一个按下按钮的人将其清除以禁止再有按钮按下;同时记录清楚抢答允许位的按钮的序号并显示出来;这就是抢答器的实现原理..二、具体要求:本实验的任务是设计一个四人抢答器;用按键模块的S8来作抢答允许按钮;用S1~S4来表示1号抢答者~4号抢答者;同时用LED模块的LED1~LED4分别表示于抢答者对应的位子..具体要求为:按下S8一次;允许一次抢答;这时S1~S4中第一个按下的按键将抢答允许位清除;同时将对应的LED点亮;用来表示对应的按键抢答成功..数码管显示对应抢答成功者的号码..在此实验中数码管、LED、按键开关与FPGA的连接电路和管脚连接在以前的实验中都做了详细说明;这里使用模块信号对应FPGA管脚说明不在赘述.. 端口名S1 按键开关S1 R16 表示1号抢答者S2 按键开关S2 P14 表示2号抢答者S3 按键开关S3 P16 表示3号抢答者S4 按键开关S4 P15 表示4号抢答者S8 按键开关S12 M15 开始抢答按键DOUT0 LED模块D1 L14 1号抢答者灯DOUT1 LED模块D2 M14 2号抢答者灯DOUT2 LED模块D3 N14 3号抢答者灯DOUT3 LED模块D4 N13 4号抢答者灯LEDAG0数码管模块A段N4 抢答成功者号码显示LEDAG1数码管模块G4B段LEDAG2数码管模块H4C段参考程序:module liu1s1;s2;s3;s4;s8;led;ledag;input s1;s2;s3;s4;input s8;output 6:0ledag;output 3:0led;reg 3:0led;reg k;reg 6:0ledag1;//initial// k<=0;always s8beginifs8==0begin k<=1;led<=4'b0000;ledag1<=7'b0111111;end elsebeginifk==1beginif~s1beginled<=4'b1000;ledag1<=7'b0000110;k<=0;endelse if~s2beginled<=4'b0100;ledag1<=7'b1011011;k<=0;endelse if~s3beginled<=4'b0010;ledag1<=7'b1001111;k<=0;endelse if~s4beginled<=4'b0001;ledag1<=7'b1100110;k<=0;endendendendassignledag=ledag1; endmodule。

Verilog HDL程序设计

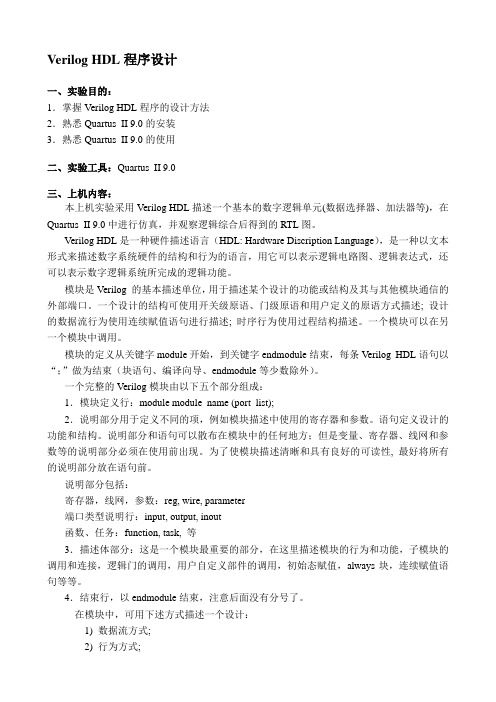

Verilog HDL程序设计一、实验目的:1.掌握Verilog HDL程序的设计方法2.熟悉Quartus_II 9.0的安装3.熟悉Quartus_II 9.0的使用二、实验工具:Quartus_II 9.0三、上机内容:本上机实验采用Verilog HDL描述一个基本的数字逻辑单元(数据选择器、加法器等),在Quartus_II 9.0中进行仿真,并观察逻辑综合后得到的RTL图。

Verilog HDL是一种硬件描述语言(HDL: Hardware Discription Language),是一种以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

模块是Verilog 的基本描述单位,用于描述某个设计的功能或结构及其与其他模块通信的外部端口。

一个设计的结构可使用开关级原语、门级原语和用户定义的原语方式描述; 设计的数据流行为使用连续赋值语句进行描述; 时序行为使用过程结构描述。

一个模块可以在另一个模块中调用。

模块的定义从关键字module开始,到关键字endmodule结束,每条Verilog HDL语句以“;”做为结束(块语句、编译向导、endmodule等少数除外)。

一个完整的Verilog模块由以下五个部分组成:1.模块定义行:module module_name (port_list);2.说明部分用于定义不同的项,例如模块描述中使用的寄存器和参数。

语句定义设计的功能和结构。

说明部分和语句可以散布在模块中的任何地方;但是变量、寄存器、线网和参数等的说明部分必须在使用前出现。

为了使模块描述清晰和具有良好的可读性, 最好将所有的说明部分放在语句前。

说明部分包括:寄存器,线网,参数:reg, wire, parameter端口类型说明行:input, output, inout函数、任务:function, task, 等3.描述体部分:这是一个模块最重要的部分,在这里描述模块的行为和功能,子模块的调用和连接,逻辑门的调用,用户自定义部件的调用,初始态赋值,always块,连续赋值语句等等。

实验二硬件描述语言(VerilogHDL)软件基本使用方法综述

编译通过后系统信息窗口:报告相关的使用芯片类型、使用的逻辑元素个数 等信息

⑷建立波形文件,设置相关端口信号,同实验一基本相同,设置之后保存波形文 件,重新进行编译。

⑸点击时序仿真按钮,进行仿真,观察结果可知完全符合数字选择电路功能。 这种通过Verilog HDL编程实现的功能与电路设计完成的功能完全相同。

⑷Verilog模块的结构特点 • Verilog程序是由若干模块构成的。每个模块的内容 都嵌在module和endmodule两个关键字之间;每个 模块实现特定的逻辑功能。 • 每个模块首先要进行端口定义,并说明输入和输出 口(input、output或inout),然后对模块的功能 进行定义。 • Verilog程序书写格式自由,一行可以写几个语句, 一个语句也可以分多行写,。 • 除了endmodule等少数语句外,每个语句的最后必 须有分号。 • 可用 /*……*/ 和 //……对Verilog程序作注释。 • Verilog程序书写区分大小写,关键字必须小写。

更多控制端口设置

lpm_counter计数器功能仿真波形

模24方向可控计数器电路

⑸Verilog 模块的模板

•module <顶层模块名> (<输入输出端口列表>); •output 输出端口列表; //输出端口声明 •input 输入端口列表; //输入端口声明 •/*定义数据,信号的类型,函数声明*/ •reg 信号名; •//逻辑功能定义 •assign <结果信号名>=<表达式>; //使用assign语句定义逻辑功能 •//用always块描述逻辑功能 •always @ (<敏感信号表达式>) • begin • //过程赋值 • //if-else,case语句 • //while,repeat,for循环语句 • //task,function调用 • end •//调用其它模块 • <调用模块名module_name > <例化模块名> (<端口列表port_list >); •//门元件例化 • 门元件关键字 <例化门元件名> (<端口列表port_list>); •endmodule

verilog hdl 题目

Verilog HDL简介及应用1. 概述Verilog HDL作为一种硬件描述语言,在数字电路设计领域中得到了广泛的应用。

本文将从Verilog HDL的定义、特点、基本语法、应用领域等方面进行介绍,以便读者对Verilog HDL有一个清晰的认识。

2. Verilog HDL的定义Verilog HDL即Verilog Hardware Description Language,是一种硬件描述语言,用于对数字电路进行描述、模拟和验证。

它是一种硬件描述语言,类似于C语言,但是它更关注于硬件层面的描述和设计。

3. Verilog HDL的特点(1)泛型性:Verilog HDL支持泛型编程,能够描述各种类型的数字电路,包括组合逻辑和时序逻辑。

(2)并发性:Verilog HDL支持并发描述,在描述数字电路时可以使用并发结构描述各个逻辑单元的交互关系。

(3)模块化:Verilog HDL支持模块化设计,模块之间可以进行层次化的描述和连接,使得复杂的电路可以被分解成多个独立的模块进行设计和验证。

4. Verilog HDL的基本语法(1)模块声明:使用module关键字声明一个模块,包括输入、输出和内部信号的声明。

(2)数据类型:Verilog HDL支持多种数据类型,包括bit、reg、wire、integer等。

(3)运算符:Verilog HDL支持各种运算符,包括赋值运算符、逻辑运算符、位运算符、条件运算符等。

(4)控制结构:Verilog HDL支持if-else、for循环、while循环等控制结构。

(5)并发语句:Verilog HDL使用always关键字和符号来描述并发执行的逻辑。

5. Verilog HDL的应用领域Verilog HDL广泛应用于数字电路的设计、仿真和验证之中,包括但不限于:(1)集成电路(IC)设计:Verilog HDL可用于描述芯片内部的数字电路,进行功能验证和时序分析。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

题目一:表决器电路设计一、设计任务及原理:所谓表决器就是对于一个行为,由多个人投票,如果同意的票数过半,就认为此行为可行;否则如果否决的票数过半,则认为此行为无效。

七人表决器顾名思义就是由七个人来投票,当同意的票数大于或者等于4时,则认为同意;反之,当否决的票数大于或者等于4时,则认为不同意。

实验中用7个拨动开关来表示七个人,当对应的拨动开关输入为‘1’时,表示此人同意;否则若拨动开关输入为‘0’,则表示此人反对。

表决的结果用一个LED表示,若表决的结果为同意,则LED被点亮;否则,如果表决的结果为反对,则LED不会被点亮。

同时,数码管上显示通过的票数。

二、具体要求:本实验就是利用实验系统中的拨动开关模块和LED模块以及数码管模块来实现一个简单的七人表决器的功能。

拨动开关模块中的K1~K7表示七个人,当拨动开关输入为‘1’时,表示对应的人投同意票,否则当拨动开关输入为‘0’时,表示对应的人投反对票;LED模块中LED1表示七人表决的结果,当LED1点亮时,表示此行为通过表决;否则当LED1熄灭时,表示此行为未通过表决。

同时通过的票数在数码管上显示出来。

在此实验中数码管、LED、拨动开关与FPGA的连接电路和管脚连接使用模块信号对应FPGA管脚说明在以前的实验中都做了详细说明,这里不在赘述。

端口名S1 按键开关S1 R16 表示1号抢答者S2 按键开关S2 P14 表示2号抢答者S3 按键开关S3 P16 表示3号抢答者S4 按键开关S4 P15 表示4号抢答者S5 按键开关S5 M15 表示5号抢答者S6 按键开关S6 N16 表示6号抢答者S7 按键开关S7 N15 表示7号抢答者DOUT0 LED模块D1 L14 表决结果亮为通过LEDAG0 数码管模块A段N4 抢答成功者号码显示LEDAG1 数码管模块B段G4LEDAG2 数码管模H4块C段参考答案:module liu(s,dout0,ledag);input [6:0]s;output dout0;output [6:0]ledag;reg [6:0]led;reg [2:0]k;reg clk_en;reg dout;always @(s)begink<=s[1]+s[2]+s[3]+s[4]+s[5]+s[6]+s[0];if(k>=4)begindout<=1;endelsebegindout<=0;endendalways@(k)begincase (k)3'd0:led<=7'b0111111;3'd1:led<=7'b0000110;3'd2:led<=7'b1011011;3'd3:led<=7'b1001111;3'd4:led<=7'b1100110;3'd5:led<=7'b1101101;3'd6:led<=7'b1111101;3'd7:led<=7'b0000111;default:led<=7'b0000000;endcaseendassignledag=led;assigndout0=dout;endmodule题目二:数字电子实验设计题目:彩灯循环电路设计一、设计任务及原理:所谓彩灯循环就是对于一组彩灯(16盏),通过不同的工作模式可按照一定的规律来点亮或者熄灭。

我们所要求的彩灯循环电路共分4个节拍,四个节拍按照一定的顺序依次循环执行。

二、具体要求:系统设有一个复位键,当按下复位键后,系统从第一节拍开始执行直到第四节拍结束,然后从第一节拍重新开始新的循环。

第一节拍:16盏灯(Q1~Q16)从Q1开始依次点亮,直到Q16为止。

每盏灯点亮的时间间隔为一秒,即Q1点亮后,间隔一秒后Q2点亮,然后依次点亮。

(下面类似间隔时间都为1秒)第二节拍:在第一节拍的基础上,16盏灯(Q1~Q16)从Q16开始依次熄灭,直到Q1为止。

每盏灯熄灭的时间间隔为一秒,即Q16熄灭后,间隔一秒后Q15熄灭,然后依次熄灭直到全部熄灭为止。

(下面类似间隔时间都为1秒)第三节拍: 16盏灯(Q1~Q16)从两端开始依次点亮,即(Q1、Q16先点亮,然后Q2、Q15再点亮,直到全部16盏等点亮为止)。

每盏灯点亮的时间间隔为一秒。

第四节拍:在第三节拍的基础上,16盏灯(Q1~Q16)从中间开始依次熄灭,即(Q8、Q9先熄灭,然后Q7、Q10再熄灭,直到全部16盏灯熄灭为止)。

每盏灯熄灭的时间间隔为一秒。

在此实验中数码管、LED、拨动开关与FPGA使用模对应说明的连接电路和管脚连接在以前的实验中都做了详细说明,这里不在赘述。

端口名块信号FPGA管脚S1 按键开关S1 R16 表示复位按键Q1 Q1 L14Q2 Q2 M14Q3 Q3 N14Q4 Q4 N13Q5 Q5 P12 参考答案:module liu2(clk,ret,led);input clk,ret;output[16:1] led;wire ret_en;reg [16:1]led1;reg [5:0]i,j,k,l,m;reg [31:0]cout;reg clk_en;assignret_en=ret;always@(posedge clk or negedge ret_en)beginif(~ret_en)beginled1<=16'b0000000000000000;i<=0;endelsebegincout<=(cout==32'd5*******)?32'd0:(cout+32'd1);clk_en<=(cout==32'd5*******)?1'd1:(1'd0);if(clk_en)beginj<=0;k<=0;i<=i+1;if(i<=16)begin//dex<=i;//l<=0;//m<=0;led1[i]<=1;//led1[i-j]<=0; endelse if(i>16&&i<=32) beginj<=k*2+1;k<=k+1;led1[i-j]<=0;//dex<=dex-1;endelse if(i>32&&i<=40) begin//dex<=dex+1;//l<=2*m+17;led1[i-32]<=1;led1[49-i]<=1; endelse if(i>40&&i<=48) beginled1[i-32]<=0;led1[49-i]<=0;//dex<=dex-1;endelsebegini<=0;led1<=16'b0000000000000000;endendendendassignled=led1;endmodule题目三:汽车尾灯控制电路设计一、设计任务及原理:假设汽车尾部左右两侧各有3个指示灯,(1)汽车正常运行时,指示灯全灭。

(2)左转弯时,左侧3个指示灯按照左循环顺序点亮(1HZ)。

(3) 右转弯时,右侧3个指示灯按照右循环顺序点亮(1HZ)。

(4)临时刹车时,所有指示灯同时闪烁(1HZ)。

二、具体要求:尾灯与汽车运行状态运行状态左尾灯右尾灯表开关控制S1 S0 D1 D2 D3 D4 D5 D6 0 0 正常运行灯灭灯灭0 1 左转弯按照D3,D2,D1顺序循环点亮灯灭1 0 右转弯灯灭按照D4,D5,D6顺序循环点亮1 1 临时停车1HZ频率同时闪烁1HZ频率同时闪烁在此实验中数码管、LED、拨动开关与FPGA的连接电路和管脚连接在以前的实验中都做了详细说明,这里不在赘述。

端口名使用模块信号对应FPGA管脚S1 按键开关S1 R16 S2 按键开关S2 P14 D1 LED模块D1 L14 D2 LED模块D2M14D3 LED模块N14D3N13D4 LED模块D4D5 LED模块P12D5D6 LED模块N12D6脉冲源50MHZ CP J3 参考程序:module lwf(clk,ledag,s);input clk;input [1:0]s;output[5:0]ledag;reg[5:0]led;reg[1:0]i,j,k;reg[31:0]cout;reg clk_en;always@(posedge clk)begincout<=(cout==32'd5*******)?32'd0:(cout+32'd1);clk_en<=(cout==32'd5*******)?1'd1:(1'd0);if(clk_en)beginif(s==2'b00)begini<=0;j<=0;k<=0;led<=6'b000000;endelse if(s==2'b01)beginled<=6'b000000;k<=0;j<=0;i<=i+1;if(i==2'b01)beginled<=6'b001000;endif(i==2'b10)beginled<=6'b010000;endif(i==2'b11)beginled<=6'b100000;i<=0;endendelse if(s==2'b10) beginled<=6'b000000;k<=0;i<=0;j<=j+1;if(j==2'b01)beginled<=6'b000100;endif(j==2'b10)beginled<=6'b000010;endif(j==2'b11)beginled<=6'b000001;j<=0;endendelse if(s==2'b11)beginled<=6'b000000;i<=0;j<=0;k<=k+1;if(k==2'b01)beginled<=6'b000000;endif(k==2'b10)beginled<=6'b111111;k<=0;endendendendassignledag=led;endmodule题目四:数字电子实验设计题目:抢答器电路设计一、设计任务及原理:抢答器在各类竞赛性质的场合得到了广泛的应用,它的出现,消除了原来由于人眼的误差而未能正确判断最先抢答的人的情况。