计算机组成原理勘误表

《计算机组成原理》勘误表

6

程序控制方式

程序查询方式

7

程序控制方式

程序查询方式

P293

题8

PE

PM

P231

倒5

100Mbps

100MBps

P232

5

从设备就绪、发出传输信号时

有传输需求、从设备就绪时

P239

题10

最大带宽是多少

最大带宽各是多少

题16

PCI总线采用的总线仲裁方式是什么?为什么?

该问改为第一问,并删除“为什么”

P245

图7.8

(b)

四处箭头有误

P264

图7.42

ID域与数据域的边界线有误

《计算机组成原理》勘误表

页数

行数

原文

修改或说明

P6

表1.1

if (nCount<5)

if (nCount<4)

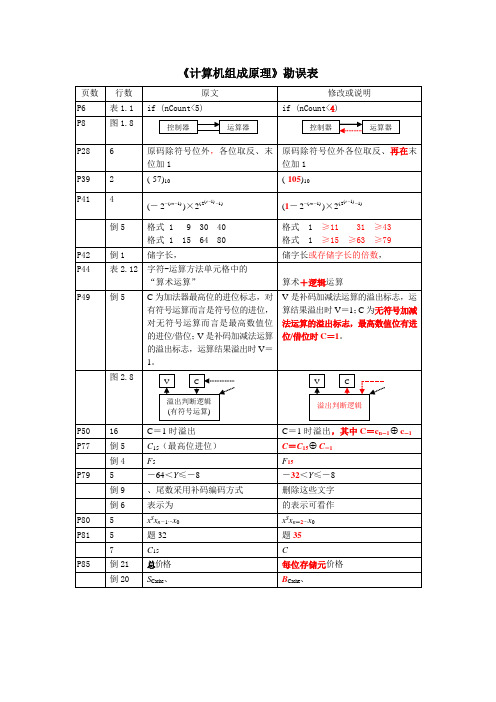

P8

图1.8

P28

6

原码除符号位外,各位取反、末位加1

原码除符号位外各位取反、再在末位加1

P39

2

(-57)10

(-105)10

P41

4

(-

(1-

倒5

格式 1 9 30 40

格式 1 15 64 80

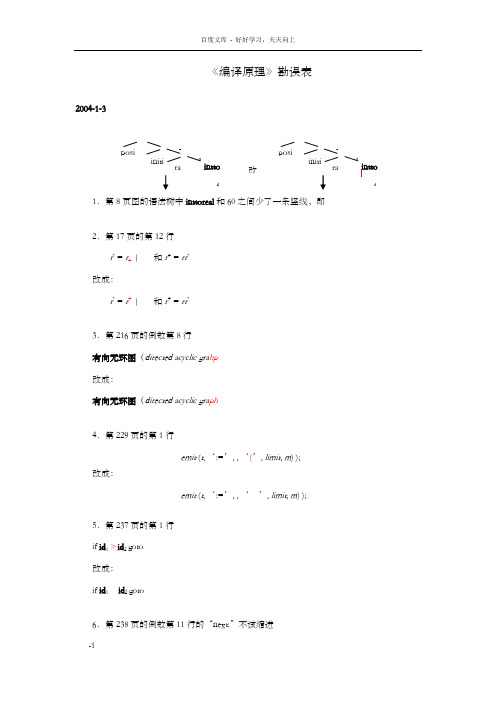

V是补码加减法运算的溢出标志,运算结果溢出时V=1;C为无符号加减法运算的溢出标志,最高数值位有进位/借位时C=1。

图2.8

P50

16

C=1时溢出

C=1时溢出,其中C=cn-1 c-1

P77

倒5

C15(最高位进位)

C=C15 C-1

倒4

F5

F15

P79

5

-64<Y≤-8

编译原理勘误表格

《编译原理》勘误表2004-1-31.第8页图的语法树中inttoreal 和60之间少了一条竖线,即2.第17页的第12行r * = r + | 和r + = rr *改成:r * = r + | 和r + = rr *3.第216页的倒数第8行有向无环图(directed acyclic gra hp改成:有向无环图(directed acyclic gra ph4.第229页的第1行emit (t , ‘:=’, , ‘(’, limit , m ) );改成:emit (t , ‘:=’, , ‘’, limit , m ) );5.第237页的第1行if id 1 > id 2 goto改成:if id 1 id 2 goto6.第238页的倒数第11行的“next:”不该缩进intto + * 6initi ra intto + * 6initi ra改L n-1: S n的代码next:改成:L n-1: S n的代码next:7.第239页的第10行的“next:”不该缩进test: if t = V1 goto L1if t = V2 goto L2. . .if t = V n-1 goto L n-1g oto L nnext:改成:test: if t = V1 goto L1if t = V2 goto L2. . .if t = V n-1 goto L n-1g oto L nnext:8.第239页的第21行的“next:”不该缩进test: case V1 L1case V2L2. . .case V n-1 L n-1case t L nnext:改成:test: case V1 L1case V2L2. . .case V n-1 L n-1case t L nnext:9.第278页的图中极点4到极点3的回边少了箭头310.改成:11.12.2003-12-131.第318页图的最下面的文字在内存中的已完全连接的可执行程序改成:完全连接的可执行代码已在内存中2003-12-61.第270页图的第11行d o j = j (1; while (a[j]> v);改成:do j = j 1; while (a[j]> v);2.第270页图的第(8)条语句(8 ) if t3> v goto (5 )改成:(8 ) if t3< v goto (5 )3.第271页图的第2个方框i f t3> v goto B2改成:if t3< v goto B24.第273页图的第2个方框i f t3> v goto B2改成:if t3< v goto B25.第277页图的第2个方框i f t3> v goto B2改成:if t3< v goto B22003-12-11.第142页第5行E E1 + T E. nptr := mknode ('+', E1. nptr, T. nptr )改成:E E1 + T E. nptr := mknode ('+', E1. nptr, T. nptr )2. 第182页图算法的倒数第2行qui C ksort(1,9)改成:qui c ksort(1,9)2003-10-121.目录第3页第8章代秒生成改成第8章代码生成2.第49页第2行对某个串,存在推导A*A 改成对某个串,存在推导A+A3.第80页第1行若是S*rm Aw *rm12w 改成:若是S*rm Aw rm12w。

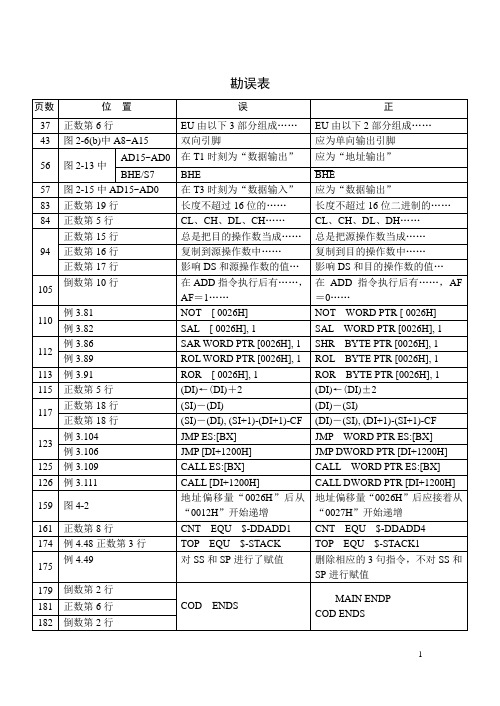

微机原理教材勘误

429

图9-21

通道B外接“8位A/D”

应为“8位D/A”

431

正数第1行

DISTR

DOSTR

433

图9-24中对D5的说明

0-校验位无效

0-此位无效

1-D4=1,D3=1,偶校验时,校验位为0

1-D4=0、D3=1时,校验位为0

1-D4=1,D3=1,奇校验时,校验位为1

1-D4=1、D3=1时,校验位为1

117

正数第18行

(SI)-(DI)

(DI)-(SI)

正数第18行

(SI)-(DI), (SI+1)-(DI+1)-CF

(DI)-(SI), (DI+1)-(SI+1)-CF

123

例3.104

JMP ES:[BX]

JMP WORD PTR ES:[BX]

例3.106

JMP [DI+1200H]

JMP DWORD PTR [DI+1200H]

83

正数第19行

长度不超过16位的……

长度不超过16位二进制的……

84

正数第5行

CL、CH、DL、CH……

CL、CH、DL、DH……

94

正数第15行

总是把目的操作数当成……

总是把源操作数当成……

正数第16行

复制到源操作数中……

复制到目的操作数中……

正数第17行

影响DS和源操作数的值…

影响DS和目的操作数的值…

434

图9-25中对D1的说明

OE=1,重偶错

OE=1,重叠错(即溢出错)

443

正数第22行

66536(或10000)

PIC单片机实用教程--基础篇勘误表

265

图10.20:第1个时序图中72 ms的左箭头应指向虚线;第2个时序图中12 ms应为72 ms

272

倒数第15行:指导控制系统

指控制系统

273

倒数第6行:TMR0

WDT

276

第2行:选型寄存器

表10.13第4列:20007H;WDTE

选项寄存器

2007H;WDTE

286

图10.34:指令抓取和执行的第3列

见更正图2.14和图2.15

36

中部:128X8

128×8

37

表2.3:FLASH存储器/B

2K、4 K、8 K

FLASH存储器

2K×14、4K×14、8K×14

38

2KB、4 KB、8 KB

2K×14、4K×14、8K×14

46

倒数第12、13行:第2部分、第3部分

第3部分、第4部分

47、

48

表2.4:错位、

指令(PC+2)和指令(PC+1)应删除

289

Table 13-1的d项中:D=1

d=1

290

下表:ADDWFW

CLRF Clear f

ADDWF

CLRW Clear w

351

附表34的MC68HC05项:LDX$2D

LDA$2D

368

附图48:EPRO

FLASH下的:PIC18C252*

OTP EPROM

242

表10.1下:GWCF(两处);累加和

CFGW (两处);累加求和

246

表10.6:外接晶体振荡器时

外接阻容时

249

预分频器(prescaler)全部被清0

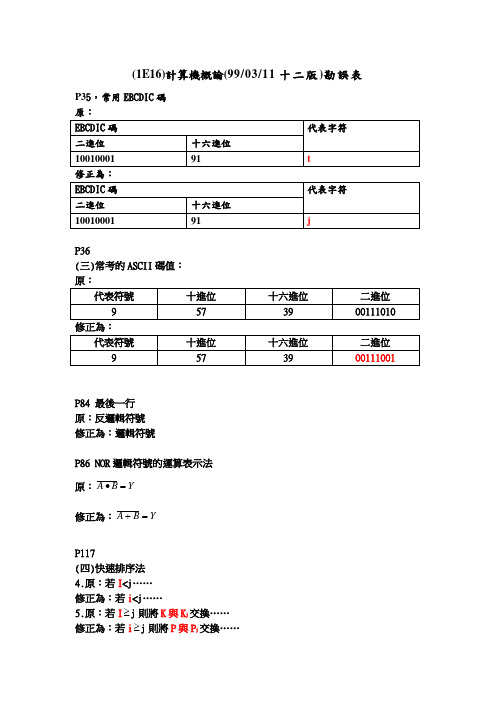

1E16计算机概论990311十二版勘误表

(1E16)計算機概論(99/03/11十二版)勘誤表P35,常用EBCDIC 碼原:修正為:P36(三)常考的ASCII 碼值:原:修正為:P84 最後一行原:反邏輯符號修正為:邏輯符號P86 NOR 邏輯符號的運算表示法原:Y B A =∙修正為:Y B A =+P117(四)快速排序法4.原:若I <j ……修正為:若i <j ……5.原:若I ≥j 則將K 與K j 交換……修正為:若i ≥j 則將P 與P j 交換……P123 倒數第三行原:……,而其它process u也正在……修正為:……,而其它process也正在……P128六、Windows系統第三行最後推層出新修正為推陳出新P128六、Windows系統第三行Windows VIista修正為windows VistaP233 第一行原「一個專家系統至少必須具備五項功能」,修改為「一個專家系統至少必須具備以下功能」P430 第17題原:Pv6修正為:I Pv6歷屆考題’99年度考試,根據國防部試題疑義公告第34題:1.題目雖未明確指明起點為何,但依據四個答案可推測出起點為A。

2.深度優先搜尋是從樹的根節點開始,一層一層向下檢查,直到沒有下一層節點為止(稱葉節點),然後再跳回該葉節點的上一層,檢查是否有其他下層的葉節點,然後再跳回上一層,檢查其他的子節點,依此類推。

等到最後又回到根節點,就表示全部的節點都已檢查完畢。

3.另外DFS室以Depth,也就是深度為優先考量的一種搜尋法,在圖論中,就是把所有節點(node)走一遍的方法。

也就是以走的深度為優先考量,當遇到末端時才走向其他的路。

4.本題目未強制由根節點向左或向右搜尋,依據上述說明,答案B與C符合搜尋原則,故針對考生所提疑義,答案B及C者均得分。

第39題:1.因題目未詳細說明是否為「永久」或「暫時」不用付費即可複製和使用,故答案A(免費軟體)及B(共享軟體)均為正確答案。

《深入理解计算机网络》勘误表

错误位置

原文

修改后

P7第2行

然后从最后得到商数(1)开始……

然后从最后得到的商数(1)开始……

P8中间位置

得到的结果分别是(101)8和(463)8。

得到的结果分别是(101)8和(4643)8。

P8图1-5右图

P10倒数第5行

3)把(758)O、(8265.42)O转换成十六进制;

3)把(756)O、(6265.42)O转换成十六进制;

对端路由器根据所收到的DD报文中的DD报头就可以判断出……

P504表10-1

把表中的“利用”全部替换为“复用”

P508倒数第2行

从表10-2可知,在传输连接建立阶段,

从表10-2可知,在数据传输阶段,

P548倒数第4行

分别为1、101、201、301、601、401、801、501的数据段

分别为1、101、201、301、601、501、801的数据段

按以下格式全部替换本表

路由类型

默认优先级

路由类型

默认优先级

直连路由

0

OSPF ASE(自治系统外部)

150

OSPF

10

O

IS-IS

15

内部BGP

255

静态路由

60

外部BGP

255

RIP

100

未知路由

256

P426表8-3第6行

全球单播地址

全局单播地址

P426倒数第9行

(Flag,8位,即0111110),

(Flag,8位,即01111110),

P190第6行最后

携带一定的检测错码外,

携带一定的检错码外,

P194第8行

微机原理及应用勘误表

微机原理及应用勘误表

1. P85,顺13行,OP S ←(OPD)∧(OPS)

纠正为:OP D ←(OPD)∧(OPS)

2. P89,顺17行,【例4-35】 利用ROL 或RCL 指令

纠正为:【例4-35】 利用SAL 和RCL 指令

3. P89,顺24行, RO L AX ,1

纠正为: SA L AX ,1

4. P89,图4-10中,RO L AX 纠正为

SA L AX

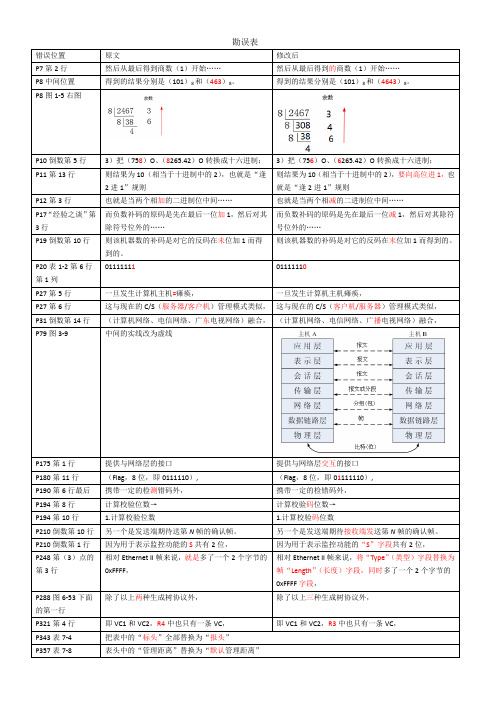

5. P97,表4-10“结果”一列中,原稿中有4处不等号没有输出到纸质上 正确表示如下表:

且倒数第9、10行中两处不等号也没有输出,纠正为:

执行CMP AL ,BL 后,ZF=0,SF=0,OF=0,AL >BL 。

执行CMP BL ,AL 后,ZF=0,SF=1,OF=0,BL <AL 。

6. P111,顺5行,CHAR DW ’AB ’

纠正为:CHAR DW ’ab ’

7. P191,倒数第1行,写入奇地址端口

纠正为: 写入偶地址端口

8. P194,图6-28中,主82C59A 和从82C59A 不能画成一个整体

9.

P34,倒数第3行,为三大部分,运算器、控制器和高速缓冲存储器

纠正为:为三大部分,运算器、控制器和寄存器

表。

勘误表

勘误表:前言第2页倒数第7行:误:正:可先浏览第11讲、21讲、31讲、33讲和45-48讲第1页倒数第9行误:可以快速地浏览下面用小字号编排的几节…正:可以快速地浏览1.1节…第2页倒数第21行误:自动冰箱的作用正:自动冰箱的构成第6页倒数第1行误:图1.6 第二条指令完成后的系统状态正:图1.6 第二条指令取指完成后的系统状态第7页第8行误:图1.7 第二条指令取指完成后的系统状态正:图1.7 第二条指令执行后的系统状态第10页第10行误:(一个加工步骤)取到IR碟中的。

正(一个加工步骤)的复印件取到IR碟中的。

第11页倒数第3行误:编写特殊菜谱的魔法师正:编写特殊菜谱的人第15页倒数第8行误:……一个十进进数转化成任何n进制数…正:……一个十进制整数转化成任何n(n>2)进制整数…第20页第3行——第4行误:在这种程序中,还要用内存地址号来取代数据原来的名称。

正:在这种程序中,常常还要用内存地址号来表示要加工的数据在内存的何处。

第21页倒数第3行误:在一台只有一个 CPU的计算机上正:在一台只有一个单核CPU的计算机上第22页第17行误:有用的息。

正:有用的信息。

第23页第6行误:……且开始#include以……正:……且程序的开始部分#include以……第23页第12行误:表1.3 部分内存结构正:表1.3 部分内存中的数据第25页第16行误:……把数据加工成有用信息的电子数字设备……正:……把输入数据加工成有用信息并输出的电子数字设备……第25页倒数第3行误:如果一台计算机只有一个CPU正:如果一台计算机只有一个单核的CPU第26页第3行误:所以在人类看来,单CPU的计算机似乎……正:所以在人们看来,单核CPU的计算机似乎……第32页第3行误:2.3 C 语言简介正:2.3 C 语言特点简介第32页倒数第4——第3行误:在ANSI C99标准….正:(备注:此两行全部删除)第34页倒数第8行误:此外还有一些修饰用的关键字……正:此外还有一些作修饰用的关键字……第37页第1行误:这个存储单元的数值……正:这个存储单元中存放的数值……正:任意多个字符,…….第41页第25行误:…….”,sizeof(ch))正:…….”,sizeof(ch));第42页第17行误:…….用这种形式的方法来…….正:…….用这种形式化的方法来…….第43页第2行误:或运算符(or)“|”、正:或运算符(or)“||”、第43页第18——19行误:即对某个数据执行取数操作指令(就象上例中的变量m和n)。

勘误表_单片机与微机原理及应用(第2版)[2页]

![勘误表_单片机与微机原理及应用(第2版)[2页]](https://img.taocdn.com/s3/m/5fbdfdfdb8f3f90f76c66137ee06eff9aef849b4.png)

16

不包括位操作类的4条转移指令

不包括位操作类的5条转移指令

109

倒5

很重要,

最重要,

127

17

扩展的内容包括:数据类型、存储类型、存储模式、指针及函数等。

扩展的内容包括:数据类型、存储类型、存储模式、中断服务函数等。

172

倒13

设置读入字节数的奇偶数校验位

设置读入字节奇偶标志

173

倒10

…奇偶数校验位

单片机与微机原理及应用(第2版)勘误表

页码

行

错误内容

更正

3

5

均源于图灵计算机和

均源于图灵计算机思想和

3

12

在此之后,

在此基础上,

12

19

(3)一些…(3)其他系统软。包括一些…45问题6

?典型的I/O接口电路包括哪几种?

?为什么需要有I/O接口电路?

45

问题10

试说明并行接口与串行接口在数据传输与结构上的主要区别?

296

14

与ADD指令相同

与加法指令相同

296

19

与ADC指令相同

与加法指令相同

296

倒3

与ADD指令相同

与加法指令相同

298

19

5.BCD码调整指令

5.十进制数调整指令

298

20

BCD码调整指令共有6条,用于对BCD码运算结果进行调整,

该类指令共有6条,用于对BCD码运算结果进行十进制调整,

300

试说明并行通信与串行通信在数据传输上的主要区别?

66

4

(1)CY(PSW.1):进位标志。

(1)CY(PSW.7):进位标志。

微机原理教材勘误(电子科大版)

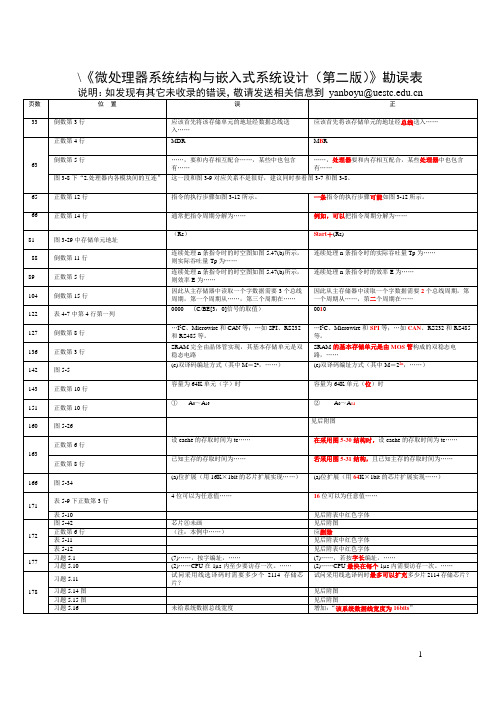

\《微处理器系统结构与嵌入式系统设计(第二版)》勘误表160页图5-26 逻辑地址到物理地址的转换A A A A A A178页习题5.14图178页习题5.15图185页图6-7 固定式多端口地址译码电路195页图6-23 DMAC的结构框图213页图6-47 波特率发生器262页图8-17 LDMDB使用示例303页【例9.9】int main(void){const char *a="Hello World!";char b[20];asm{MOV R0, a //;把数组a的首地址赋值给R0MOV R1, b //;把数组b的首地址赋值给R1BL my_strcpy, {R0, R1}}303页【例9.10】#include <stdio.h>int add(int i, int j){int res; /*定义中间变量res*/__asm{ADD res, i, j //;实现res=i+j}return res;}void main( ){int a;a = add(2,3);printf("addition result is : %d\n",a);}332页示例程序TLOOP LDR R2, =UTRSTAT0 ; 读取UART0收发状态寄存器的值LDR R0, [R2]TST R0, #0x02 ; 判断发送缓冲区是否空闲…RLOOP LDR R2, =UTRSTAT0 ; 读取UART0收发状态寄存器的值LDR R0, [R2]TST R0, #0x01 ; 判断接收缓冲区是否有数据…B TLOOP。

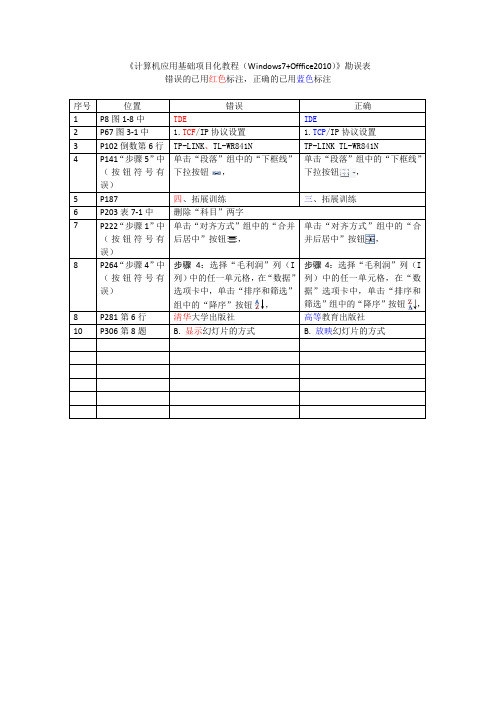

《计算机组成与设计》勘误表——学生版

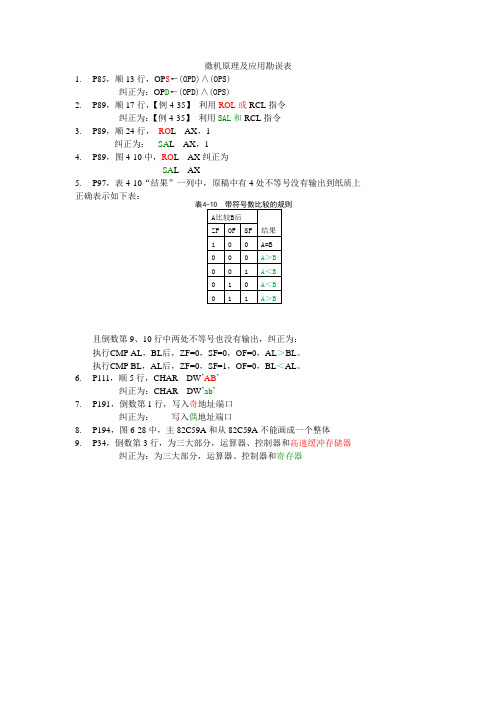

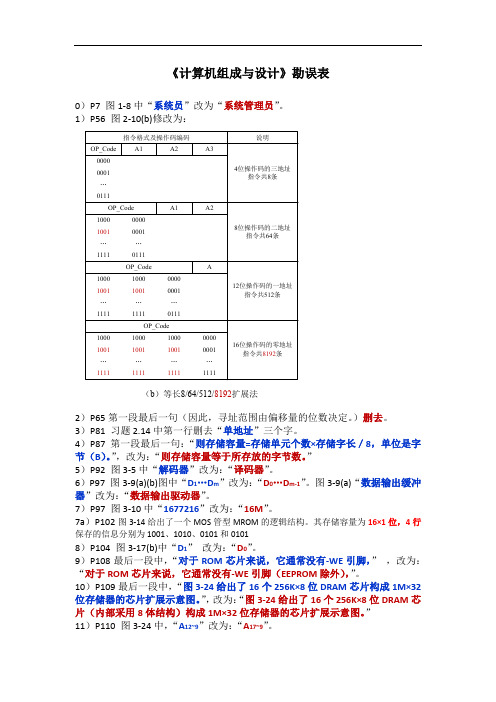

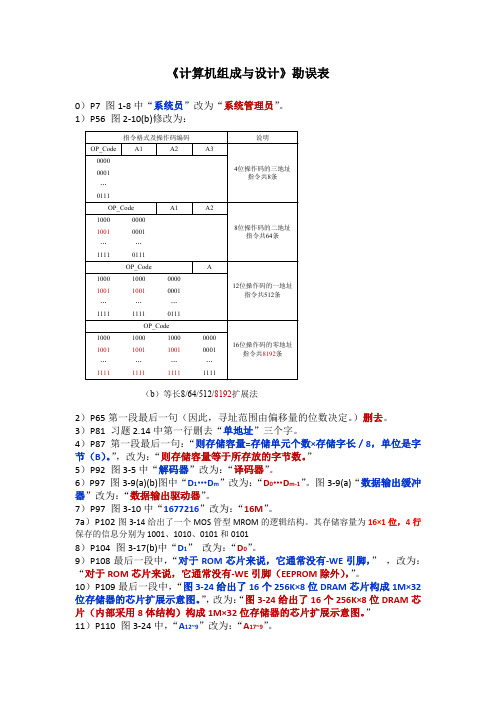

《计算机组成与设计》勘误表0)P7 图1-8中“系统员”改为“系统管理员”。

1)P56 图2-10(b)修改为:指令格式及操作码编码说明OP_Code A1A2A300000001…01114位操作码的三地址指令共8条OP_Code A1A2 10001001 (1111)8位操作码的二地址指令共64条00000001…0111OP_Code A10001001 (1111)12位操作码的一地址指令共512条00000001…011110001001…1111OP_Code10001001 (1111)16位操作码的零地址指令共8192条00000001…111110001001…111110001001…1111(b)等长8/64/512/8192扩展法2)P65第一段最后一句(因此,寻址范围由偏移量的位数决定。

)删去。

3)P81 习题2.14中第一行删去“单地址”三个字。

4)P87 第一段最后一句:“则存储容量=存储单元个数×存储字长/8,单位是字节(B)。

”,改为:“则存储容量等于所存放的字节数。

”5)P92 图3-5中“解码器”改为:“译码器”。

6)P97 图3-9(a)(b)图中“D1…D m”改为:“D0…D m-1”。

图3-9(a)“数据输出缓冲器”改为:“数据输出驱动器”。

7)P97 图3-10中“1677216”改为:“16M”。

7a)P102图3-14给出了一个MOS管型MROM的逻辑结构。

其存储容量为16×1位,4行保存的信息分别为1001、1010、0101和01018)P104 图3-17(b)中“D1”改为:“D0”。

9)P108最后一段中,“对于ROM芯片来说,它通常没有-WE引脚,”,改为:“对于ROM芯片来说,它通常没有-WE引脚(EEPROM除外),”。

10)P109最后一段中,“图3-24给出了16个256K×8位DRAM芯片构成1M×32位存储器的芯片扩展示意图。

勘误表(新)

B.显示幻灯片的方式

B.放映幻灯片的方式

4

P141“步骤5”中(按钮符号有误)

单击“段落”组中的“下框线”下拉按钮 ,

单击“段落”组中的“下框线”下拉按钮 ,

5

P187四、拓Βιβλιοθήκη 训练三、拓展训练6

P203表7-1中

删除“科目”两字

7

P222“步骤1”中

(按钮符号有误)

单击“对齐方式”组中的“合并后居中”按钮 ,

单击“对齐方式”组中的“合并后居中”按钮 ,

《计算机应用基础项目化教程(Windows7+Offfice2010)》勘误表

错误的已用红色标注,正确的已用蓝色标注

序号

位置

错误

正确

1

P8图1-8中

TDE

IDE

2

P67图3-1中

1.TCF/IP协议设置

1.TCP/IP协议设置

3

P102倒数第6行

TP-LINK、TL-WR841N

TP-LINK TL-WR841N

8

P264“步骤4”中

(按钮符号有误)

步骤4:选择“毛利润”列(I列)中的任一单元格,在“数据”选项卡中,单击“排序和筛选”组中的“降序”按钮 ,

步骤4:选择“毛利润”列(I列)中的任一单元格,在“数据”选项卡中,单击“排序和筛选”组中的“降序”按钮 ,

8

P281第6行

清华大学出版社

高等教育出版社

10

单片机原理及应用勘误表(宗成阁)

单片机原理及应用(宗成阁)--勘误表第5页倒数13行:生产低位的→生产低价位的第8页正数7行:分别供URAT →分别供UART第21页正数5行:数据存储器→程序存储器第25页表2.6第2列、倒数第4行:—→AF第29页倒数1行:应大于20ns→应大于20 us第43页表3.1的第3行:程序存储器→位地址空间;第5行:128字节→256字节此页倒数第2行:内部数据RAM单元→内部和外部数据RAM单元第49页图3.11的倒数第2个框中:(A)+06H →(A)+60H第52页正数1行:2.3.4 → 3.3.4第61页正数15行:堆栈区内(61H)=23H →堆栈区内(61H)=25H第65页正数4行:MAIN:→MAIN第67页习题12有错误第69页倒数第1行:AVR→VAR第71页图4.5的正数第6个框中:地址加→地址加1第75页图4.9(a)正数第4个框中:结果×10→结果×100程序清单中:第3行BCDBIN1→BCDB1;第4行#0AH→#64H;第5行乘以10→乘以100第76页正数第3行和第9行:取高位BCD码→取BCD码;倒数第11和12行去掉,改为CJNE A, #0AH, LOOP第77页正数第5行和第6行之间加一条指令MOV A, R2第80页倒数第2行:高8位和送R5→高8位和送R4;倒数第5行:送入R4→送入R5第81页正数第9行:SUB→SUBB第85页倒数第4行:(R3+R7) →(R3×R7)第86页正数第5行:;正数第6行:注释删除;正数第13行:(Ra×R7)→(R2×R7);正数19行:(R2→2R6)改为(R2×R6)第87页倒数第4行:NDNE1→NDVE1第88页图4.17中,左边的循环线入口应从第2和第3个框之间改到第3和第4个框之间第89页正数第19行:(R2R3R6R7)→(R2R3R4R5);倒数第2行:IDIVE→IDVE;倒数第5行:NDIV1→NDIVI第91页倒数第5行:F0H→F0 倒数第6行:MOV R7,07H →MOV R7,#07H第97页正数第14行:删除CPU关中断,;图5.5左端:8AH→A8H第99页图5.7中:地址→位地址第117页图6.7中:在TL0框后的反馈线箭头应改为指向三角形中间第124页倒数第4行:6MHz→12 MHz;倒数12行:TH0→TH1;倒数13行:TL0→TL1第125页正数第11行:TL0→TL1;正数12行:TH0→TH1第130页图7.4右下端:PXD→RXD第133页倒数第1行:串行输入并行输出→并行输入串行输出第134页图7.10 引脚6的INHCL→INH;引脚7的K→CLK第136页正数第2行:并行输入→并行输出;正数11行:TXD→RXD第140页倒数第18行:RB8,是发送→RB8是发送第147页图8.2中:VDD→VPP第149页正数第5行:为11脚→为1脚;倒数第4行:GA→G2A第152页图8.6和图8.7中:74LS373右下角D7→Q7 ;2746→2764第156页正数第6行及图8.11和图8.12中:WR→WE第157页正数第4行:自动产生、控制→自动产生RD、WR控制第158页图8.14的62128中:WR→WE第159页图8.15的62128中:WR→WE第164页图8.21左下端:CS→CS第165页倒数第5行:PC6→PC4(注意有两处)第166页图8.22(b)右上端:有3个箭头方向画反了第167页表8.8方式1输出中IBFB→OBFB第174页图8.30正数第7行:PC为STBA→PC2为STBA第175页倒数第8行:为7FF→为FFF(注意共有3处)第176页#7FF→#0FFF(注意共有5处);倒数第11行:0003H→0013H;倒数第17行:#7FF0→#0FFF3;倒数第13行和第15行:注释有错全部删除第181页倒数第16行:PB口→PA口;倒数第17行:PA口→PB口第184页正数第13行:DS1、DS2、CS1、CS2→DS1、DS2、CS1、CS2 ;倒数第3行:CS1、CS2→CS1、CS2第185页倒数第13行:HP─HELP→HELP第187页正数第22行:#7FFFH→#0BFFFH;正数第25行:在第一片→在第二片。

《计算机组成与设计》勘误表——学生版

《计算机组成与设计》勘误表0)P7 图1-8中“系统员”改为“系统管理员”。

1)P56 图2-10(b)修改为:指令格式及操作码编码说明OP_Code A1A2A300000001…01114位操作码的三地址指令共8条OP_Code A1A2 10001001 (1111)8位操作码的二地址指令共64条00000001…0111OP_Code A10001001 (1111)12位操作码的一地址指令共512条00000001…011110001001…1111OP_Code10001001 (1111)16位操作码的零地址指令共8192条00000001…111110001001…111110001001…1111(b)等长8/64/512/8192扩展法2)P65第一段最后一句(因此,寻址范围由偏移量的位数决定。

)删去。

3)P81 习题2.14中第一行删去“单地址”三个字。

4)P87 第一段最后一句:“则存储容量=存储单元个数×存储字长/8,单位是字节(B)。

”,改为:“则存储容量等于所存放的字节数。

”5)P92 图3-5中“解码器”改为:“译码器”。

6)P97 图3-9(a)(b)图中“D1…D m”改为:“D0…D m-1”。

图3-9(a)“数据输出缓冲器”改为:“数据输出驱动器”。

7)P97 图3-10中“1677216”改为:“16M”。

7a)P102图3-14给出了一个MOS管型MROM的逻辑结构。

其存储容量为16×1位,4行保存的信息分别为1001、1010、0101和01018)P104 图3-17(b)中“D1”改为:“D0”。

9)P108最后一段中,“对于ROM芯片来说,它通常没有-WE引脚,”,改为:“对于ROM芯片来说,它通常没有-WE引脚(EEPROM除外),”。

10)P109最后一段中,“图3-24给出了16个256K×8位DRAM芯片构成1M×32位存储器的芯片扩展示意图。

电脑概论模拟试题勘误表

(HF77)電腦概論模擬試題(96年8月2日二版) 勘誤表P.5第11題原題目多數個同類或相關的資料錄(Record)之集合體稱為應更正為多數個同類或相關的資料記錄(Record)之集合體稱為P.6第15題原選項(C)DISK-COPY應更正為(C)DISKCOPYP.9第4題原題目儲存媒體空間制用效率較低應更正為儲存媒體空間利用效率較低P.9簡答第1題倒數第2行原通常和日常使用的化數式或自然語言應更正為通常和日常使用的數學式或自然語言P.10簡答第1題原(二)組合語言(2)編繹所需的電腦資源較少應更正為(2)編譯所需的電腦資源較少P.11第3題第三行原演算法(algorirthm)應更正為演算法(algorithm)P.14選擇第2題原選項(C)螢光幕應更正為(C)螢幕P.15第6題原選項(D)螢光幕規格應更正為(D)螢幕規格P.18第17題原選項二分查詢法中應更正為二分查尋法中P.20第7題原題目看到檔名為「某某‧ZIP」應更正為看到檔名為「某某.ZIP」P.24第13題原題目瀏灠器開啟後所看到的第一個網頁稱之為首頁應更正為瀏覽器開啟後所看到的第一個網頁稱之為首頁P.25第4題原解析ASICII大小應更正為ASCII大小P.27第11題原解析稱為LIFO序列,(Lastin, First-out),而佇列(Queue)是FIFO,Firstin,First-out應更正為稱為LIFO(Last in, First out)序列,而佇列(Queue)是FIFO(First in, First out)P.35第15題原題目(Accessmechanism)所需的移動的時間,稱之為存取動作時間(accessmotiontime)應更正為(Access mechanism)所需的移動的時間,稱之為存取動作時間(access motion time)P.36第2題原題目可能需更改某些資料欄的檔案應更正為可能需更改某些資料欄位的檔案P.37第6題原題目資料錄應更正為資料記錄P.47第5題原題目藍芽(Blue tooth)應更正為藍芽(Bluetooth)P.50第9題答案修正為(D)P.54簡答題第1題原答案(一)mbps應更正為MbpsP.60第19題原題目DIMSUM%宣告與DIMSUMASINTEGER宣告效果是相同應更正為DIM SUM %宣告與DIM SUM AS INTEGER宣告效果是相同P.61第3題原題目暖開機(warm stad)應更正為暖開機(warm start)P.63第14題原選項(A)動態終端設定協定(DHCP)伺服器侶應更正為(A)動態終端設定協定(DHCP)P.70第20題原題目物件導向(Object-Ori-ented)程式語言應更正為物件導向(Object Oriented)程式語言P.75第6題原題目較適合於資料錄之新增應更正為較適合於資料記錄之新增P.77第6題第4行原KB-BIOS介面連接鍵盤應更正為PS/2介面連接鍵盤P.86第1題原答案資料通訊(Date Communication)應更正為資料通訊(Data Communication)P.86第7題原題目腦資料處理作業中,多數個同類或相關的資料錄(Record)應更正為電腦資料處理作業中,多數個同類或相關的資料記錄(Record)P.89第7題原答案資料錄應更正為資料記錄P.90第4題原題目PRINTASC("A")應更正為PRINT ASC("A")原題目PRINTCHR$(66)應更正為PRINT CHR$(66)P.90第5題原題目PRINTCHR$(ASC("A"))應更正為PRINT CHR$(ASC("A"))P.90第6題原題目OPTIONBASE1應更正為OPTION BASE1P.91第11題原題目 e XP erience應更正為experienceP.94第14題原題目y為輪入端應更正為y為輸入端P.97第2題原題目何謂電傳會議(telecon ference)與視訊會議(video confenece)應更正為何謂電傳會議(teleconference)與視訊會議(videoconference)P.100第3題原題目PRINTCINT(12.51)應更正為PRINT CINT(12.51)P.100第6題原題目PRINTFIX(12.55)應更正為PRINT FIX(12.55)P.104 第15題題目修正為當有奇數個輸入訊號為1時,其輸出訊號為1;否則其輸出訊號為0的是哪一種邏輯閘。

《计算机图学》勘误表

《计算机图形学》勘误表P17 图2-4 偏差差别 应改为 偏差判别 , P29 图2-11 直线应该从(0,0)到(-8,-4) ,P38 图3-6 图中与多边形相交的两条水平扫描线,上面一条为Y=y (k+1),下面一条为 Y=y k ,P39 行2 标上点阵 改为 空白图3-7 图中与多边形相交的两条水平扫描线,下面一条为Y=y i , 倒11 如图中实线与虚线 去掉,P40 图3-8 图中与多边形相交的两条水平扫描线,上面一条为Y=e ,下面一条为 Y=d ,P42改为P44AEL 改为 , P45AEL 改为 ,P50 行13 /* 输入n 改为 /* input 输入四个顶点的值 ,P60 行8 则 F X X Y Y R F X X X X C C A C 11212200222=-++-=--+()()()∆∆ 改为 则 F X X Y Y R F X X X X C C A C 1121220022=-+--=--+()()()∆∆,P62 倒2 Y i +=-1221 改为 Y R i +=-1221, P67 倒8 其中 ∆∆∆F X X F X X F X 111(,)(,)()=-=Λ 改为 其中 ∆∆∆F X X F X X F X 111(,)()()=+-=Λ, P70 行3 X Y R X Y R H H L lL i i i i 222222++++- 改为 X Y R X Y R H H L lL i i i i 222222+-++-, P71 行2 (,)X Y i i ++11 改为 (,)X Y i i +-11 , P74 表4-4 d d a Y i i i +=++1223() 改为 d d b X a Y i i i i +=+++-+1222223()() d d a Y b X i i i i +=+++-+1222322()() 改为 d d a Y i i i +=+-+1223() ,P76 r t a a t e t e t a a t at e e t e e t '()()()()()()=+++-+++++1212201221212222121 改为r t a a t e t e t a a t a t e e t e e t '()()()()()()=+++-+++++1212201221212222121, 倒11 =-L P P ()31 改为 =-L P P ()32 P97 倒2 裁B 剪 改为 裁剪 , P98 图5-10 中的R 改为r ,P106 则主多边形 改为则图5-14左图中主多边形 , P133 公式(6.14) f x a a x a x m m(),=+++01Λ 改为 f x a a x a x m m ()=+++01Λ, P138 行6 P x x 111(,) 改为 P x y 111(,), P145 倒13 y S x i =() 改为 y S x i i =(),P166 公式(6.46) 1812M l l t t i i i i [()]+-+ 改为 1812M l l t l i i i i [()]+-+ ,P196 P u v Bu B v P j ni m ij j mi n (,)()(),,===∑∑00 改为P u v Bu B v P i nj m ij j mi n(,)()(),,===∑∑00 ,P217 倒1 1000101-⎡⎣⎢⎢⎢⎤⎦⎥⎥⎥X Y rr改为 1000101--⎡⎣⎢⎢⎢⎤⎦⎥⎥⎥X Y rr, P218 图7-5 (a ) 应为(d ) 应为(e )应为,P219 行4 [][]X YY X X Y XY ''''=-=⎧⎨⎩=-⎡⎣⎢⎢⎢⎤⎦⎥⎥⎥11010100001 改为[][]X YY X X Y XY ''''==⎧⎨⎩=⎡⎣⎢⎢⎢⎤⎦⎥⎥⎥11010100001行7 [][]X YY X X Y XY ''''==-⎧⎨⎩=-⎡⎣⎢⎢⎢⎤⎦⎥⎥⎥11010100001 改为[][]X YY XX Y XY ''''=-=-⎧⎨⎩=--⎡⎣⎢⎢⎢⎤⎦⎥⎥⎥11010100001本页中矩阵元素 Xs-X 均为 Xs (两处)本页中矩阵元素 Ys-Y 均为 Ys (两处)倒6[][]X Y XY a b c d ef g hi ''11=⎡⎣⎢⎢⎢⎤⎦⎥⎥⎥ 改为X Y a bc d e f g h i X Y ''11⎡⎣⎢⎢⎢⎤⎦⎥⎥⎥=⎡⎣⎢⎢⎢⎤⎦⎥⎥⎥⎡⎣⎢⎢⎢⎤⎦⎥⎥⎥ P221 夹角 改为 夹角’ αβλδ⎡⎣⎢⎤⎦⎥= 改为 αβλδ⎡⎣⎢⎤⎦⎥*, P222 行14 C’=S(t - t 0) 改为 t’=S(t - t 0)行16 []cos [()A t t B t t A t t 211212122222222112+++-θ 改为 []cos [()'A t tB t t A t t 211212122222212112++-θ,P225 倒2 cos sin sin cos θθθθ010000-⎡⎣⎢⎢⎢⎢⎤⎦⎥⎥⎥⎥ 改为 cos sin sin cos θθθθ00000010001-⎡⎣⎢⎢⎢⎢⎤⎦⎥⎥⎥⎥, P226 行1 R X Y Z A A A A =---⎡⎣⎢⎢⎢⎢⎤⎦⎥⎥⎥⎥1000010000101 改为 R X Y Z A AAA=⎡⎣⎢⎢⎢⎢⎤⎦⎥⎥⎥⎥1000010000101, P229 倒3 如图7-3 改为 如图7-13 ,P235 倒1 x hx h zx z h y y z h z '''=-=-=-=⎧⎨⎪⎪⎩⎪⎪110改为x hx h zx z h y y zh z '''=-=-=-=⎧⎨⎪⎪⎪⎪⎩⎪⎪⎪⎪110,P238 行5 cos sin sin cos θθθθ00010000001hhn h --⎡⎣⎢⎢⎢⎢⎢⎤⎦⎥⎥⎥⎥⎥ 改为 cos sin sin cos θθθθ00010000001m h h n h --⎡⎣⎢⎢⎢⎢⎢⎤⎦⎥⎥⎥⎥⎥, P239 倒7 cos sin sin cos θθθθ0000001-⎡⎣⎢⎢⎢⎢⎤⎦⎥⎥⎥⎥ 改为 cos sin sin cos θθθθ000100000001-⎡⎣⎢⎢⎢⎢⎤⎦⎥⎥⎥⎥, P245 行4 ()θ∈V 改为 ()θ∈U ,P255 倒4 P P P P P P P 1234567 改为 P P P P P P P 1243567 ,P261 rootB B B BE B B B B B BF B B E B B F B BE BBB BF F FP264 1.层次层 改为 1.层次模型 P267 表8-4 应为NE NVS NVE NE NVS NVE NE 1 V 1 V 2 NE 6 V 2 V 6 NE 2 V 3 V 1 NE 7 V 5 V 4 NE 3 V 2 V 3 NE 8 V 4 V 6 NE 4 V 5 V 1 NE 9 V 5 V 6 NE 5 V 4 V 3。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

顺8

移码的最高为位为符号位

移码的最高位为符号位

47

顺9

[X]移=0X1X2…Xn-1Xn

[X]移=0XnXn-1…X2X1

47

顺10

[X]移=0X1X2…Xn-1Xn

[X]移=0XnXn-1…X2X1

48

顺9

便于比较浮点数大小和简化

便于比较大小和简化

48

顺11

均为2n-1个

均为(2n-1)个

48

M/IO和D15~D0

273

倒7

(1024×210×32)/(256×210×8)=16片,

(1024×210×32)/(256×210×8)=16片,

273

倒4

(3)中的“存储器…均是相同的。”

“存储器…均是相同的。”调到(4)中的后面

274

倒3

存储访问控制信号(M/IO

存储访问控制信号(M/IO

倒11

由含有WE控制线的8K×8位的…

由含有CS控制线的8K×8位的…

294

顺5

…指令功能与寻址方式而形成的,

…指令的功能需求与寻址方式而形成的,

294

顺8

指令功能与寻址特性是由中央…

指令的功能与寻址特性是由中央…

294

倒22

③指令功能与寻址特性实现的…

③指令的功能与寻址特性的实现…

294

倒1

…按指令功能与寻址特性进行…

过程调用指令于条件转移指令

过程调用指令与条件转移指令

97

顺8

原码、反码、补码与移码,其中机器数字长为8位。

原码、反码、补码与移码(仅定点整数),其中机器数字长为8位(移码偏置值为27)。

97

顺11

机器数的真值。

机器数的真值(移码偏置值为24)。

98

顺1

移码表示的定点小数

移码表示的定点整数

98

倒6

设PC、Rx、Rb分别为

顺6

一是从内存取出该指令的…

一是主存取出该指令的…

313

顺13

“由于控制信号序列发生器…”

该句另起一段

313

顺14

其中ID译码与测试与CU生成…

而ID译码测试与CU生成…

313

倒5

正是存放ADD指令的内存单元。

正是存放ADD指令的主存单元。

313

倒4

从内存中取出一个源操作数。

从主存中取出一个源操作数。

87

顺8

若采用变址接寻址

若采用变址寻址

93

表2-17

Rb

Ry

93

倒7

(4)基值寻址,操作数在E=(Rb)+D

(4)基址寻址,操作数在E=(Ry)+D

94

图2-45

Rb

Ry

94

倒6

图2-45例2.26设计的指令格式

图2-45 例2.27设计的指令格式

96

倒8

地址码个数可以减少

地址码个数可以不同

96

倒3

314

倒12

累加器自算术右移,即R(AC)→AC、AC0→AC0。

累加器逻辑右移SHR,即R(AC)→AC、0→AC7、AC0→CF。

315

顺2

正是存放JMP指令的内存单元。

正是存放JMP指令的主存单元。

315

顺19

和指令处理的可知

和指令处理可知

315

顺4

通常把一个指令周期一般分为

通常把一个指令周期分为

…在1K到几K主存存储字之间。

229

顺16

主存的速度一般是辅存的105倍。

主存的速度一般是辅存的十万倍以上。

230

倒7

…送到MAR中的N位地址信号,

…送到MAR中的W位地址信号,

230

倒6

使2N个选择信号中的一个有效,

使2W个选择信号中的一个有效,

230

倒6

以选中与N位地址信号对应…

以选中与W位地址信号对应…

58

顺9

例2.13采用的就是一维

例2.14采用的就是一维

59

顺2

表2-10 例2.14被检验数据块

表2-10 例2.15被检验数据块

60

顺8

奇偶检验位P4、P3、P2、P1分别

奇偶检验位P1、P2、P3、P4分别

61

顺2

每组中的位由一位奇偶检验位

每组中的数位由一位奇偶检验位

63

图2-25

下面一行顺数第三个字符----D3

下面一行顺数第三个字符----D4

66

顺3

做模2除如下

做模2除如前

勘误表

页码

行号或图表号

原错误

改进后正确

66

顺9

对于例2.18余数与出错位

对于例2.19余数与出错位

67

倒3

对于例2.18,数据有效编码为

对于例2.19,数据有效编码为

70

倒1

一个结果操作数地址地址

一个结果操作数地址

71

顺1

一个结果操作数地址地址

倒5

AC(GR)→ALUS、ALUS→ALU、MDR→ALUS

AC(GR)→ALUR、ALUR→ALU、MDR→ALUR

308

倒1

IR(Ad)→ALUS、

IR(Ad)→ALUR、

309

顺17

ALUS→ALU、

ALUR→ALU、

313

表6-3顺4

将累加器内容算术右移存到…

将累加器内容逻辑右移存到…

313

175

顺14

Pj=Pjn+1Pjn…P2P1

Pj=Pj(n+1)Pjn…Pj2Pj1

180

图4-23

并行加法器左上角的Pjn+2′~Pj1′

并行加法器左上角的Pj(n+2)′~Pj1′

187

图4-27

X1

x1

191

倒9

即最后部余数为正

即最后部分余数为正

195

倒2

商的处理规则

商处理规则

202

倒11

即Mx+y=Mx±My×2-△E

313

倒1

…(031)8→MAR,

…(030)8→MAR,

314

顺17

正是存放SHR指令的内存单元。

正是存放SHR指令的主存单元。

314

顺18

从内存中取出目的操作数地址。

从主存中取出目的操作数地址。

314

倒18

…(030)8→MAR,

…(031)8→MAR,

314

倒14

将累加器内容取反

将累加器内容逻辑右移

浮点机器数精度是否可表示

53

倒1

为24位(单精度)或53位(双精度)

为24位(单精度)或52位(双精度)

54

倒5

如精心设计逻辑思路来

如精心设计逻辑电路来

55

顺5

称为检错码纠错码

称为检错纠错码

57

顺11

表2-9 例2.13被检验数据

表2-9 例2.14被检验数据

57

倒5

偶检验码所有位做异或运算

奇检验码所有位做…、

请求信号线BRN、BRN-1、……、

117

顺8

和计算机有很大影响

和计算机性能有很大影响

147

倒10

使次最低位及其后的进位输出与最低位的进位输出并行生成,

使次最低位及其后的进位输出并行生成,

152

图4-11

C0有实线连接到P1*与门输入端

C0无实线连接到P1*与门输入端

即Mx+y=Mx±My×2-△E

209

顺9

F=A∧B,实现与运算

E=A∧B,实现与运算

210

图4-41

C1

Ci

211

顺7

共有23根引脚,其中输出引脚8根、输入引脚15根

共有22根引脚,其中输出引脚8根、输入引脚14根

223

倒12

……与串行存储器的访问特性。

……与串行存储器的访问规则。

225

表5-1第二行第四列

倒6

0≤X≤2-n-1

0≤X≤2n-1

41

倒5

-(2-n-1)≤X≤0

-(2n-1)≤X≤0

42

顺18

[X]原=0 0110000

[X]原=0 0001101

44

顺9

补码最高为位为符号位

补码最高位为符号位

45

倒13

反码最高为位为符号位

补码最高位为符号位

47

顺1

[+0]移=[-0]补=1 00…00

[+0]移=[-0]移=1 00…00

地址+数据写+等待+数据读

113

倒6

由总线仲裁器发出的计数器值

由总线仲裁器发出计数器值

115

顺7

独立请求集中式仲裁方式

独立请求集中仲裁方式

115

图3-18

部件N-3中长向下箭线连于BRN-3

部件N-3中长向下箭线不能连于BRN-3

115

倒7

分别需要读取N-2、N-3、

分别需要读取N-1、N-2、

116

…存储器芯片引脚线的连接与图5-40类似。

269

图5-42

左上角与非门和A13直接连# 的片选

左上角与非门CE输入端加非“”,加一个或门,其输入端连CE和A13,其输出端连# 的片选,A13不直接连# 的片选

271

图5-43

CS(三处)

CE

272

图5-44