Hi3516A H.265核心开发板手册

基于Hi3516A的高清视频处理系统的硬件设计

基于Hi 3516A 的高清视频处理系统的硬件设计孙刚刘守山!樊丽山东科技大学电子通信与物理学院山东青岛266000摘要:提出了基于Hi 3516A 的高清视频处理系统的硬件设计方案。

利用IMX 185图像传感器采集图像,经过系统的编解码,然后通过HDMI 接口传输到显示器上。

主要介绍了电源管理模块的设计、存储器模块的设计、JTAG 接口的设计、HDMI 接口的设 计等。

关键词! Hi 3516 A $高清视频;视频处理系统4电子信息_________________________________________________________________________________科技风2017年8月下D O I :10.19392/j. cnki. 1671-7341.201716061视频处理系统在近年来一直受到人们广泛关注,然而低分 辨率的图像已经满足不了人们对图像视觉的要求。

本视频系 统采用Hi 3516A 芯片作为核心,可以实现1080P 的高清视频采 集和传输。

本文主要介绍了一套高清视频的采集与传输系统 的硬件设计,可以应用到医疗,交通和监控等众多领域。

1系统总体设计系统采用的Hi 3516A 是基于C 〇rtex -A 7内核,主频最高可 以达到600Mhz ,还具有32KB 的指令缓存和数据缓存和128KB 的二级缓存,其内部集成了 H .264/H .265/MJPEG/JPEG 的多 协议编解码器,既支持1080p @ 30fpS ,而且支持SM @30fpS 等的 多码流实时独立编码;视频输入接口支持BT 601,BT 656,BT & 1120;支持HDMI 接口的高清视频传输。

本系统采用CMOS 传 感器获得图像数据,通过Hi 3516A 芯片实现对视频的实时采集 与传输。

最终在PC 端等地实现高清播放。

系统的设计总框图 如图1所示。

图1系统总体框图2硬件的各模块设计2.1图像传感器模块本系统采用的是索尼200万像素的IMX 185的CMOS 传感 器,具有高灵敏度和多功能输出接口(低压LVDS 并行,串行和 CSI -2系列)的特点,支持光学尺寸1/2型全高清,具有高达120 帧/秒的10位A / D 转换模式,以及高达60帧/ s 的12位A / D 转换模式。

Hi3516A H.265核心开发板手册

Inode-cache hash table entries: 4096 (order: 2, 16384 bytes)

Memory: 64MB = 64MB total

Memory: 55128k/55128k available, 10408k reserved, 0K highmem

Virtual kernel memory layout:

.bss : 0xc0594924 - 0xc09918e0 (4084 kB)

SLUB: Genslabs=11, HWalign=64, Order=0-3, MinObjects=0, CPUs=1, Nodes=1

NR_IRQS:128

sched_clock: 32 bits at 49MHz, resolution 20ns, wraps every 86767ms

附核心板启动信息:

U-Boot 2010.06 (Nov 07 2014 - 17:58:56) NAND: Check nand flash controller v610. found Special NAND id table Version 1.36 Nand ID: 0x00 0x00 0x00 0x00 0x00 0x00 0x00 0x00 No NAND device found!!! 0 MiB Check spi flash controller v350... Found Spi(cs1) ID: 0xC2 0x20 0x18 0xC2 0x20 0x18 Spi(cs1): Block:64KB Chip:16MB Name:"MX25L128XX" In: serial Out: serial Err: serial Hit any key to stop autoboot: 0 16384 KiB hi_sfc at 0:0 is now current device

海思 3516AV200全功能核心板技术手册说明书

海思3516AV200全功能核心板技术手册一、应用场合:1. 适用于开发以下产品:(1)网络摄像机。

(2)4G/WIFI无线传输产品。

(3)安防监控产品。

(4)网络音视频产品。

(5)编码器。

(6)4K摄像机。

(7)1200万抓拍摄像机。

(8)多路摄像机。

(9)运动相机。

(10)航拍摄像机。

(11)人工智能(AI)产品。

2. 适用于学习linux平台、熟悉ARM开发。

3. 适用于需要熟悉海思音视频编解码、AI算法、多路图像处理、图像拼接、图像展开、4G/WIFI无线传输的开发人员。

二、型号:IPC-4KCODE-MAIN-V4三、产品特色:■核心芯片采用海思高性能多媒体处理器片上系统(SOC),内部集成双核A7(800MHZ)、A17(1.25GHZ)。

■集成了海思第四代ISP,支持WDR、多级降噪、六轴防抖及多种图像增强和矫正算法,为客户提供专业级的图像质量■图像质量优异、功耗低。

■采用标准的H.264/H.265 High Profile压缩算法,方便在窄带上实现高清晰的图像传输。

■最大支持600万编码,最高支持600万/30帧或者1080P/90帧H.264/H.265编码。

■支持多达2路Sensor输入,支持全景相机和无人机等多种产品应用。

■支持双向语音对讲。

■支持ONVIF协议,可对接海康、大华、美电贝尔、雄迈等NVR。

■支持GB28181协议。

■支持手机监看。

■支持WIFI:热点和STA模式。

■支持4G全网通:联通/移动/电信,5模或者7模。

■支持二次开发四、技术参数:五、产品外观及接口定义: 核心板正面:核心板背面:(一)、核心板与底板连接J3座子定义:(二)、核心板与底板连接座子J5定义:(三)、核心板与sensor1接接座子J2定义:(四)、核心板与sensor2连接座子J6定义:。

芯海单片机用户手册

5 电气特性 ....................................................................................................................................................... 51

2011.11.10

REV1.0

第 1 页,共 54 页

CSU8RF2111/CSU8RF2112

历史版本. REV 1.0

版本历史

修改内容 初版

版本历史

版本日期 2011-11-10

2011.11.10

REV1.0

第 2 页,共 54 页

2.1 2.1.1 2.1.2 2.1.3 2.2 2.3 2.4 2.5 2.6 2.7 2.7.1 2.8

CPU核 ..................................................................................................................................................... 6 存储器 ..................................................................................................................................................... 8 状态寄存器 ........................................................................................................................................... 10 INTE及INTF中断寄存器 ..................................................................................................................... 11 SFR ........................................................................................................................................................ 13 时钟系统 ............................................................................................................................................... 14 复位系统 ............................................................................................................................................... 16 中断 ....................................................................................................................................................... 18 定时器 0 ................................................................................................................................................ 20 定时/计数器 1 ....................................................................................................................................... 22 PWM...................................................................................................................................................... 24 I/O PORT ............................................................................................................................................... 25

基于Hi3516A的高清视频处理系统的硬件设计

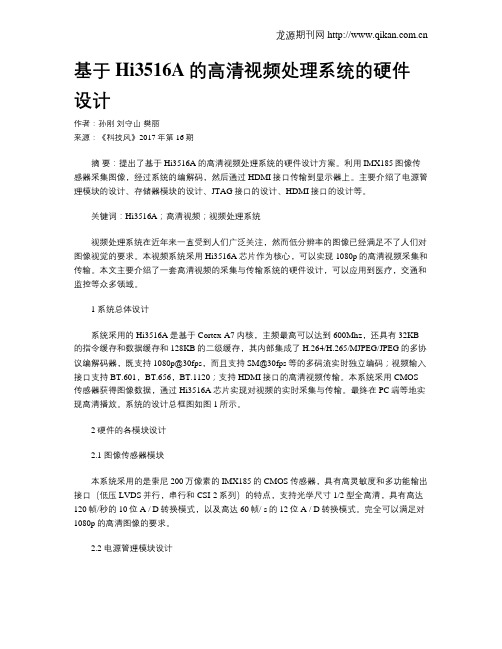

基于Hi3516A的高清视频处理系统的硬件设计作者:孙刚刘守山樊丽来源:《科技风》2017年第16期摘要:提出了基于Hi3516A的高清视频处理系统的硬件设计方案。

利用IMX185图像传感器采集图像,经过系统的编解码,然后通过HDMI接口传输到显示器上。

主要介绍了电源管理模块的设计、存储器模块的设计、JTAG接口的设计、HDMI接口的设计等。

关键词:Hi3516A;高清视频;视频处理系统视频处理系统在近年来一直受到人们广泛关注,然而低分辨率的图像已经满足不了人们对图像视觉的要求。

本视频系统采用Hi3516A芯片作为核心,可以实现1080p的高清视频采集和传输。

本文主要介绍了一套高清视频的采集与传输系统的硬件设计,可以应用到医疗,交通和监控等众多领域。

1 系统总体设计系统采用的Hi3516A是基于Cortex-A7内核,主频最高可以达到600Mhz,还具有32KB 的指令缓存和数据缓存和128KB的二级缓存,其内部集成了H.264/H.265/MJPEG/JPEG的多协议编解码器,既支持1080p@30fps,而且支持SM@30fps等的多码流实时独立编码;视频输入接口支持BT.601,BT.656,BT.1120;支持HDMI接口的高清视频传输。

本系统采用CMOS 传感器获得图像数据,通过Hi3516A芯片实现对视频的实时采集与传输。

最终在PC端等地实现高清播放。

系统的设计总框图如图1所示。

2 硬件的各模块设计2.1 图像传感器模块本系统采用的是索尼200万像素的IMX185的CMOS传感器,具有高灵敏度和多功能输出接口(低压LVDS并行,串行和CSI-2系列)的特点,支持光学尺寸1/2型全高清,具有高达120帧/秒的10位A / D转换模式,以及高达60帧/ s的12位A / D转换模式。

完全可以满足对1080p的高清图像的要求。

2.2 电源管理模块设计电源模块稳定地提供系统所需的电压和功率是系统运行的关键,本系统的电源模块需提供3.3V,1.8V,1.35V;1.2V和1.1V几种电源。

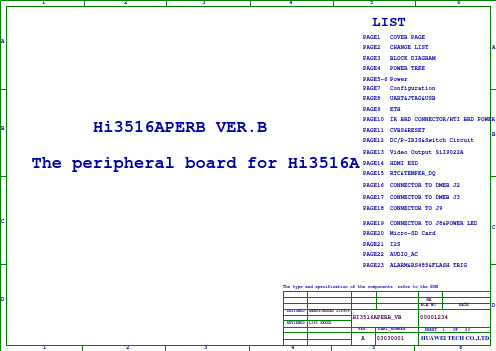

Hi3516APERB_VER_B_SCH

refer to the BOM NA ECA NO

D

DESIGNED REVIEWED WANGYONGHAO 206908

DATE

D

HI3516APERB_VB

LISI XXXXX

00001234

SHEET 1 OF 23

VER

PART_NUMBER

A 1 2 3 4 5

03030001

HUAWEI TECH CO.,LTD. 6

C

3V3 3V3_1V8_RGMII_IO C162 3V3 C18 R152 1V8 R153 NC/0 0 C209 10UF C43 100NF

1V2

U18 TPS79301

3 IN OUT 1

1V2_SII9022A 200mA C161 C17

C

6

EN

FB

5 1.2246V

10UF

100NF

BOOT_SEL(internal pull down) 0: SPI FLASH 1: NAND FLASH

1K 1K 1K 1K

POR_SEL VO_DAT1/BOOTROM_SEL

SFC_DEVICE_MODE(internal pull down) 0: Spi Nor flash 1: Spi Nand flash

D

HI3516APERB_VB

LISI XXXXX

00001234

SHEET 6 OF 23

VER

PART_NUMBER

A 1 2 3 4 5

03030001

HUAWEI TECH CO.,LTD. 6

1

2

3

4

5

6

Configuration

海思Hi3516 DataBrief(产品简介)

SPI Flash

Nand Flash

DDR2/3 SPI Audio Codec

VI0

Nand CVBS

BT.656 PCIe

VI1 GIRMAC

Hi3516

SDIO USB2.0 Host

VIV0I0

VI1 GMAC

UART0/2/3 UART1 GPIO SDIO

DSP

WiFi

PHY

POE

RS485 ALAR

A9@Max.800Mhz (32KB/32KB,256KB L2 Cache)

Image Subsystem

IVS ENGINE

VPP+TDE

ISP (3A\WDR)

CVBS/ BT1120

RAW/ BT1120+

BT656

AMBA3.0 BUS

Video Subsystem H.264 HP/MPEG4/ MJPEG/JPEG

测、周界防范、人脸检测、视频诊断等多 种智能分析应用 视频与图形处理 ● 支持de-interlace、图像增强、边缘增强、 3D去噪等前处理功能 ● 支持视频、图形输出抗闪烁处理 ● 支持视频1/16~8x缩放功能 ● 支持图形1/2~2x缩放功能 ● 8个区域的编码前处理OSD叠加 ● 2层(视频层、图形层1)视频后处理硬件 图像叠加 ISP ● 支持3A功能,3A的控制用户可调节 ● 支持WDR、强光抑制、背光补偿、 gamma、色彩增强

QVGA@30fps+1080P JPEG抓拍1fps − 720P@60fps+D1@30fps+CIF@30fps+

QVGA@30fps+720P JPEG抓拍1fps ● 支持JPEG抓拍3M Pixels@15fps~16M

Hi3516A_DEMO_V1_0_PCB布板布线要求

Hi3516A_DEMO_V1_0_PCB设计要求V1.0北京极图科技研发部陈戈 2015.3.27一、布局要求1、根据原理图,将每页中元器件按照芯片分堆,将阻容、磁珠、电感等器件靠近芯片或接插件放置;2、阻容、磁珠晶振等器件与BGA芯片距离控制在5mm,与其他芯片距离控制在0.7mm左右,便于调试和维修;3、注意板框与元器件距离,一般控制在1mm左右,以便于SMT贴片;4、晶振、SD卡座、端子座背面应远离功率器件:DC-DC、LDO、及芯片;5、接插件:BNC、音频座、电源座、HDMI、网座、SD卡座、USB座等应放置在板边,插口朝外;6、元器件布局,按照信号走向放置,便于后续调试;7、DC-DC电源芯片按照用户手册布局,注意铺地散热;8、IC电源去耦电容,尽量靠近芯片电源管脚;9、为便于调试维修,接插件之间勿放置小器件:如SMD的阻容、二极管等;10、布局考虑散热和美观,考虑板子重心是否合理;11、接插件之间距离10mm左右,便于更换;12、ADC器件注意在芯片背面割地,单点连接,信号线勿跨区域走线;13、各路主电源在电源层分割,与其它层打足够过孔连接。

14、ESD器件布局保证泄放回路面积足够小,接地管脚铺地。

二、布线要求1、电源线宽度按照原理图中POWER TREE要求的电流大小来设置,留足50%左右余量;2、布线区域距离板边1mm以上,以及固定孔周围1mm以上,禁止布线;3、每个芯片信号线回路面积要求足够小;4、相邻信号层走线垂直交叉;5、DDR3走线:信号走线避免穿越电源地分割区域,保持完整的参考平面,线宽不小于4mil;时钟线差分等长走线,CLK的走线长度小于4inch;控制线、命令线、地址线、数据线等长走线,具体请查看附录1。

6、USB、HDMI、RS485:差分等长,偏差50mil,走线宽度在5mil以上。

7、芯片时钟输入走线包地处理;8、CVBS视频信号包地处理;9、线与线之间满足3W原则,一般为10mil;10、ADC信号线不能跨越ADC背面地分割区域。

Hi3516A Hi3516D 硬件设计用户指南

National LP265 LP365 数据手册

C1995 National Semiconductor Corporation TL H 5023

RRD-B30M115 Printed in U S A

Absolute Maximum Ratings

If Military Aerospace specified devices are required please contact the National Semiconductor Sales Office Distributors for availability and specifications

LP265 LP365 Micropower Programmable Quad Comparator

查询LP265供应商

December 1994

LP265 LP365 Micropower Programmable Quad Comparator

General Description

The LP365 consists of four independent voltage comparators The comparators can be programmed four at the same time for various supply currents input currents response times and output current drives This is accomplished by connecting a single resistor between the VCC and ISET pins

VDC to 36 VDC or g2 0 VDC to g18 VDC)

Y Low supply current drain (10 mA) and low power

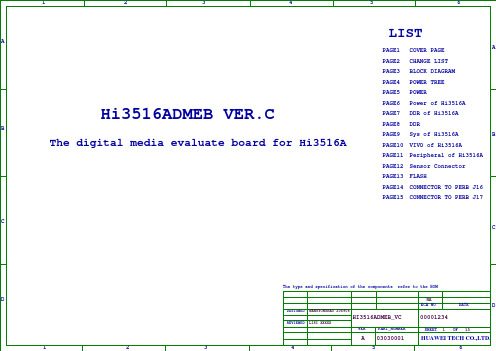

HI3516ADMEB_VER_C_SCH

VER

PART_NUMBER

A 1 2 3 4 5

03030001

HUAWEI TECH CO.,LTD. 6

1

2

3

4

5

6

BLOCK DIAGRAM

A A

B B

C C

The type and specification of the components

refer to the BOM NA ECA NO

1

2

3

4

5

6

LIST

A PAGE1 PAGE2 PAGE3 PAGE4 PAGE5 PAGE6 COVER PAGE CHANGE LIST BLOCK DIAGRAM POWER TREE POWER Power of Hi3516A DDR of Hi3516A DDR Sys of Hi3516A VIVO of Hi3516A Peripheral of Hi3516A Sensor Connector FLASH CONNECTOR TO PERB J16 CONNECTOR TO PERB J17 B A

DESIGNED REVIEWED WANGYONGHAO 206908

DATE

D

HI3516ADMEB_VC

LISI XXXXX

00001234

SHEET 4 OF 15

VER

PART_NUMBER

A 1 2 3 4 5

03030001

HUAWEI TECH CO.,LTD. 6

1

2

3

4

5

6

Power

The type and specification of the components

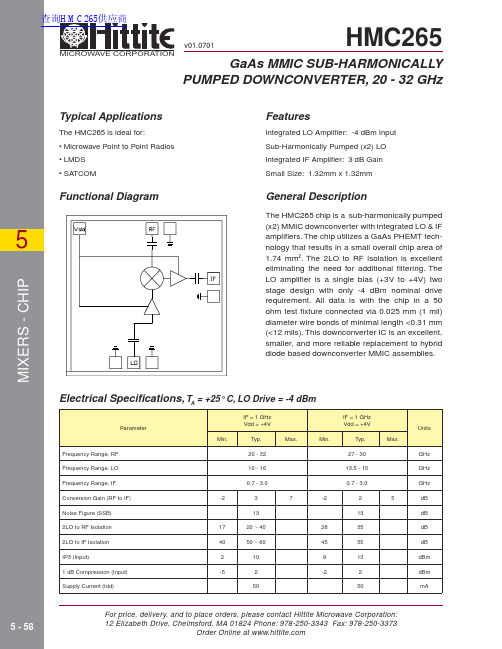

Hittite HMC265 数据手册

MICROWAVE CORPORATION MIXERS-CHIP5HMC265v01.0701General Description Features Functional Diagram Integrated LO Amplifi er: -4 dBm Input Sub-Harmonically Pumped (x2) LO Integrated IF Amplifi er: 3 dB Gain Small Size: 1.32mm x 1.32mm Electrical Specifi cations, T A = +25° C, LO Drive = -4 dBm Typical Applications The HMC265 is ideal for:• Microwave Point to Point Radios • LMDS • SA TCOM The HMC265 chip is a sub-harmonically pumped (x2) MMIC downconverter with integrated LO & IF amplifi ers. The chip utilizes a GaAs PHEMT tech-nology that results in a small overall chip area of 1.74 mm 2. The 2LO to RF isolation is excellent eliminating the need for additional fi ltering. The LO amplifi er is a single bias (+3V to +4V) two stage design with only -4 dBm nominal drive requirement. All data is with the chip in a 50 ohm test fi xture connected via 0.025 mm (1 mil) diameter wire bonds of minimal length <0.31 mm (<12 mils). This downconverter IC is an excellent, smaller, and more reliable replacement to hybrid diode based downconverter MMIC assemblies.GaAs MMIC SUB-HARMONICALL Y PUMPED DOWNCONVERTER, 20 - 32 GHz Parameter IF = 1 GHz Vdd = +4V IF = 1 GHz Vdd = +4V Units Min.Typ.Max.Min.Typ.Max.Frequency Range, RF 20 - 3227 - 30GHz Frequency Range, LO 10 - 1613.5 - 15GHz Frequency Range, IF 0.7 - 3.00.7 - 3.0GHz Conversion Gain (RF to IF)-237-225dB Noise Figure (SSB)1313dB 2LO to RF Isolation 1720 ~ 402835dB 2LO to IF Isolation 4050 ~ 604555dB IP3 (Input)210913dBm 1 dB Compression (Input)-52-22dBm Supply Current (Idd)5050mA 查询HMC265供应商M I X E R S - C H I P 5-20-15-10-50510182022242628303234C O N V E R S I O N G A I N (d B )RF FREQUENCY (GHz)182022242628303234RF FREQUENCY (GHz)Conversion Gain vs. Temperature @ LO = -4 dBm Vdd = +4V -20-15-10-50510C O N V E R S I O N G A I N (d B )-70-60-50-40-30-20-10010182022242628303234I S OL A T IO N (d B )RF FREQUENCY (GHz)182022242628303234RF FREQUENCY (GHz)Conversion Gain vs. Temperature @ LO = -4 dBm Vdd = +3VConversion Gain vs. LO Drive @ Vdd = +4V Conversion Gain vs. LO Drive@ Vdd = +3VPUMPED DOWNCONVERTER, 20 - 32 GHz502468101214161820182022242628303234T H I R D O R D E R I N T E R C E P T (d B m )RF FREQUENCY (GHz)182022242628303234RF FREQUENCY (GHz)IP3 vs. LO Drive @ Vdd = +4V IP3 vs. Temperature @ LO = -4 dBm, Vdd = +4V LO & RF Return Loss@ LO = -4 dBm, Vdd = +4V -20-15-10-500510152025303540R ETU R NLO S S (d B )FREQUENCY (GHz)PUMPED DOWNCONVERTER, 20 - 32 GHz IF Return Loss @ LO = -4 dBm, Vdd = +4V P1dB vs. Temperature@ LO = -4 dBm, Vdd = +4V IF Bandwidth @ LO = -4 dBm-20-15-10-500123456R ET UR NL OSS(dB )FREQUENCY (GHz)-5-4-3-2-10123182022242628303234P 1dB (d B m )RF FREQUENCY (GHz)0123456IF FREQUENCY (GHz)M I X E R S -C H I P 5Outline Drawing (See Handling Mounting Bonding Note)Absolute Maximum RatingsPUMPED DOWNCONVERTER, 20 - 32 GHzNOTES:1. ALL DIMENSIONS ARE IN INCHES [MM].2. DIE THICKNESS IS .004”.3. TYPICAL BOND P AD IS .004” SQUARE.4. BOND P AD SPACING CENTER TOCENTER IS .006”.5. BACKSIDE MET ALLIZA TION: GOLD.6. BOND P AD MET ALLIZA TION: GOLD.7. BACKSIDE MET AL IS GROUND.8. CONNECTION NOT REQUIRED FORUNLABELED BOND PADS.5MIC Assembly Techniques Mounting & Bonding Techiniques for Millimeterwave GaAs MMICs The die should be attached directly to the ground plane eutectically or with conductive epoxy (see HMC general Handling, Mounting, Bonding Note).50 Ohm Microstrip transmission lines on 0.127mm (5 mil) thick alumina thin fi lm substrates are recommended for bringing RF to and from the chip (Figure 1). If0.254mm (10 mil) thick alumina thin fi lm substrates must be used, the die shouldbe raised 0.150mm (6 mils) so that the surface of the die is coplanar with thesurface of the substrate. One way to accomplish this is to attach the 0.102mm(4 mil) thick die to a 0.150mm (6 mil) thick molybdenum heat spreader (moly-tab) which is then attached to the ground plane (Figure 2).Microstrip substrates should be brought as close to the die as possible in orderto minimize bond wire length. Typical die-to-substrate spacing is 0.076mm (3mils).An RF bypass capacitor should be used on the Vdd input. A 100 pF single layercapacitor (mounted eutectically or by conductive epoxy) placed no further than0.762mm (30 mils) from the chip is recommended. The photo in fi gure 3 shows atypical assembly for the HMC265 MMIC chip.PUMPED DOWNCONVERTER, 20 - 32 GHz Figure 3:Typical HMC265 AssemblyM I X E R S - C H I P 5PUMPED DOWNCONVERTER, 20 - 32 GHzHandling PrecautionsFollow these precautions to avoid permanent damage.Cleanliness: Handle the chips in a clean environment. DO NOT attempt to clean the chip using liquid cleaning systems.Static Sensitivity: Follow ESD precautions to protect against > ± 250V ESD strikes.Transients: Suppress instrument and bias supply transients while bias is applied. Use shielded signal and bias cables to minimize inductive pick-up.General Handling: Handle the chip along the edges with a vacuum collet or with a sharp pair of bent tweezers. The surface of the chip has fragile air bridges and should not be touched with vacuum collet, tweezers, or fi ngers.MountingThe chip is back-metallized and can be die mounted with AuSn eutectic preforms or with electrically conductive epoxy. The mounting surface should be clean and fl at.Eutectic Die Attach: A 80/20 gold tin preform is recommended with a work surface temperature of 255 °C and a tool temperature of 265 °C. When hot 90/10 nitrogen/hydrogen gas is applied, tool tip temperature should be 290 °C. DO NOT expose the chip to a temperature greater than 320 °C for more than 20 seconds. No more than 3 seconds of scrubbing should be required for attachment.Epoxy Die Attach: Apply a minimum amount of epoxy to the mounting surface so that a thin epoxy fi llet is observed around the perimeter of the chip once it is placed into position. Cure epoxy per the manufacturer’s schedule.Wire BondingBall or wedge bond with 0.025 mm (1 mil) diameter pure gold wire. Thermosonic wirebonding with a nominal stage temperature of 150 °C and a ball bonding force of 40 to 50 grams or wedge bonding force of 18 to 22 grams is recommended. Use the minimum level of ultrasonic energy to achieve reliable wirebonds. Wirebonds should be started on the chip and terminated on the package or substrate. All bonds should be as short as possible <0.31 mm (12 mils).。

Hi3516A Hi3516D 硬件设计用户指南

版本 03 02 01

00B04 00B03 00B02

00B01

修订说明

修改 1.1.3、1.2.1 和 1.4 小节 修改 1.2.5 小节 第一次正式版本发布,修改图 1-14 和图 1-15,添加图 118 和图 1-19,2.1.3 小节有新增内容。添加 Hi3516D 的相 关内容。

修改图 1-2 及图 1-17 1.3.3.2 章节,VI 接口中有修改。 第二次临时版本发布 新增第 3 章 ESD 设计建议,其他章节都涉及修改。 初始版本

产品版本 V100 V100

读者对象

本文档(本指南)主要适用于以下工程师: z 技术支持工程师 z 单板硬件开发工程师

修订记录

修订记录累积了每次文档更新的说明。最新版本的文档包含以前所有文档版本的更新 内容。

修订日期 2016-03-28 2015-11-02

版本 05 04

修订说明 1.2.5、1.3.5、1.3.8 小节涉及修改 修改 2.1.3 小节的相关内容

文档版本 05 (2016-03-28)

海思专有和保密信息 版权所有 © 深圳市海思半导体有限公司

i

Hi3516A/Hi3516D 硬件设计 用户指南

前言

修订日期 2015-06-15 2015-02-10 2014-12-20

2014-10-20 2014-09-25 2014-09-14

2014-07-15

Hi3516A/Hi3516D 硬件设计

用户指南

文档版本 发布日期

05 2016-03-28

版权所有 © 深圳市海思半导体有限公司 2014-2016。保留一切权利。

非经本公司书面许可,任何单位和个人不得擅自摘抄、复制本文档内容的部分或全部,并不得以任何 形式传播。

Hi3516A Demo单板用户指南

3.1 注意事项....................................................................................................................................................... 11 3.2 单板设置....................................................................................................................................................... 11 3.3 Sensor 板和 demo 板对接使用指南 ............................................................................................................. 14

修订记录

修订记录累积了每次文档更新的说明。最新版本的文档包含以前所有文档版本的更新 内容。

文档版本 00B01 (2014-09-18)

第 1 次临时版本发布。

文档版本 00B01 (2014-09-18)

海思专有和保密信息 版权所有 © 深圳市海思半导体有限公司

i

Hi3516A Demo 单板 用户指南

海思Hi3520开发工具套件(Hi3520_SHDK)说明书

Hi3520_SHDK说明书(海思Hi3520开发工具套件)雅仪科技提供海思半导体Hi35xx系列网络多媒体SOC处理器之软件开发包、硬件评估板,简称Hi35xx_SHDK。

SHDK包含Demo单板、开发文档、编译工具、驱程源码、媒体函数库、样例程序、应用Demo等。

基于此完整开发套件,客户可立即开始评估测试Hi35xx系列处理器硬件性能,并启动基于此处理器平台DVR/DVS/IPCam等视频监控/网络通信产品的软件开发调试工作。

1. 简介Hi3520 Demo单板是针对海思Hi3520 H.264编解码处理器芯片(以下简称为Hi3520芯片)开发的参考设计单板,用于给客户展示Hi3520芯片强大的多媒体处理功能和丰富的外围接口,同时为客户提供基于Hi3520芯片的硬件参考设计,使客户不需修改或者只需要简单修改参考设计的模块电路,就可以完成产品的硬件开发。

Hi3520 Demo单板支持Hi3520芯片的SDK开发、应用软件的开发和运行等。

Hi3520 Demo 单板通过串口和网口线与开发PC 连接,可以作为一个基本开发系统使用,或实现更完全的开发系统或演示环境,此时连接如下设备或部件:z电视机或监视器z视频源(如模拟摄像头)z音频源及音箱z USB 2.0 device 设备z ARM11仿真器z SATA 硬盘、SD Card 等存储设备Hi3520 Demo单板最多支持外接16路CVBS信号和16路音频信号。

Hi3520 Demo单板将音视频信号编码后,把码流传到网络上或存储在本地SATA硬盘,也可以自身解码后显示。

Hi3520 Demo单板典型应用场景如图1-1所示。

2. 功能特性Hi3520 Demo单板具有以下功能特性:z支持16 路CVBS输入,H264 Main Profile @ Level 3视频编解码,最大编码能力为8D1@30fps或32CIF@30fps。

z支持2路CVBS输出和1路VGA输出。

VH265 V00主板使用说明书

(VH265V00)手机模块应用简要说明书目录1.概述------------------------------------------------------------------3 2.原理框图---------------------------------------------------------------4 3.功能接口简介3.1音频接口-------------------------------------------------------------5 3.2LCD接口-------------------------------------------------------------6 3.3I/O接口--------------------------------------------------------------7 3.3.1充电功能-------------------------------------------------------------8 3.3.2耳机功能-------------------------------------------------------------8 3.3.3FM收音机天线--------------------------------------------------------8 3.3.4USB数据传输-----------------------------------------------------------8 3.3.5充电宝功能------------------------------------------------------------8 3.4电池接口--------------------------------------------------------------8 3.5天线馈点及RF测试点----------------------------------------------------9 3.6蓝牙-------------------------------------------------------------------9 3.7摄像头FPC接口----------------------------------------------------------10 3.8扩展按键接口------------------------------------------------------------11 3.9手电筒接口--------------------------------------------------------------123.10马达-------------------------------------------------------------------124.硬件设计建议----------------------------------------------------------13一、概述本说明书简要介绍VH265V00手机模块各接口定义及快速手机开发。

Hi3510 Linux开发环境用户指南(V1.00)

HISILICONHi3510 Linux开发环境用户指南V1.00Hi3510 Linux开发环境用户指南手册版本: V1.00B O M编码:深圳市海思半导体有限公司为客户提供全方位的技术支持,用户可与就近的海思公司办事处联系,也可直接与公司总部联系。

深圳市海思半导体有限公司地址:深圳市龙岗区坂田华为基地华为电气生产中心邮编:518129网址: 客户服务电话:+86-755-28788858客户服务传真:+86-755-28788838客户服务邮箱:support@声明Copyright ©2006深圳市海思半导体有限公司版权所有,保留一切权利。

非经本公司书面许可,任何单位和个人不得擅自摘抄、复制本书内容的部分或全部,并不得以任何形式传播。

、Hisilicon、海思,均为深圳市海思半导体有限公司的商标。

对于本手册中出现的其它商标,由各自的所有人拥有。

由于产品版本升级或其它原因,本手册内容会不定期进行更新。

除非另有约定,本手册仅作为使用指导,本手册中的所有陈述、信息和建议不构成任何明示或暗示的担保。

前言版本说明本手册对应产品版本为:Hi3510媒体解决方案平台版本为V100R001。

本手册简介本手册介绍了Hi3510视频评估板(VSEVB板)的Linux开发环境和各种系统软件的使用。

全书共分为7章和2个附录。

z第1章开发环境简介。

本章介绍如何搭建Hi3510视频评估板的Linux开发环境。

首先介绍了开发环境的组成,然后详细介绍了Linux主机中交叉编译工具和Hi3510视频评估板SDK的安装。

通过阅读本章,可以指导读者完成开发环境的搭建。

z第2章 HiBoot。

本章详细介绍海思半导体公司有限公司的BootLoader——HiBoot。

本章包括如何使用HiBoot以及如何编译HiBoot,并使用调试器将HiBoot烧写入Hi3510VSEVB板中。

z第3章 Linux内核。

介绍HiLinux内核的配置和编译。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Inode-cache hash table entries: 4096 (order: 2, 16384 bytes)

Memory: 64MB = 64MB total

Memory: 55128k/55128k available, 10408k reserved, 0K highmem

Virtual kernel memory layout:

## Booting kernel from Legacy Image at 82000000 ... Image Name: Linux-3.4.35 Image Type: ARM Linux Kernel Image (uncompressed) Data Size: 2957704 Bytes = 2.8 MiB Load Address: 80008000 Entry Point: 80008000 Loading Kernel Image ... OK

modules : 0xbf000000 - 0xc0000000 ( 16 MB)

.text : 0xc0008000 - 0xc0539000 (5316 kB)

.init : 0xc0539000 - 0xc055a67c ( 134 kB)

.data : 0xc055c000 - 0xc0594900 ( 227 kB)

vector : 0xffff0000 - 0xffff1000 ( 4 kB)

fixmap : 0xfff00000 - 0xfffe0000 ( 8ቤተ መጻሕፍቲ ባይዱ6 kB)

vmalloc : 0xc4800000 - 0xff000000 ( 936 MB)

lowmem : 0xc0000000 - 0xc4000000 ( 64 MB)

Hi3516A H.265 Encoder Board

Hi3516A 核心板适合于音视频、监控、机器视觉、图像处理等系统原型快 速搭建,用户专注于核心算法开发

核心板全部采用机器贴片焊接以确保质量

板内已烧录 UBOOT,Linux kernel 和文件系统,并提供 BIN 文件 核心板上已烧录 USB,以太网、SPI、SDIO、UART、I2C、802.11 等驱动 提供 Hi3516A 最新视频开发包 SDK 及源码 提供核心板原理图

OK

Starting kernel ...

Uncompressing Linux... done, booting the kernel. Booting Linux on physical CPU 0 Linux version 3.4.35 (pub@BVT-SDK-SERVER3) (gcc version 4.8.3 20131202 (prerelease) (Hisilicon_v300) ) #1 Fri Nov 7 17:59:57 HKT 2014 CPU: ARMv7 Processor [410fc075] revision 5 (ARMv7), cr=10c53c7d CPU: PIPT / VIPT nonaliasing data cache, VIPT aliasing instruction cache Machine: hi3516a

.bss : 0xc0594924 - 0xc09918e0 (4084 kB)

SLUB: Genslabs=11, HWalign=64, Order=0-3, MinObjects=0, CPUs=1, Nodes=1

NR_IRQS:128

sched_clock: 32 bits at 49MHz, resolution 20ns, wraps every 86767ms

48

... MAX_LOCKDEP_KEYS:

8191

... CLASSHASH_SIZE:

4096

... MAX_LOCKDEP_ENTRIES:

16384

... MAX_LOCKDEP_CHAINS:

32768

... CHAINHASH_SIZE:

16384

memory used by lock dependency info: 3679 kB

Console: colour dummy device 80x30

Lock dependency validator: Copyright (c) 2006 Red Hat, Inc., Ingo Molnar

... MAX_LOCKDEP_SUBCLASSES: 8

... MAX_LOCK_DEPTH:

我们支持您设计自己的外设板与 Hi3516A 核心板配合工作,您也可以选配 本店的外设板

如有定制需求,请联系 QQ 2768494362 或 Email: 2768494362@ Features

Hi3516A: Hi3516ARBCV100 DDR3: 1GByte SPI FLASH:128Mbit UART: TTL SD CARD: MicroSD Socket VIDEO INPUT CONNECTOR:

附核心板启动信息:

U-Boot 2010.06 (Nov 07 2014 - 17:58:56) NAND: Check nand flash controller v610. found Special NAND id table Version 1.36 Nand ID: 0x00 0x00 0x00 0x00 0x00 0x00 0x00 0x00 No NAND device found!!! 0 MiB Check spi flash controller v350... Found Spi(cs1) ID: 0xC2 0x20 0x18 0xC2 0x20 0x18 Spi(cs1): Block:64KB Chip:16MB Name:"MX25L128XX" In: serial Out: serial Err: serial Hit any key to stop autoboot: 0 16384 KiB hi_sfc at 0:0 is now current device

mtdparts=hi_sfc:1M(boot),3M(kernel),12M(rootfs)

PID hash table entries: 256 (order: -2, 1024 bytes)

Dentry cache hash table entries: 8192 (order: 3, 32768 bytes)

Memory policy: ECC disabled, Data cache writeback

Built 1 zonelists in Zone order, mobility grouping on. Total pages: 16256

Kernel command line: mem=64M console=ttyAMA0,115200 root=/dev/mtdblock2 rootfstype=jffs2

− 8-/10-/12-/14-bit RGB Bayer DC − BT.601, BT.656, or BT.1120 VI interface − HD CMOS sensor parallel interface (Upto 5 megapixels) THREE PERIPHERAL EXTENSION CONNECTOR: − USB2.0 − RGMII − SPI − SDIO − Video Output − Analog Audio − I2S − UART − Reset Out, Power SIZE: 51mm X 84mm

per task-struct memory footprint: 1152 bytes

Calibrating delay loop... 1196.85 BogoMIPS (lpj=5984256)

pid_max: default: 32768 minimum: 301 Mount-cache hash table entries: 512 Initializing cgroup subsys freezer CPU: Testing write buffer coherency: ok Setting up static identity map for 0x8040fb70 - 0x8040fbc8 NET: Registered protocol family 16 Serial: AMBA PL011 UART driver uart:0: ttyAMA0 at MMIO 0x20080000 (irq = 40) is a PL011 rev2 console [ttyAMA0] enabled uart:1: ttyAMA1 at MMIO 0x20090000 (irq = 41) is a PL011 rev2 bio: create slab <bio-0> at 0 SCSI subsystem initialized hi-spi-master hi-spi-master.0: hi_spi_probe: hisilicon soc spi host driver loaded for bus spi-0 with 1 chip select slaves attached hi-spi-master hi-spi-master.1: hi_spi_probe: hisilicon soc spi host driver loaded for bus spi-1 with 3 chip select slaves attached usbcore: registered new interface driver usbfs usbcore: registered new interface driver hub usbcore: registered new device driver usb Switching to clocksource timer0 NET: Registered protocol family 2 IP route cache hash table entries: 1024 (order: 0, 4096 bytes) TCP established hash table entries: 2048 (order: 2, 16384 bytes) TCP bind hash table entries: 2048 (order: 4, 73728 bytes) TCP: Hash tables configured (established 2048 bind 2048) TCP: reno registered UDP hash table entries: 64 (order: 0, 5120 bytes) UDP-Lite hash table entries: 64 (order: 0, 5120 bytes) NET: Registered protocol family 1 RPC: Registered named UNIX socket transport module. RPC: Registered udp transport module. RPC: Registered tcp transport module. RPC: Registered tcp NFSv4.1 backchannel transport module. VFS: Disk quotas dquot_6.5.2