Xilinx 开发板用户手册

Xilinx FPGA 中文手册-《Platform Flash PROM User Guide》中文版

《Platform Flash PROM User Guide》中文版FPGA的配置分为主串行和从串行两种,差别在于时钟源不同。

nCF为高时PROM的DO数据有效,nCE和OE使能。

P24和26介绍了接线图和引脚功能。

原型开发优势每写一次可以有4套不同的程序进行测试。

板子测试配置或安全升级设计的版本中写有诊断程序,如果发现原程序不满足要求,可以调用符合要求的程序重新执行,节省了调试时间。

PlatForm具有备份程序的功能。

防止不完整或损坏数据FPGA的所有IO口在DONE为低电平时均不可用,PlatForm满足这个要求。

为什么使用内部解压或晶振Platform PROM片上解压使得用户可以多存储50%的数据。

Platform PROM提供20MHz或者40MHz(默认)的时钟用于将配置数据从PROM送入FPGA。

内部晶振,特别是40MHz的操作只应用于解压模式。

否则,FPGA的CCLK或者外部晶振会用于驱动。

PROM的解压输出数据速率为内部时钟的一半,换言之,解压数据流配置时间是非压缩数据流的两倍。

如果需要快速配置,FPGA的BitGen-g compress方式可以作为压缩模式。

时钟CLKOUT信号在配置过程中,且在nCE低、OE/nRESET高时有效;无效时呈高组态并且需要外部上拉以避免不确定状态。

时钟速率可以配置,默认为1MHz,可以为1,3,6,12等,XCFxxS最大为33MHz。

PROM文件生成和烧写.bit(Bitstream)文件为输入数据流,.mcs文件为输出数据,.cfi文件为配置格式信息文件。

.bit文件为FPGA使用的二进制数据,.mcs文件为PROM运行文件,.cfi(Configuration format information)文件名字与前两者根目录相同。

标准的PROM文件为前两者。

在XCFxxP系列PROM使用多版本程序设计、CLKOUT、解压缩等功能时还需要使用.cfi文件。

AC7021B 开发板 用户手册说明书

文档版本控制目录文档版本控制 (2)(一)简介 (4)(二)ZYNQ芯片 (5)(三)DDR3 DRAM (7)(四)QSPI Flash (11)(五)eMMC Flash (12)(六)时钟配置 (14)(七)USB转串口 (15)(八)LED灯 (16)(九)复位按键 (18)(十)JTAG接口 (18)(十一)拨码开关配置 (19)(十二)电源 (20)(十三)结构图 (21)(十四)连接器管脚定义 (22)(一) 简介AC7021B(核心板型号,下同)核心板,ZYNQ 芯片是基于XILINX 公司的ZYNQ7000系列的XC7Z020-2CLG484I 。

ZYNQ 芯片的PS 系统集成了两个ARM Cortex™-A9处理器,AMBA®互连,内部存储器,外部存储器接口和外设。

ZYNQ 芯片的FPGA 内部含有丰富的可编程逻辑单元,DSP 和内部RAM 。

这款核心板使用了2片SK Hynix 公司的H5TQ4G63AFR-PBI 这款DDR3芯片,每片DDR 的容量为4Gbit ;2片DDR 芯片组合成32bit 的数据总线宽度,ZYNQ 和DDR3之间的读写数据时钟频率高达533Mhz ;这样的配置,可以满足系统的高带宽的数据处理的需求。

为了和底板连接,这款核心板的4个板对板连接器扩展出了PS 端的USB 接口,千兆以太网接口,SD 卡接口及其它剩余的MIO 口。

以及PL 端的BANK13, BANK33, BAN34和BANK35的几乎所有IO 口(198个),其中BANK33和BANK34的IO 的电平可以通过更换核心板上的LDO 芯片来修改,满足用户不用电平接口的要求。

对于需要大量IO 的用户,此核心板将是不错的选择。

而且IO连接部分,ZYNQ 芯片到接口之间走线做了等长和差分处理,并且核心板尺寸仅为60*60(mm ),对于二次开发来说,非常适合。

AC7021B 核心板正面图AC7021B 核心板背面图(二) ZYNQ 芯片开发板使用的是Xilinx 公司的Zynq7000系列的芯片,型号为XC7Z020-2CLG484I 。

FPGA开发板EP1C12用户手册(一版)

使用手册目 录第一章综述 (1)EP1C12核心板资源介绍 (1)FPGA开发板资源介绍 (2)第二章 系统模块功能介绍 (5)EP1C12核心板模块说明EP1C12F324C8芯片说明 (7)NOR FLASH模块说明 (8)SRAM模块说明 (9)FPGA接口I/O说明 (10)调试接口JTAG、AS说明 (11)其它功能模块 (12)EP1C12核心板使用注意事项 (15)FPGA开发平台模块说明液晶显示模块 (17)RTC实时时钟模块 (19)USB接口模块 (19)音频CODEC接口模块 (20)EEPROM存储模块 (21)数字温度传感器模块 (22)其它功能模块 (23)FPGA开发平台使用注意事项 (24)附表一核心板载资源与FPGAEP1C12I/O接口对照表 (25)附表二EP1C12与开发板硬件资源I/O接口对照表 (30)第一章综述FPGA开发来台是根据现代电子发展的方向,集EDA和SOPC系统开发为一体的综合性实验开发系统,除了满足高校专、本科生和研究生的SOPC教学实验开发之外,也是电子设计和电子项目开发的理想工具。

整个开发系统由核心板EP1C12、SOPC开发平台和扩展板构成,根据用户不同的需求配置成不同的开发系统。

EP1C12核心板EP1C12核心板为基于Altera Cyclone器件的嵌入式系统开发提供了一个很好的硬件平台,它可以为开发人员提供以下资源:1主芯片采用Altera Cyclone器件EP1C12F324C82EPCS4I8配置芯片34个用户自定义按键44个用户自定义LED51个七段码LED6标准AS编程接口和JTAG调试接口750MHz高精度时钟源8三个高密度扩展接口9系统上电复位电路10支持+5V直接输入,板上电源管理模块系统主芯片采用324引脚、BGA封装的E1C12 FPGA,它拥有12060个LE,52个M4K 片上RAM(共计239616bits),2个高性能PLL以及多达249个用户自定义IO。

xilinx700AN1400A用户手册

Red Cyclone开发板RCIII-3S700A/700AN/1400A 用户手册修订记录前言本手册适用于使用Red Cyclone系列开发板红色飓风三代XILINX版本的用户。

开发板由三部分组成:核心板,底板(基础功能扩展板)。

核心板与底板可以配合使用也可以单独使用核心板,核心板支持USB接口供电和直接5v电源供电两种模式,底板上不要外接电源模块。

配合底板这套开发板面向FPGA的所有用户,既可以用它来学习FPGA基础的设计知识,也可以只用核心模块配合用户自定义底板实现工程应用。

所以,设计本着简单实用,扩展性好的原则。

本开发套件配合较高容量的FPGA。

XC3S700A,XC3S1400A是xilinx主推高性价比产品,700AN更是xilinx 09推出的新产品,它的配置模式支持内部flash烧写,使得破解内部代码非常困难,加密性能大大提高,非常适合内部算法的加密处理。

该产品也可以作为产品开发的原型验证板或者IC前端设计验证板。

我们也希望大家在这套板上开发出有创意的产品。

同时,这套开发板也提供了一个SOPC(System On Programming Chip)平台,可以实现嵌入式的软CPU,如microblaze ,picroblaze等。

为嵌入式电子产品设计提供了又一种选择。

如何使用本用户手册:用户手册主要是使用户了解开发板上各部分功能模块,硬件连接到FPGA上的对应的管脚映射,介绍用到的芯片操作的基本原理,当然在这里只是一个简单的介绍,具体如何使用芯片请用户参照芯片手册。

由于本人水平有限,手册有错漏和不严谨之处在所难免,如果发现错误恳请发送邮件到xilinx◎,欢迎大家批评指正目录V3-RC3-3S700A/700AN/1400A用户手册 (1)修订记录............................................................................................................................................................... ..2前言. (3)目录 (4)开发板用户手册内容介绍 (6)CHAPTER 1主要器件及特性 (7)主要元器件介绍 (7)CHAPTER 2 核心板与底板接口 (9)核心板用户IO连接器 (9)底板用户IO连接器 (11)底板用户IO (11)CHAPTER 3 高速同步SDRAM (14)CHAPTER 4大容量,快速FLASH (16)CHAPTER 5高速异步SRAM (18)CHAPTER 6 FPGA配置方案 (21)JTAG接口 (21)AS接口 (21)CHAPTER 7 时钟分配 (22)CHAPTER 8 复位电路 (23)CHAPTER 9 LED数码管 (24)CHAPTER 10 系统电源接口 (25)CHAPTER 11USB 2.0接口 (26)CHAPTER 12 320AIC23音频编码芯片 (33)FPGA管脚映射 (33)该芯片主要有如下特性: (33)TLV320AIC23的使用 (34)1控制接口 (34)2控制寄存器的使用 (35)CHAPTER 13拨码开关按键开关 (36)拨码开关 (36)按键开关 (36)CHAPTER 14 七段数码管 (38)CHAPTER 15 PS/2 鼠标(键盘)接口 (41)键盘 (41)鼠标 (42)CHAPTER 16 RS-232 串口 (45)串行通信标准 (45)接收机设计 (46)发送机设计 (46)CHAPTER17 字符型液晶显示器 (49)介绍 (49)FPGA控制原理 (51)CHAPTER 18 蜂鸣器与红外线接口 (53)CHAPTER 19 SD卡接口 (54)附录A:原理图 (55)附录B, 主要元件的相关材料 (55)开发板用户手册内容介绍Chapter 1, “主要器件及特性”Chapter 2,“核心板与底板接口”核心板部分Chapter 3,“高速同步SDRAM”Chapter 4,“大容量快速FLASH”Chapter 5,“高速异步SRAM”Chapter 6,“FPGA配置方案”Chapter 7,“时钟分配”Chapter 8,“复位电路”Chapter 9,“LED数码管”Chapter 10,“系统电源接口”基础底板部分Chapter 11, “USB 2.0接口”Chapter 12, “320AIC23音频编码芯片” Chapter 13, “拨码开关按键开关”Chapter 14, “七段数码管”Chapter 15,“PS/2鼠标(键盘)接口” Chapter 16,“RS-232串口”Chapter 17,“字符型液晶显示器”Chapter 18, “蜂鸣器与红外线接口”Chapter 19,“SD卡接口”附录 A,“电路板原理图”附录 B,“主要元件的相关材料”注1 核心板分为三种版本:(1)xc3s700a4f484c+mt48lc4m16a+28f640j3 (2)xc3s700an4f484c+mt48lc4m16a+28f640j3 (3)xc3s1400a4f484c+mt48lc16m16a+28f128j3Chapter 1主要器件及特性本部分中描述了Red CycloneIII代xilinx开发板的设计原理和使用方法,作为开发板的配套材料。

黑金 AX7020 开发板 用户手册说明书

文档版本控制版权申明:本手册版权归属芯驿电子公司(上海)有限公司所有, 并保留一切权力。

非经本公司(书面形式),同意,任何单位及个人不得擅自摘录或修改本手册部分或全部内容,违者我们将追究其法律责任。

感谢您购买黑金开发板,在使用产品之前,请仔细地阅读该手册并且确保知道如何正确使用该产品,不合理的操作可能会损坏开发板,使用过程中随时参考该手册以确保正确使用。

此手册不断更新中,建议您使用时下载最新版本。

软件版本:本手册使用Xilinx官方提供的Vivado版本,请从Xilinx网站下载正确的版本和使用我们提供的软件版本安装。

黑金官网:黑金动力社区:黑金官方淘宝店:联系方式:************目录一、简介 (6)二、结构尺寸 (8)三、电源 (8)四、Z YNQ7000 (10)1)JTAG接口 (12)2)FPGA供电系统 (13)3)ZYNQ启动配置 (14)五、时钟配置 (14)5.1PS系统时钟源 (14)5.2PL系统时钟源 (15)六、P S端的外设 (16)6.1QSPI F LASH (16)6.2DDR3DRAM (17)6.3千兆以太网接口 (21)6.4USB2.0 (24)6.5USB转串口 (25)6.6SD卡槽 (27)6.7PS PMOD连接器 (28)6.8用户LED (29)6.9用户按键 (30)七、P L端的外设 (31)7.1HDMI接口 (31)7.2EEPROM24LC04 (33)7.3实时时钟DS1302 (34)7.4扩展口J10 (36)7.5扩展口J11 (38)7.6用户LED (41)7.7用户按键 (42)黑金基于XILINX ZYNQ7000开发平台的开发板2016款正式发布了,型号为:AX7020 。

此款开发平台是XILINX 的Zynq7000 SOC 芯片的解决方案。

它采用ARM+FPGA SOC 技术将双核ARM Cortex-A9 和FPGA可编程逻辑集成在一颗芯片上。

DSP TMS320C665x + Xilinx Artix-7 FPGA开发板规格书

Revision HistoryDraft Date Revision No. Description2018/4/3 V1.4 1.修改开发板简介。

2.修改产品订购型号。

3.修改开发板套件清单。

4.修改附录A开发例程。

2018/2/24 V1.3 1.修改电气特性。

2.修改附录A例程。

2017/12/19 V1.2 1.修改产品订购型号。

2.新增附录A例程。

2017/4/25 V1.1 1.更新为A2版本。

2016/12/14 V1.0 1.初始版本。

目录1 开发板简介 (4)2 典型运用领域 (6)3 软硬件参数 (6)4 开发资料 (10)5 电气特性 (10)6 机械尺寸图 (11)7 产品订购型号 (12)8 开发板套件清单 (13)9 技术支持 (13)10 增值服务 (14)更多帮助....................................................................................................... 错误!未定义书签。

附录A 开发例程.. (15)1开发板简介基于TI KeyStone C66x多核定点/浮点DSP TMS320C665x + Xilinx Artix-7 FPGA处理器;TMS320C665x主频为1.0/1.25GHz,每核运算能力高达40GMACS和20GFLOPS,每核心32KByte L1P、32KByte L1D、1MByte L2,1MByte多核共享内存,8192个多用途硬件队列,支持DMA传输;FPGA芯片型号为XC7A100T-2FGG484I,逻辑单元101K个,DSP Slice 240个;TMS320C665x与FPGA内部通过uPP、EMIF16、SRIO连接;双SFP接口,传输速率可高达5Gbit/s,可接SFP光口模块或SFP电口模块;千兆以太网口,可接工业网络摄像机;工业级FMC连接器,支持高速ADC、DAC和视频输入输出等FMC-LPC标准模块; PCI Express 2.0高速数据传输接口,双通道,每通道通信速率可高达5GBaud;Serial Rapid I/O高速数据传输接口,双通道,每通道通信速率可高达5GBaud;可通过DSP配置及烧写FPGA程序,DSP和FPGA可以独立开发,互不干扰;支持uPP、EMIF16、SPI、McBSP、TIMER、GPIO等常见接口;连接稳定可靠,开发板采用工业级精密B2B高速连接器,关键大数据接口使用高速连接器,保证信号完整性;提供丰富的开发例程,入门简单,支持裸机和SYS/BIOS操作系统。

xilinx使用步骤

Xilinx软件使用步骤目录基本操作1. 打开xilinx2. open project3. New project4. 创建新的 .vhd文件5. 建立波形文件6. 综合7. 仿真8. 下载程序到电路板中需要注意的问题1.生成顶层原理图2.建立.ucf文件3. implement时出错的原因4.仿真时的问题基本操作1. 打开xilinx图1 打开xilinx界面2. open project图2 open project图3 查找要打开的.ise文件单击打开后,出现在左侧box中。

图4 open project3. New project顶层文件类型,原理图类型选Schematic,否则选择HDL;单击下一步,通过右侧value各项目,配置器件类型,即FPGA 型号。

注意:此处配置错误的话,综合时会出现放不下或者些不进去的错误。

配置完成后,单击下一步,出现创建源文件对话框如下图所示。

不需做设置更改,直接点击下一步,出现添加现有源对话框如下图所示。

不需做任何设置,直接单击下一步,出现New project information对话框,如下图所示。

确认信息无误后,单击完成,创建的新的project即出现在主页面左侧Sources in project中,如下图所示。

4. 创建新的 .vhd文件右击主页面左侧Sources in project中xc2s200-5pq208,在右键菜单中选择New source,如下图所示;出现New source对话框;左侧选择VHDL Module,右侧输入文件名,如下图所示,单击下一步;出现define vhdl source对话框,输入端口名,输入输出类型和MSB,LSB, 如下图所示,然后单击下一步,出现信息对话框,如下图所示,确认无误后,单击完成。

然后主页面如下图所示:5. 建立波形文件在主页面,编程之后保存。

在如下图所示位置右击.vhd文件,选择new source选项。

Xilinx ISE 使用入门手册

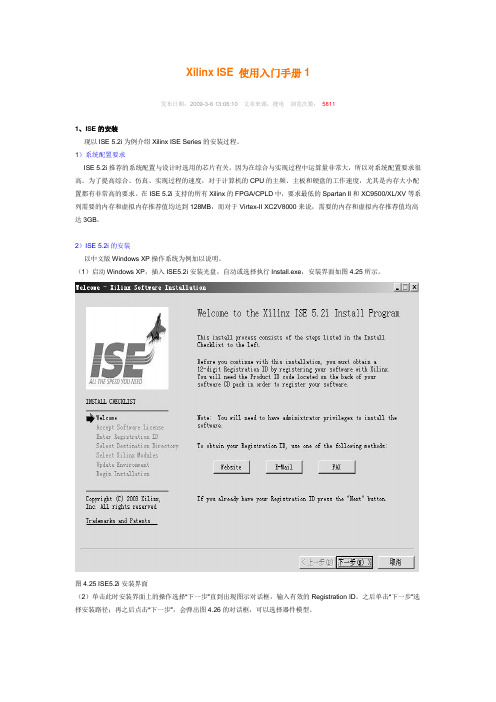

Xilinx ISE 使用入门手册1发布日期:2009-3-6 13:06:10文章来源:搜电浏览次数:58111、ISE的安装现以ISE 5.2i为例介绍Xilinx ISE Series的安装过程。

1)系统配置要求ISE 5.2i推荐的系统配置与设计时选用的芯片有关。

因为在综合与实现过程中运算量非常大,所以对系统配置要求很高。

为了提高综合、仿真、实现过程的速度,对于计算机的CPU的主频、主板和硬盘的工作速度,尤其是内存大小配置都有非常高的要求。

在ISE 5.2i支持的所有Xilinx的FPGA/CPLD中,要求最低的Spartan II和XC9500/XL/XV等系列需要的内存和虚拟内存推荐值均达到128MB,而对于Virtex-II XC2V8000来说,需要的内存和虚拟内存推荐值均高达3GB。

2)ISE 5.2i的安装以中文版Windows XP操作系统为例加以说明。

(1)启动Windows XP,插入ISE5.2i安装光盘,自动或选择执行Install.exe,安装界面如图4.25所示。

图4.25 ISE5.2i安装界面(2)单击此时安装界面上的操作选择“下一步”直到出现图示对话框,输入有效的Registration ID。

之后单击“下一步”选择安装路径;再之后点击“下一步”,会弹出图4.26的对话框,可以选择器件模型。

图4.26 器件模型选择对话框(3)点击“下一步”,如图4.27所示,可以选择器件种类。

图4.27 器件种类选择对话框通过以上步骤后,可根据具体情况来选择,继续“下一步”即可完成安装。

安装完成后,环境变量应作如下描述:若操作系统是Windows NT/2000/XP,选择开始->控制面板->系统->选项->系统->高级->环境变量,在环境变量中加入:变量名:Xilinx变量值:C:Xilinx(即安装路径)具体设置如图4.28所示。

图4.28 环境变量设置操作图3)安装第三方软件在PC上安装完ISE之后,还需要安装第三方仿真软件,如ModelSim等。

AV7K300 开发板用户手册说明书

XILINX FPGA开发平台用户手册AV7K300开发板AV7K300开发板用户手册2/39芯驿电子科技(上海)有限公司文档版本控制文档版本修改内容记录REV1.0创建文档AV7K300开发板用户手册目录文档版本控制 (2)一、开发板简介 (5)二、AC7K325B核心板 (7)(一)简介 (7)(二)FPGA芯片 (8)(三)DDR3DRAM (9)(四)QSPI Flash (13)(五)时钟配置 (15)(六)LED灯 (16)(七)电源 (17)(八)结构图 (19)(九)连接器管脚定义 (19)三、扩展板 (28)(一)简介 (28)(一)光纤接口 (29)(二)PCIe插槽 (30)(三)SDI输出接口 (32)(四)SDI输入接口 (33)(五)USB转串口 (34)(六)SD卡槽 (34)(七)40针扩展口 (35)(八)按键和LED灯 (37)(九)JTAG调试口 (38)(十)电源 (38)(十一)结构尺寸图 (39)3/39AV7K300开发板用户手册4/39芯驿电子科技(上海)有限公司芯驿电子科技(上海)有限公司基于XILINX KINTEX-7开发平台的开发板(型号:AV7K300)2020款正式发布了正式发布了,为了让您对此开发平台可以快速了解,我们编写了此用户手册。

这款KINTEX-7FPGA 开发平台采用核心板加扩展板的模式,方便用户对核心板的二次开发利用。

核心板使用XILINX 的KINTEX-7芯片XC7K325的解决方案,含挂载了4片512MB 的高速DDR3SDRAM 芯片和1片128Mb 的QSPI FLASH 芯片。

在底板设计上我们为用户扩展了丰富的外围接口,比如1个PCIex8接口、4路光纤接口、2路SDI 输出接口、2路SDI 输入接口、1路UART 串口接口、1路SD 卡接口、2个40针扩展接口等等。

满足用户各种高速数据交换,数据存储,视频传输处理以及工业控制的要求,是一款"专业级“的FPGA 开发平台。

Xilinx开发工具手册

Xilinx 开发工具手册目录1ISE的介绍和使用 (3)1.1 简介 (3)1.2 软件使用 (4)1.2.1 创建工程 (4)1.2.2 设计输入 (6)1.2.3 引脚分配 (10)1.2.4 仿真 (12)1.2.5 器件编程 (16)2常用第三方EDA工具 (20)2.1 最常用的FPGA仿真工具——ModelSim (20)2.1.1 建立Xilinx器件仿真库 (20)2.1.2在ISE中链接ModelSim (21)2.2 最常用的FPGA仿真工具——Synplify (23)3ISE高级调试工具——ChipScope (25)3.1 简介 (25)3.1.1 ChipScope的安装 (25)3.1.2 ChipScope的软件分类 (26)3.1.3 使用方法 (26)3.2 软件使用 (27)3.2.1生成正确的ChipScope文件 (27)3.2.2正确的配置ChipScope相关选项 (29)3.2.3分析ChipScope信号 (33)Xilinx在可编程逻辑器件市场中雄居领先地位。

本文立足工程实践,介绍了Xilinx的FPGA/CPLD开发工具ISE在进行FPGA设计时的使用方法。

1ISE的介绍和使用1.1 简介使用Xilinx的FPGA时,ISE是必备的设计工具。

ISE可以完成FPGA开发的全部流程,包括设计输入、仿真、综合、布局布线、生成bit文件、配置以及在线调试等,功能非常强大。

ISE是一个集成的开发环境,集成了大量实用工具,包括HDL Editor、IP核生成器CORE Generator System、约束编辑器Constraints Editor、静态时序分析工具Static Timing Analyzer、布局规划工具FloorPlanner、FPGA编辑工具FPGA Editor和功耗分析工具Xpower等,这些工具可以帮助设计人员完成设计任务,或者提高工作效率。

EDK-GKB-3S400AN手册

EDK EDK--GKB GKB--3S400AN 开发板发板 USER MANUAL USER MANUALVer 1.0深圳市依元素科技有限公司 E-elements Technologies Co., Ltd.版权所有 侵权必究 All rights reserved目录Table of Contents1、Introduction 简介 (5)1.1 Purpose 目的 (5)1.2 Scope 范围 (5)2、功能简介 (5)2.1 主要特点 (6)2.2 功能单元 (6)3 硬件配置及描述 (7)3.1 FPGA芯片 (8)3.2 Clocks (8)3.3 Static RAM (8)3.4JTAG Port (13)3.5 Switch与FPGA配置 (13)3.6LED (15)3.7 扩展I/O接脚 (15)图目录List of Figure图1 EDK-GKB-3S400A开发板实物图 (6)图2 EDK-GKB-3S400A开发板结构图 (7)图3 功能模块图 (8)图4 写循环1 (9)图5 写循环2 (10)图6 读循环1 (10)图7 读循环2 (11)图8 读循环3 (11)图9 读循环4 (12)图10 14-Pin 和6-Pin的JTAG Port与FPGA连接图 (13)图11 Switch与FPGA连接图 (14)表目录List of Table表1 硬件配置 (7)表2 引脚描述 (9)表3 SRAM真值表 (9)表4 引脚定义 (13)表5 扩展I/O接脚定义如下表 (15)EDK-GKB-3S400AN User Manual摘 要Abstract Abstract::EDK-GKB-3S400AN 开发板采用XILINX 最新90ns 工艺的Spartan3S400AN FPGA,针对学校教育市场与科研研发单位,推出的一款具有超强I/O 扩展接口的FPGA 开发平台。

睿智FPGA开发板用户手册1.0版本

伟欣科技®睿智FPGA 2.0开发板 用户手册我们的FPGA开发网官方网站:官方淘宝店: /邮箱:OurFPGA@QQ群:155291300提醒:请您在使用此开发板前,认真阅读此说明书,并将此电子书妥善保管,在开发学习中,可能会经常使用查询!(以上促销信息有时效性,以官网及淘宝店通知为准)没有购买开发板的朋友,也欢迎您登陆网站,在普通会员区,仍提供了约200多门视频教程下载(截止到2011年8月1日的数量,每周会更新添加,数量还在增加中。

),欢迎您来访!现在立即去体验一下:开发板简介FPGA与EDA技术是目前相当热门的技术,翻遍各大招聘网站电子类招聘信息,类似“精通FPGA技术,熟悉Verilog VHDL语言”等字眼已经为应聘者所熟悉;甚至,有的时候,“熟悉FPGA”就意味着高薪!实际上,FPGA技术已经成为目前电子行业应用最为广泛的技术之一,未来的就业和发展前景相当好!目前有众多朋友热切的期望能学习FPGA知识,FPGA技术实践性极强,拥有一块适合学习需求的FPGA开发板是非常有必要的!睿智FPGA开发板正是为此推出的一套高性价比开发板!此开发板由“伟欣科技®”精心设计开发,采用 Altera公司的CycloneII系列芯片EP2C5Q208C8(兼容EP2C8Q208C8)作为核心处理器进行设计,CycloneII系列芯片可以说是目前市场上性价比最高的芯片,比第一代芯片设计上、内部的逻辑资源上都有很大的改进,同时价格也可以被广大用户接受。

睿智FPGA开发板采用核心板与接口板分离的方式,核心板上除FPGA、各类存储器以及用户扩展PACK外,还有按键、LED及电源插座等。

因为有用户扩展PACK,核心板完全可以脱离接口板而单独使用,通过PACK,用于自己的设计或电子设计大赛,扩展性极好。

接口板上集成了最常用和经典外围接口,所有的外设经过精心分配及设计,不需要进行任何跳线设置,实验时非常方便!此外,对于重点外设的关键信号都设置了测试点,方便用户使用逻辑分析仪、示波器、万用表等进行信号测量。

MYD-C7Z010 20 用户手册说明书

MYD-C7Z010/20 产品用户手册版本V1.32019 年7 月4 日版本记录版本号说明时间V1.0 初始版本2015/5/11 V1.1 增加eMMC,看门狗和复位电路的描述2015/7/28 V1.2 替换产品图片,将看门狗描述移到核心板手册2015/8/312019/7/04 V1.3 更新U-Boot版本;更新linux kernel版本;支持QT5.11.3;使用标准的Linux Framebuffer 驱动目录1.1产品简介 (1)1.2产品预览 (1)第2 章硬件资源介绍 (2)2.1核心板硬件资源 (2)2.2底板硬件资源 (2)第3 章硬件指南 (5)3.1板上接口说明 (5)3.2PS 单元接口 (6)3.2.1以太网 (6)3.2.2USB (6)3.2.3CAN (6)3.2.4串口 (7)3.2.5I2C (7)3.2.6按键 (7)3.2.7JTAG (7)3.2.8TF 卡 (7)3.2.9实时时钟 (7)3.2.10eMMC (7)3.3PL 单元接口 (7)3.3.1FMC (8)3.3.2Pmod (8)3.3.3XADC (8)3.3.4SATA、SFP、PCI-E (8)3.4 复位电路 (8)第4 章软件资源介绍 (9)4.1Linux 软件资源 (9)第5 章机械参数 (10)附录一售后服务与技术支持 (12)第1 章产品概述1.1 产品简介MYD-C7Z010/20 开发板是由MYC-C7Z010/20 核心板加MYB-C7Z010/20 底板组成,以Xilinx Zynq-7010/7020 作为核心的嵌入式核心板。

采用了Xilinx 最新的基于28nm 工艺流程的Zynq-7000 All Programmable SoC 平台,将ARM 处理器和FPGA 架构紧密集成,PS 单元拥有双核ARM Cortex-A9 MPCore 的高性能,低功耗特性,在设计中能更好的满足各种工业需要。

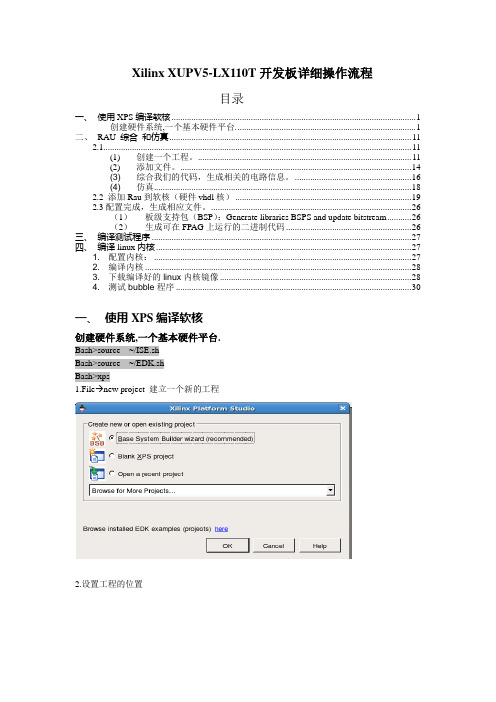

Xilinx XUPV5-LX110T开发板详细操作流程

Xilinx XUPV5-LX110T开发板详细操作流程目录一、使用XPS编译软核 (1)创建硬件系统,一个基本硬件平台. (1)二、RAU 综合和仿真 (11)2.1 (11)(1) 创建一个工程。

(11)(2) 添加文件。

(14)(3)综合我们的代码,生成相关的电路信息。

(16)(4)仿真 (18)2.2 添加Rau到软核(硬件vhdl核) (19)2.3配置完成,生成相应文件。

(26)(1)板级支持包(BSP):Generate libraries BSPS and update bitstream (26)(2)生成可在FPAG上运行的二进制代码 (26)三、编译测试程序 (27)四、编译linux内核 (27)1. 配置内核: (27)2. 编译内核 (28)3. 下载编译好的linux内核镜像 (28)4. 测试bubble程序 (30)一、使用XPS编译软核创建硬件系统,一个基本硬件平台.Bash>source ~/ISE.shBash>source ~/EDK.shBash>xps1.File new project 建立一个新的工程2.设置工程的位置ok3. 选择―I would like to create a new design‖ ,点击next选择我们的硬件平台: LX110T,继续next。

4.选择MicroBlaze ,接下来是定制硬件。

5.使能On-chip H/W debug module, Cache setup 和FPU6. 选择XPS_UART16550 as RS232_Uart_1, 并使用中断use interrupt (UART是通用异步串行口的意思RS232是UART的一种。

用作连接串口,监视和操作系统)7. 继续―next‖,(未提到的硬件设备可选可不选),直到出现Hard_Ethernet_MAC(以太网网卡)。

选择该设备,并选择Scatter gather DMA(直接内存存取)5. 接下来选择DDR2_SDRAM(二代内存,片外)6. 选择―add Peripheral‖, 添加一个定时器,模式选Two timers are present,并允许中断use Interrupt。

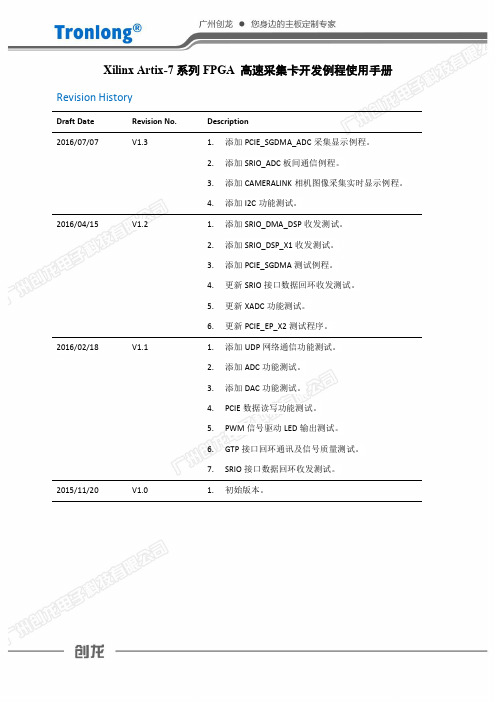

Xilinx Artix-7系列FPGA 高速采集卡开发例程使用手册

Xilinx Artix-7系列FPGA 高速采集卡开发例程使用手册Revision HistoryDraft Date Revision No. Description2016/07/07 V1.3 1.添加PCIE_SGDMA_ADC采集显示例程。

2.添加SRIO_ADC板间通信例程。

3.添加CAMERALINK相机图像采集实时显示例程。

4.添加I2C功能测试。

2016/04/15 V1.2 1.添加SRIO_DMA_DSP收发测试。

2.添加SRIO_DSP_X1收发测试。

3.添加PCIE_SGDMA测试例程。

4.更新SRIO接口数据回环收发测试。

5.更新XADC功能测试。

6.更新PCIE_EP_X2测试程序。

2016/02/18 V1.1 1.添加UDP网络通信功能测试。

2.添加ADC功能测试。

3.添加DAC功能测试。

4.PCIE数据读写功能测试。

5.PWM信号驱动LED输出测试。

6.GTP接口回环通讯及信号质量测试。

7.SRIO接口数据回环收发测试。

2015/11/20 V1.0 1.初始版本。

目录1 基于下载器的程序加载与烧写 (4)1.1程序加载 (4)1.2程序烧写 (8)2 采集卡功能测试 (10)2.1LED——流水灯测试 (10)2.2KEY——按键测试 (10)2.3PWM——PWM信号驱动LED输出测试 (11)2.4UART——UART回环测试 (11)2.5EEPROM——IIC总线写入和读取测试 (13)2.6DDR3——DDR3的读写测试 (14)2.7XADC——XADC功能测试 (16)2.8UDP_DEMO——UDP网络通信功能测试 (18)2.9ADC_AD9613——ADC功能测试 (20)2.10DAC_AD9706——DAC功能测试 (21)2.11PCIE_EP_X2——PCIE数据读写功能测试 (23)2.12PCIE_SGDMA——PCIE SGDMA的传输功能测试 (27)2.13PCIE_SGDMA_ADC——ADC数据通过PCIE传输到PC波形显示 (36)2.14GTP_CONNECTION——GTP接口回环通讯及信号质量测试 (37)2.15FPGA_SRIO——SRIO接口数据回环收发测试 (41)2.16SRIO_DSP_X1——SRIO板间通信测试 (46)2.17SRIO_DMA_DSP——SRIO_DMA方式收发测试 (48)2.18SRIO_ADC——SRIO板间ADC通讯测试 (51)2.19CAMERALINK_VGA_V1——CAMERALINK相机图像采集实时显示 (52)2.20I2C——I2C功能测试 (54)备注:●如实验无特别说明,表示广州创龙Artix-7采集卡均在VIVADO开发平台做对应实验。

Xilinx Zynq 开发手册

HZZD-MEZYNQ 硬件使用手册

第 1 页 共 38 页

阅前须知

阅前须知

声明

北京合众致达科技有限公司保留随时对其产品进行修正、改进和完善的权利,客户在下 单前应获取相关信息的最新版本,并验证这些信息是正确的。本文档一切解释权归北京合众 致达科技有限公司所有。

北京合众致达科技有限公司 © 2012 版权所有 京 ICP 备 12015578 号-1 技术支持:35 互联

HZZD-MEZYNQ 硬件使用手册

HZZD-MEZYNQ 硬件使用手册

主题 文档号 创建时间 最后修改 版本号 文件名 文件格式

HZZD-MEZYNQ 硬件使用手册 1.1 2015-08-04 2016-04-18 1.1 HZZD-MEZYNQ rd Document

HZZD-MEZYNQ 硬件使用手册

第 2 页 共 38 页

修改记录

修改记录

版本号 1.0 1.1

日期 2015.11.30 2016.04.18

修改人 赵彦彦 赵彦彦

注释 初始版本 更正扩展接口处信号描述错误

HZZD-MEZYNQ 硬件使用手册

第 3 页 共 38 页

目录

目录

1 概述.............................................................................................................................................6 1.1 硬件结构框图.................................................................................................................... 6 1.2 硬件实物图........................................................................................................................ 7

ARTIX-7 FPGA 开发平台 用户手册说明书

ARTIX-7 FPGA 开发平台用户手册1.0目录1、开发板简介: (3)2、开发板功能描述 (6)2.1 Artix-7 FPGA 引脚分配 (6)2.2 扩展接口 (6)2.3 电源 (10)2.3.1 电源变换 (10)2.3.2电源分配功能 (10)2.3.3电源启动顺序 (10)2.4 有源晶振 (10)2.5 FPGA启动 (11)2.6 LED和按键 (12)2.6.1 LED (12)2.6.2 按键 (15)2.7 XADC (17)2.8 DDR3 (18)2.9 SPI FLASH (19)2.9.1 FLASH (19)2.9.2 USER FLASH (19)2.10 / JTAG接口 (20)2.10.1 JTAG (20)2.10.2 USER JTAG (20)2.11 蜂鸟与FPGA连接 (21)1、开发板简介:正面背面此款开发板使用的是 Xilinx 公司的 Artix-7 系列 FPGA ,型号XC7A35T-1FTG256C ,256个引脚的 FBGA 封装。

此款 FPGA 的资源如下图所示:其中,主要的参数:逻辑单元 Logic Cells :33280; 乘法器 DSP48:90;可配置逻辑块 CLBs :400Kb ; Block RAM :1800Kb ; 时钟单元 CMTs :5; 可用 IO 数量:210 个; 内核电压:1.0V ;工作温度:0——﹢85℃;图为整个系统的结构示意图:FPGAXC7A35T晶振+5V电源接口 JTAG 口USER_JTAG 口PMOD口FLASHUSER_ FLASH256MByte DDR33.3V 电源1.0V电源1.8V电源DDR 电源 用户按键拨动开关配置指示灯用户LED 灯用户RGB 灯高速接插件电源指示灯电源开关Arduino兼容接口1.5V 电源Arduino 兼容接口2、开发板功能描述2.1 Artix-7 FPGA 引脚分配XC7A35T-1FTG256C共有5个I/0 Bank,其中U2E是FPGA专用的配置Bank,其2.2 扩展接口开发板有P1、P2、JP1三个用户接口。

1-2 详解基于创龙TI DSP TMS320C6678 + Xilinx FPGA Kintex-7开发板的硬件说明书2

封面(根据需求选用封面,美工设计模板)TL6678F-EasyEVM开发板硬件说明书前言TL6678F-EasyEVM是广州创龙基于SOM-TL6678F核心板而研发的一款多核高性能DS P+FPGA开发板。

开发板采用核心板+底板方式,底板采用沉金无铅工艺的8层板设计,尺寸为247.33mm*139.8mm,它为用户提供了SOM-TL6678F核心板的测试平台。

为了方便用户开发和参考使用,上面引出了各种常见的接口,可以帮助用户快速评估SOM-TL66 78F核心板的整体性能。

广州创龙SOM-TL6678F核心板基于TI KeyStone C66x多核定点/浮点TMS3206678 + Xilinx Kintex-7 FPGA设计的高性能DSP+FPGA高速大数据采集处理器,采用沉金无铅工艺的14层板设计,尺寸为112mm*75mm,经过专业的PCB Layout保证信号的完整性,和经过严格的质量管控,满足多种环境应用。

详解基于创龙TI DSP TMS320C6678 + Xilinx FPGA Kintex-7的开发板特点: 基于TI KeyStone C66x多核定点/浮点DSP TMS320C6678 + Xilinx Kintex-7 FPGA的高性能信号处理器;TI TMS320C6678集成8核C66x,每核主频1.0/1.25GHz,每核运算能力高达40GMACS 和20GFLOPS,每核心32KByte L1P、32KByte L1D、512KByte L2,4MByte多核共享内存,8192个多用途硬件队列,支持DMA传输;FPGA芯片型号为XC7K325T-2FFG676I,逻辑单元326K个,DSP Slice 840个,8对速率为12.5Gb/s高速串行收发器,兼容XC7K160T/410T-2FFG676I;TMS320C6678与FPGA内部通过I2C、EMIF16、SRIO连接,其中SRIO每通道传输速度最高可达到5GBaud;外设接口丰富,集成PCIe、EMIF16、双千兆网口等多种高速接口,同时支持SPI、GPI O、TIMER等常见接口;FPGA扩展接口,可连多通道AD、DA等模块,拓展能力强;XADC接口,模拟到数字转换,可灵活配置逻辑输入,片内或片外参考电压可选;2个SFP+接口,传输速率可高达10Gbit/s,可接SFP+光口模块或SFP+电口模块;2个工业级FMC连接器,支持高速ADC、DAC和视频输入输出等FMC-LPC标准模块;可通过DSP配置及烧写FPGA程序,DSP和FPGA可以独立开发且互不干扰;工业级精密B2B连接器,0.5mm间距,稳定,易插拔,防反插,所有数据接口使用高速连接器,保证信号完整性。

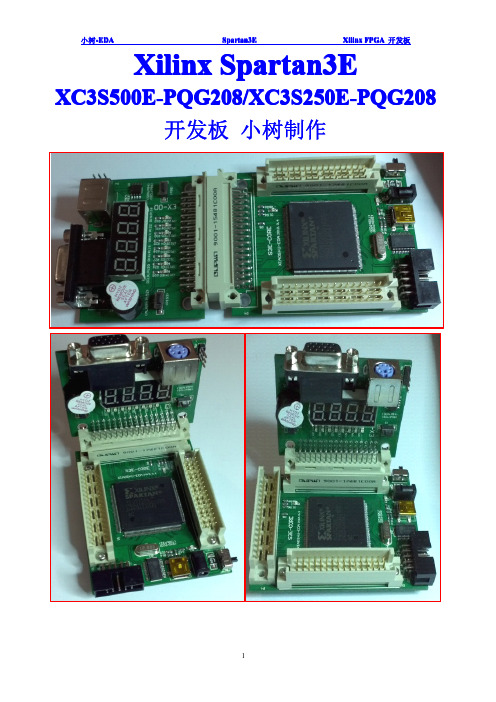

XILINX-S3E开发板(完整版)手册2012.3.39

always @(posedge clk)begin //run led, if(!rst)begin led<=8'hff;led_n<=0;end else begin led<=8'hff; led[led_n]<=0; if(counter==0)led_n<=led_n+1; end end always @(posedge clk)begin // interval time set, 2^24/50000000=0.33s if(!rst)counter<=0; else counter<=counter+1; end endmodule

8、编写 testbench ,这里注意:仿真的时候为了能看到效果,这里把源代码中的

6 个系统时钟就可能完成一个循环的计 reg[23:0]counter 改为 reg[7:0]counter .这样每过 25 256 数,否则时间太长,仿真器要运行很长的时间。 在 Simulation 选择 New Source 过程和上面过程基本相同。 执行

6、继续单击 Next ,之后单击 finish,弹出的对话框点击 Yes.之后可以看到 如图所示:

11

小树-EDA

Spartan3E

Xilinx FPGA 开发板

7、填写源代码,填入如下代码:

module run_led(clk,rst,led); //module port input input output reg reg reg clk;//system clock rst;//system reset [7:0] led; // 8bits led [7:0] led; [23:0]counter; //time counter [2:0]led_n; // decied the led to be lighted

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SP605 Hardware User GuideUG526 (v1.6) July 18, 2011© Copyright 2009–2011 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners. DISCLAIMERThe information disclosed to you hereunder (the “Materials”) is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR ST ATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials, or to advise you of any corrections or update. Y ou may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at /warranty.htm; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications:/warranty.htm#critapps.Revision HistoryThe following table shows the revision history for this document.Date Version Revision10/07/09 1.0Initial Xilinx release.11/09/09 1.1•Updated Figure1-17 and Figure1-23.•Changed speed grade from -2 to -3.•Miscellaneous typographical edits.02/01/10 1.1.1Minor typographical edits to Table1-24 and Table1-25.05/18/10 1.2Updated Figure1-2. Added Note 6 to Table1-11. Updated board connections forSFP_TX_DISABLE in Table1-12. Added note about FMC LPC J63 connector in 18. VITA57.1 FMC LPC Connector. Updated U1 FPGA Pin column for FMC_LA00_CC_P/N inTable1-28. Updated description of PMBus Pod and TI Fusion Digital Power SoftwareGUI in Onboard Power Regulation. Updated Appendix B, VITA 57.1 FMC LPCConnector Pinout, and Appendix C, SP605 Master UCF.06/16/10 1.3Updated 2. 128 MB DDR3 Component Memory. Added note 1 to Table1-30.09/24/10 1.4Updated description of Fusion Digital Power Software in Onboard Power Regulation.02/16/11 1.5Revised oscillator manufacturer information from Epson to SiTime in Table1-1. Revisedoscillator manufacturer information from Epson to SiTime on page page23. Deleted noteon page 44 referring to J55: “Note: This header is not installed on the SP605 as built.”Revised values for R50 and R216 in Figure1-12. Revised oscillator manufacturerinformation from Epson to SiTime on page page69.07/18/11 1.6Corrected “jitter” to “stability” in section Oscillator (Differential), page23. Revised thefeature and notes descriptions for reference numbers 6 and 12 in Table1-1, page10.Revised FPGA pin numbers for ZIO and RZQ in Table1-4, page14. Added Table1-29,page52, Table1-31, page55, and table notes in Table1-30.SP605 Hardware User Guide UG526 (v1.6) July 18, 2011SP605 Hardware User Guide 3UG526 (v1.6) July 18, 2011Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2Preface: About This GuideGuide Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5Additional Documentation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5Additional Support Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6Chapter 1: SP605 Evaluation BoardOverview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7Additional Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9Related Xilinx Documents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10Detailed Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101. Spartan-6 XC6SLX45T-3FGG484 FPGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12I/O Voltage Rails . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132. 128 MB DDR3 Component Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133. SPI x4 Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164. Linear BPI Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18FPGA Design Considerations for the Configuration Flash . . . . . . . . . . . . . . . . . . . . . . . 205. System ACE CF and CompactFlash Connector. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206. USB JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227. Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23Oscillator (Differential). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23Oscillator Socket (Single-Ended, 2.5V or 3.3V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24SMA Connectors (Differential). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 258. Multi-Gigabit Transceivers (GTP MGTs). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 259. PCI Express Endpoint Connectivity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2810. SFP Module Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3011. 10/100/1000 Tri-Speed Ethernet PHY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3112. USB-to-UART Bridge. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3313. DVI CODEC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3414. IIC Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 358-Kb NV Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3615. Status LEDs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38Ethernet PHY Status LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39FPGA INIT and DONE LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4016. User I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41User LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41User Pushbutton Switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42User DIP Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43User SIP Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44User SMA GPIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4517. Switches. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46Power On/Off Slide Switch SW2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46Table of ContentsSP605 Hardware User Guide UG526 (v1.6) July 18, 2011FPGA_PROG_B Pushbutton SW3 (Active-Low). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47SYSACE_RESET_B Pushbutton SW9 (Active-Low) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47System ACE CF CompactFlash Image Select DIP Switch S1 (Active-High) . . . . . . . . . . 48Mode DIP Switch SW1 (Active-High). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4918. VITA 57.1 FMC LPC Connector. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5019. Power Management. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52AC Adapter and 12V Input Power Jack/Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52Onboard Power Regulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54Configuration Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57Appendix A: Default Jumper and Switch Settings Appendix B: VITA 57.1 FMC LPC Connector Pinout Appendix C: SP605 Master UCF Appendix D: ReferencesPreface About This GuideThis manual accompanies the Spartan®-6 FPGA SP605 Evaluation Board and containsinformation about the SP605 hardware and software tools.Guide ContentsThis manual contains the following chapters:•Chapter1, SP605 Evaluation Board, provides an overview of and details about thecomponents and features of the SP605 board.•Appendix A, Default Jumper and Switch Settings.•Appendix B, VITA 57.1 FMC LPC Connector Pinout.•Appendix C, SP605 Master UCF.•Appendix D, References.Additional DocumentationThe following documents are available for download at/products/spartan6/.•Spartan-6 Family OverviewThis overview outlines the features and product selection of the Spartan-6 family.•Spartan-6 FPGA Data Sheet: DC and Switching CharacteristicsThis data sheet contains the DC and switching characteristic specifications for theSpartan-6 family.•Spartan-6 FPGA Packaging and Pinout SpecificationsThis specification includes the tables for device/package combinations and maximumI/Os, pin definitions, pinout tables, pinout diagrams, mechanical drawings, andthermal specifications.•Spartan-6 FPGA Configuration User GuideThis all-encompassing configuration guide includes chapters on configurationinterfaces (serial and parallel), multi-bitstream management, bitstream encryption,boundary-scan and JTAG configuration, and reconfiguration techniques.•Spartan-6 FPGA SelectIO Resources User GuideThis guide describes the SelectIO™ resources available in all Spartan-6 devices.•Spartan-6FPGA Clocking Resources User GuideSP605 Hardware User Guide 5 UG526 (v1.6) July 18, 2011Preface:About This GuideThis guide describes the clocking resources available in all Spartan-6 devices,including the DCMs and PLLs.•Spartan-6 FPGA Block RAM Resources User GuideThis guide describes the Spartan-6 device block RAM capabilities.•Spartan-6 FPGA GTP Transceivers User GuideThis guide describes the GTP transceivers available in the Spartan-6 LXT FPGAs.•Spartan-6 FPGA DSP48A1 Slice User GuideThis guide describes the architecture of the DSP48A1 slice in Spartan-6FPGAs andprovides configuration examples.•Spartan-6 FPGA Memory Controller User GuideThis guide describes the Spartan-6 FPGA memory controller block, a dedicatedembedded multi-port memory controller that greatly simplifies interfacingSpartan-6FPGAs to the most popular memory standards.•Spartan-6 FPGA PCB Designer’s GuideThis guide provides information on PCB design for Spartan-6 devices, with a focus onstrategies for making design decisions at the PCB and interface level.Additional Support ResourcesTo search the database of silicon and software questions and answers or to create atechnical support case in WebCase, see the Xilinx website at:/support. SP605 Hardware User GuideUG526 (v1.6) July 18, 2011Chapter1 SP605 Evaluation BoardOverviewThe SP605 board enables hardware and software developers to create or evaluate designstargeting the Spartan®-6 XC6SLX45T-3FGG484 FPGA.The SP605 provides board features common to many embedded processing systems. Somecommonly used features include: a DDR3 component memory, a 1-lane PCI Express®interface, a tri-mode Ethernet PHY, general purpose I/O and a UART. Additional userdesired features can be added through mezzanine cards attached to the onboard highspeed VITA-57 FPGA Mezzanine Connector (FMC) low pin count (LPC) connector.Features, page8 provides a general listing of the board features with details provided inDetailed Description, page10.Additional InformationAdditional information and support material is located at:•/sp605This information includes:•Current version of this user guide in PDF format•Example design files for demonstration of Spartan-6 FPGA features and technology•Demonstration hardware and software configuration files for the System ACE™ CFcontroller, Platform Flash configuration storage device, and linear flash chip•Reference Design Files•Schematics in PDF format and DxDesigner schematic format•Bill of materials (BOM)•Printed-circuit board (PCB) layout in Allegro PCB format•Gerber files for the PCB (Many free or shareware Gerber file viewers are available onthe Internet for viewing and printing these files.)•Additional documentation, errata, frequently asked questions, and the latest newsFor information about the Spartan-6 family of FPGA devices, including product highlights,data sheets, user guides, and application notes, see the Spartan-6 FPGA website at/support/documentation/spartan-6.htm.SP605 Hardware User Guide 7 UG526 (v1.6) July 18, 2011SP605 Hardware User GuideUG526 (v1.6) July 18, 2011Chapter 1:SP605 Evaluation BoardFeaturesThe SP605 board provides the following features (see Figure 1-2 and Table 1-1):• 1. Spartan-6 XC6SLX45T-3FGG484 FPGA • 2. 128 MB DDR3 Component Memory • 3. SPI x4 Flash • 4. Linear BPI Flash• 5. System ACE CF and CompactFlash Connector • 6. USB JTAG •7. Clock Generation •Fixed 200 MHz oscillator (differential)•Socket with a 2.5V 27MHz oscillator (single-ended)•SMA connectors (differential)•SMA connectors for MGT clocking (differential)•8. Multi-Gigabit Transceivers (GTP MGTs)•FMC LPC connector •SMA •PCIe•SFP module connector •9. PCI Express Endpoint Connectivity •Gen1 x1•10. SFP Module Connector•11. 10/100/1000 Tri-Speed Ethernet PHY •12. USB-to-UART Bridge •13. DVI CODEC •14. IIC Bus •IIC EEPROM - 1KB •D VI COD EC •DVI connector •FMC LPC connector •SFP Module connector •15. Status LEDs •Ethernet Status •FPGA INIT •FPGA D ONE •16. User I/O •USER LED GPIO •User pushbuttons •CPU Reset pushbutton •User D IP switch - GPIO •User SMA GPIO connectorsSP605 Hardware User Guide 9UG526 (v1.6) July 18, 2011Overview•17. Switches •Power On/Off slide switch •System ACE CF Reset pushbutton•System ACE CF bitstream image select DIP switch •Mode D IP switch•18. VITA 57.1 FMC LPC Connector •19. Power Management •AC Adapter and 12V Input Power Jack/Switch •Onboard Power Regulation•Configuration Options • 3. SPI x4 Flash (both onboard and off-board)• 4. Linear BPI Flash• 5. System ACE CF and CompactFlash Connector •6. USB JTAGBlock DiagramFigure 1-1 shows a high-level block diagram of the SP605 and its peripherals.Figure 1-1:SP605 Features and BankingSP605 Hardware User Guide UG526 (v1.6) July 18, 2011Chapter 1:SP605 Evaluation BoardRelated Xilinx DocumentsPrior to using the SP605 Evaluation Board, users should be familiar with Xilinx resources. See the following locations for additional documentation on Xilinx tools and solutions:•ISE: /ise•Answer Browser: /support •Intellectual Property: /ipcenterDetailed DescriptionFigure 1-2 shows a board photo with numbered features corresponding to Table 1-1 and the section headings in this document.The numbered features in Figure 1-2 correlate to the features and notes listed in Table 1-1.Figure 1-2:SP605 Board Photo15e1316b197a15h1234815g8517c7c93, 14 (on backside)7b 101861216c1116a15f15c17d16d17b15b 15a17a19b15dUG526_02 _050610Table 1-1:SP605 FeaturesNumberFeatureNotesSchematic Page1Spartan-6 FPGAXC6SLX45T-3FGG484 FPGA 2–72DDR3 Component Memory Micron MT41J64M16LA-187E 93SPI Header Ext. x4SPI Flash x4 (on backside)Winbond W25Q64VSFIG184Linear BPI Flash x16Numonyx JS28F256P30T95195System ACE CompactFlashSocketXCCACE-TQ144I Controller206USB UART (USB-to-UARTBridge)Silicon Labs CP2103GM327Clock Generation200 MHz OSC, oscillator socket,SMA connectors13, 14a. 200 MHz oscillator SiTime 200 MHz 2.5V LVDS14b. Oscillator socket, single-ended, LVCMOSMMD Components 2.5V 27 MHz14c. SMA connectors SMA pair P(J41) / N(J38)138GTP port SMA x4 andMGT Clocking SMA (REFCLK)MGT RX,TX Pairs x4 SMA MGTREFCLK x2 SMA139PCIe 1-lane edge conn.(Gen 1)Card Edge Connector, 1-lane12 10SFP Module Cage/Connector AMP 136073-112 11Ethernet 10/100/1000Marvell M88E1111 EPHY11 12USB JTAG Conn. (USB Mini-B)USB JTAG Download Circuit15 13DVI Codec and Video Connector Chrontel CH7301C-TF16,17 14IIC EEPROM (on backside)ST Micro M24C08-WDW6TP1515Status LEDs10, 11, 14,18, 20, 25,27, 31, 33a. FMC Power Good10b. System ACE CF Status 11c. FPGA INIT and DONE14d. Ethernet PHY Status18e. JTAG USB Status20f. FPGA Awake27g. TI Power Good31h. MGT AVCC, DDR3 TermPwr Good3316a. User LEDs (4)Red LEDs (active-High)14b. User Pushbuttons (4)Active-High14c. User DIP Switch (4-pole)4-pole (active-High)14d. User SMA (2)GPIO x2 SMA13Number Feature Notes Schematic PageSP605 Hardware User Guide 1. Spartan-6 XC6SLX45T -3FGG484 FPGAA Xilinx Spartan-6 XC6SLX45T-3FGG484 FPGA is installed on the SP605 Evaluation Board.ReferencesSee the Spartan-6 FPGA Data Sheet. [Ref 1]ConfigurationThe SP605 supports configuration in the following modes:•JTAG (using the included USB-A to Mini-B cable)•JTAG (using System ACE CF and CompactFlash card)•Master SPI x4•Master SPI x4 with off-board device •Linear BPI FlashFor details on configuring the FPGA, see Configuration Options .Mode switch SW1 (see Table 1-32, page 57) is set to 10 = Slave SelectMAP to choose the System ACE CF default configuration.ReferencesSee the Spartan-6 FPGA Configuration User Guide for more information. [Ref 2]17SwitchesPower, Configuration, Pushbutton Switches14, 18, 20,25a. SP605 Power On-Off Slide Switch25b. FPGA Mode DIP Switch 18c. System ACE CFConfiguration DIP Switch 20d. FPGA PROG, CPU Reset, and System ACE CF Reset Pushbutton Switches14, 2018FMC LPC Connector Samtec ASP-134603-011019a. Power Management Controller2x TI UCD9240PFC 21, 26b. Mini-Fit Type 6-Pin, ATX Type 4-pin12V input power connectors25NumberFeatureNotesSchematic PageI/O Voltage RailsThere are four available banks on the XC6SLX45T-3FGG484 device. Banks 0, 1, and 2 areconnected for 2.5V I/O. Bank 3 is used for the 1.5V DDR3 component memory interface ofSpartan-6 FPGA’s hard memory controller. The voltage applied to the FPGA I/O banksused by the SP605 board is summarized in Table1-2.Table 1-2:I/O Voltage Rail of FPGA BanksFPGA Bank I/O Voltage Rail0 2.5V1 2.5V2 2.5V3 1.5VReferencesSee the Xilinx Spartan-6 FPGA documentation for more information at/support/documentation/spartan-6.htm.2. 128 MB DDR3 Component MemoryThere are 128 MB of DDR3 memory available on the SP605 board. A 1-Gb MicronMT41J64M16LA-187E (96-ball) DDR3 memory component is accessible through Bank 3 ofthe LX45T device. The Spartan-6 FPGA hard memory controller is used for data transferacross the DDR3 memory interface’s 16-bit data path using SSTL15 signaling. The SP605board supports the “standard” VCCINT setting of 1.20V ± 5%. This setting provides thestandard memory controller block (MCB) performance of 667Mb/s for DDR3 memory ina -3 speed grade device. Signal integrity is maintained through DDR3 resistor terminationsand memory on-die terminations (ODT), as shown in Table1-3 and Table1-4.Table 1-3:Termination Resistor RequirementsSignal Name Board Termination On-Die Termination MEM1_A[14:0]49.9Ω to V TT –MEM1_BA[2:0]49.9Ω to V TT –MEM1_RAS_N49.9Ω to V TT –MEM1_CAS_N49.9Ω to V TT –MEM1_WE_N49.9Ω to V TT –MEM1_CS_N100Ω to GND –MEM1_CKE 4.7KΩ to GND –MEM1_ODT 4.7KΩ to GND –MEM1_DQ[15:0] –ODTMEM1_UDQS[P,N], MEM1_LDQS[P,N] –ODTMEM1_UDM, MEM1_LDM –ODTSP605 Hardware User Guide Table 1-5 shows the connections and pin numbers for the DDR3 Component Memory.MEM1_CK[P ,N]100Ω differential at memorycomponent–Notes:1.Nominal value of V TT for DDR3 interface is 0.75V .Table 1-4:FPGA On-Chip (OCT) Termination External Resistor Requirements U1 FPGA PinFPGA Pin NumberBoard Connection for OCTZIO M7No Connect RZQK7100Ω to GROUNDTable 1-5:DDR3 Component Memory ConnectionsU1 FPGA PinSchematic Net NameMemory U42Pin NumberPin NameK2MEM1_A0N3A0K1MEM1_A1P7A1K5MEM1_A2P3A2M6MEM1_A3N2A3H3MEM1_A4P8A4M3MEM1_A5P2A5L4MEM1_A6R8A6K6MEM1_A7R2A7G3MEM1_A8T8A8G1MEM1_A9R3A9J4MEM1_A10L7A10/AP E1MEM1_A11R7A11F1MEM1_A12N7A12/BCN J6MEM1_A13T3NC/A13H5MEM1_A14T7NC/A14J3MEM1_BA0M2BA0J1MEM1_BA1N8BA1H1MEM1_BA2M3BA2R3MEM1_DQ0G2DQ6R1MEM1_DQ1H3DQ4P2MEM1_DQ2E3DQ0Table 1-3:Termination Resistor Requirements (Cont’d)Signal NameBoard TerminationOn-Die TerminationReferencesSee the Micron Technology, Inc. DDR3 SDRAM Specification for more information. [Ref 12]Also, see the Spartan-6 FPGA Memory Controller User Guide . [Ref 3]P1MEM1_DQ3F2DQ2L3MEM1_DQ4H7DQ7L1MEM1_DQ5H8DQ5M2MEM1_DQ6F7DQ1M1MEM1_DQ7F8DQ3T2MEM1_DQ8C2DQ11T1MEM1_DQ9C3DQ9U3MEM1_DQ10A2DQ13U1MEM1_DQ11D7DQ8W3MEM1_DQ12A3DQ15W1MEM1_DQ13C8DQ10Y2MEM1_DQ14B8DQ14Y1MEM1_DQ15A7DQ12H2MEM1_WE_B L3WE_B M5MEM1_RAS_B J3RAS_B M4MEM1_CAS_B K3CAS_B L6MEM1_ODT K1ODT K4MEM1_CLK_P J7CLK_P K3MEM1_CLK_N K7CLK_N F2MEM1_CKE K9CKE N3MEM1_LDQS_P F3LDQS_P N1MEM1_LDQS_N G3LDQS_N V2MEM1_UDQS_P C7UDQS_P V1MEM1_UDQS_N B7UDQS_N N4MEM1_LDM E7LDM P3MEM1_UDM D3UDM E3MEM1_RESET_BT2RESET_BTable 1-5:DDR3 Component Memory Connections (Cont’d)U1 FPGA PinSchematic Net NameMemory U42Pin NumberPin Name3. SPI x4 FlashThe Xilinx Spartan-6 FPGA hosts a SPI interface which is visible to the Xilinx iMPACTconfiguration tool. The SPI memory device operates at 3.0V; the Spartan-6 FPGA I/Os are3.3V tolerant and provide electrically compatible logic levels to directly access the SPI flashthrough a 2.5V bank. The XC6SLX45T-3FGG484 is a master device when accessing anexternal SPI flash memory device.The SP605 SPI interface has two parallel connected configuration options (Figure1-3): anSPI X4 (Winbond W25Q64VSFIG) 64-Mb flash memory device (U32) and a flashprogramming header (J17). J17 supports a user-defined SPI mezzanine board. The SPIconfiguration source is selected via SPI select jumper J46. For details on configuring theFPGA, see Configuration Options.Figure 1-3:J17 SPI Flash Programming HeaderFigure 1-4:SPI Flash Interface Topology SP605 Hardware User GuideReferencesSee the Winbond Serial Flash Memory Data Sheet for more information. [Ref 13] See the XPS Serial Peripheral Interface Data Sheet for more information. [Ref 4]Table 1-6:SPI x4 Memory ConnectionsU1 FPGA Pin Schematic Net Name SPI MEM U32SPI HDR J17Pin #Pin NamePin #Pin NameAB2FPGA_PROG_B – –1–T14FPGA_D2_MISO31IO3_HOLD_B 2 –R13FPGA_D1_MISO2_R9IO2_WP_B3 – AA3SPI_CS_B– –4TMS AB20FPGA_MOSI_CSI_B_MISO015DIN 5TDI AA20FPGA_D0_DIN_MISO_MISO18IO1_DOUT6TDO Y20FPGA_CCLK16CLK7TCK– – – –8GND – – – –9VCC3V3J46.2(1)SPIX4_CS_B7CS_B––Notes:1.Not a U1 FPGA pin4. Linear BPI FlashA Numonyx JS28F256P30 Linear Flash memory (U25) on the SP605 (Figure1-5) provides32MB of non-volatile storage that can be used for configuration as well as softwarestorage. The Linear Flash is operated in asynchronous mode.For details on configuring the FPGA, see Configuration Options.Figure 1-5:Linear BPI Flash InterfaceTable 1-7:Linear Flash ConnectionsU1 FPGA Pin Schematic Net Name U25 BPI FLASHPin Number Pin NameN22FLASH_A029A1N20FLASH_A1 25A2M22FLASH_A2 24A3M21FLASH_A3 23A4L19FLASH_A4 22A5K20FLASH_A5 21A6H22FLASH_A6 20A7H21FLASH_A7 19A8L17FLASH_A8 8A9K17FLASH_A9 7A10G22FLASH_A106A11G20FLASH_A115A12K18FLASH_A124A13K19FLASH_A133A14H20FLASH_A142A15J19FLASH_A151A16 SP605 Hardware User GuideE22FLASH_A1655A17E20FLASH_A1718A18F22FLASH_A1817A19F21FLASH_A1916A20H19FLASH_A2011A21H18FLASH_A2110A22F20FLASH_A229A23G19FLASH_A2326A24AA20FPGA_D0_DIN_MISO_MISO134DQ0R13FPGA_D1_MISO236DQ1T14FPGA_D2_MISO339DQ2AA6FLASH_D 3 41D Q3AB6FLASH_D 4 47D Q4Y5FLASH_D 5 49D Q5AB5FLASH_D 6 51D Q6W9FLASH_D 7 53D Q7T7FLASH_D 8 35D Q8U6 FLASH_D 9 37D Q9AB19FLASH_D1040DQ10AA18FLASH_D1142DQ11AB18FLASH_D1248DQ12Y13FLASH_D1350DQ13AA12FLASH_D1452DQ14AB12FLASH_D1554DQ15V13FMC_PWR_GOO D _FLASH_RST_B 44RST_B R20FLASH_WE_B 14WE_B P22FLASH_OE_B 32OE_B P21FLASH_CE_B 30CE_B T19FLASH_ADV_B 46ADV_B T18FLASH_WAIT56WAITTable 1-7:Linear Flash Connections (Cont’d)U1 FPGA PinSchematic Net NameU25 BPI FLASH Pin NumberPin NameFPGA Design Considerations for the Configuration FlashThe SP605 has the P30 BPI flash connected to the FPGA dual use configuration pins and isnot shared. It can be used to configure the FPGA, and then controlled post-configurationvia the FPGA fabric. After FPGA configuration, the FPGA design can disable theconfiguration flash or access the configuration flash to read/write code or data.When the FPGA design does not use the configuration flash, the FPGA design must drivethe FLASH_OE_B pin High in order to disable the configuration flash and put the flashinto a quiescent, low-power state. Otherwise, the flash memory can continue to drive itsarray data onto the data bus causing unnecessary switching noise and powerconsumption.For FPGA designs that access the flash for reading/writing stored code or data, connectthe FPGA design or EDK embedded memory controller (EMC) peripheral to the flashthrough the pins defined in Figure1-5, page14.ReferencesSee the Numonyx StrataFlash Embedded Memory Data Sheet for more information. [Ref14]In addition, see the Spartan-6 FPGA Configuration User Guide for more information. [Ref2]5. System ACE CF and CompactFlash ConnectorThe Xilinx System ACE CompactFlash (CF) configuration controller allows a Type I orType II CompactFlash card to program the FPGA through the JTAG port. Both hardwareand software data can be downloaded through the JTAG port. The System ACE CFcontroller supports up to eight configuration images on a single CompactFlash card. Theconfiguration address switches allow the user to choose which of the eight configurationimages to use.The CompactFlash (CF) card shipped with the board is correctly formatted to enable theSystem ACE CF controller to access the data stored in the card. The System ACE CFcontroller requires a FAT16 file system, with only one reserved sector permitted, and asector-per-cluster size of more than one (UnitSize greater than 512). The FAT16 file systemsupports partitions of up to 2GB. If multiple partitions are used, the System ACE CFdirectory structure must reside in the first partition on the CompactFlash, with thexilinx.sys file located in the root directory. The xilinx.sys file is used by the SystemACE CF controller to define the project directory structure, which consists of one mainfolder containing eight sub-folders used to store the eight ACE files containing theconfiguration images. Only one ACE file should exist within each sub-folder. All foldernames must be compliant to the DOS 8.3 short file name format. This means that the foldernames can be up to eight characters long, and cannot contain the following reservedcharacters: < > " / \ |. This DOS 8.3 file name restriction does not apply to the actual ACEfile names.Other folders and files may also coexist with the System ACE CF project within the FAT16partition. However, the root directory must not contain more than a total of 16 folderand/or file entries, including deleted entries. When ejecting or unplugging theCompactFlash device, it is important to safely stop any read or write access to theCompactFlash device to avoid data corruption. SP605 Hardware User Guide。