一种四采样低噪声CMOS光电探测器读出电路

2[1].4+GHz低相位误差低相位噪声CMOS+QVCO设计

![2[1].4+GHz低相位误差低相位噪声CMOS+QVCO设计](https://img.taocdn.com/s3/m/098aec6427d3240c8547ef05.png)

咿魅怂测磐发2.4GHz低相位误差低相位噪声CMOSQVCO设计高慧,吕志强,来逢昌(哈尔滨工业大学微电子中心,哈尔滨150001)摘要:提出了一种新型的适用于锁相环频率夸成器的正交压控振荡器(Qvc0)结构,分析了OvcO的工作原理及其相位噪声性能。

ADs仿真结果表明,电路工作在2.4GHz、偏离中心频率600kHz的情况下相位噪声为一115.4dBc/Hz,在1.8v电源下功耗仪为2.9mw,输出信号的相位误差小于O.19。

结果还表明相对于目前流行的Ovc0结构,提出的结构实现了低相位误差、低功耗、高,0M值。

关键词:正交压控振荡器;相位噪声;相位误差;品质因数中图分类号:TN752文献标识码:A文章编号:1003.353x(2007)11-0988—04Designof2.4GHzLow-Phase-ErrorLow-Phase-NoiseCMoSQVC0GA0Hui,LOZhi-qiang,LAIFeng—ch锄g(肼b捌跏豳c咖,肼缸k血妇矿7‰缸影,黝缸150001,cMM)Absn譬ct.AnovelLcqIladr砒I珊voltage-conⅡ柚led08cilhtor(QVcO)w鹅deBi印edforPh船e—locked100p雠queⅡcysymhesi北r.Th8叩emtionpdnciple且ndpha8enoiseoftheQVcOwere粕嘶zed,ADsBi圳1“onreBults8howt}laltheci工cu“achievestheph踟noi∞0f一115.4dBc/}Izat600k№offset,a11dpowerdissip砒iononly2.9mwfhthewholeQVc0attllevolt89eB“pply0f1.8V.nepha跎emrbefweenIandQsigI“siB且tm08tO.19。

.The唧adBonofADsreBultsaIldreceⅡtPublisheddesi印s8ho啪thattheadvaIltag骼0ftheQVc0stnlctIlrearetllecharacⅫstics0fmt}Ier10wpha舱ermr,10wpowercoIlsump60n蛐dhighngLIre-of.medt.Key啪r凼:Qvco;pha8enoi∞;ph踟ermr;69Ilre—of-merit(FoM)1引言近年来,随着无线通信的广泛需求和迅速发展,直接变频收发器由于其低功耗、低造价、高集成度已成为Ic设计中大量研究的课题。

ccd探测器原理

ccd探测器原理

CCD(Charge-Coupled Device)探测器原理是一种用于光电信

号转换的电子器件。

它由许多光敏感的电荷耦合元件(pixel)组成,每个元件包含一个反型沟道结和一个储存结构。

以下将详细描述CCD探测器的工作原理。

当光照射在CCD探测器上时,光子会激发出电子。

这些电子

会在反型沟道结中形成电荷包。

当控制电压施加在沟道结上时,电荷包将开始移动,通过耦合电容传输到储存结构中。

在传输过程中,控制信号会按顺序把电荷包从一个元件传输到相邻的元件。

这种传输的原理可以实现像素之间的电荷耦合。

这样,整个图像的电荷包就可以顺序传输到最后的读出电路中。

在读出电路中,电荷包会被转换成电压信号。

这个过程涉及到将电荷包转移成电流,然后使用放大器将电流转换为电压。

最终,读出电路会根据电压信号来生成数字图像。

CCD探测器的工作原理基于电荷耦合的方式,其优点是输入

信号与输出信号之间的联系非常直接。

通过这种工作原理,CCD探测器可以实现高灵敏度和低噪声的图像检测。

总结起来,CCD探测器原理是通过将光信号转换为电荷包并

利用电荷耦合的方式传输和读出,进而实现对图像的检测。

这种工作原理使得CCD探测器在光电信号转换方面具有优秀的

性能。

光电传感器读出电路的参数可调控制研究

—— +一 {。 — ・

Reset

]

工

0 口 t

上 耋

.

. / .

者采用 了不 同的读 出结构 【 J l。 ' 2

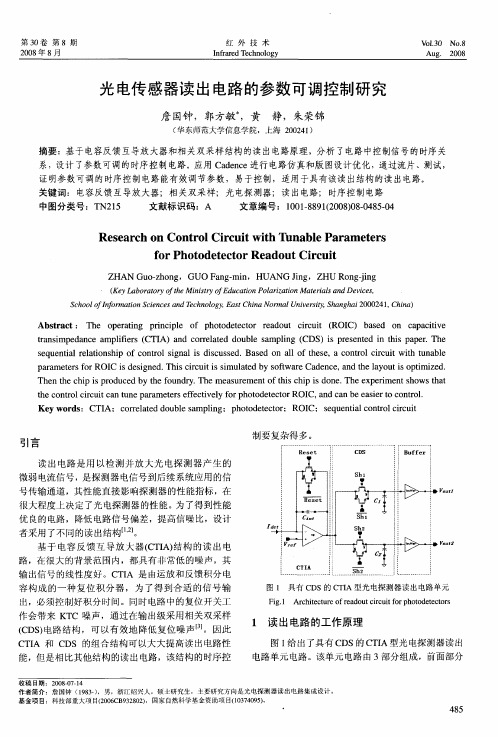

基 于 电容 反馈 互 导放 大 器 ( T A) C I 结构 的读 出 电 路 ,在很大 的 背景 范 围内 ,都具 有非 常低 的噪声 ,其 输 出信 号 的线性度 好 。C I 是 由运 放 和反馈 积 分 电 TA 容 构 成 的 一 种 复位 积 分 器 ,为 了得 到合 适 的信 号输

f rPh t d t c o a o tCic i o o o e e t rRe d u r u t

Z N G oz o g HA u —h n ,GUO F n — n a gmi,HU ANG J g HU R n n n ,Z o gj g i i

( e a oaoyo te ns E u ain oai t n t ila d vcs K y b rtr h ir o d ct lr ai e as n ie, L f Mi t f y oP z o Ma r De S h o I omainSi cs n eh ooy E sC i om l nvri, h n h i 0 0 4 , hn ) co lf n r t ce e dTcn lg, at hn N r a i syS a g a 0 2 1 C ia o f o n a a U e t 2

第3 O卷 第 8 期 20 年 8 08 月

红 外 技 术

I f ae e h o o y nrrdT c n lg

四象限光电探测器电路设计方案

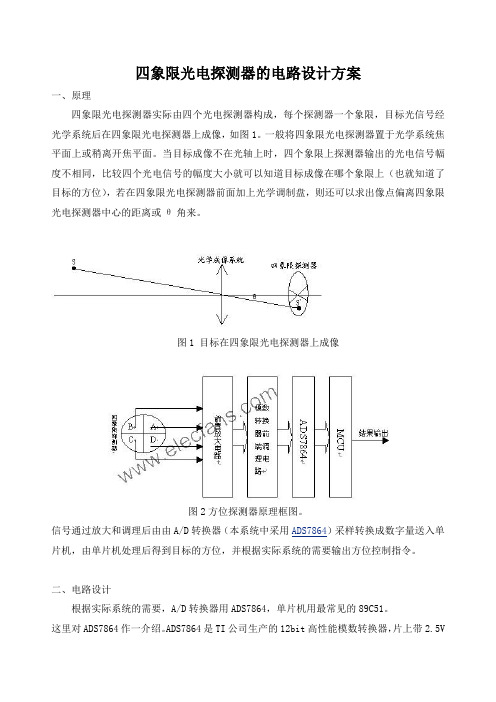

四象限光电探测器的电路设计方案一、原理四象限光电探测器实际由四个光电探测器构成,每个探测器一个象限,目标光信号经光学系统后在四象限光电探测器上成像,如图1。

一般将四象限光电探测器置于光学系统焦平面上或稍离开焦平面。

当目标成像不在光轴上时,四个象限上探测器输出的光电信号幅度不相同,比较四个光电信号的幅度大小就可以知道目标成像在哪个象限上(也就知道了目标的方位),若在四象限光电探测器前面加上光学调制盘,则还可以求出像点偏离四象限光电探测器中心的距离或θ角来。

图1 目标在四象限光电探测器上成像图2方位探测器原理框图。

信号通过放大和调理后由由A/D转换器(本系统中采用ADS7864)采样转换成数字量送入单片机,由单片机处理后得到目标的方位,并根据实际系统的需要输出方位控制指令。

二、电路设计根据实际系统的需要,A/D转换器用ADS7864,单片机用最常见的89C51。

这里对ADS7864作一介绍。

ADS7864是TI公司生产的12bit高性能模数转换器,片上带2.5V基准电压源,可用作ADS7864的参考电压。

每片ADS7864实际由2个转换速率为500ksps 的ADC构成,每个ADC有3个模拟输入通道,每个通道都有采样保持器,2个ADC组成3对模拟输入端,可同时对其中的1~3对输入信号同时采样保持,然后逐个转换。

由于6个通道可以同时采样,很适合用来转换四象限光电探测器的4路光电信号,剩下2个通道作系统扩展用。

*下面主要介绍电路中的信号采样转换和处理部分。

ADS7864前端调理电路模数转换器的前端调理电路缩放和平移要采样的信号,通过调理后的信号适合A/D转换器的模拟输入要求。

图3是ADS7864一个输入通道的前端调理电路,图3 ADS7864前端调理电路ADS7864模拟输入通道的+IN和-IN的最大电压输入范围为-0.3V~+5.3V(ADS7864 +5V 供电)。

图3的电路中使用了2个运放,A1用作跟随器,用来缓冲ADS7864输出的2.5V基准电压源;A2和四个电阻构成了信号调理网络,适当配置R1~R4电阻可以实现对输入信号Vi的缩放和平移以适合ADS7864模拟通道的输入要求。

cmos传感器工作原理

cmos传感器工作原理CMOS传感器是一种常见的数字图像传感器,广泛应用于数码相机、手机摄像头、安防监控等领域。

它具有低功耗、高集成度、低噪声等优点,成为了替代CCD传感器的主流技术。

本文将详细介绍CMOS 传感器的工作原理。

一、CMOS传感器的基本结构CMOS传感器由像素阵列和读出电路两部分组成。

像素阵列由大量光敏元件(也称为光电二极管或光电晶体管)组成,每个光敏元件对应一个像素点,用于接收光信号并转换为电信号。

读出电路负责将每个像素点产生的电信号放大并转换为数字信号输出。

二、CMOS传感器的工作原理1. 光敏元件的工作原理光敏元件是CMOS传感器中最基本的单元,它由一个PN结构组成。

当光线照射到PN结时,会产生载流子(即正负离子对),其中正离子向P区移动,负离子向N区移动,在PN结上形成电荷分布。

这些电荷会被收集到P型或N型衬底上,并形成电压信号。

这个过程称为光电转换。

2. 像素点的输出原理每个像素点都有一个对应的读出电路,用于将光敏元件产生的电信号放大并转换为数字信号输出。

读出电路通常由放大器、采样器和模数转换器等组成。

其中,放大器负责将微弱的电信号放大到一定程度,采样器负责对放大后的信号进行采样,模数转换器将采样后的模拟信号转换为数字信号输出。

3. CMOS传感器的工作流程当光线照射到CMOS传感器上时,每个像素点都会产生一个电荷,并通过读出电路被转化为数字信号输出。

具体流程如下:(1)曝光阶段:当快门打开时,光线进入镜头并照射到CMOS传感器上。

此时,每个像素点会产生一定数量的电荷。

(2)清除阶段:曝光结束后,需要将所有像素点中残留的电荷清零。

这个过程称为清除。

(3)读出阶段:在清除完成后,开始进行读出操作。

每个像素点中产生的电荷会被读出并通过放大、采样和模数转换等步骤转化为数字信号输出。

三、CMOS传感器的优缺点1. 优点(1)低功耗:CMOS传感器采用的是基于MOSFET的读出电路,功耗比CCD传感器低得多。

一种适用于微传感器读出电路的低噪声、低失调斩波放大器

10 8 ) 0 0 0

104) 0 0 9

( 1中 国科 学 院 电子 学 研 究 所 传 感技 术 国 家 重 点 实 验 室 ,北 京

( 中 国科 学 院研 究 生 院 ,北 京 2

摘 要 :提 出一 种 适 合 微 传 感 器 读 出 电路 的 高 精 度 折 叠 共 源 共 栅 放 大 器 . 于 斩 波 技 术 和 动 态 元 件 匹 配 技 术 , 低 基 降 了折 叠 共 源 共 栅 放 大器 的 噪 声 和 失 调 , 用 低 阻 节 点 斩 波 的方 法 和 低 压 共 源 共 栅 电流 镜 扩 大 了放 大 器 可 处 理 的 输 采 入 信 号 带 宽 和 输 出 电压 摆 幅 . 片 在 0 3 2 4 C O 芯 . 5 m P M M S工 艺 下 设 计 并 流 片 , 试 表 明 在 3 3 的 典 型 电源 电 压 测 .V 和 10 Hz的斩 波 频 率 下 , 波 放 大 器 具 有 小 于 9 . 的输 入 等 效 失 调 电 压 典 型 值 ,9 6 V/ 0k 斩 37 V 1.n 声, 开环 增 益 达 8 . d 单 位 增 益 带 宽 为 1 MHz 3 9 B, 0 . 关 键 词 :斩 波 放 大 器 ;低 噪 声 ;低 失 调 ;微 传 感 器

战 ~ 引.

为 了达 到上 一 代 C MOS工 艺 下 相 同 的动 态 范 围, 电路 需要尽 可 能保 持最 大 的输 出摆幅 , 以及 采用 各种 技术 降低 失调 电压 和 1 f噪声 . / 目前 降低 失 调 和 1 f噪声 的 主 要 方 法 有 : 调 技 术 (r / 微 ti n ) mmig 、 自动置 零技 术 和斩 波 技 术 . 调技 术 广 泛 用 于 双 极 微 工艺中, 是在 芯 片制作 完 成后 , 通过 激光 等方 法利用 电路 中的冗 余 器 件 , 整 器 件 的 匹 配 , 低 失 调 电 调 降 压_ , 4 由于其无 法 降低 CMOS器 件 的 1 f噪声 和温 J / 度漂 移 , 而且设 备 昂贵 , 因此 这 种方 法 在 低 成 本 、 小

光电探测器读出噪声分析方法

光电探测器读出噪声分析方法

文/韩振伟 宋克非 刘阳 陈波

摘

空间科学领域广泛应用多种

类型光电探测器对探测目标的各 要 个谱段进行精密测量。本文主要

研究了光电二极管的等效电路模

型 和 读 出 电 路 设 计 方 案, 给 出 了

读 出 噪 声 分 析 方 法, 并 且 计 算 了

经过 BS2 后,系统状态为: 探测器测量控制电子,发生测量塌缩:

由此可见,信号量子比特的信息不会发 生改变,从端口 D1、D2 输出的概率分别是:

当 D1 输出;

时,p1 为 1, 光 子 确 定 从

当

时,p2 为 1,光子确定从

D2 输出。这个完全由控制量子比特决定。

5 总结

本文提出的量子路由使用量子点,使信 号光子与量子点相互作用,通过控制量子点中 的控制量子决定光子的输出路径,完成双端量

随后光路 2 中,光子通过 1/4 波片(线偏 振和圆偏振的转换 |L〉(|R〉)↔|H〉(|V〉)后 进入控制相位门,与量子点进行相互作用, 若无耦合作用,则光子传输经过微腔(路径 r1),否则,光子会和电子耦合,被微腔反射(路 径 r2):

随后经过 PS1、PS2 和两个反射镜,系统 的量子态演变为:

图 1:信号处理采集电路框图

图 2:光电二极管放大电路噪声模型

于导电产生的散粒噪声成为附加的噪声源。在 光电二极管应用过程中,需要根据两种模式的 特性,对设计方法进行优化,得到较好的性能。

光电二极管在零偏压状态下实现光电转 换过程简单高效,当特定波长的入射光照射在 光电二极管表面,光子能量被半导体所吸收后, 价带中的电子被激发到导带中,而在价带中留 下空穴,产生电子和空穴对。电子和空穴受到 耗尽层中的电场的加速分别向 N 区和 P 区运 动,当读出电路连接至 PN 结两端,电子和空 穴会定向移动形成电流。当光照为零时,光电 二极管由于热运动产生的电流为暗电流,也称 为暗噪声。在精密光电测量领域,微弱入射光 产生的光电流也非常微弱,此时光电二极管自 身的暗噪声就不可忽略。

新型X线探测器材料及性能评估

新型 X 线探测器材料及性能评估第一部分X 线探测器材料概述 (2)第二部分新型材料研究背景与意义 (3)第三部分常见X 线探测器类型介绍 (6)第四部分新型X 线探测器材料分类 (8)第五部分无机半导体探测器材料特性 (10)第六部分有机半导体探测器材料特性 (13)第七部分薄膜晶体管(TFT)技术应用 (15)第八部分探测器性能评估方法与指标 (17)第九部分实际应用中的挑战与解决方案 (20)第十部分未来发展趋势与前景展望 (21)第一部分X 线探测器材料概述X 线探测器材料是实现X 射线成像的关键组成部分。

随着科学技术的不断发展,各种新型X 线探测器材料的研发和应用逐渐成为研究热点。

X 线探测器的工作原理主要基于光电效应、康普顿散射和电子-空穴对的产生与分离。

根据不同的物理过程和信号转换方式,X 线探测器可分为直接转换型和间接转换型两大类。

其中,直接转换型探测器将X 射线能量直接转化为电荷或电信号;而间接转换型探测器则需要通过闪烁体等中介物质将X 射线能量转化为可见光或其他形式的能量,然后再通过光电二极管等器件将这种能量转化为电信号。

常见的直接转换型X 线探测器材料包括硅(Si)、硒化镉(CdSe)、碲化镉(CdTe)和硒化锌镉(ZnCdSe)等半导体材料。

这些材料具有较高的检测效率和良好的线性响应特性,能够实现高分辨率和快速响应的X 射线成像。

然而,由于其成本较高、工艺复杂等原因,它们的应用范围相对较窄。

相比之下,间接转换型X 线探测器材料具有更广泛的应用前景。

常用的间接转换型X 线探测器材料主要包括碘化铯(CsI)、碘化铅(PbI2)和硫氧化钆(GdOS)等闪烁体材料。

这些闪烁体材料具有较低的成本、较宽的吸收范围和较好的发光特性,能够在低剂量条件下获得高质量的X 射线图像。

此外,近年来还出现了一些新型X 线探测器材料,如钙钛矿材料、二维材料等。

例如,钙钛矿材料因其独特的光电性能和易于制备的特点,被广泛关注。

一种光电探测器读出电路的设计方法[发明专利]

![一种光电探测器读出电路的设计方法[发明专利]](https://img.taocdn.com/s3/m/af2241cfa5e9856a57126000.png)

专利名称:一种光电探测器读出电路的设计方法

专利类型:发明专利

发明人:郭方敏,李峻蔚,詹国钟,韩建强,徐斌,叶宇诚,胡大鹏,朱自强,褚君浩

申请号:CN200910047116.X

申请日:20090306

公开号:CN101504313A

公开日:

20090812

专利内容由知识产权出版社提供

摘要:本发明公开了一种光电探测器读出电路的设计方法,特点是将光电探测器的电特性曲线拟合,使输出电流为电压的函数、电容为电压的函数,在等效电路模型中可以实现一个或多个电压控制电流源及电容、输出阻抗来实现,由此建立等效电路模型,并用电路模拟软件对其进行修正与完善,最后将等效电路模型作为CTIA型读出结构的输入源,得到读出电路的相应参数并作出光电探测器读出电路的匹配设计。

本发明与现有技术相比具有电路建模程序简单、结构明了、精度高的优点,大大方便了光电探测器设计相匹配的读出电路,而且具有读出电路信号偏差小,动态范围大的优良性能。

申请人:华东师范大学

地址:200062 上海市普陀区中山北路3663号

国籍:CN

代理机构:上海蓝迪专利事务所

代理人:徐筱梅

更多信息请下载全文后查看。

光电探测器低噪声增益调节方法研究

光电探测器低噪声增益调节方法研究

另外,量子噪声可以通过增加光电探测器的增益来降低。

光电探测器

的增益是指输入光信号转换为输出电信号的倍数。

在增加增益的同时,光

电探测器的噪声也会相应增加,因此需要在增益调节中进行权衡。

在增益调节中,一个常用的方法是调节探测器的偏置电压。

偏置电压

是指在光电探测器的两个接口之间加上的电压。

通过调节偏置电压,可以

改变光电探测器的工作状态,进而改变其增益水平。

通常,适当的偏置电

压可以使光电探测器在较低噪声水平下获得较高的增益。

此外,还可以通过改变读出电路的放大倍数来调节光电探测器的增益。

读出电路是光电探测器的一个重要组成部分,负责将光信号转化为电信号

并进行放大。

通过调节读出电路的放大倍数,可以改变光电探测器输出信

号的振幅,从而实现增益调节。

总之,光电探测器的低噪声增益调节方法是一个涉及到多方面因素的

复杂问题。

通过降低热噪声和调节增益,可以有效降低光电探测器的噪声

水平,提高其灵敏度和性能。

但需要注意的是,在增益调节中要避免过高

的增益,以免引入过多的噪声。

因此,在实际应用中,需要对光电探测器

的工作状态进行综合考虑,并根据具体需求进行调整。

《基于半绝缘SiC基底的垂直结构光电探测器阵列及其读出电路》范文

《基于半绝缘SiC基底的垂直结构光电探测器阵列及其读出电路》篇一一、引言随着科技的飞速发展,光电探测器在众多领域中扮演着越来越重要的角色。

其中,基于半绝缘SiC基底的垂直结构光电探测器阵列以其独特的高频、高灵敏度、低噪声等特点,正逐渐成为研究热点。

本文将详细介绍基于半绝缘SiC基底的垂直结构光电探测器阵列的设计原理、性能特点及其实验结果,并对其读出电路进行详细阐述。

二、半绝缘SiC基底垂直结构光电探测器阵列的设计与原理1. 基底材料选择半绝缘SiC因其具有高击穿电压、高电子饱和速度等优点,成为制造垂直结构光电探测器阵列的理想材料。

其独特的能带结构和电子特性使得在光电器件中具有较高的性能表现。

2. 垂直结构设计垂直结构光电探测器阵列的核心理念是利用垂直于基底表面的导电通道,将光信号转化为电信号。

其优点在于可以提高器件的光照面积和灵敏度,降低噪声干扰。

3. 工作原理基于半绝缘SiC基底的垂直结构光电探测器阵列利用光电效应和电流传导机制实现光信号的转换和检测。

当光照到探测器上时,产生的光生电流经过内部导电通道传递到读出电路,从而实现光信号的读取。

三、性能特点基于半绝缘SiC基底的垂直结构光电探测器阵列具有以下特点:1. 高灵敏度:由于采用垂直结构,提高了光照面积,增强了光生电流的生成效率。

2. 低噪声:半绝缘SiC材料具有较低的噪声特性,提高了信噪比。

3. 高频响应:适用于高速光通信和成像系统。

4. 良好的热稳定性:半绝缘SiC材料具有较高的热导率,使得器件在高温环境下仍能保持良好的性能。

四、读出电路设计为了实现光电探测器阵列的信号读取,需要设计相应的读出电路。

读出电路主要包括前置放大器、模数转换器(ADC)以及数据处理单元等部分。

其中,前置放大器用于放大光电探测器产生的微弱信号;ADC将放大的信号转换为数字信号以便于后续处理;数据处理单元则对数字信号进行进一步的处理和分析。

五、实验结果与分析通过实验验证了基于半绝缘SiC基底的垂直结构光电探测器阵列的优异性能。

光电探测器的噪声

温度噪声与热噪声在产生原因、表示形式上有一定的差 别,主要区别在于: 对于热噪声,材料的温度T一定,引起粒子随机性波动, 从而产生了随机性电流 ; i n 对于温度噪声,材料温度有变化ΔT,从而导致热流量的 变化Δφ,这种热流量的变化导致产生物体的温度噪声。

• 热噪声属于白噪声频谱

4. 1/f 噪声 1)产生原因

1/f 噪声又称为闪烁或低频噪声。 这种噪声是由于光敏层的微粒不均匀或不必要的微量杂质 的存在,当电流流过时在微粒间发生微火花放电而引起的微 电爆脉冲。 几乎在所有探测器中都存在这种噪声。它主要出现在大约 1KHz以下的低频频域,而且与光辐射的调制频率f成反比,故 称为低频噪声或1/f 噪声。 实验发现,探测器表面的工艺状态(缺陷或不均匀等)对这 种噪声的影响很大,所以有时也称为表面噪声或过剩噪声。 一般说,只要限制低频端的调制频率不低于1千赫兹,这 种噪声就可以防止。

2)度量 • 除了考虑载流子由于吸收光受到激发产生的载流子数的随机起 伏外,还要考虑到载流子在运动过程中复合的随机性。经理论 推导g—r噪声的表达式为:

2 ing r 4e I Mf

式中,e为电子电荷,I 为平均电流, 为探测器的工作带宽, M 0 为光电导探测器的内增益,它是载流子平均寿命τ 0和渡 d 越时间τ d的比值。

1.散粒噪声: 1)产生原因 探测器的散粒噪声是由于探测器在光辐射作用或热激 发下,光电子或光生载流子的随机产生所造成的。由 于随机起伏是一个一个的带电粒子或电子引起的,所 以称为散粒噪声。

•这种噪声存在于所有光电探测器中。

•电子管中任一短时间 τ 内发射出来的电子决不会总 是等于平均数,而是围绕这一平均数有一涨落。

短波IRFPAs读出电路CTIA输入级的优化设计

短波IRFPAs读出电路CTIA输入级的优化设计王攀;丁瑞军;叶振华【摘要】针对凝视短波红外焦平面阵列探测器弱信号耦合读出的难题,设计了一种高注入效率、低噪声、精简结构的运放积分型(CTIA)输入级.该CTIA单元输入级采用电流源负载的共源共栅结构,不仅具有传统CTIA结构的优点,还能克服常规的CTIA结构复杂、功耗过高的缺点.在低温模型的仿真环境下,进行了前仿真和提取版图寄生参数的后仿真.基于CSMC-6S05DPTM 0.5μm工艺流片,CTIA读出电路芯片的测试结果与仿真结果基本一致,输出信号电压范围达到2.5V,单元功耗小于1.0 μW.【期刊名称】《激光与红外》【年(卷),期】2013(043)012【总页数】5页(P1363-1367)【关键词】短波红外焦平面;运放积分(CTIA)读出电路;弱信号耦合读出【作者】王攀;丁瑞军;叶振华【作者单位】中国科学院上海技术物理研究所红外成像材料与器件重点实验室,上海200083;中国科学院研究生院,北京100039;中国科学院上海技术物理研究所红外成像材料与器件重点实验室,上海200083;中国科学院上海技术物理研究所红外成像材料与器件重点实验室,上海200083【正文语种】中文【中图分类】TN4321 引言短波红外焦平面阵列正向着大面阵、高分辨率等方向发展[1-2]。

读出电路是红外焦平面阵列的重要部分,短波红外焦平面的发展要求读出电路具有更小的像元面积、更高的注入效率和更高的信号输出帧频,同时保持一定的面阵总功耗。

合理的输入级设计是短波红外焦平面读出电路设计的关键,必须综合读出电路对输入级单元在尺寸、功耗、注入效率等方面的参数要求。

凝视探测器的单元面积限制了读出电路单元结构的复杂度,导致常规的输入级结构难以满足弱信号耦合读出的特殊要求。

因此,本文提出并设计了一种新型的电流源负载的共源共栅结构三管运放CTIA输入级结构。

新型CTIA输入级不仅具有传统CTIA结构的高注入效率、低噪声、高线性度和稳定偏压等特点,还能有效克服了一般的CTIA结构面积过大、功耗过高的缺点,进而实现短波红外焦平面弱信号的高帧频、高注入效率、高分辨率和低功耗的读出。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Keywords

Four Sampling, Rate Optimization, Low Noise, CMOS Readout Circuit

一种四采样低噪声CMOS光电探测器读出电路

袁红辉1*,陈永平1,黄志伟2,陈 瑶1,王 欣1,陈世军1

1中国科学院上海技术物理研究所,中国科学院红外成像材料与器件重点实验室,上海 2中国科学院微小卫星创新研究院微小卫星重点实验室,上海

Honghui Yuan1*, Yongping Chen1, Zhiwei Huang2, Yao Chen1, Xin Wang1, Shijun Chen1

1Key Laboratory of Infrared Imaging Materials and Detectors, Shanghai Institute of Technical Physics, Chinese Academy of Sciences, Shanghai 2Key Laboratory of Micro-Satellite, Innovation Research Institute of Micro-Satellite, Chinese Academy of Sciences, Shanghai

Received: May 14th, 2019; accepted: May 27th, 2019; published: Jun. 3rd, 2019

Abstract

In order to meet the requirements of high sampling rate of imaging detection, a four sampling long-line CMOS detector with 6 MHz sampling frequency is designed in this paper. By reducing the width to length ratio of the first stage P-type following transistor to decrease the bus parasitic capacitance and reducing the bias voltage of the P-type following load transistor to increase the driving current, thus the sampling frequency of the read-out circuit is increased from the original 2 MHz to the 6 MHz, which effectively improves the readout frequency of the long-line visible light CMOS detector. In order to achieve truely correlated double sampling and reduce the equivalent input noise of the device, the four sampling is used to connect CTIA integral amplifier. Through the test, the CMOS detector possesses an equivalent input noise electron less than 50e when the integral time is 200 us and the area of photosensitive is 20 um × 18 um, it can work steadily at the sampling rate of 6 MHz. The linearity, the output swing and the sensitivity of the detector can meet the requirements of the system. The development of the CMOS detector has laid an important theoretical foundation and practical value for the future ultra high speed and high definition imaging detection.

图 3 为双采样后一级跟随寄生电容为 3 pf 时的仿真结果,上升延迟为 151 nS,不满足采样速率 6 MHz 的频率要求。

为减小延迟,达到 6 MHz 的采用频率,采用减小源级跟随管来减小寄生电容来增加带宽和降低跟随

DOI: 10.12677/oe.2019.92013

85

光电子

袁红辉 等 负载管的偏置电压增大电流来增加带宽。但源级跟随管的设计不能太小,否则会导致跟随后的驱动能力 不够,减小源级跟随管后对电路进行了仿真。图 4 为优化后的仿真结果。当采样后一级跟随寄生电容为 3 pf,Vb 从 2 V 降低到 1.5 V,最后一级差分放大倍数由 2.5 倍增加到 4.5 倍时的仿真结果,上升延迟为 76.5 nS,满足采样速率 6 MHz 的频率要求。

Figure 1. CTIA pixel circuit structure 图 1. CTIA 像素电路结构图

当 Reset 为低电平,CTIA 处于积分状态,光电二极管光生电流 Iin 存储列积分电容 Cint 上,假定积分 时间为 t 时,CTIA 输出的积分信号由公式(1)表示。

V= CTIA _ sig

2. CMOS 探测器读出电路设计及原理

2.1. 四采样电路结构

四采样读出电路工作模式设计为:电路分为两组交替工作,分别用于前后两帧复位信号和积分信号

DOI: 10.12677/oe.2019.92013

84

光电子

袁红辉 等

的采样保持,再通过后续差分电路减除复位电平及复位噪声,从而实现真正的帧内相关采样。通道内所 有像素同时积分、同时复位,串行输出,积分与信号输出同时进行的工作模式,即在同一脉冲控制下, 所有像素同时复位后开始积分,积分完成以后,所有像素的信号同时采样到各自的保持电路上,在下一 帧积分的过程中,上一帧信号按顺序串行读出。图 1 为单列像素电路结构原理图。

Open Access

1. 引言

随着超大规模集成技术的发展,CMOS 图像传感器显示出强劲的发展趋势,早在 70 年代初,国外 就已经开发出 CMOS 图像传感器,但成像质量不如 CCD,但随着近年超大规模集成技术的飞速发展, CMOS 图像传感器可在单芯片内集成 A/D 转换、信号处理、自动增益控制、精密放大和存储等功能,大 大减小了系统复杂性,降低了成本,因而显示出强劲的发展势头,此外,它还具有低功耗、单电源、低 工作电压、成品率高,可对局部像元随机访问等突出优点。因此,CMOS 图像传感器重新成为研究、开 发的热点,发展极其迅猛,目前已占据低、中分辨领域。CMOS 图像传感器的一些参数性能指标已达到 或超过 CCD。在航天遥感领域,可见光成像探测是航天探测的重要组成部分,为了获取更高分辨率的可 见光图像数据,需要采用小像元长线列的可见光 CMOS 探测器[1]-[6]。

为满足高分辨率对地观测需求,本论文针对航天遥感领域,根据目前外协代工厂的加工能力,采用 了 0.35 微米工艺,设计了 PIN 探测器与读出电路集成的长线列 CMOS 探测器。为实现真正相关双采样 降低器件等效输入噪声,采用了 CTIA 积分放大器后接四采样跟随电路;通过减小四采样后的第一级 P 跟随管宽长比降低总线寄生电容,和减小 P 跟随负载管偏置电压增加驱动电流,缩小信号延迟,使读出 电路的采样频率由原来的 2 MHz 增加到 6 MHz,有效地提高了长线列可见光 CMOS 探测器的读出频率, 研制了 820 元四采样低噪声高采样速率 CMOS 探测器[7]-[13]。

(2)

为减小像素的单元面积,本设计中采用的像素放大电路结构为单端放大器,主放大器只有四个 MOS 管,包括两个 PMOS 管和两个 NMOS 管,为减小噪声,需尽量增加第一级放大器的跨导,采用较大宽长 比的输入 MOS 管,本输入管的宽长比设计为 20 um/1um。

2.2. 仿真分析

图 2 为像素 CTIA 积分和四采样工作时序图,当 Reset 为低电平,CTIA 处于积分状态,光电二极管 光生电流 Iin 存储在列积分电容 Cint 上;当 Reset 为高电平,CTIA 处于复位状态。复位信号由 R1 和 R2 交替输入信号控制,selA 和 selB 输入信号控制 R1 和 R2 复位信号输出,光信号采样由 S1 和 S2 输入信 号控制,四个 Cload 为相应的复位信号保持电容和光积分信号保持电容,两个列选通管由 selA 和 selB 输 入信号控制,实现了真正的相关双采样读出方式。各通道最终输出信号为复位信号 VoutR 和光信号 VoutS 之差,由每个通道设置的差分放大器进行差分放大后输出,有效地降低了 CMOS 探测器的总噪声。

Optoelectronics 光电子, 2019, 9(2), 83-91 Published Online June 2019 in Hans. /journal/oe https:///10.12677/oe.2019.92013

A Four-Sampling Lower Noise Readout Circuit for CMOS Detector

关键词

四采样,速率优化,低噪声,CMOS读出电路

Copyright © 2019 by author(s) and Hans Publishers Inc. This work is licensed under the Creative Commons Attribution International License (CC BY). /licenses/by/4.0/