03第三章VHDL语言基础习题答案

VHDL程序练习题含答案

VHDL程序填空题一在下面横线上填上合适的VHDL关键词;完成2选1多路选择器的设计.. LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;1 MUX21 ISPORTSEL:IN STD_LOGIC;A;B:IN STD_LOGIC;Q: OUT STD_LOGIC ;END MUX21;2 BHV OF MUX21 ISBEGINQ<=A WHEN SEL=’1’ ELSE B;END BHV;二在下面横线上填上合适的语句;完成BCD-7段LED显示译码器的设计.. LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL;ENTITY BCD_7SEG ISPORT BCD_LED : IN STD_LOGIC_VECTOR3 DOWNTO 0;LEDSEG : OUT STD_LOGIC_VECTOR6 DOWNTO 0;END BCD_7SEG;ARCHITECTURE BEHA VIOR OF BCD_7SEG ISBEGINPROCESSBCD_LED3IF BCD_LED="0000" THEN LEDSEG<="0111111";ELSIF BCD_LED="0001" THEN LEDSEG<="0000110";ELSIF BCD_LED="0010" THEN LEDSEG<= 4 ;ELSIF BCD_LED="0011" THEN LEDSEG<="1001111";ELSIF BCD_LED="0100" THEN LEDSEG<="1100110";ELSIF BCD_LED="0101" THEN LEDSEG<="1101101";ELSIF BCD_LED="0110" THEN LEDSEG<="1111101";ELSIF BCD_LED="0111" THEN LEDSEG<="0000111";ELSIF BCD_LED="1000" THEN LEDSEG<="1111111";ELSIF BCD_LED="1001" THEN LEDSEG<="1101111";ELSE LEDSEG<= 5 ;END IF;END PROCESS;END BEHA VIOR;三在下面横线上填上合适的语句;完成数据选择器的设计..LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MUX16 ISPORT D0; D1; D2; D3: IN STD_LOGIC_VECTOR15 DOWNTO 0;SEL: IN STD_LOGIC_VECTOR 6 DOWNTO 0;Y: OUT STD_LOGIC_VECTOR15 DOWNTO 0;END;ARCHITECTURE ONE OF MUX16 ISBEGINWITH 7 SELECTY <= D0 WHEN "00";D1 WHEN "01";D2 WHEN "10";D3 WHEN 8 ;END;四在下面横线上填上合适的语句;完成JK触发器的设计..LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY JKFF1 ISPORT PSET;CLR;CLK;J;K : IN STD_LOGIC;Q : OUT STD_LOGIC;END JKFF1;ARCHITECTURE MAXPLD OF JKFF1 ISSIGNAL TEMP:STD_LOGIC;BEGINPROCESSPSET;CLR;CLKBEGINIF PSET='0'AND CLR='1' THEN TEMP<='1';ELSIF PSET='1'AND CLR='0' THEN TEMP<='0';ELSIF PSET='0'AND CLR='0' THEN NULL;9 CLK'EVENT AND CLK='1' THEN10 J='0' AND K='0' THEN TEMP<=TEMP;ELSIF J='0' AND K='1' THEN TEMP<='0';ELSIF J='1' AND K='0' THEN TEMP<='1';ELSIF J='1' AND K='1' THEN TEMP<= 11 ;END IF;END IF;END PROCESS;Q<=TEMP;END ;五在下面横线上填上合适的语句;完成计数器的设计..说明:设电路的控制端均为高电平有效;时钟端CLK;电路的预置数据输入端为4位D;计数输出端也为4位Q;带同步始能EN、异步复位CLR和预置控制LD的六进制减法计数器.. LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT6 ISPORTEN;CLR;LD;CLK:IN STD_LOGIC;D: IN STD_LOGIC_VECTOR3 DOWNTO 0;Q:OUT STD_LOGIC_VECTOR3 DOWNTO 0;END CNT6;ARCHITECTURE BEHA OF CNT6 ISSIGNAL QTEMP:STD_LOGIC_VECTOR3 DOWNTO 0;BEGINPROCESSCLK;CLR;LDBEGINIF CLR='1' THEN QTEMP<="0000"; --CLR=1清零ELSIF CLK'EVENT AND CLK='1' THEN --判断是否上升沿IF LD='1' THEN QTEMP<= 12 ; --判断是否置位ELSIF EN='1' THEN --判断是否允许计数IF QTEMP="0000" THEN QTEMP<= 13 ; --等于0;计数值置5 ELSE QTEMP<= 14 ; --否则;计数值减1END IF;END IF;END IF;Q<=QTEMP;END PROCESS;END BEHA;六在下面横线上填上合适的语句;完成状态机的设计..说明:设计一个双进程状态机;状态0时如果输入”10”则转为下一状态;否则输出”1001”;状态1时如果输入”11”则转为下一状态;否则输出”0101”;状态2时如果输入”01”则转为下一状态;否则输出”1100”;状态3时如果输入”00”则转为状态0;否则输出”0010”..复位时为状态0..LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY MOORE1 ISPORT DATAIN: IN STD_LOGIC_VECTOR1 DOWNTO 0;CLK; RST:IN STD_LOGIC;Q: OUT STD_LOGIC_VECTOR3 DOWNTO 0;END;ARCHITECTURE ONE OF MOORE1 ISTYPE ST_TYPE IS ST0; ST1; ST2; ST3; --定义4个状态SIGNAL CST; NST: ST_TYPE; --定义两个信号现态和次态SIGNAL Q1:STD_LOGIC_VECTOR3 DOWNTO 0;BEGINREG: PROCESSCLK; RST --主控时序进程BEGINIF RST='1' THEN CST<= 15 ; --异步复位为状态0 ELSIF CLK'EVENT AND CLK='1' THENCST<= 16 ; --现态=次态END IF;END PROCESS;COM: PROCESSCST; DATAINBEGINCASE CST ISWHEN ST0 => IF DATAIN="10" THEN NST<=ST1;ELSE NST<=ST0; Q1<="1001"; END IF;WHEN ST1 => IF DATAIN="11" THEN NST<=ST2;ELSE NST<=ST1; Q1<="0101"; END IF;WHEN ST2 => IF DATAIN="01" THEN NST<=ST3;ELSE NST<=ST2; Q1<="1100"; END IF;WHEN ST3 => IF DATAIN="00" THEN NST<=ST0;ELSE NST<=ST3; Q1<="0010"; END IF;17 ;END PROCESS;Q<=Q1;END;七在下面横线上填上合适的语句;完成减法器的设计..由两个1位的半减器组成一个1位的全减器--1位半减器的描述LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY HALF_SUB ISPORTA;B : IN STD_LOGIC;DIFF;COUT : OUT STD_LOGIC;END HALF_SUB;ARCHITECTURE ART OF HALF_SUB ISBEGINCOUT<= 18 ; --借位DIFF<= 19 ; --差END ;--1位全减器描述LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY FALF_SUB ISPORTA;B;CIN: IN STD_LOGIC;DIFF;COUT : OUT STD_LOGIC;END FALF_SUB;ARCHITECTURE ART OF FALF_SUB ISCOMPONENT HALF_SUBPORTA;B : IN STD_LOGIC;DIFF;COUT : OUT STD_LOGIC;END COMPONENT;20 T0;T1;T2:STD_LOGIC;BEGINU1: HALF_SUB PORT MAPA;B; 21 ;T1;U2: HALF_SUB PORT MAPT0; 22 ; 23 ;T2; COUT<= 24 ;END ;八在下面横线上填上合适的语句;完成分频器的设计..说明:占空比为1:2的8分频器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CLKDIV8_1TO2 ISPORTCLK:IN STD_LOGIC;CLKOUT:OUT STD_LOGIC ;END CLKDIV8_1TO2;ARCHITECTURE TWO OF CLKDIV8_1TO2 ISSIGNAL CNT:STD_LOGIC_VECTOR1 DOWNTO 0;SIGNAL CK:STD_LOGIC;BEGINPROCESSCLKBEGINIF RISING_EDGE 25 THENIF CNT="11" THENCNT<="00";CK<= 26 ;ELSE CNT<= 27 ;END IF;END IF;CLKOUT<=CK;END PROCESS;END;九在下面横线上填上合适的语句;完成60进制减计数器的设计..LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY COUNT ISPORTCLK: IN STD_LOGIC;H;L: OUT STD_LOGIC_VECTOR3 DOWNTO 0;END COUNT;ARCHITECTURE BHV OF COUNT ISBEGINPROCESSCLKV ARIABLE HH;LL: STD_LOGIC_VECTOR3 DOWNTO 0; BEGINIF CLK'EVENT AND CLK='1' THENIF LL=0 AND HH=0 THENHH:="0101"; LL:="1001";ELSIF LL=0 THENLL:= 28 ;HH:= 29 ;ELSELL:= 30 ;END IF;END IF;H<=HH;L<=LL;END PROCESS;END BHV;十在下面横线上填上合适的语句;完成4-2优先编码器的设计..LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY CODE4 ISPORTA;B;C;D : IN STD_LOGIC;Y0;Y1 : OUT STD_LOGIC;END CODE4;ARCHITECTURE CODE4 OF CODE4 ISSIGNAL DDD:STD_LOGIC_VECTOR3 DOWNTO 0;SIGNAL Q:STD_LOGIC_VECTOR 31 DOWNTO 0;BEGINDDD<= 32 ;PROCESSDDDBEGINIF DDD0='0' THEN Q <= "11";ELSIF DDD1='0' THEN Q <= "10";ELSIFDDD2='0' THEN Q<="01";ELSE Q <= "00";END IF;33 ;Y1<=Q0; Y0<=Q1;END CODE4;十一在下面横线上填上合适的语句;完成10位二进制加法器电路的设计.. LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ 34 .ALL;ENTITY ADDER1 ISPORTA;B:IN STD_LOGIC_VECTOR9 DOWNTO 0;COUT:OUT STD_LOGIC;SUM:OUT STD_LOGIC_VECTOR9 DOWNTO 0;END;ARCHITECTURE JG OF ADDER1 ISSIGNAL ATEMP: STD_LOGIC_VECTOR10 DOWNTO 0;SIGNAL BTEMP: STD_LOGIC_VECTOR10 DOWNTO 0;SIGNAL SUMTEMP: STD_LOGIC_VECTOR 35 DOWNTO 0; BEGINATEMP<=’0’& A;BTEMP<=’0’& B;SUMTEMP<= 36 ;SUM<=SUMTEMP9 DOWNTO 0;COUT<= 37 ;END JG;十二在下面横线上填上合适的语句;完成移位寄存器的设计..说明:8位的移位寄存器;具有左移一位或右移一位、并行输入和同步复位的功能.. LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY SHIFTER ISPORTDATA :IN STD_LOGIC_VECTOR7 DOWNTO 0;CLK:IN STD_LOGIC;SHIFTLEFT;SHIFTRIGHT:IN STD_LOGIC;RESET:IN STD_LOGIC;MODE:IN STD_LOGIC_VECTOR1 DOWNTO 0;QOUT:BUFFER STD_LOGIC_VECTOR7 DOWNTO 0;END SHIFTER;ARCHITECTURE ART OF SHIFTER ISBEGINPROCESSBEGIN38 RISING_EDGECLK; --等待上升沿IF RESET='1' THEN QOUT<="00000000"; --同步复位ELSECASE MODE ISWHEN "01"=>QOUT<=SHIFTRIGHT& 39 ; --右移一位WHEN "10"=>QOUT<=QOUT6 DOWNTO 0& 40 ; --左移一位WHEN "11"=>QOUT<= 41 ; --不移;并行输入WHEN OTHERS=>NULL;42 ;END IF;END PROCESS;END ART;十三在下面横线上填上合适的语句;完成计数器的设计..说明:设计一个带有异步复位和时钟使能的一位八进制加法计数器带进位输出端.. LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT8 ISPORT CLK;RST;EN : IN STD_LOGIC;CQ : OUT STD_LOGIC_VECTOR 43 DOWNTO 0;COUT : OUT STD_LOGIC ;END CNT8;ARCHITECTURE BEHA V OF CNT8 ISBEGINPROCESSCLK; RST; EN44 CQI : STD_LOGIC_VECTOR2 DOWNTO 0;BEGINIF RST = '1' THEN CQI := “000”;45CLK'EVENT AND CLK='1' THENIF EN = '1' THENIF CQI < "111" THEN CQI := 46 ;ELSE CQI := 47 ;END IF;END IF;END IF;IF CQI = "111" THEN COUT <= '1';ELSE COUT <= '0';END IF;CQ <= CQI;END PROCESS;END BEHA V;十四在下面横线上填上合适的语句;完成序列信号发生器的设计..说明:已知发送信号为”10011010”;要求以由高到低的序列形式一位一位的发送;发送开始前及发送完为低电平..LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY XULIE ISPORT RES; CLK: IN STD_LOGIC;Y: OUT STD_LOGIC ;END;ARCHITECTURE ARCH OF XULIE ISSIGNAL REG:STD_LOGIC_VECTOR7 DOWNTO 0;BEGINPROCESSCLK; RESBEGINIFCLK’EVENT AND CLK=’1’ THENIF RES=’1’ THENY<=’0’;REG<= 48 ; --同步复位;并加载输入ELSE Y<= 49 ; --高位输出REG<= 50 ; --左移;低位补0END IF;END IF;END PROCESS;END;十五在下面横线上填上合适的语句;完成数据选择器的设计..说明:采用元件例化的设计方法;先设计一个2选1多路选择器;再使用3个2选1多路选择器构成一个4选1多路选择器..LIBRARY IEEE; --2选1多路选择器的描述USE IEEE.STD_LOGIC_1164.ALL;ENTITY MUX21 ISPORTA;B;SEL : IN STD_LOGIC;Y : OUT STD_LOGIC;END MUX21;ARCHITECTURE ART OF MUX21 ISBEGINY<=A WHEN SEL='0' ELSE B;END ;LIBRARY IEEE; --4选1多路选择器的描述USE IEEE.STD_LOGIC_1164.ALL;ENTITY MUX41 ISPORTA;B;C;D : IN STD_LOGIC;S1;S2 : IN STD_LOGIC;Y:OUT STD_LOGIC ;END;ARCHITECTURE ART OF MUX41 ISCOMPONENT MUX41PORTA;B;SEL : IN STD_LOGIC;Y : OUT STD_LOGIC;END COMPONENT;51 Y1;Y2:STD_LOGIC;BEGINU1: MUX21 PORT MAPA;B;S1; 52 ;U2: MUX21 PORT MAPC;D; 52 ;Y2;U2: MUX21 PORT MAPY1;Y2; 54 ;Y;END ;十六在下面横线上填上合适的语句;完成8位奇偶校验电路的设计..LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY PC ISPORT A : IN STD_LOGIC_VECTOR7 DOWNTO 0;Y : OUT STD_LOGIC ;END PC;ARCHITECTURE A OF PC ISBEGINPROCESSA.V ARIABLE TMP: STD_LOGIC;BEGINTMP 55 '0';FOR I IN 0 TO 7 LOOPTMP:= 56 ;END LOOP;Y<= 57 ;END PROCESS;END;十七在下面横线上填上合适的语句;完成一个逻辑电路的设计;其布尔方程为Y=A+BC⊙D+B⊕F.LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY COMB ISPORTA; B;C;D;E;F;: IN STD_LOGIC;Y: OUT STD_LOGIC;END COMB;ARCHITECTURE ONE OF COMB ISBEGINY<=A OR B AND C 58 D OR B 59 F;END ARCHITECTURE ONE;十八在下面横线上填上合适的语句;完成一个带使能功能的二-十进制译码器的设计.. LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MY2TO10 ISPORT EN: IN STD_LOGIC;DIN: IN STD_LOGIC_VECTOR60 DOWNTO 0;POUT: OUT STD_LOGIC_VECTOR9 DOWNTO 0 ;END;ARCHITECTURE ARCH OF MY2TO10 ISBEGINPROCESSEN; DINBEGINIF EN=’1’ THENCASE DIN ISWHEN "0000" => POUT<="0000000001";WHEN "0001" => POUT<="0000000010";WHEN "0010" => POUT<="0000000100";WHEN "0011" => POUT<="0000001000";WHEN "0100" => POUT<="0000010000";WHEN "0101" => POUT<="0000100000";WHEN "0110" => POUT<="0001000000";WHEN "0111" => POUT<="0010000000";WHEN "1000" => POUT<="010*******";WHEN "1001" => POUT<="1000000000";WHEN OTHERS => POUT<="0000000000";END CASE;END IF;END PROCESS;END;十九在下面横线上填上合适的语句;完成下降沿触发的D触发器的设计..LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL ;ENTITY DFF ISPORTD;CLK:IN STD_LOGIC;Q; QB: OUT STD_LOGIC;END DFF;ARCHITECTURE BEHAVE OF DFF ISBEGINPROCESSCLKBEGINIF 61 AND CLK'EVENT THENQ <=62 ;QB<=NOT D;END IF;END PROCESS;END BEHAVE;二十在下面横线上填上合适的语句;完成移位寄存器的设计..说明:4位串入-串出移位寄存器有有1个串行数据输入端DI、1个串行数据输出输出端DO 和1个时钟输入端CLKLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY SISO ISPORTDI: IN STD_LOGIC;CLK:IN STD_LOGIC;DO:OUT STD_LOGIC;END SISO;ARCHITECTURE A OF SISO ISSIGNAL Q: STD_LOGIC_VECTOR3 DOWNTO 0;BEGINPROCESSCLK;DIBEGINIF CLK’ EVENT AND CLK=’1’ THENQ0<=63 ;FOR 64 LOOPQI<=65 ;END IF;END PROCESS;DO<=Q3;END A;二十一在下面横线上填上合适的语句;完成同步22进制计数器的设计..LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY COUNTER22 ISPORT CLK: IN STD_LOGIC;CH; C: OUT STD_LOGIC;QB1; QA1: OUT STD_LOGIC_VECTOR3 DOWNTO 0;END;ARCHITECTURE BEHAV OF COUNTER22 ISSIGNAL QB; QA: STD_LOGIC_VECTOR3 DOWNTO 0;SIGNAL CIN: STD_LOGIC;BEGINQB1<=QB;QA1<=QA;PROCESSCLKBEGINIF CLK'EVENT AND CLK='1' THENIF QA=66 OR QB=2 AND QA=1 THEN QA<="0000"; CIN<='0';ELSIF QA=67 THEN CIN<='1'; QA<=QA+1;ELSE QA<=68 ;CIN<='0';END IF;END IF;END PROCESS;PROCESSCIN; CLKBEGINIF CLK'EVENT AND CLK='1' THENIF QB=2 AND QA=1 THEN QB<=69 ; C<='1';ELSE C<=70 ;END IF;IF CIN='1' THEN QB<=71 ;END IF;END IF;END PROCESS;CH<=CIN;END;二十二在下面横线上填上合适的语句;完成一个“01111110”序列发生器的设计..LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY SENQGEN ISPORTCLK;CLR;CLOCK:IN STD_LOGIC;ZO:OUT STD_LOGIC;END;ARCHITECTURE ART OF SENQGEN ISSIGNAL COUNT:STD_LOGIC_VECTOR2 DOWNTO 0;SIGNAL Z:STD_LOGIC:='0';BEGINPROCESSCLK;CLRBEGINIF CLR='1' THEN COUNT<="000";ELSEIF CLK='1' AND CLK'EVENT THENIF COUNT=72 THEN COUNT<="000";ELSE COUNT<=COUNT+1;END IF;END IF;END IF;END PROCESS;PROCESSCOUNTBEGINCASE COUNT ISWHEN "000"=>Z<='0';WHEN "001"=>Z<='1';WHEN "010"=>Z<='1';WHEN "011"=>Z<='1';WHEN "100"=>Z<='1';WHEN "101"=>Z<='1';WHEN "110"=>Z<='1';WHEN OTHERS=>Z<=73 ;END CASE;END PROCESS;PROCESSCLOCK;ZBEGINIF CLOCK='1' AND CLOCK'EVENT THENZO<=74 ;END IF;END PROCESS;END ART;二十三在下面横线上填上合适的语句;完成一个“01111110”序列信号检测器的设计..LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY DETECT ISPORT DATAIN:IN STD_LOGIC;CLK:IN STD_LOGIC;Q:BUFFER STD_LOGIC;END DETECT;ARCHITECTURE ART OF DETECT ISTYPE STATETYPE IS S0;S1;S2;S3;S4;S5;S6;S7;S8;BEGINPROCESSCLKVARIABLE 75 :76 ;BEGINQ<='0';CASE PRESENT_STATE ISWHEN S0=>IF DATAIN='0' THEN PRESENT_STATE:=S1;ELSE PRESENT_STATE:=S0; END IF;WHEN S1=>IF DATAIN='1' THEN PRESENT_STATE:=S2;ELSE PRESENT_STATE:=S1; END IF;WHEN S2=>IF DATAIN='1' THEN PRESENT_STATE:=S3;ELSE PRESENT_STATE:=S1; END IF;WHEN S3=>IF DATAIN='1' THEN PRESENT_STATE:=S4;ELSE PRESENT_STATE:=S1; END IF;WHEN S4=>IF DATAIN='1' THEN PRESENT_STATE:=S5;ELSE PRESENT_STATE:=S1; END IF;WHEN S5=>IF DATAIN='1' THEN PRESENT_STATE:=S6;ELSE PRESENT_STATE:=S1; END IF;WHEN S6=>IF DATAIN='1' THEN PRESENT_STATE:=S7;ELSE PRESENT_STATE:=S1; END IF;WHEN S7=>IF DATAIN='0' THEN PRESENT_STATE:=S8;Q<='1'; ELSE PRESENT_STATE:=S0; END IF;WHEN S8=>IF DATAIN='0' THEN PRESENT_STATE:=77 ;ELSE PRESENT_STATE:=78 ; END IF;END CASE;79 CLK='1';END PROCESS;END ART;二十四在下面横线上填上合适的语句;完成序列信号发生器的设计..说明:带异步复位为CLR;时钟端为CLK;输出端为Q;串行输出指定序列低位先出.. LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY SENQGEN ISPORTCLR;CLK:IN STD_LOGIC;Q:OUT STD_LOGIC;END SENQGEN;ARCHITECTURE BEHA OF SENQGEN ISSIGNAL Q_TEMP:STD_LOGIC_VECTOR2 DOWNTO 0;BEGINPROCESSCLK;CLRBEGINIF CLR='1' THEN Q_TEMP<="000";80 CLK'EVENT AND CLK='1' THENIF Q_TEMP="111" THEN Q_TEMP<="000";81 Q_TEMP<=Q_TEMP+1;END IF;82 ;END PROCESS;PROCESSQ_TEMPBEGINCASE Q_TEMP ISWHEN "000"=>Q<='0';WHEN "001"=>Q<='1';WHEN "010"=>Q<='0';WHEN "011"=>Q<='1';WHEN "100"=>Q<='1';WHEN "101"=>Q<='1';WHEN "110"=>Q<='1';WHEN "111"=>Q<='0';WHEN OTHERS=>83 ;END CASE;END PROCESS;END BEHA;二十五在下面横线上填上合适的语句;完成七人表决器的设计..说明:一个带输出显示的七人表决器两种结果:同意;反对.. LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY BIAOJUE7 ISPORTD:IN STD_LOGIC_VECTOR0 TO 6;RLED;GLED:OUT STD_LOGIC;LEDSEG:OUT STD_LOGIC_VECTOR 6 DOWNTO 0;END;ARCHITECTURE BEV OF BIAOJUE7 ISBEGINPROCESSDVARIABLE COUNT:INTEGER RANGE 0 TO 7 ;BEGINCOUNT:=84 ;FOR 85 LOOPIF DI='1' THEN COUNT:=86 ;ELSE COUNT:=COUNT;END IF;END LOOP;IF COUNT>87 THEN GLED<='1'; RLED<='0'; ELSE GLED<='0'; RLED<='1';END IF;CASE COUNT ISWHEN 0=> LEDSEG<="0111111";WHEN 1=> LEDSEG<="0000110";WHEN 2=> LEDSEG<="1011011";WHEN 3=> LEDSEG<="1001111";WHEN 4=> LEDSEG<="1100110";WHEN 5=> LEDSEG<="1101101";WHEN 6=> LEDSEG<="1111101";WHEN 7=> LEDSEG<="0100111";END CASE;END PROCESS;END BEV;二十六在下面横线上填上合适的语句;完成有限状态机的设计..说明:状态转换图如右图;S0~S3为状态号;圈内为输出..LIBRARY 1EEE;USE IEEE.STD_ LOGIC_1164.ALL;PORT CLK;RESET:IN STD_LOGIC;INPUTS :IN STD_LOGIC_VECTOR 0 TO 1;OUTPUTS :OUT INTEGER RANGE 0 TO 15 ;END S_ MACHINE;ARCHITECTURE BEHA V OF S_MACHINE ISTYPE STA TES IS S0; S1; S2; S3;SIGNAL CURCENT_STA TE;NEXT_STA TE:STA TES;BEGINREG: PROCESS RESET;CLK --状态切换BEGINIF RESET = ‘1’ THEN CURRENT_ STATE <= S0;ELSIF CLK=’L’AND CLK‘EVENT THENCURRENT_ STA TE <= NEXT_ STA TE;END IF;END PROCESS;COM:PROCESSCURRENT_ STATE; INPUTS--下一状态、BEGINCASE CURRENT_ STATE ISWHEN S0 => OUTPUTS<= 88 ;IF INPUTS=”00” THEN NEXT_ STA TE<=S0;ELSE NEXT_ STATE<=SL;END IF;WHEN SL=> OUTPUTS<=8;IF INPUTS= 89 THEN NEXT_ STA TE<= 90 ;ELSE NEXT_STATE<=S2;END IF;WHEN S2=> OUTPUTS<=12;IF INPUTS=“11”THEN NEXT_STATE<=S0;ELSE NEXT_STATE<= S3;END IF;WHEN S3=> OUTPUTS<=14;IF INPUTS = “11”THEN NEXT_STA TE <=S3;;ELSE NEXT STATE <=S0;END IF;END CASE;91 ;END BEHA V;二十七在下面横线上填上合适的语句;完成移位寄存器74166的设计.. LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY TTL74166 ISPORT A;B;C;D;E;F;G;H:IN STD_LOGIC; --8位并行输入信号CLK:IN STD_LOGIC; --时钟信号RESET:IN STD_LOGIC; --复位信号SE:IN STD_LOGIC; --串行输入信号FE:IN STD_LOGIC; --时钟信号禁止端SL:IN STD_LOGIC; --移位装载控制端Q:OUT STD_LOGIC; --串行输出信号END TTL74166;ARCHITECTURE ART OF TTL74166 ISSIGNAL TMPREG8:STD_LOGIC_VECTOR7 DOWNTO 0;BEGINPROCESSCLK;RESET;SL;FEBEGINIF RESET='1' THEN TMPREG8<=92 ; Q<=TMPREG87; ELSIF CLK'EVENT AND CLK='1' THENIF FE='0' THENIF SL='0' THENTMPREG80<=A;TMPREG81<=B;TMPREG82<=C;TMPREG83<=D;TMPREG84<=E;TMPREG85<=F;TMPREG86<=G;TMPREG87<=H;93 SL='1' THENFOR I IN TMPREG8'HIGH DOWNTO 94 LOOPTMPREG8I<=95 ;END LOOP;TMPREG8TMPREG8'LOW<=96 ;Q<=97 ;END IF;END IF;END IF;END PROCESS;END ART;二十八在下面横线上填上合适的语句;完成8位双向总线缓冲器的设计..LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY TRI_BIGATE ISPORT A;B: INOUT STD_LOGIC_VECTOR7 DOWNTO 0;EN; DR: IN STD_LOGIC;END;ARCHITECTURE RTL OF TRI_BIGATE ISSIGNAL AOUT; BOUT:STD_LOGIC_VECTOR7 DOWNTO 0;BEGINPROCESSA; DR; ENBEGIN IF EN=‘0’ AND DR=‘1’ THEN BOUT<=A;ELSEBOUT<=“ZZZZZZZZ”;END IF;B<=BOUT;END PROCESS;PROCESSB; DR; ENBEGINIF EN=‘0’ AND DR=‘0’ THENAOUT<=98 ;ELSEAOUT<=99 ;END IF;A<=100 ;END PROCESS;END;二十九在下面横线上填上合适的语句;完成4位串入/并出移位寄存器的设计.. 说明:4位串入/并出移位寄存器可以用D触发器组成..LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL ;ENTITY DFF ISPORTD;CLK:IN STD_LOGIC;Q: OUT STD_LOGIC;END DFF;ARCHITECTURE BEHAVE OF DFF ISBEGIN PROCESSCLKBEGINIF CLK= '0' AND CLK'EVENT THEN Q <=D;END IF;END PROCESS;END BEHAVE;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY SHIFT ISPORTA;CLK: IN STD_LOGIC;D : OUT STD_LOGIC;END SHIFT;ARCHITECTURE SHIFT1 OF SHIFT ISCOMPONENT DFF1PORT D;CLK: IN STD_LOGIC;Q: OUT STD_LOGIC;END COMPONENT ;SIGNAL Z:STD_LOGIC_VECTOR0 TO 4;BEGINZ0<=101 ;G1:FOR 102 GENERATEDFFX:DFF1 PORT MAP ZI;CLK;103 ;END GENERATE;D<=104 ;END SHIFT1;三十在下面横线上填上合适的语句;完成4位异步计数器的设计..说明:4位异步计数器可以用D触发器器组成..LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL ;ENTITY DFF1 ISPORTD;CLK:IN STD_LOGIC;Q; QB: OUT STD_LOGIC;END DFF1;ARCHITECTURE BEHAVE OF DFF1 ISBEGIN PROCESSCLKBEGINIF CLK= '1' AND CLK'EVENT THEN Q <=D; QB<=NOT D;END IF;END PROCESS;END BEHAVE;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY RPLCONT ISPORT CLK : IN STD_LOGIC;COUNT : OUT STD_LOGIC_VECTOR3 DOWNTO 0;END RPLCONT;ARCHITECTURE RPLCONT OF RPLCONT ISCOMPONENT DFF1PORT CLK;D:IN STD_LOGIC;Q;QB:OUT STD_LOGIC;END COMPONENT ;SIGNAL COUNT_IN_BAR:STD_LOGIC_VECTOR4 DOWNTO 0;BEGINCOUNT_IN_BAR0<=CLK;GEN1:FOR I IN 0 TO 3 GENERATEU:DFF1 PORT MAP CLK=>105 ; D=>106 ;Q=>107 ;QB=>108 ;END GENERATE;END RPLCONT;三十一在下面横线上填上合适的语句;完成交通灯控制器的设计..说明:红、黄、绿灯分别亮10秒;状态0时东西绿灯亮;南北红灯亮;状态1时东西绿、黄灯亮;南北红灯亮;状态2时东西红灯亮;南北绿灯亮;状态3时东西红灯亮;南北绿、黄灯亮..LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY TRAFFICLED1 ISPORT CLK; RESET: IN STD_LOGIC;Q: OUT STD_LOGIC_VECTOR11 DOWNTO 0 ;END;ARCHITECTURE ONE OF TRAFFICLED1 ISSIGNAL Y_EWSN; G_EWSN; R_EWSN:STD_LOGIC_VECTOR3 DOWNTO 0;SIGNAL COUNT:INTEGER RANGE 0 TO 9;SIGNAL STATE:INTEGER RANGE 0 TO 3;BEGINPROCESSRESET; CLK;COUNTBEGINIF RESET='1' THEN COUNT<=0; STATE<=0;ELSIF CLK'EVENT AND CLK='1' THEN COUNT<=COUNT+1;IF COUNT=109 THEN STATE <=STATE+1;END IF;IF STATE>110 THEN STATE <=0;END IF;END IF;CASE STATE ISWHEN 0 => Y_EWSN<="0000"; G_EWSN<="1100"; R_EWSN<="0011";WHEN 1 => Y_EWSN<="1100"; G_EWSN<="1100"; R_EWSN<="0011";WHEN 2 => Y_EWSN<="0000"; G_EWSN<="0011"; R_EWSN<="1100";WHEN 3=> Y_EWSN<="0011"; G_EWSN<="0011"; R_EWSN<="1100";WHEN OTHERS=>111 ;END CASE;END PROCESS;Q0<=R_EWSN0; Q1<=G_EWSN0; Q2<=Y_EWSN0 ;Q3<=R_EWSN2; Q4<=G_EWSN2; Q5<=Y_EWSN2 ;Q6<=R_EWSN1; Q7<=G_EWSN1; Q8<=Y_EWSN1 ;Q9<=R_EWSN3; Q10<=G_EWSN3; Q11<=Y_EWSN3 ;END;三十二在下面横线上填上合适的语句;完成8位数字比较器的设计..ENTITY COMP ISPORTA;B: IN 112 RANGE 0 T0 113 ;AEQUALB; AGREATB; ALESSB : OUT BIT;END COMP;ARCHITECTURE BEHA VE OF COMP ISBEGINAEQUALB<=‘1’WHEN A=B ELSE‘0’;AGREATB<=‘1’WHEN A>B ELSE‘0’;ALESSB<=‘1’WHEN A<B ELSE‘0’;END BEHA VE;三十三在下面横线上填上合适的语句;完成一个16个字节的堆栈的设计..说明:堆栈有复位信号、压栈/弹栈信号、堆栈满信号、数据输入/输出口.. LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_SIGNED.ALL;ENTITY STACK ISPORTDATAIN : IN STD_LOGIC_VECTOR 7 DOWNTO 0 ;PUSH ; POP ; RESET ; CLK : IN STD_LOGIC;STACKFULL : OUT STD_LOGIC;DATAOUT : BUFFER STD_LOGIC_VECTOR 7 DOWNTO 0 ;END STACK;ARCHITECTURE A OF STACK ISTYPE ARRAYLOGIC IS ARRAY 15 DOWTO 0 OF STD_LOGIC_VECTOR 7 DOWNTO 0 ;--定义一个16字节数据类型SIGNAL DATA : ARRAYLOGIC;-- 此处定义了DA TA为一个数组16×8 SIGNAL STACKFLAG : STD_LOGIC_VECTOR 15 DOWNTO 0 ;--定义堆栈标志;每一字节有数据为1;无数据为0 BEGINSTACKFULL<=114 ; --字节0为栈底PROCESS CLK ; NRESET ; POP ; PUSHBEGINIF RESET = ‘1’ THENSTACKFLAG<=OTHERS => ‘0’ ;DATAOUT<=OTHERS => ‘0’ ;FOR I IN 0 TO 15 LOOPDATA I <=115 ;END LOOP;ELSIF CLK’EVENT AND CLK = ‘1’ THENIF PUSH = ‘1’ AND POP= ‘0’ THEN -- PUSHFOR I IN 0 TO 14 LOOPDATA I <=116 ;END LOOP;DATA 15 <=117 ;STACKFLAG<=‘1’ & STACKFLAG15 DOWNTO 1 ;ELSIF PUSH = ‘0’ AND POP= ‘1’ THEN -- POPDATAOUT<=DA TA 15;FOR I IN 15 DOWNTO 1 LOOPDATA I <=118 ;END LOOP;STACKFLAG<=STACKFLAG 119 DOWNTO 0 & ‘0’;END IF;END IF;END PROCESS;END A;三十四在下面横线上填上合适的语句;完成一个8位分频器的设计..LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY PULSE ISPORT CLK : IN STD_LOGIC;D : IN STD_LOGIC_VECTOR 7 DOWNTO 0;FOUT : OUT STD_LOGIC ;END;ARCHITECTURE ONE OF PULSE ISSIGNAL FULL : STD_LOGIC;BEGINP_REG: PROCESSCLK120 CNT8 : STD_LOGIC_VECTOR7 DOWNTO 0;BEGINIF CLK’EVENT AND CLK = ‘1’ THENIF CNT8 = "11111111" THENCNT8 := 121 ; --当CNT8计数计满时;输入数据D被同步预置给计数器CNT8FULL <= '1'; --同时使溢出标志信号FULL输出为高电平ELSE CNT8 := 122 ; --否则继续作加1计数FULL <= '0'; --且输出溢出标志信号FULL为低电平END IF;END IF;END PROCESS P_REG;P_DIV: PROCESS 123VARIABLE CNT2 : STD_LOGIC;BEGINIF FULL'EVENT AND FULL = '1' THENCNT2 <= 124 ; --如果溢出标志信号FULL为高电平;D触发器输出取反IF CNT2 = '1' THEN FOUT <= '1';ELSE FOUT <= '0';END IF;END IF;END PROCESS P_DIV;END;三十五在下面横线上填上合适的语句;完成一个10线-4线优先编码器的设计..LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL;ENTITY CODER ISPORT DIN : IN STD_LOGIC_VECTOR9 DOWNTO 0;OUTPUT : OUT STD_LOGIC_VECTOR3 DOWNTO 0 ;END CODER;ARCHITECTURE BEHA V OF CODER ISSIGNAL SIN : STD_LOGIC_VECTOR3 DOWNTO 0;BEGINPROCESS 125BEGINIF DIN9='0' THEN SIN <= "1001" ;126 DIN8=’0’ THEN SIN <= "1000" ;ELSIF DIN7='0' THEN SIN <= "0111" ;ELSIF DIN6='0' THEN SIN <= "0110" ;ELSIF DIN5='0' THEN SIN <= "0101" ;ELSIF DIN4='0' THEN SIN <= "0100" ;ELSIF DIN3='0' THEN SIN <= "0011" ;ELSIF DIN2='0' THEN SIN <= "0010" ;ELSIF DIN1='0' THEN SIN <= "0001" ;ELSE SIN <= 127 ;128 ;END PROCESS ;OUTPUT <= SIN ;END BEHA V;三十六在下面横线上填上合适的语句;完成一个摩尔状态机的设计..说明:状态机的状态图见图A;状态结构图见图B.。

VHDL程序设计教程习题解答

VHDL程序设计教程习题参考解答第1章思考题解答1.什么是VHDL?简述VHDL的发展史。

答:VHDL是美国国防部为电子项目设计承包商提供的,签定合同使用的,电子系统硬件描述语言。

1983年成立VHDL语言开发组,1987年推广实施,1993年扩充改版。

VHDL 是IEEE标准语言,广泛用于数字集成电路逻辑设计。

2.简述VHDL设计实体的结构。

答:实体由实体名、类型表、端口表、实体说明部分和实体语句部分组成。

根据IEEE标准,实体组织的一般格式为:ENTITY 实体名 IS[GENERIC(类型表);] --可选项[PORT(端口表);] --必需项实体说明部分; --可选项[BEGIN实体语句部分;]END [ENTITY] [实体名];3.分别用结构体的3种描述法设计一个4位计数器。

答:用行为描述方法设计一个4位计数器如下,其它描述方法,读者可自行设计。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;use ieee.std_logic_unsigned.all;ENTITY countA ISPORT (clk,clr,en:IN STD_LOGIC;Qa,qb,qc,qd:OUT STD_LOGIC);END countA;ARCHITECTURE example OF countA ISSIGNAL count_4:STD_LOGIC_vector (3 DOWNTO 0);BEGINQa <= count_4(0);Qb <= count_4(1);Qc <= count_4(2);Qd <= count_4(3);PROCESS (clk,clr)BEGINIF (clr = '1' ) THENCount_4 <= "0000";ELSIF (clk'EVENT AND clk = '1' ) THENIF (en = '1' ) THENIF (count_4 = "1111") THENcount_4 <= "0000";ELSEcount_4 <= count_4+ '1';END IF;END IF;END IF;END PROCESS;END example;第2章思考题解答1.什么叫对象?对象有哪几个类型?答:在VHDL语言中,凡是可以赋于一个值的客体叫对象(object)。

第3章--作业解答

(3)C1C2=10时, F A B

(4)C1C2=11时, F AB

试设计符合上述要求旳逻辑电路(器件不限)。

解:题目中要求控制信号对不同功能进行选择, 故选用数据选择器实现,分析设计要求,得到 逻辑体现式:

F C1C 2( A B ) C C1 2( AB ) C1C 2( A B ) C1C2( AB )

1

0

1

1

0

1

0

0

0

1

1

1

1

0

0

0

0

0

1

1

1

10

0

1

1

习题3.19 用8选1数据选择器设计一种组合逻

辑电路。该电路有3个输入逻辑变量A、B、C 和1个工作状态控制变量M。当M=0时电路实 现“意见一致”功能(A、B、C状态一致时输出 为1,不然输出为0),而M=1时电路实现“多 数表决”功能,即输出与A、B、C中多数旳状

B1B0 A1A0

00

01

11

10

00 1 0 0

0

B1 B0

01 1

10

0

A B0 1 11 1

1

11

10 1 1 0 1

A1 B1

A1 A0

A1 B0

F1 A1 B1 B1 B0 A1 A0 A1B0 A0 B1

(3)卡诺图化简函数,得到最简与或式

F1 A1 B1 B1 B0 A1 A0 A1B0 A0 B1

outp(0)<='1' WHEN inp="000" ELSE '0'; outp(1)<='1' WHEN inp="001" ELSE '0'; outp(2)<='1' WHEN inp="010" ELSE '0'; outp(3)<='1' WHEN inp="011" ELSE '0'; outp(4)<='1' WHEN inp="100" ELSE '0'; outp(5)<='1' WHEN inp="101" ELSE '0'; outp(6)<='1' WHEN inp="110" ELSE '0'; outp(7)<='1' WHEN inp="111" ELSE '0'; END behave;

VHDL参考答案这是我们这学期考的大题都是

一、简答题1、VHDL语言程序的基本结构?实体、结构体、配置、包集合、库。

2、信号和变量的区别?①信号用于作为电路中的信号连线,变量用于作为进程中局部数据存储单元;②信号是全局量在整个结构体内的任何地方都可以使用,变量是局部量只能在进程、子程序内部定义和使用;③信号代入语句采用“<=”代入符,该语句即使被执行也不会使信号立即发生代入,变量的赋值符号为“:=”,在变量赋值语句中,语句一旦被执行,其值立即被赋予变量。

3、可编程逻辑器件的优点?①集成度高,极大的减小电路的面积,降低功耗,提高可靠性;②具有完善先进的开发工具,提供语言、图形等设计方法,十分灵活,通过仿真工具来验证设计的正确性;③可以反复地擦除、编程,方便设计的修改和升级;④灵活地定义管教功能,减轻设计工作量,缩短系统开发时间;⑤保密性好。

4、函数与过程的异同?相同点:函数与过程都是子程序,主函数调用它们以后能将处理结果返回主程序;函数与过程中的语句都是顺序执行的。

不同点:过程的参数可以是输入,也可以是输出,函数的参数都是输入参数;函数只有一个输出,只能通过函数体内的RETURN语句来实现,函数体内不能有信号赋值语句,而过程却可以有不止一个输出,而且是通过过程体内的信号赋值语句或者变量赋值语句来实现的;函数的调用只能通过表达式来实现,过程的调用则是通过过程调用语句来实现的。

5、CPLD与FPGA的异同?①FPGA采用SRAM进行功能配置,可重复编程,但系统掉电后,SRAM中的数据丢失。

因此,需在FPGA外加EPROM,将配置数据写入其中,系统每次上电自动将数据引入SRAM中。

CPLD器件一般采用EEPROM存储技术,可重复编程,并且系统掉电后,EEPROM中的数据不会丢失,适于数据的保密。

②FPGA器件含有丰富的触发器资源,易于实现时序逻辑,如果要求实现较复杂的组合电路则需要几个器件结合起来实现。

CPLD的与或阵列结构,使其适于实现大规模的组合功能,但触发器资源相对较少。

vhdl课后习题答案

vhdl课后习题答案VHDL课后习题答案在学习VHDL(VHSIC Hardware Description Language)这门课程时,课后习题是巩固知识、提高能力的重要方式。

通过认真完成课后习题并查看答案,我们可以更好地理解和掌握VHDL的相关知识,提高自己的编程能力。

下面我们将通过几个典型的VHDL课后习题答案来展示VHDL的魅力和应用。

1. 课后习题一题目:使用VHDL编写一个简单的门电路,包括AND门、OR门和NOT门,并进行仿真验证。

答案:首先,我们定义AND门、OR门和NOT门的输入输出信号。

然后,使用VHDL语言编写各个门电路的逻辑实现,并进行仿真验证。

最后,我们可以观察仿真波形图,验证门电路的功能是否符合预期。

2. 课后习题二题目:使用VHDL编写一个4位全加器,并进行综合、布线和时序分析。

答案:首先,我们定义全加器的输入输出信号。

然后,使用VHDL语言编写4位全加器的逻辑实现,并进行综合、布线和时序分析。

最后,我们可以观察综合和布线报告,分析全加器的资源利用情况和时序性能。

3. 课后习题三题目:使用VHDL编写一个有限状态机(FSM),实现一个简单的计数器,并进行状态转移图和状态转移表的分析。

答案:首先,我们定义有限状态机的状态和状态转移条件。

然后,使用VHDL 语言编写有限状态机的逻辑实现,并进行状态转移图和状态转移表的分析。

最后,我们可以观察状态转移图和状态转移表,验证有限状态机的状态转移是否符合预期。

通过以上几个VHDL课后习题答案的展示,我们可以看到VHDL在数字电路设计和硬件描述方面的强大应用。

通过学习VHDL并完成课后习题,我们可以提高自己的编程能力,掌握数字电路设计的基本原理和方法。

希望大家在学习VHDL的过程中能够认真完成课后习题,并不断提高自己的编程水平。

EDA技术与VHDL程序开发基础教程课后答案(完整版)

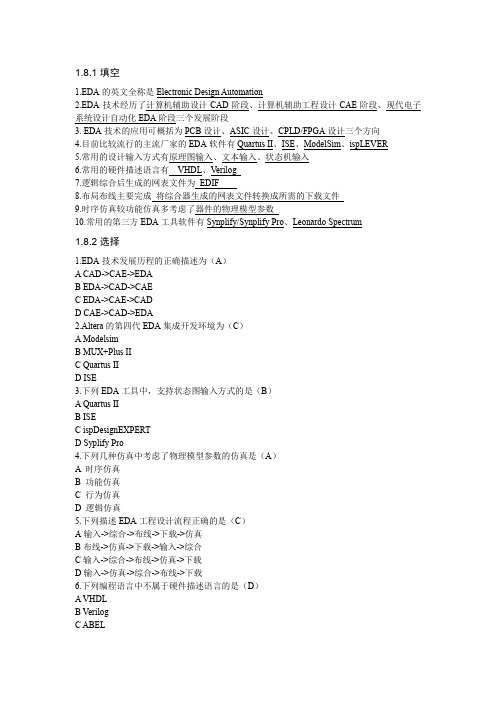

1.8.1填空1.EDA的英文全称是Electronic Design Automation2.EDA技术经历了计算机辅助设计CAD阶段、计算机辅助工程设计CAE阶段、现代电子系统设计自动化EDA阶段三个发展阶段3. EDA技术的应用可概括为PCB设计、ASIC设计、CPLD/FPGA设计三个方向4.目前比较流行的主流厂家的EDA软件有Quartus II、ISE、ModelSim、ispLEVER5.常用的设计输入方式有原理图输入、文本输入、状态机输入6.常用的硬件描述语言有VHDL、Verilog7.逻辑综合后生成的网表文件为EDIF8.布局布线主要完成将综合器生成的网表文件转换成所需的下载文件9.时序仿真较功能仿真多考虑了器件的物理模型参数10.常用的第三方EDA工具软件有Synplify/Synplify Pro、Leonardo Spectrum1.8.2选择1.EDA技术发展历程的正确描述为(A)A CAD->CAE->EDAB EDA->CAD->CAEC EDA->CAE->CADD CAE->CAD->EDA2.Altera的第四代EDA集成开发环境为(C)A ModelsimB MUX+Plus IIC Quartus IID ISE3.下列EDA工具中,支持状态图输入方式的是(B)A Quartus IIB ISEC ispDesignEXPERTD Syplify Pro4.下列几种仿真中考虑了物理模型参数的仿真是(A)A 时序仿真B 功能仿真C 行为仿真D 逻辑仿真5.下列描述EDA工程设计流程正确的是(C)A输入->综合->布线->下载->仿真B布线->仿真->下载->输入->综合C输入->综合->布线->仿真->下载D输入->仿真->综合->布线->下载6.下列编程语言中不属于硬件描述语言的是(D)A VHDLB VerilogC ABELD PHP1.8.3问答1.结合本章学习的知识,简述什么是EDA技术?谈谈自己对EDA技术的认识?答:EDA(Electronic Design Automation)工程是现代电子信息工程领域中一门发展迅速的新技术。

Verilog HDL数字设计与综合(第二版) 第三章课后习题答案

1.试写出以下数字:a.将十进制数123用8位二进制数表示出来,使用“_”增加可读性;b.未知的16位十六进制数,各位均为x;c.将十进制数 2使用4位二进制数表示出来,并写出结果的2的补码形式;d.一个无位宽说明的十六进制数1234。

答:a. 8’b0111_1011b. 16’hxc. -4’b0010,补码4’b1110d. ’h12342.下面的各个字符串是否合法?如果非法,请写出正确答案。

a.“This is a string displaying the % sign”b.“out =in1 +in2 ”c.“Please ring a bell \007”d.“This is a backslash \character\n”答:a是错误的,应改为“This is a string displaying the % %sign”,编译后输出:# This is a string displaying the % sign(注意,输出结果前#符号是仿真器输出每行前自带的标志符,在本习题解答中不予去除,下同)b# out =in1 +in2c# Please ring a belld# This is a backslash character#应改为双斜线\\,如“This is a backslash \\character\n”(主要考察的是特殊字符的输出,比如a中的输出%需要%%操作。

C中的\007在编译器中输出为空,复制到word中输出是一个 ,有兴趣的同学可以自己试验一下,比如\006输出是 ,\004输出是 ,等等。

d中的\character在转义操作符\后跟的单词无语法意义,故在输出character,而\n 表示换行,仿真后的输出也是如此显示的。

)3.下面的各个标识符是否合法?a.system1b.1regc.$latchd.exec$答:a是合法的;b、c不能以1和$开头;d是合法的。

vhdl_参考答案_上机练习三:时序逻辑电路设计2

vhdl_参考答案_上机练习三:时序逻辑电路设计2VHDL与复杂数字系统设计上机实验3:时序逻辑电路的VHDL程序设计⼀、实验⽬的:1.掌握在Max+plus II开发平台上,使⽤硬件描述语⾔设计电路的基本操作步骤;2.运⽤所学VHDL的描述语句完成⼀种时序逻辑电路的设计。

⼆、要点:时序逻辑电路在电路结构上有两个显著特点:第⼀,时序电路通常包含组合电路和存储电路两个组成部分,⽽且存储电路是必不可少的。

第⼆,存储电路的输出状态必须反馈到组合电路的输⼊端,与输⼊信号⼀起,共同决定组合逻辑电路的输出。

时序电路的信号变化特点:时序电路以时钟信号为驱动;电路内部信号的变化(或输出信号的变化)只发⽣在特定的时钟边沿;其他时刻输⼊信号的变化对电路不产⽣影响;要点:执⾏条件的控制;时钟边沿的检测;1、执⾏条件的控制采⽤进程描述可以有效控制执⾏条件,若进程以时钟信号(clk)为唯⼀敏感信号,则只有当时钟信号变化时,进程才执⾏;在其他时刻,任何输⼊信号的变化对电路(进程)不起作⽤;模版1:process(clock) --敏感信号表中只有时钟beginif rising_edge(clock) then--监测时钟上升沿,若⽤falling_edge(clock) ……--则监测时钟下升沿。

end if;end process;例:时钟上升沿动作的D触发器library ieee;use ieee.std_logic_1164.all;entity dff1 isport(clk, d: in std_logic;q: out std_logic);end dff1;architecture rtl of dff1 isbeginprocess(clk)beginif (clk'event and clk='1') thenq<=d;end if;end process;end rtl;时序逻辑电路的初始状态应由复位(或清零)信号来设置,根据复位信号对时序逻辑电路复位操作的不同,可分为同步复位和异步复位。

(三)VHDL语言的数据类型及运算操作符090914(119)

5. 布尔量(Boolean)

一个布尔量具有两种状态,“真”或者“假”。虽然布尔量也是 二值枚举量,但它和位不同,没有数值的含义,也不能进行算术 运算。它能进行关系运算。例如,它可以在IF语句中被测试,测 试结果产生一个布尔量TRUE或者FALSE。 一个布尔量常用来表示信号的状态或者总线上的情况。如果 某个信号或者变量被定义为布尔量,那么在仿真中将自动地对其 赋值进行核查。这一类型的数据的初始值一般总为FALSE。

【例3-1-b】

PROCESS( A, B, C)

VARIABLE D:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

D:=A; X<=B+D;

结果:X<=B+A; Y<=B+C;

D:=C;

Y<=B+D;

END PROCESS;

进程内的语句是顺序执行的, 由于D是变量,在执行 D:=A后,D=A,接着执行X<=B+D,使得在退出进程后 X=B+A 。接着执行D:=C 和 Y<=B+D ,使D=C,退出时, Y=B+C。

信号赋值语句举例: X<= y; a <= ‘1’; s1 <= s2 AFTER 10 ns;

3.1.4 信号和变量的主要区别

1) 赋值符不同 信号和变量的赋值符不同,如果一个值要赋给信号应用

代入符“<=”;而变量赋值则用赋值符“:=”。

信号和变量可以互相赋值,此时赋值符应根据左边被赋 值量的类型来确定。如果被赋值是信号应用代入符“<=”;如 果是变量,则应用赋值符“:=”。

例如: CONSTANT VCC: REAL:=5.0; CONSTANT DALY: TIME:=100 ns; CONSTANT FBUS: BIT_VECTOR:="0101";

最新整理版 EDA技术与VHDL第三章课后习题答案(第3版)潘松 黄继业

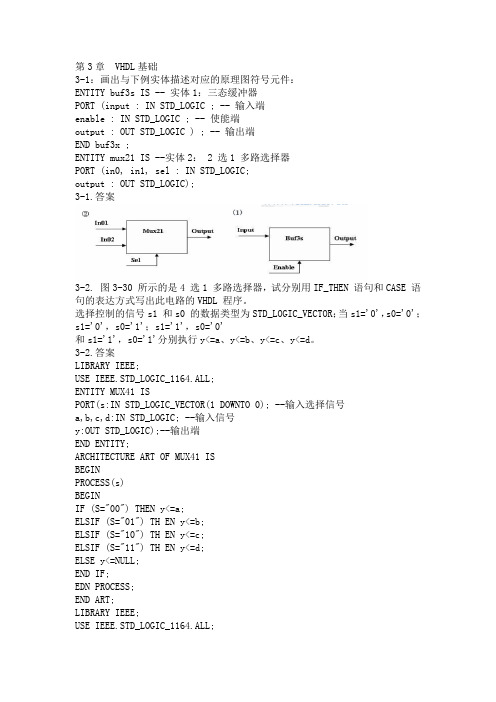

第3章 VHDL基础3-1:画出与下例实体描述对应的原理图符号元件:ENTITY buf3s IS -- 实体1:三态缓冲器PORT (input : IN STD_LOGIC ; -- 输入端enable : IN STD_LOGIC ; -- 使能端output : OUT STD_LOGIC ) ; -- 输出端END buf3x ;ENTITY mux21 IS --实体2: 2 选1 多路选择器PORT (in0, in1, sel : IN STD_LOGIC;output : OUT STD_LOGIC);3-1.答案3-2. 图3-30 所示的是4 选1 多路选择器,试分别用IF_THEN 语句和CASE 语句的表达方式写出此电路的VHDL 程序。

选择控制的信号s1 和s0 的数据类型为STD_LOGIC_VECTOR;当s1='0',s0='0';s1='0',s0='1';s1='1',s0='0'和s1='1',s0='1'分别执行y<=a、y<=b、y<=c、y<=d。

3-2.答案LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MUX41 ISPORT(s:IN STD_LOGIC_VECTOR(1 DOWNTO 0); --输入选择信号a,b,c,d:IN STD_LOGIC; --输入信号y:OUT STD_LOGIC);--输出端END ENTITY;ARCHITECTURE ART OF MUX41 ISBEGINPROCESS(s)BEGINIF (S="00") THEN y<=a;ELSIF (S="01") TH EN y<=b;ELSIF (S="10") TH EN y<=c;ELSIF (S="11") TH EN y<=d;ELSE y<=NULL;END IF;EDN PROCESS;END ART;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MUX41 ISPORT(s:IN STD_LOGIC_VECTOR(1 DOWNTO 0); --输入选择信号a,b,c,d:IN STD_LOGIC; --输入信号y:OUT STD_LOGIC);--输出端END MUX41;ARCHITECTURE ART OF MUX41 ISBEGINPROCESS(s)BEGINCASE s ISWHEN “00” => y<=a;WHEN “01” => y<=b;WHEN “10” => y<=c;WHEN “11” => y<=d;WHEN OTHERS =>NULL;END CASE;END PROCESS;END ART;3-3. 图3-31 所示的是双 2 选 1 多路选择器构成的电路MUXK,对于其中MUX21A,当s='0'和'1'时,分别有y<='a'和y<='b'。

数字电子技术基础第三版第三章答案

答:VHDL的覆盖面广,描述能力强,是一个多层次的硬件描述语言,VHDL已成为IEEE承认的一个工业标准,是一种通用的硬件描述语言。

VHDL有良好的可读性,可以被计算机接受,也容易被读者理解,VHDL源文件既是程序又是技术人员之间交换信息的文件,也可作为合同签约者之间的文件;VHDL的生命周期长,因为VHDL硬件描述与工艺无关;VHDL支持大规模设计的分解和已有设计的再利用。

对于译码器每一组输入编码,在若干个输出中仅有一个输出端为有效电平,其余输出皆处于无效电平,这类译码器称为变量译码器。常用的有2-4线译码器、3-8线译码器、4-10线8421BCD译码器等。

在数字电路中,需要将数字量的代码经过译码,送到数字显示器显示。能把数字量翻译成数字显示器能识别的译码器称为数字显示译码器,常用的有七段显示译码器。

F=

=

函数F的或非门电路如思考题图(c)所示。

题 什么叫竞争-冒险现象当门电路的两个输入端同时向相反的逻辑状态转换(即一个从0变成1,另一个从1变成0)时,输出是否一定有干扰脉冲产生

答:竞争指的是一个门电路多个输入信号同时跳变,或者一个信号经过不同路径传到同一个门电路的输入端导致信号到达时间不同的现象。冒险指的是由于竞争可能在电路输出端产生的毛刺现象。当门电路的两个输入端同时向相反的逻辑状态转换时,输出不一定有干扰脉冲产生。

组合逻辑电路的设计是根据实际逻辑问题,求出实现相应逻辑功能的最简单或者最合理的数字电路的过程。逻辑电路的设计步骤如下:

首先分析设计要求,建立真值表,选择所用门的类型,将逻辑表达式化为最简形式,或者变换为最合理的表达式,最后画出逻辑图。

题 组合逻辑电路如思考题图(a)所示。

(1)写出函数F的表达示。

《VHDL应用教程》课后习题参考答案

第1章绪论1.1电子设计自动化1.2EDA技术,是以大规模可编程逻辑器件为设计载体,以硬件描述语言为系统逻辑描述的主要表达方式,以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具,通过有关的开发软件,自动完成用软件的方式设计的电子系统到硬件系统的逻辑编译、逻辑化简、逻辑分割、逻辑综合及优化、逻辑布局布线、逻辑仿真,直至完成对于特定目标芯片的适配编译、逻辑映射、编程下载等工作,最终形成集成电子系统或专用集成芯片的一门新技术。

1.31、用软件的方式设计硬件。

2、用软件方式设计的系统到硬件系统的转换是由有关的开发软件自动完成的。

3、设计过程中可用有关软件进行各种仿真。

4、系统可现场编程,在线升级。

5、整个系统可集成在一个芯片上,体积小、功耗低、可靠性高。

因此,EDA技术是现代电子设计的发展趋势。

1.4可编程逻辑器件(Programmable Logic Device,PLD)是一种由用户编程以实现某种逻辑功能的新型逻辑器件。

FPGA和CPLD分别是现场可编程门阵列和复杂可编程逻辑器件的简称。

1.51、自顶向下设计方法是一种模块化设计方法。

它对设计的描述从上到下,逐步由粗略到详细,符合常规的逻辑思维习惯。

由于高层设计与器件无关,设计易于在各种集成电路工艺或可编程器件之间移植。

2、适合多个设计者同时进行设计。

随着技术的不断进步,许多设计由一个设计者已无法完成,而必须经过多个设计者分工协作来完成。

在这种情况下,应用自顶向下的设计方法便于多个设计者同时进行设计,对设计任务进行合理分配,并用系统工程的方法对设计进行管理。

第2章可编程逻辑器件2.1按结构的复杂程度分类、按互连结构分类、按可编程特性分类、按可编程器件的编程元件分类2.2主动串行配置式、主动并行配置模式、外设配置模式、从动串行配置模式、菊花链配置模式2.31、编程单元。

查找表型FPGA的编程单元为SRAM结构,可以无限次编程,但它属于易失性元件,掉电后芯片内的信息会丢失;而CPLD则采用EEPROM编程单元,不仅可无限次编程,且掉电后片内的信息不会丢失。

VHDL习题解答

V H D L习题解答(共15页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--VHDL 程序设计教程习题参考解答第一章习题参考答案1.什么是VHDLVHDL的实现有哪几种形态硬件描述语言(Hardware Description Language,HDL),顾名思义,是电子系统硬件行为描述、结构描述、数据流描述的语言。

VHDL语言的英文全名是Very High Speed Integrated Circuit Hardware Description Language,即超高速集成电路硬件描述语言。

2.简述VHDL的发展史。

1981年6月VHDL工作小组成立,提出了一个满足电子设计各种要求的能够作为工业标准的硬件描述语言。

1983年第三季度,由IBM公司、TI公司、Inter metrics公司签约,组成开发小组,工作任务是提出语言版本和开发软件环境。

1986年IEEE标准化组织开始工作,讨论VHDL语言标准,历时一年有余,于1987年12月通过标准审查,版本宣布实施,即IEEE STD 1076-1987。

1993年经过重新修订,发布版本,从而形成新的标准即IEEE STD 1076-1993。

2006年VHDL发布版本;2008年8月,VHDL 版本发布,解决了版本中发现的多个问题。

2009年1月,IEEE公布了VHDL 的标准版本,最新VHDL标准IEEE 1076-2008在2009年1月实施。

3. 详述VHDL设计IP模块的流程。

第1种设计形态,VHDL程序以IP模块的形态存在,VHDL-IP设计流程如图所示。

IP模块是与集成电路工艺无关的芯片设计方案,可以移植到不同的设计环境。

IP产品形态有规范,有IP包装规则和复用规则,是原生态的芯片硬件设计产品。

图 VHDL-IP设计流程4. 简答VHDL设计用FPGA实现的意义。

可编程器件FPGA具有容量大、密度高等特点,是科学实验、小批量生产、样机研制的载体。

夏宇闻-第三章-verilogHDL基本语法习题

夏宇闻-第三章-verilogHDL基本语法习题难理解的习题:7)请根据以下两条语句,从选项中找出正确答案。

7.1) reg [7:0] A;A=2'hFF;1) 8'b0000_0011 2) 8'h03 3) 8'b1111_1111 4) 8'b11111111标准答案:1)7.2) reg [7:0] B;B=8'bZ0;1) 8'0000_00Z0 2) 8'bZZZZ_00003) 8'b0000_ZZZ0 4) 8'bZZZZ_ZZZ0标准答案:4)8)请指出下⾯⼏条语句中变量的类型。

8.1) assign A=B;8.2) always #1Count=C+1;标准答案:A(wire) B(wire/reg) Count(reg) C(wire/reg)9)指出下⾯模块中Cin,Cout,C3,C5,的类型。

module FADD(A,B,Cin,Sum,Cout);input A, B, Cin;output Sum, Cout;....endmodulemodule Test;...FADDM(C1,C2,C3,C4,C5);...endmodule标准答案:Cin(wire) Cout(wire/reg) C3(wire/reg) C5(wire)10〕在下⼀个程序段中,当ADDRESS的值等于5'b0X000时,问casex执⾏完后A和B的值是多少。

A=0;B=0;casex(ADDRESS)5'b00: A=1;5'b10?00,5'b11?00:beginA=1;B=1;endendcase标准答案: A=1 and B=0; casex的⽤法9)指出下⾯模块中Cin,Cout,C3,C5,的类型。

module FADD(A,B,Cin,Sum,Cout);input A, B, Cin;output Sum, Cout;....endmodulemodule Test;...FADDM(C1,C2,C3,C4,C5);...endmodule标准答案:Cin(wire) Cout(wire/reg) C3(wire/reg) C5(wire)10〕在下⼀个程序段中,当ADDRESS的值等于5'b0X000时,问casex执⾏完后A和B的值是多少。

第3章 VHDL语言基础

Verilog:Cadence公司开发

ABEL(Advanced Boolean Hardware Description, 高级布尔方程语言) :Lattice公司 AHDL(Analog模拟硬件描述语言): Altera公司

第二节

VHDL的基本结构

通过与非门的逻辑描述,阐述VHDL的基本结构

第三节 VHDL结构体的子结构

4位计数器

module count4(out,reset,clk);

output[3:0] out;

input reset,clk; reg[3:0] out; always @(posedge clk) begin if(reset) out<=0; //同步复位 else end endmodule out<=out+1; //计数

Nand_2实体说明

结构体

BEGIN y <= NOT (a AND b);

END rtl;

1. 库说明

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL;

语法: library 库名

use 库名.程序包名.项目名:

库是用VHDL语言编写的源程序及其通过编译 的数据集合,它由各种程序包组成,程序包提供了 各种数据类型、函数的定义以及各种类型转换函数 及运算等,以供给设计者使用。

库序项库是用vhdl语言编写的源程序及其通过编译的数据集合它由各种程序包组成程序包提供了各种数据类型函数的定义以及各种类型转换函数及运算等以供给设计者使用

第三章 硬件描述语言HDL Hardware Description Language

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

单实例来介绍VHDL语言程序的一些基础知识,包括VHDL语言的组成,VHDL语言 的实体,VHDL语言的结构体和VHDL语言的描述风格等。

从而缩短设计周期,提高工作效率。

•系统可以现场编程,在线升级。

第二章

Altera公司的QuartusI【集成开发环境根据设计者的需求提供了一个完整的多平台 开发环境,其包含了整个可编程逻辑器件设计阶段的所有解决方案,提供了完整的图形用 户界面可以完成可编程片上系统的整个开发流程的各个阶段,包括输入、综合、仿真 等,在其中设计者可以方便的完成数字系统设计的全过程。本章将介绍如何在Quartus H

答案:

块语句、进程语句、子程序调用语句、信号赋值语句和元件例化语句。

5、VHDL有哪四种描述风格?

答案:

行为描述、数据流描述、结构描述以及由前三种组合的混合描述。

实验题

实验【一】编写一个实体

实验目的:熟悉实体的编写方法。

实验任务:在Quartus H+建立一个VHDL语言文件,编写一个实体,该实体要求如 下:

实体名:TEST o

输入端口:INPUTA,INPUTB,数据类型为BIT。

实验【二】编写一个结构体 实验目的:熟悉结构体的编写方法。

实验任务:在Quartus H+建立一个VHDL语言文件,编写一个结构体,该结构体要 求如下:

实体名:TEST o

结构体名:RTLo

没有功能描述语句。

答案:

ARCHITECTURE RTL OF TEST IS—结构体,名称为RTL,对应实体为TEST

源,不允许多重驱动。

6、VHDL语言的结构体的这些子结构互相之间是并行的

7、将VHDL语言的行为描述语句转换为门级描述由VHDL开发工具自动完成,是

VHDL语言综合器的任务。

8、数据流描述也称为RTL(寄存器传输级)描述方式,它类似于布尔方程,它既

表示某种行为,又隐含结构信息,主要指非结构化的并行语句描述。

填空题

1、一个标准的VHDL语言程序由库、实体和结构体组成。

2、个完整的VHDL语言描述是以对一个功能元件的完整描述为基础的

3、实体相当于电路图中一个器件符号。

4、端口说明(PORT)是对设计实体与外部接口的描述,也可以说是设计实体的外_

部引脚的名称,它为实体与外部环境的动态通信提供通道

5、缓冲(BUFFER)端口描述模式和INOUT双向模式的区别在于只能接受一个驱动

说的是Quartus11有完整版和Web Edtion两个版本,前者收费而后者收费,前者对于

后者而言只是多了很多内部集成的IP核,所以对于普通入门级用户而言直接下载免

费使用的后者即可。

2.1

图1.2QuartusII设计流程

第三章

VHDL语言的应用程序都是由几个固定的部分组成的,通常來说缺一不可,并且其

集成开发环境应用VHDL语言进行数字系统的开发。

注意:QuartusII集成开发环境的最新版是V12.0,但是在最新版中其去掉了直接输入波形

文件进行仿真的功能,取而代之的是使用ModelSim的仿真文件进行仿真,为了便于

读者快速上手学习,不增加难度,本书采用了依然可以使用波形文件进行仿真的V9.1

版本,读者可以在Altera的网站上免费下载到该版本的Web Edtion版;另外值得一

从而形成集成电子系统,不包含电子生产自动化。

EDA技术在电子系统设计中具有以下特点,所以的到了广泛应用:

•用软件的方式设计硬件。

•用软件方式设计的系统到硬件系统的转换是由相关软件自动完成的。

•在设计过程中可以用软件进行各种仿真进行验证。

•现代EDA工具具有高层综合和优化功能,能够在系统级进行综合、优化和方针,

EDA技术是现代电子信息工程领域中一门发展迅速的新技术。它是以计算机为工作

平台,其以EDA软件工具为开发环境,以硬件描述语言为主要表达方式,以大规模可 编程器件为设计载体,以ASIC、SOC、FPGA芯片为目标器件,以电子系统设计为应用

方向的电子产品自动化设计过程。

EDA技术有广义和狭义之分。

从广义来说EDA技术包括半导体工艺设计自动化、可编程器件设计自动化、电子 系统设计自动化、印制电路板设计自动化、仿真与测试故障诊断自动化等,例如PSPICE、

9、在结构描述中,元件间的连接是通过定义的端口界面来实现的。

10、结构描述的缺点是程序表示的是电路的述题

1、写出实体的结构。

答案:

ENTITY实体名IS

[GENER1C(类属表);]

[PORT(端口表);]

END ENTITY实体名;

2、在IEEE库中定义了哪四种VHDL语言的端口模式?

逻辑器件的种类和开发方法,使用EDA进行设计的流程等。

1.1

EDA是电子设计自动化(Electronic Design Automation)的缩写,是在20世纪60年代中期从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT) 和计算机辅助工程(CAE)的概念发展而来的。

1.1.1EDA技术简介

BEGIN

-无逻辑语句

END RT;

第一章

在EDA开发中,用户以计算机为工具,在对应的集成开发环境中,用硬件描述语 言完成设计文件,然后由计算机自动地完成逻辑编译、综合、优化、布局、布线和仿真 等工作,并且对于特定目标芯片进行适配编译、逻辑映射和编程下载。本章将介绍EDA

开发技术的基础知识,包括EDA的发展历史、可编程逻辑语言的分类和特点,可编程

EWB、MATLAB等计算机辅助分析CAA技术和PROTEL>ORCAD等印刷制版计算机 辅助设计等。

从狭义来说EDA技术就是电子设计自动化,即通过相关的开发软件,自动完成用 软件方式设计的电子系统到硬件系统的逻辑编译、化简、分割、综合、优化、以及布局 布线、逻辑仿真等工作,最终完成对于特定目标芯片的适配编译、逻辑映射、编程下载,

答案:

IN:输入。

OUT:输出。

INOUT:双向,输入输出。

BUFFER:缓冲,其实质也是双向的,但是只能接受一个驱动源。

3、写出结构体的结构。

答案:

ARCHITECTURE结构体名OF实体名IS

[说明语句]

BEGIN

[功能描述语句]

END ARCHITECTURE结构体名;

4、写出结构体的功能性描述语句的5种子结构。