veriloghdl试卷及答案

Verilog HDL试卷及答案教学提纲

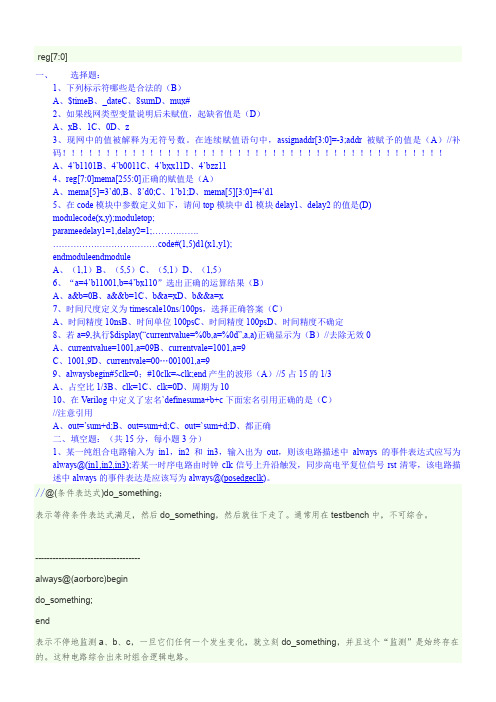

V e r i l o g H D L试卷及答案河北大学课程考核试卷2008——2009学年第一学期 2006级电气类专业(类)考核科目EDA技术课程类别必修考核类型考查考核方式闭卷类别 A一、选择题:1、下列标示符哪些是合法的(B )A、$timeB、_dateC、8sumD、mux#2、如果线网类型变量说明后未赋值,起缺省值是(D )A、xB、1C、0D、z3、现网中的值被解释为无符号数。

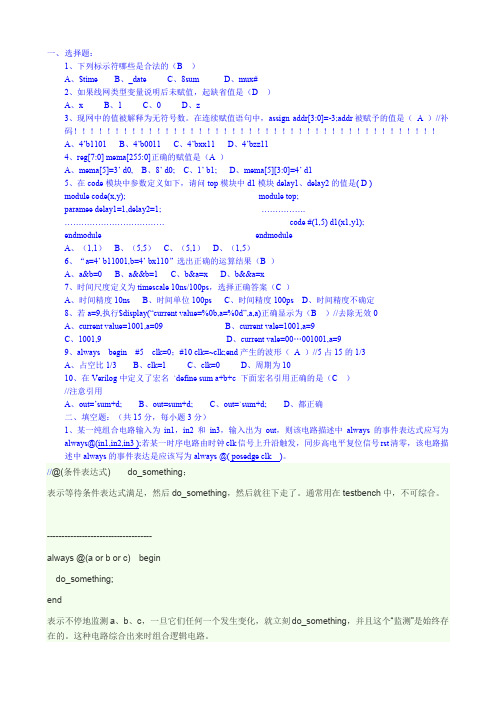

在连续赋值语句中,assign addr[3:0]=-3;addr被赋予的值是( A )A、4’b1101B、4’b0011C、4’bxx11D、4’bzz114、reg[7:0] mema[255:0]正确的赋值是(A )A、mema[5]=3’ d0,B、8’ d0;C、1’ b1;D、mema[5][3:0]=4’ d15、在code模块中参数定义如下,请问top模块中d1模块delay1、delay2的值是( D )module code(x,y); module top;paramee delay1=1,delay2=1; …………….……………………………… code #(1,5) d1(x1,y1);endmodule endmoduleA、(1,1)B、(5,5)C、(5,1)D、(1,5)6、“a=4’ b11001,b=4’ bx110”选出正确的运算结果(B )A、a&b=0B、a&&b=1C、b&a=xD、b&&a=x7、时间尺度定义为timescale 10ns/100ps,选择正确答案(C )A、时间精度10nsB、时间单位100psC、时间精度100psD、时间精度不确定8、若a=9,执行$display(“current value=%0b,a=%0d”,a,a)正确显示为(B )A、current value=1001,a=09B、current vale=1001,a=9C、1001,9D、current vale=00…001001,a=99、aways begin #5 clk=0;#10 clk=~clk;end产生的波形( A )A、占空比1/3B、clk=1C、clk=0D、周期为1010、在Verilog中定义了宏名 `define sum a+b+c 下面宏名引用正确的是(C )A、out=’sum+d;B、out=sum+d;C、out=`sum+d;D、都正确二、填空题:(共15分,每小题3分)1、某一纯组合电路输入为in1,in2和in3,输入出为out,则该电路描述中always的事件表达式应写为always@(in1,in2,in3 );若某一时序电路由时钟clk信号上升沿触发,同步高电平复位信号rst清零,该电路描述中always的事件表达是应该写为always @( posedge clk )。

veriloghdl答案

verilog-hdl答案第1章简介1.Verilog HDL是在哪一年首次被IEEE标准化的?Verilog HDL是在1995年首次被IEEE标准化的。

2.Verilog HDL支持哪三种基本描述方式Verilog HDL可采用三种不同方式或混合方式对设计建模。

这些方式包括:行为描述方式—使用过程化结构建模;数据流方式—使用连续赋值语句方式建模;结构化方式—使用门和模块实例语句描述建模3.可以使用Verilog HDL描述一个设计的时序吗?Verilog HDL可以清晰的建立时序模型,故可以使用Verilog HDL描述一个设计的时序。

4.语言中的什么特性能够用于描述参数化设计?在行为级描述中, Verilog HDL不仅能够在RT L级上进行设计描述,而且能够在体系结构级描述及其算法级行为上进行设计描述,而且能够使用门和模块实例化语句在结构级进行结构描述,这种特性可用于描述参数化设计。

5.能够使用Verilog HDL编写测试验证程序吗?能,可以编写testbench来对编写的程序进行验证。

6.Verilog HDL是由哪个公司最先开发的?Verilog HDL是由Gateway Design Automation公司最先开发的7.Verilog HDL中的两类主要数据类型是什么?线网数据类型和寄存器数据类型。

线网类型表示构件间的物理连线,而寄存器类型表示抽象的数据存储元件。

8.UDP代表什么?UDP代表用户定义原语9.写出两个开关级基本门的名称。

pmos nmos10.写出两个基本逻辑门的名称。

and or第2章 HDL指南1. 在数据流描述方式中使用什么语句描述一个设计?设计的数据流行为使用连续赋值语句进行描述2. 使用` t i m e s c a l e 编译器指令的目的是什么?举出一个实例。

使用编译指令将时间单位与物理时间相关联。

例如` timescale 1ns /100ps 此语句说明时延时间单位为1ns并且时间精度为100ps (时间精度是指所有的时延必须被限定在0.1ns内)3. 在过程赋值语句中可以定义哪两种时延?请举例详细说明。

VerilogHDL复习题

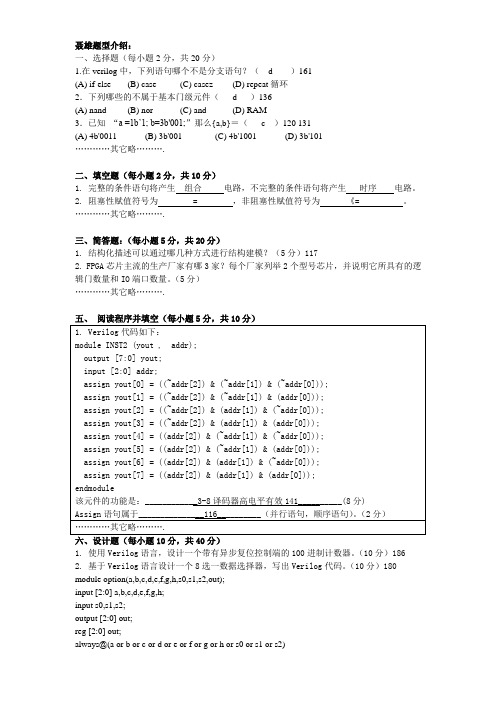

聂雄题型介绍:一、选择题(每小题2分,共20分)1.在verilog中,下列语句哪个不是分支语句?( d )161(A) if-else (B) case (C) casez (D) repeat循环2.下列哪些的不属于基本门级元件( d )136(A) nand (B) nor (C) and (D) RAM3.已知“a =1b’1; b=3b'001;”那么{a,b}=( c )120 131(A) 4b'0011 (B) 3b'001 (C) 4b'1001 (D) 3b'101…………其它略……….二、填空题(每小题2分,共10分)1. 完整的条件语句将产生组合电路,不完整的条件语句将产生时序电路。

2. 阻塞性赋值符号为 = ,非阻塞性赋值符号为《= 。

…………其它略……….三、简答题:(每小题5分,共20分)1. 结构化描述可以通过哪几种方式进行结构建模?(5分)1172. FPGA芯片主流的生产厂家有哪3家?每个厂家列举2个型号芯片,并说明它所具有的逻辑门数量和IO端口数量。

(5分)…………其它略……….五、阅读程序并填空(每小题5分,共10分)六、设计题(每小题10分,共40分)1. 使用Verilog语言,设计一个带有异步复位控制端的100进制计数器。

(10分)1862. 基于Verilog语言设计一个8选一数据选择器,写出Verilog代码。

(10分)180 module option(a,b,c,d,e,f,g,h,s0,s1,s2,out);input [2:0] a,b,c,d,e,f,g,h;input s0,s1,s2;output [2:0] out;reg [2:0] out;always@(a or b or c or d or e or f or g or h or s0 or s1 or s2)begincase({s0,s1,s2})3'd0 : out=a;3'd1 : out=b;3'd2 : out=c;3'd3 : out=d;3'd4 : out=e;3'd5 : out=f;3'd6 : out=g;3'd7 : out=h;endcase endendmodule…………其它略……….网上试题:填空:1.已知x=4’b1001,y=4’0110,则 x 的 4 位补码为4’b1111,而 y 的 4 位的补码为4’b0110?2.在 case 语句中至少要有一条 default 语句。

VerilogHDL复习题与答案

VerilogHDL硬件描述语言复习一、1. Verilog HDL 是在哪一年首次被I E E E标准化的答:Verilog HDL是在1995年首次被IEEE标准化的..2. Verilog HDL支持哪三种基本描述方式答:Verilog HDL可采用三种不同方式或混合方式对设计建模..这些方式包括:行为描述方式—使用过程化结构建模;数据流方式—使用连续赋值语句方式建模;结构化方式—使用门和模块实例语句描述建模3. Verilog HDL 是由哪个公司最先开发的答:Verilog HDL是由Gateway Design Automation公司最先开发的4. Verilog HDL中的两类主要数据类型什么答:线网数据类型和寄存器数据类型..线网类型表示构件间的物理连线; 而寄存器类型表示抽象的数据存储元件..5. U D P代表什么答:UDP代表用户定义原语6. 写出两个开关级基本门的名称..答:pmos nmos7.写出两个基本逻辑门的名称..答:and or8.在数据流描述方式中使用什么语句描述一个设计答:设计的数据流行为使用连续赋值语句进行描述9. 采用结构描述方式描述1位全加器..答:module full_adda;b;cin;s;co;input a;b;cin;output s;co;wire S1;T1;T2;T3;xorX1S1;a;b;X2s;S1;cin;andA1T3;a;b;A2T2;b;cin;A3T1;a;cin;orO1co;T1;T2;T3;endmodule10. i n i t i a l语句与always 语句的关键区别是什么答: 1 initial语句:此语句只执行一次..2 always语句:此语句总是循环执行; 或者说此语句重复执行..11.采用数据流方式描述2 - 4译码器..答:'timescale 1ns/nsmodule Decoder2×4A;B;EN;Z;input A;B;EN;output 0:3Z;wire abar;Bbar;assign #1 Abar=~A;assign #1 Bbar=~B;assign #2 Z0=~Abar&Bbar&EN;assign #2 Z1=~Abar&B&EN;assign #2 Z2=~A&Bbar&EN;assign #2 Z3=~A&B&EN;endmodule1 2. 找出下面连续赋值语句的错误..assign Reset=#2 Sel^WriteBus;答:不符合连续赋值语句的语法;应该为:assign #2 Reset = ^ WriteBus;二、1. 下列标识符哪些合法;哪些非法C O u n T; 1_2 M a n y; \**1; R e a l ; \wait; Initial答:COunT合法;1_2 Many非法;\**1;Real 非法;\wait合法;Initial合法2. 在Verilog HDL中是否有布尔类型答:没有3. 如果线网类型变量说明后未赋值;其缺省值为多少答:z4. Verilog HDL 允许没有显式说明的线网类型..如果是这样;怎样决定线网类型答:在Verilog HDL 中;有可能不必声明某种线网类型..在这样的情况下;缺省线网类型为1位线网..5.下面的说明错在哪里i n t e g e r 0:3 R i p p l e;答:应该是integer Ripple 0:36. Verilog HDL有哪几大类数据类型答:verilog hdl 有两大类数据类型:线网类型和寄存器类型..7.Verilog HDL有哪几种寄存器类型答:有五种不同的寄存器类型:reg、integer、time、real、realtime..三、1. 假定长度为6 4个字的存储器; 每个字8位;编写Verilog 代码;按逆序交换存储器的内容..即将第0个字与第6 3个字交换;第1个字与第6 2个字交换;依此类推..答:reg 7:0 mem 63:0;integer i = 0;reg 7:0 temp;whilei < 32begintemp = memi;memi = mem63 - i;mem63 - i = temp;i = i + 1;end2. 假定3 2位总线A d d re s s _ B u s; 编写一个表达式;计算从第11位到第2 0位的归约与非.. 答:~& addressBus20:113. 假定一条总线C o n t ro l _ B u s 1 5 : 0 ;编写赋值语句将总线分为两条总线:A b u s 0 : 9 和B b u s 6 : 1 ..答:Abus = ControlBus9:0;Bbus = ControlBus15:10;4. 编写一个表达式;执行算术移位;将Qparity 中包含的8位有符号数算术移位..答:{Qparity7-i:0; Qparity7:8-i}//左移;i表示移的位数{Qparityi-1:0; Qparity7: i}//右移;i表示移的位数5.使用条件操作符; 编写赋值语句选择N e x t S t a t e的值..如果C u rre n t S t a t e的值为R E S E T; 那么N e x t S t a t e的值为G O;如果C u rre n t S t a t e的值为G O;则N e x t S t a t e 的值为B U S Y;如果C u rre n t S t a t e的值为B U S Y;则N e x t S t a t e的值为R E S E T..答:NextState = CurrentState == RESET Go : CurrentState == Go BUSY : RESET6. 如何从标量变量A;B;C和D中产生总线B u s Q0:3 如何从两条总线B u s A 0 : 3 和B u s Y 2 0 : 1 5 形成新的总线B u s R 1 0 : 1答:BusQ3:0 = {D; C; B; A}BusR10:1 = {BusY20:15; BusA3:0}四、1、Verilig HDL提供的内置基本门分为哪几类1 多输入门、2 多输出门、3 三态门2、多输入门与多输出门的区别在哪里答:多输入门:and nand nor or xor xnor 这些逻辑门只有单个输出; 1个或多个输入第一个端口是输出;其它端口是输入..多输出门有:buf; not 这些门都只有单个输入;一个或多个输出最后的端口是输入端口;其余的所有端口为输出端口..3、Verilog HDL内置的mos开关门有哪些答:cmos; nmos; pmos; rcmos; rnmos; rpmos4、门时延值的组成有哪几个值答:1 上升时延2 下降时延3 关断时延5. Verilig HDL提供的内置基本门分为哪几类答:1 多输入门2 多输出门 3 三态门4 上拉、下拉电阻5 MOS开关6 双向开关6.假定一条总线Control_Bus7:0;编写赋值语句将总线分为两条总线:Abus 0:2和Bbus 4 : 1 ..答:Abus=ControlBus2:0;Bbus=ControlBus15:12;7. 编写一个表达式;执行算术移位;将Qparity 中包含的8位有符号数算术左移3位..答:{Qparity4:0; Qparity7:5}8.要求采用数据流方式设计一个半加器;写出完整的Verilig HDL设计模块..答:module half_addSum; Cout;A; B;input A; B;output Sum; Cout;assign Sum=A^B;assign Cout=A&B;endmodule五、1、操作符有按操作数个数分为3 种类型;其中三目操作符有 2 个操作符和 3 个操作数..2、关键字全是小写;标识符的首字符必须是字母或下划线..3、数字A=5’b011 的表示z ..设B=5’b101x1;C=5’b01x11;则操作运算F=B+C的结果F= 5'bxxxxx ..4、VerilogHDL中保存字符串“Hello”需要 5 位..5、声明reg 7:0data4:0表示5 个8 位的存储单元..6、module testq;clk;crt;output q;reg q;Input clk;crt;always @posedge clkbeginifcrt==1q=~q;endendmodule7、数据流建模的主要语法结构是assign LHS_target = RHS_expression; 语句;采用assign 关键字开始..8、线网赋值延迟可以通过普通赋值延迟; 隐式连续赋值延迟和线网声明延迟三种方法来实现..9、模型引用时;要指定实例名;但硬件和用户定义原语例外..10、语句assign #2:3:4;5:6:7portout;clk;in中的典型关断延迟是 4 ;最大关断延时是7 ..11、VerilogHDL语言可以从四个不同的抽象层次描述电路;这四层是开关级、门级、寄存器传送级、算法级12、结构化建模的主要语句是内置门原语和用户定义原语..六、1.门级建模的类型有:Aor和AND BOR和andCand和or DA、B、C都正确 C2.VerilogHDL使用的是逻辑是:A二值逻辑B四值逻辑C三值逻辑D八种强度 B3.不属于寄存器类型的是:Ainteger BregCwand Dtime C4.VerilogHDL语言中;标识符的作用范围是:A本模块B外部模块C所有模块D全局模块 A5.具有多个输出端口的门是:Aand BorCnor Dnot D七、1、语句内部时延与语句前时延效果是否一样答:不一样2、当时延表达式为负数时;时延值是如何处理得到答:取绝对值3、VeriligHDL有几种循环语句分别采用关键字是什么答:总共有四种循环语句;分别采用forever、repeat、while、for..八、1.VerilogHDL语言和C语言的结构化语句有何不同答:1.Verilog HDL是在C语言的基础上发展起来的;保留了C语言的结构特点..2.C语言由函数组成;Verilog由模块module组成3.C语言通过函数名及其端口变量实现调用;Verilog也通过模块名和端口变量实现调用4.C语言有主函数main;Verilog的个module均等价;但必有一个顶层模块;包含芯片系统与外界的所有I/O信号5.C语言是顺序执行;而Verilog的所有module均并发执行6.C 语言与Verilog语法相似..2、VerilogHDL语言的操作符类型有哪些其数据流建模采用什么来描述设计吗答:算术、逻辑、关系、等价、按位、缩减、移位、拼接、条件数据流建模采用算术与逻辑来描述设计3、VerilogHDL语言的优点是什么答:Verilog HDL语言的优势:由于它在其门级描述的底层;也就是晶体管开关的描述方面比VHDL等各种其它的HDL语言有更强的功能..所以在复杂数字逻辑电路和系统的设计仿真时更有优势;描述的设计思想、电路结构和逻辑关系清晰明了;并且设计语言简练、易学易用;其模块化分层结构在大规模设计时更能体现出优势..因此可以看出;Verilog HDL语言在EDA设计中相对与其他的各种硬件描述语言更有优势..4、下列例子中;b;c;d的最终值分别是什么initialbeginb=1’b1;c=1’b0;#10 b=1’b0;endinitialbegind=#25{b|c};end答:b=1'b0、c=1'b0、d=1'b05.一位全减器模块wsub具有三个一位输入:x;y和z前面的借位;两个一位的输出D差和B借位..计算D和B的逻辑等式如下所示:..D..yx=++..+..xyzzzxyyzx..+=B.+yzyzxx写出VerilogHDL数据流描述的该全减器wsub..答: module wsubD;B;x;y;xinput x;y;z;output D;B;assign D=~x*~y*~z+~x*y*~z+x*~y*~Z+x*y*z;assign B=~x*y+~x*z+y*z;endmodule。

HDL语言应用与设计试卷A卷(附答案)

中国矿业大学2010~2011学年第 二 学期 《HDL 语言应用与设计 》试卷(A )卷 考试时间:100 分钟 考试方式:闭卷学院_________班级_____________姓名 ___________学号____________一、综合程序设计题(100分)(1)请简答或画出基于verilog HDL 的数字系统设计流程(10分) (2)写出下图所示3选1的多路选择器的verilog 程序实现(行为描述方式)(10分)(3)写出一位全加器的UDP 描述(15分)(4)请编写5分频的Verilog 程序模块。

其中模块输入信号为:clk_in,reset(复位信号,低电平有效) 输出信号为:clk_out 。

(要求:使用行为描述方式)(15分)。

(5)请用循环语句实现一个从t=1000ns 时刻(假定一个仿真时间单位为1ns )开始的 周期为100个仿真时间单位的时钟信号产生模块(10分)。

(6)编写一位全加器的verilog 的结构描述程序(15分)(7) 请写一个用于比较两个整数的大小的比较器程序(用Verilog 函数实现)(10分)(8)请给出如下图所示的一个4位移位寄存器结构的Verilog 结构描述程序(这个移位寄存器是由四个D 触发器(U1、U2、U3和U4)构成的。

其中seri_in 是这个移位寄存器的串行输入;clk 为移位时钟脉冲输入;clrb 为清零控制信号输入;Q[0] ~Q[3] 则是移位寄存器的并行输出)(15分)注意:模块调用时端口对应方式要求使用端口位置关联方式。

Q[3]Q[2]Q[1]Q[0](1)(2)module sel_from_three(q,sela,selb,a,b,c );input sela,selb,a,b,c;output q;reg q;always @(sela or selb or a or b or c)beginif (sela) q = a;else if (selb) q = b;else q = c;endendmoduleprimitive carry(cout,cin,a,b );output cout;input a ,b ,cin;table //cout 对应的table表项//cin a b :cout0 0 0 :0;0 0 1 :0;0 1 0 :0;0 1 1 :1:1 0 0 :0:1 0 1 :1;1 1 0 :1;1 1 1 :1;endtableendprimitiveprimitive summ(sum,cin,a,b );output sum;input a ,b ,cin;table //sum对应的table表项//cin a b :sum0 0 0 :0;0 0 1 :1;0 1 0 :1;0 1 1 :0:1 0 0 :1:1 0 1 :0;1 1 0 :0;1 1 1 :1;endtableendprimitive(4)module div(clk_in,reset,clk_out);parameter bitsize=3;parameter L=4;input clk_in,reset;output clk_out;reg [bitsize:1] count;reg clk_out;always @(posedge clk_in) beginif(!reset)count=0;elsebeginif(count<(L))count=count+1;elsecount=0;endclk_out=count[bitsize];endendmodule(5)module clk_gen(clk);output clk;initialbeginclk = 0;#1000;forever#50 clk = ~clk;//被指定循环执行的语句endendmodule(6)module full_adder (c_out,s_out,a_in,b_in,c_in );output c_out,s_out;input a_in,b_in,c_in;wire w1,w2,w3;parameter AND_DELAY=2;parameter OR_DELAY=2;parameter XOR_DELAY=4;//元件实例语句and #AND_DELAY A1 ( w1,a_in,b_in );and #AND_DELAY A2 ( w2,b_in,c_in );and #AND_DELAY A3 ( w3,c_in,a_in );or #OR_DELAY O1 ( cout,w1,w2,w3 );xor #XOR_DELAY X1 (s_out,a_in,b_in,c_in );endmodule(7)function compare_2;input a,b;reg result_2;beginassign result_2=(a>=b)?1:0; compare_2=result;endendfunction(8)module shifter (seri_in,clk,clrb,Q );input seri_in,clk,clrb;output [3:0] Q;// 模块实例语句,对D触发器模块进行调用d_flop U1 (Q[0],seri_in,clrb,clk ) ,U2 (Q[1],Q[0],clrb,clk ) ,U3 (Q[2],Q[1],clrb,clk ) ,U4 (Q[3],Q[2],clrb,clk ) ;endmodule。

最新Verilog-HDL考核试卷一及答案资料

河北大学课程考核试卷2008 —— 2009学年第一学期2006级电气类专业(类)考核科目EDA技术课程类别必修考核类型考查考核方式闭卷类别A 选择题:1、下列标示符哪些是合法的(B )A、$timeB、_dateC、8sumD、mux#2、如果线网类型变量说明后未赋值,起缺省值是(D )A、xB、1C、0D、z3、现网中的值被解释为无符号数。

在连续赋值语句中,assign addr[3:0]=-3;addr被赋予的值是(A)A、4'1101B、4'0011C、4'bxx11D、4'bzz114、r eg[7:0] mema[255:0]正确的赋值是(A)A、mema[5]=3 'd0,B、8'd0; C 1'b1; D、mema[5][3:0]=4 'd15、在code模块中参数定义如下,请问top模块中d1模块delay1、delay2的值是(D )module code(x,y); module top;paramee delay1=1,delay2=1; ............ ......................................... code #(1,5) d1(x1,y1);en dmodule en dmoduleA、(1,1)B、(5,5) C (5,1)D、(1,5)6、“a=4‘ b11001,b=4 ' bx110”选出正确的运算结果(B )A、a&b=0B、a&&b=1C、b&a=xD、b&&a=x7、时间尺度定义为timescale 10ns/100ps,选择正确答案(C )A、时间精度10nsB、时间单位100psC、时间精度100psD、时间精度不确定8、若a=9,执行$display(“urrent value=%0b,a=%0d ",a,a)正确显示为(B )A、current value=1001,a=09B、current vale=1001,a=9C 1001,9 D、current vale=00 …001001,a=99、aways begin #5 clk=0; #10 clk=~clk;end 产生的波形(A )A、占空比1/3 B clk=1 C、clk=0 D、周期为1010、在Verilog中定义了宏名'define sum a+b+c下面宏名引用正确的是( C )A、out= 'um+d;B、out=sum+d;C、out='sum+d;D、都正确二、填空题:(共15分,每小题3分)1、某一纯组合电路输入为in1, in2和in3,输入出为out,则该电路描述中always的事件表达式应写为always@(in1,in2,in3 );若某一时序电路由时钟clk信号上升沿触发,同步高电平复位信号rst 清零,该电路描述中always的事件表达是应该写为always@( posedge clk )。

VerilogHDL试卷及答案

一、选择题:1、下列标示符哪些是合法的(B )A、$timeB、_dateC、8sumD、mux#2、如果线网类型变量说明后未赋值,起缺省值是(D )A、xB、1C、0D、z3、现网中的值被解释为无符号数。

在连续赋值语句中,assign addr[3:0]=-3;addr被赋予的值是(A )//补码!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!A、4’b1101B、4’b0011C、4’bxx11D、4’bzz114、reg[7:0] mema[255:0]正确的赋值是(A )A、mema[5]=3’ d0,B、8’ d0;C、1’ b1;D、mema[5][3:0]=4’ d15、在code模块中参数定义如下,请问top模块中d1模块delay1、delay2的值是( D )module code(x,y); module top;paramee delay1=1,delay2=1; …………….………………………………code #(1,5) d1(x1,y1);endmodule endmoduleA、(1,1)B、(5,5)C、(5,1)D、(1,5)6、“a=4’ b11001,b=4’ bx110”选出正确的运算结果(B )A、a&b=0B、a&&b=1C、b&a=xD、b&&a=x7、时间尺度定义为timescale 10ns/100ps,选择正确答案(C )A、时间精度10nsB、时间单位100psC、时间精度100psD、时间精度不确定8、若a=9,执行$display(“current value=%0b,a=%0d”,a,a)正确显示为(B )//去除无效0A、current value=1001,a=09B、current vale=1001,a=9C、1001,9D、current vale=00…001001,a=99、always begin #5 clk=0;#10 clk=~clk;end产生的波形(A )//5占15的1/3A、占空比1/3B、clk=1C、clk=0D、周期为1010、在Verilog中定义了宏名`define sum a+b+c 下面宏名引用正确的是(C )//注意引用A、out=’sum+d;B、out=sum+d;C、out=`sum+d;D、都正确二、填空题:(共15分,每小题3分)1、某一纯组合电路输入为in1,in2和in3,输入出为out,则该电路描述中always的事件表达式应写为always@(in1,in2,in3 );若某一时序电路由时钟clk信号上升沿触发,同步高电平复位信号rst清零,该电路描述中always的事件表达是应该写为always @( posedge clk )。

EDA verilog hdl考试题和答案

EDA verilog hdl考试题和答案一、选择题(每题2分,共20分)1. 在Verilog HDL中,以下哪个关键字用于定义模块?A. moduleB. endmoduleC. inputD. output答案:A2. Verilog HDL中,以下哪个操作符用于按位取反?A. ~B. !C. ^D. &答案:A3. 在Verilog HDL中,以下哪个关键字用于定义组合逻辑?A. alwaysB. initialC. always_combD. always_seq答案:C4. 以下哪个是Verilog HDL中合法的标识符?A. 2variableB. variable2C. variable$2D. variable_2答案:B5. 在Verilog HDL中,以下哪个关键字用于定义信号的初始值?A. initialB. alwaysC. assignD. defparam答案:A6. 在Verilog HDL中,以下哪个关键字用于定义参数?A. parameterB. defparamC. localparamD. specparam答案:A7. 在Verilog HDL中,以下哪个关键字用于定义一个始终块,该块在仿真开始时执行一次?A. alwaysB. initialC. always_combD. always_ff答案:B8. 在Verilog HDL中,以下哪个操作符用于逻辑与?A. &&B. &C. ||D. |答案:B9. 在Verilog HDL中,以下哪个关键字用于定义一个始终块,该块在信号变化时触发?A. alwaysB. initialC. always_combD. always_ff答案:A10. 在Verilog HDL中,以下哪个关键字用于定义一个三态输出?A. outputB. inoutC. triD. wire答案:C二、填空题(每题2分,共20分)1. 在Verilog HDL中,____关键字用于定义一个始终块,该块在信号的边沿触发时执行。

VerilogHDL复习题与答案

VerilogHDL硬件描述语言复习一、1. Verilog HDL 是在哪一年首次被I E E E标准化的?答:Verilog HDL是在1995年首次被IEEE标准化的。

2. Verilog HDL支持哪三种基本描述方式?答:Verilog HDL可采用三种不同方式或混合方式对设计建模。

这些方式包括:行为描述方式—使用过程化结构建模;数据流方式—使用连续赋值语句方式建模;结构化方式—使用门和模块实例语句描述建模3. Verilog HDL 是由哪个公司最先开发的?答:Verilog HDL是由Gateway Design Automation公司最先开发的4. Verilog HDL中的两类主要数据类型什么?答:线网数据类型和寄存器数据类型。

线网类型表示构件间的物理连线,而寄存器类型表示抽象的数据存储元件。

5. U D P代表什么?答:UDP代表用户定义原语6. 写出两个开关级基本门的名称。

答:pmos nmos7.写出两个基本逻辑门的名称。

答:and or8.在数据流描述方式中使用什么语句描述一个设计?答:设计的数据流行为使用连续赋值语句进行描述9. 采用结构描述方式描述1位全加器。

答:module full_add(a,b,cin,s,co);input a,b,cin;output s,co;wire S1,T1,T2,T3;xorX1(S1,a,b),X2(s,S1,cin);andA1(T3,a,b),A2(T2,b,cin),A3(T1,a,cin);orO1(co,T1,T2,T3);endmodule10. i n i t i a l语句与always 语句的关键区别是什么?答: 1) initial语句:此语句只执行一次。

2) always语句:此语句总是循环执行, 或者说此语句重复执行。

11.采用数据流方式描述2 - 4译码器。

答:'timescale 1ns/nsmodule Decoder2×4(A,B,EN,Z);input A,B,EN;output [0:3]Z;wire abar,Bbar;assign #1 Abar=~A;assign #1 Bbar=~B;assign #2 Z[0]=~(Abar&Bbar&EN);assign #2 Z[1]=~(Abar&B&EN);assign #2 Z[2]=~(A&Bbar&EN);assign #2 Z[3]=~(A&B&EN);endmodule1 2. 找出下面连续赋值语句的错误。

中南大学EDA VerilogHDL试题(附答案)

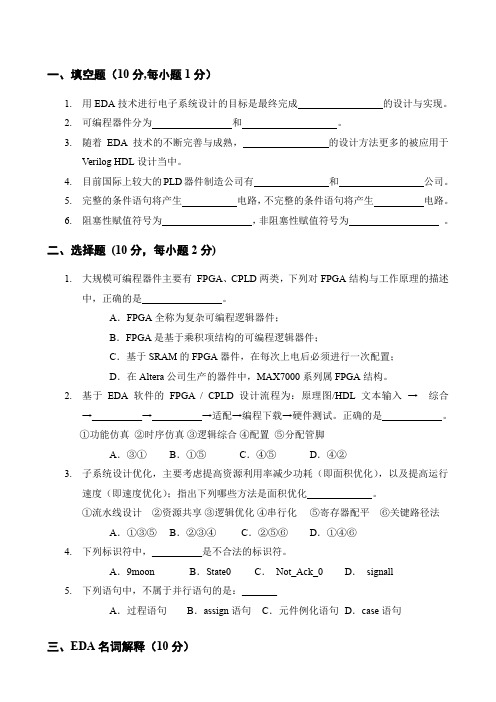

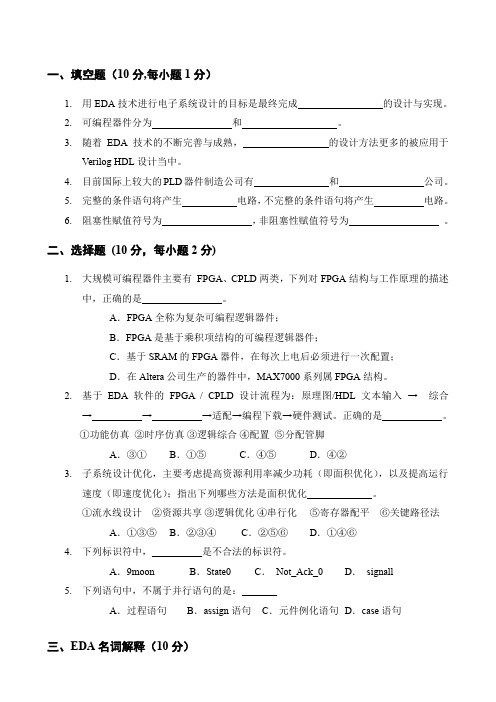

一、填空题(10分,每小题1分)1.用EDA技术进行电子系统设计的目标是最终完成的设计与实现。

2.可编程器件分为和。

3.随着EDA技术的不断完善与成熟,的设计方法更多的被应用于Verilog HDL设计当中。

4.目前国际上较大的PLD器件制造公司有和公司。

5.完整的条件语句将产生电路,不完整的条件语句将产生电路。

6.阻塞性赋值符号为,非阻塞性赋值符号为。

二、选择题(10分,每小题2分)1.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是。

A.FPGA全称为复杂可编程逻辑器件;B.FPGA是基于乘积项结构的可编程逻辑器件;C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置;D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。

2.基于EDA软件的FPGA / CPLD设计流程为:原理图/HDL文本输入→综合→_____→→适配→编程下载→硬件测试。

正确的是。

①功能仿真②时序仿真③逻辑综合④配置⑤分配管脚A.③①B.①⑤C.④⑤D.④②3.子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);指出下列哪些方法是面积优化。

①流水线设计②资源共享③逻辑优化④串行化⑤寄存器配平⑥关键路径法A.①③⑤B.②③④C.②⑤⑥D.①④⑥4.下列标识符中,__________是不合法的标识符。

A.9moon B.State0 C.Not_Ack_0 D.signall5.下列语句中,不属于并行语句的是:_______A.过程语句B.assign语句C.元件例化语句D.case语句三、EDA名词解释(10分)写出下列缩写的中文含义:ASIC:RTL:FPGA:SOPC:CPLD:LPM:EDA:IEEE:IP:ISP:四、简答题(10分)1、简要说明仿真时阻塞赋值与非阻塞赋值的区别(本题4分)。

答:非阻塞(non-blocking)赋值方式 ( b<= a):b的值被赋成新值a的操作, 并不是立刻完成的,而是在块结束时才完成;块内的多条赋值语句在块结束时同时赋值;硬件有对应的电路。

Verilog HDL复习题

聂雄题型介绍:一、选择题(每小题2分,共20分)1.在verilog中,下列语句哪个不是分支语句?( d )161(A) if-else (B) case (C) casez (D) repeat循环2.下列哪些的不属于基本门级元件( d )136(A) nand (B) nor (C) and (D) RAM3.已知“a =1b’1; b=3b'001;”那么{a,b}=( c )120 131(A) 4b'0011 (B) 3b'001 (C) 4b'1001 (D) 3b'101…………其它略……….二、填空题(每小题2分,共10分)1. 完整的条件语句将产生组合电路,不完整的条件语句将产生时序电路。

2. 阻塞性赋值符号为 = ,非阻塞性赋值符号为《= 。

…………其它略……….三、简答题:(每小题5分,共20分)1. 结构化描述可以通过哪几种方式进行结构建模?(5分)1172. FPGA芯片主流的生产厂家有哪3家?每个厂家列举2个型号芯片,并说明它所具有的逻辑门数量和IO端口数量。

(5分)…………其它略……….六、设计题(每小题10分,共40分)1. 使用Verilog语言,设计一个带有异步复位控制端的100进制计数器。

(10分)1862. 基于Verilog语言设计一个8选一数据选择器,写出Verilog代码。

(10分)180 module option(a,b,c,d,e,f,g,h,s0,s1,s2,out);input [2:0] a,b,c,d,e,f,g,h;input s0,s1,s2;output [2:0] out;reg [2:0] out;always@(a or b or c or d or e or f or g or h or s0 or s1 or s2)begincase({s0,s1,s2})3'd0 : out=a;3'd1 : out=b;3'd2 : out=c;3'd3 : out=d;3'd4 : out=e;3'd5 : out=f;3'd6 : out=g;3'd7 : out=h;endcase endendmodule…………其它略……….网上试题:填空:1.已知x=4’b1001,y=4’0110,则 x 的 4 位补码为4’b1111,而 y 的 4 位的补码为4’b0110?2.在 case 语句中至少要有一条 default 语句。

最新Verilog-HDL试卷及答案

河北大学课程考核试卷2008 —— 2009学年第一学期2006级电气类专业(类)考核科目EDA技术课程类别必修考核类型考查考核方式闭卷类别A 选择题:1、下列标示符哪些是合法的(B )A、$timeB、_dateC、8sumD、mux#2、如果线网类型变量说明后未赋值,起缺省值是(D )A、xB、1C、0D、z3、现网中的值被解释为无符号数。

在连续赋值语句中,assign addr[3:0]=-3;addr被赋予的值是(A)A、4'1101B、4'0011C、4'bxx11D、4'bzz114、r eg[7:0] mema[255:0]正确的赋值是(A)A、mema[5]=3 'd0,B、8'd0; C 1'b1; D、mema[5][3:0]=4 'd15、在code模块中参数定义如下,请问top模块中d1模块delay1、delay2的值是(D )module code(x,y); module top;paramee delay1=1,delay2=1; ........... ......................................... code #(1,5) d1(x1,y1);en dmodule en dmoduleA、(1,1)B、(5,5) C (5,1)D、(1,5)6、“a=4‘ b11001,b=4 ' bx110”选出正确的运算结果(B )A、a&b=0B、a&&b=1C、b&a=xD、b&&a=x7、时间尺度定义为timescale 10ns/100ps,选择正确答案(C )A、时间精度10nsB、时间单位100psC、时间精度100psD、时间精度不确定8、若a=9,执行$display(“urrent value=%0b,a=%0d ",a,a)正确显示为(B )A、current value=1001,a=09B、current vale=1001,a=9C 1001,9 D、current vale=00 …001001,a=99、a ways begin #5 clk=0; #10 clk=~clk;end 产生的波形(A )A、占空比1/3 B clk=1 C、clk=0 D、周期为1010、在Verilog中定义了宏名'define sum a+b+c下面宏名引用正确的是( C )A、out= 'um+d;B、out=sum+d;C、out='sum+d;D、都正确二、填空题:(共15分,每小题3分)1、某一纯组合电路输入为in1, in2和in3,输入出为out,则该电路描述中always的事件表达式应写为always@(in1,in2,in3 );若某一时序电路由时钟clk信号上升沿触发,同步高电平复位信号rst 清零,该电路描述中always的事件表达是应该写为always@( posedge clk )。

verilog hdl答案

第1章简介1.Verilog HDL是在哪一年首次被IEEE标准化的?Verilog HDL是在1995年首次被IEEE标准化的。

2.Verilog HDL支持哪三种基本描述方式Verilog HDL可采用三种不同方式或混合方式对设计建模。

这些方式包括:行为描述方式—使用过程化结构建模;数据流方式—使用连续赋值语句方式建模;结构化方式—使用门和模块实例语句描述建模3.可以使用Verilog HDL描述一个设计的时序吗?Verilog HDL可以清晰的建立时序模型,故可以使用Verilog HDL描述一个设计的时序。

4.语言中的什么特性能够用于描述参数化设计?在行为级描述中, Verilog HDL不仅能够在RT L级上进行设计描述,而且能够在体系结构级描述及其算法级行为上进行设计描述,而且能够使用门和模块实例化语句在结构级进行结构描述,这种特性可用于描述参数化设计。

5.能够使用Verilog HDL编写测试验证程序吗?能,可以编写testbench来对编写的程序进行验证。

6.Verilog HDL是由哪个公司最先开发的?Verilog HDL是由Gateway Design Automation公司最先开发的7.Verilog HDL中的两类主要数据类型是什么?线网数据类型和寄存器数据类型。

线网类型表示构件间的物理连线,而寄存器类型表示抽象的数据存储元件。

8.UDP代表什么?UDP代表用户定义原语9.写出两个开关级基本门的名称。

pmos nmos10.写出两个基本逻辑门的名称。

and or第2章 HDL指南1. 在数据流描述方式中使用什么语句描述一个设计?设计的数据流行为使用连续赋值语句进行描述2. 使用` t i m e s c a l e 编译器指令的目的是什么?举出一个实例。

使用编译指令将时间单位与物理时间相关联。

例如` timescale 1ns /100ps 此语句说明时延时间单位为1ns并且时间精度为100ps (时间精度是指所有的时延必须被限定在0.1ns内)3. 在过程赋值语句中可以定义哪两种时延?请举例详细说明。

中南大学EDA VerilogHDL试题 附答案

一、填空题(10分,每小题1分)1.用EDA技术进行电子系统设计的目标是最终完成的设计与实现。

2.可编程器件分为和。

3.随着EDA技术的不断完善与成熟,的设计方法更多的被应用于Verilog HDL设计当中。

4.目前国际上较大的PLD器件制造公司有和公司。

5.完整的条件语句将产生电路,不完整的条件语句将产生电路。

6.阻塞性赋值符号为,非阻塞性赋值符号为。

二、选择题(10分,每小题2分)1.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是。

A.FPGA全称为复杂可编程逻辑器件;B.FPGA是基于乘积项结构的可编程逻辑器件;C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置;D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。

2.基于EDA软件的FPGA / CPLD设计流程为:原理图/HDL文本输入→综合→_____→→适配→编程下载→硬件测试。

正确的是。

①功能仿真②时序仿真③逻辑综合④配置⑤分配管脚A.③①B.①⑤C.④⑤D.④②3.子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);指出下列哪些方法是面积优化。

①流水线设计②资源共享③逻辑优化④串行化⑤寄存器配平⑥关键路径法A.①③⑤B.②③④C.②⑤⑥D.①④⑥4.下列标识符中,__________是不合法的标识符。

A.9moon B.State0 C.Not_Ack_0 D.signall5.下列语句中,不属于并行语句的是:_______A.过程语句B.assign语句C.元件例化语句D.case语句三、EDA名词解释(10分)写出下列缩写的中文含义:ASIC:RTL:FPGA:SOPC:CPLD:LPM:EDA:IEEE:IP:ISP:四、简答题(10分)1、简要说明仿真时阻塞赋值与非阻塞赋值的区别(本题4分)。

答:非阻塞(non-blocking)赋值方式 ( b<= a):b的值被赋成新值a的操作, 并不是立刻完成的,而是在块结束时才完成;块内的多条赋值语句在块结束时同时赋值;硬件有对应的电路。

verilog HDL期末考试

硬件语言与FPGA期末测试开课时间:2015~2016第2学期学生姓名:班级:学号:硬件语言与FPGA 期末测试第一题:计数器设计1.设计一个最基本的计数器,功能每个时钟上升沿实现加1的功能。

(工程名cnt1+学号后两位)(10)module cnt1_42(CLK,Q);input CLK;output[2:0] Q;reg[2:0] Q1;always@(posedge CLK)begin //实现0-4加法计数if(Q1<4)Q1<=Q1+1;elseQ1<=0;endassign Q=Q1;endmodule计数器1.rar2.对上诉计数器进行功能扩展,要求有复位、数据加载、加减计数选择功能(如有无法实现功能,会适当扣分)(20)module cnt1_42(CLK,RST,LOAD,CHNG,DOUT,COUT,DATA);input CLK,RST,LOAD,CHNG; //CLK为时钟信号,LOAD为数据加载使能,CHN为加减计数选择,COUT为进位DOUT为输出,DATA为数据加载,RST为复位input[2:0] DATA;output[2:0] DOUT;output COUT;reg[2:0] Q=0;reg COUT;always@(posedge CLK or negedge RST)beginif(!RST)Q<=0;else if(LOAD)Q=DATA;else if(CHNG)beginif(Q<4)Q<=Q+1;elseQ<=0;endelse beginif(Q>0)Q<=Q-1;elseQ<=0;endendalways@(Q)if(Q==3'b100)COUT=1;elseCOUT=0;assign DOUT=Q;endmodule计数器2.rar第二题:分频器设计设计一个奇数分频器,要求可以通过参数完成任意奇数分频。

veriloghdl数字设计与综合答案

veriloghdl数字设计与综合答案【篇一:verilog习题选答】txt>答:fpga中,由程序来转换为可烧录的二进制码。

ic设计中,主要是由design-compiler来实现。

2.能否说模块相当于电路图中的功能模块,端口相当于功能模块的 3.assign声明语句,实例元件,always块,这三类描述中哪一种直接与电路结构有关?4.由连续赋值语句(assign)赋值的变量能否是reg型的?答:赋值运算分为连续赋值和过程赋值两种。

(1)连续赋值连续赋值语句只能对线网型变量进行赋值,而不能对寄存器型变量进行赋值,基本的语法结构为:assign #(延时量) 线网型变量名 = 赋值表达式; 一个线网型变量一旦被连续赋值语句赋值后,赋值语句右端赋值表达式的值将持续对赋值变量产生连续驱动,只要右端表达式任一操作数的值发生变化,就会立即触发对赋值变量的更新操作。

(2)过程赋值过程赋值主要用于两种结构化模块(initial和always)中的赋值语句。

在过程块中只能使用过程赋值语句,不能在过程块中出现连续赋值语句,同时过程赋值语句也只能用在过程赋值模块中。

基本的语法结构为:被赋值变量赋值操作符赋值表达式,其中,赋值操作符是“=”或“=”,它分别代表了阻塞赋值和非阻塞赋值类型。

过程赋值语句只能对寄存器类型的变量进行赋值,经过赋值后,上面这些变量的值将保持不变,直到另一条赋值语句对变量重新赋值为止。

5.如果都不带时间延迟、阻塞和非阻塞赋值有何不同?说明它们的不同点?答:代码1:module test(a,b,c,d,y); //两个与逻辑,1个或逻辑input a,b,c,d;output y;reg y,tmp1,tmp2;always @(a or b or c or d)// y的值并不等于当前的tmp1,tmp2相或的值,而是等于上 begin一次运算时tmp1,tmp2相或的值。

相当于一个延迟,在第2 tmp1 = ab; 次always模块运行完后得到想要的y值tmp2 = cd;y = tmp1|tmp2;endendmodule代码2:基本与代码1一样,只是在always的敏感列表中加入了temp1,temp2module test(a,b,c,d,y);input a,b,c,d;output y;reg y,tmp1,tmp2;always @(a or b or c or d or tmp1 or tmp2)//与代码一不同,begintmp1 = ab;tmp2 = cd;y = tmp1|tmp2;endendmodule代码3:在代码2中加进参数j,来帮助判断always模块的运行次数:module test(a,b,c,d,y);input a,b,c,d;output y;reg y,tmp1,tmp2;reg [8:0]j=0;always @(a or b or c or d or tmp1 or tmp2)beginj = j + 1;#5 //这里加了一个延时,方便分析tmp1 = ab;延迟消失了。

(完整)Verilog_HDL试卷及答案,推荐文档.doc

河北大学课程考核试卷2008 —— 2009 学年第一学期2006 级电气类专业(类)考核科目 EDA 技术课程类别必修考核类型考查考核方式闭卷类别 A一、选择题:1、下列标示符哪些是合法的( B )A、 $timeB、 _dateC、 8sumD、 mux#2、如果线网类型变量说明后未赋值,起缺省值是( D )A、 xB、 1C、 0D、 z3、现网中的值被解释为无符号数。

在连续赋值语句中,assign addr[3:0]=-3;addr 被赋予的值是( A )A、 4’b1101B、 4’b0011C、 4’bxx11D、 4’bzz114、 reg[7:0] mema[255:0] 正确的赋值是( A )A、 mema[5]=3 ’d0,B、 8’d0;C、 1’b1;D、 mema[5][3:0]=4 ’d15、在 code 模块中参数定义如下,请问top 模块中 d1 模块 delay1、 delay2 的值是 ( D )module code(x,y); module top;paramee delay1=1,delay2=1; .code #(1,5) d1(x1,y1);endmodule endmoduleA、( 1,1)B、(5,5)C、( 5,1)D、( 1,5)6、“ a=4’b11001,b=4 ’bx110”选出正确的运算结果( B )A、 a&b=0B、a&&b=1C、b&a=xD、 b&&a=x7、时间尺度定义为timescale 10ns/100ps ,选择正确答案( C )A、时间精度 10nsB、时间单位 100psC、时间精度 100psD、时间精度不确定8、若 a=9,执行 $display( “current value=%0b,a=%0d ”,a,a)正确显示为( B )A、 current value=1001,a=09B、current vale=1001,a=9C、 1001,9D、 current vale=00 001001,a=99、 aways begin #5 clk=0; #10 clk=~clk;end 产生的波形( A )A、占空比 1/3B、 clk=1C、 clk=0D、周期为 1010、在 Verilog 中定义了宏名`define sum a+b+c 下面宏名引用正确的是( C )A、 out= ’sum+d;B、 out=sum+d;C、 out=`sum+d;D、都正确二、填空题:(共 15 分,每小题 3 分)1、某一纯组合电路输入为in1,in2 和 in3,输入出为 out ,则该电路描述中always 的事件表达式应写为always@(in1,in2,in3 ); 若某一时序电路由时钟clk 信号上升沿触发,同步高电平复位信号rst 清零,该电路描述中always 的事件表达是应该写为always @( posedge clk )。

Verilog_HDL试卷及答案

reg[7:0]一、选择题:1、下列标示符哪些是合法的(B)A、$timeB、_dateC、8sumD、mux#2、如果线网类型变量说明后未赋值,起缺省值是(D)A、xB、1C、0D、z3、现网中的值被解释为无符号数。

在连续赋值语句中,assignaddr[3:0]=-3;addr被赋予的值是(A)//补码!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!A、4’b1101B、4’b0011C、4’bxx11D、4’bzz114、reg[7:0]mema[255:0]正确的赋值是(A)A、mema[5]=3’d0,B、8’d0;C、1’b1;D、mema[5][3:0]=4’d15、在code模块中参数定义如下,请问top模块中d1模块delay1、delay2的值是(D)modulecode(x,y);moduletop;parameedelay1=1,delay2=1;…………….………………………………endmoduleendmoduleA、(1,1)B、(5,5)C、(5,1)D6、“a=4’b11001,b=4’bx110A、a&b=0B、a&&b=1C、b&a=xD、7、时间尺度定义为timescale10ns/100psA、时间精度10nsB、时间单位100psC、都正确in3,输入出为out,则该电路描述中always的事件表达式应写为always@(in1,in2,in3);若某一时序电路由时钟clk信号上升沿触发,同步高电平复位信号rst清零,该电路描述中always的事件表达是应该写为always@(posedgeclk)。

//@(条件表达式)do_something;表示等待条件表达式满足,然后do_something,然后就往下走了。

通常用在testbench中,不可综合。

------------------------------------always@(aorborc)begindo_something;end表示不停地监测a、b、c,一旦它们任何一个发生变化,就立刻do_something,并且这个“监测”是始终存在的。

Verilog_HDL试卷

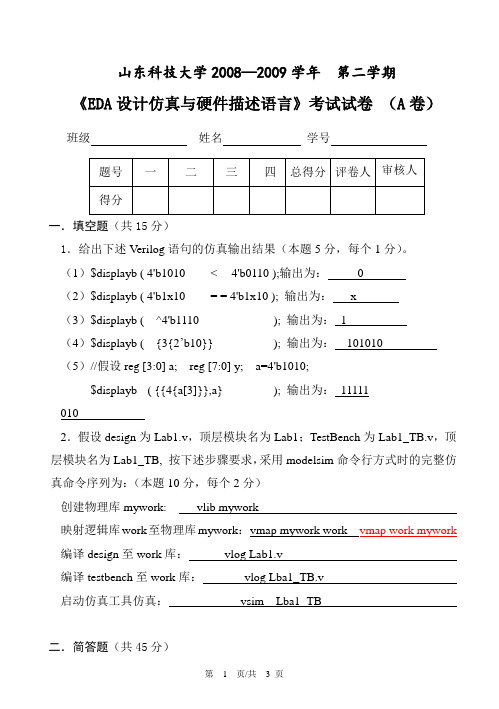

山东科技大学2008—2009学年第二学期《EDA设计仿真与硬件描述语言》考试试卷(A卷)班级姓名学号一.填空题(共15分)1.给出下述Verilog语句的仿真输出结果(本题5分,每个1分)。

(1)$displayb ( 4'b1010 < 4'b0110 );输出为:0(2)$displayb ( 4'b1x10 = = 4'b1x10 ); 输出为:x(3)$displayb ( ^4'b1110 ); 输出为: 1(4)$displayb ( {3{2’b10}} ); 输出为:101010(5)//假设reg [3:0] a; reg [7:0] y; a=4'b1010;$displayb ( {{4{a[3]}},a} ); 输出为:111110102.假设design为Lab1.v,顶层模块名为Lab1;TestBench为Lab1_TB.v,顶层模块名为Lab1_TB, 按下述步骤要求,采用modelsim命令行方式时的完整仿真命令序列为:(本题10分,每个2分)创建物理库mywork: vlib mywork映射逻辑库work至物理库mywork:vmap mywork work vmap work mywork 编译design至work库:vlog Lab1.v编译testbench至work库:vlog Lba1_TB.v启动仿真工具仿真:vsim Lba1_TB二.简答题(共45分)1.简述下述Verilog语句的含义(所有信号均为1bit位宽;有时序信息时请同时说明时序含义,若需要用式子表达,可用X(t)表达“t时刻时X的值”;可均从0时刻描述)(本题10分,每个2分)(1)assign #10 out = in1 & in2 ;out(10)=in1(10)&in2(10)(2)assign out = # 5 in1 | in2 ;out(5)=in1(0)&in2(0)(3)or #(1,2,3)or_inst(o,in1,in2);上升延时为1个单位,下降延时为2个单位,关断延时为3个单位,0=in1|in2;(4)`timescale 1ns / 100ps单位为纳秒,精度为100皮秒;(5)reg [7:0] led_out; 代码片段:led_out[7:0] <= {led_out[6:0],led_out[7]};实现循环左移功能;2. 假设design为Lab1.v,顶层模块名为Lab1;TestBench为Lab1_TB.v,顶层模块名为Lab1_TB,简述使用QuartusII工具的FPGA实现、验证操作步骤。

Verilog系统设计考试试卷与答案

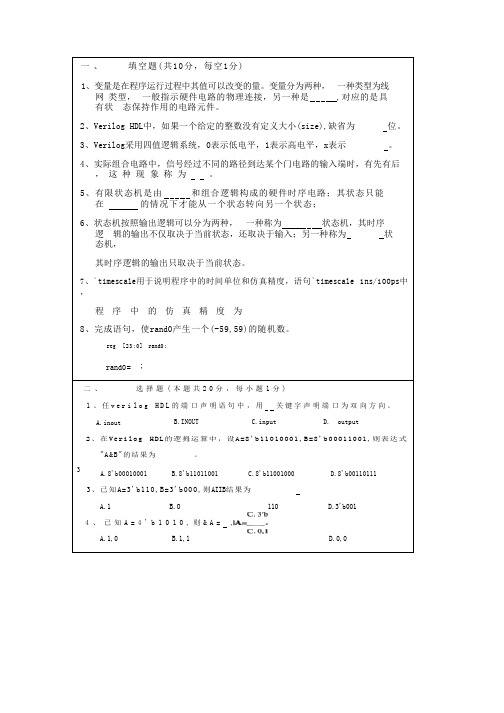

一、填空题(共10分,每空1分)1、变量是在程序运行过程中其值可以改变的量。

变量分为两种,一种类型为线网类型,一般指示硬件电路的物理连接,另一种是 ,对应的是具有状态保持作用的电路元件。

2、Verilog HDL中,如果一个给定的整数没有定义大小(size),缺省为位。

3、Verilog采用四值逻辑系统,0表示低电平,1表示高电平,x表示。

4、实际组合电路中,信号经过不同的路径到达某个门电路的输入端时,有先有后,这种现象称为。

5、有限状态机是由和组合逻辑构成的硬件时序电路;其状态只能在的情况下才能从一个状态转向另一个状态;6、状态机按照输出逻辑可以分为两种,一种称为状态机,其时序逻辑的输出不仅取决于当前状态,还取决于输入;另一种称为状态机,其时序逻辑的输出只取决于当前状态。

7、`timescale用于说明程序中的时间单位和仿真精度,语句`timescale 1ns/100ps中,程序中的仿真精度为8、完成语句,使rand0产生一个(-59,59)的随机数。

reg [23:0] rand0;rand0= ;二、选择题 ( 本题共 2 0 分,每小题 1 分 )1 、任v e r i l o g H D L 的端口声明语句中,用关键字声明端口为双向方向。

A.inoutB.INOUTC.inputD. output2、在V e r i l o g H D L的逻拇运算中,设A=8'b11010001,B=8'b00011001,则表达式"A&B"的结果为。

3A.8'b00010001B.8'b11011001C.8'b11001000D.8'b001101113、已知A=3'b110,B=3'b000,则AIIB结果为A.1B.O 110 D.3'b0014 、已知 A = 4 ' b 1 0 1 0 , 则 & A = ,A.1,0B.1,1 D.0,015、不完整的IF语句,其综合结果可实现:A . 三态控制电路B .条件相或的逻辑电路C.双向控制电路D.时序逻辑电路16、下列关于同步有限状态机的描述错误的是A. 状态变化只能发生在同一个时钟跳变沿;B.状态是否变化要根据输入信号,只要输入条件满足,就会立刻转入到下一个状态。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

河北大学课程考核试卷

2008——2009学年第一学期2006级电气类专业(类)

考核科目EDA技术课程类别必修考核类型考查考核方式闭卷类别A

一、选择题:

1、下列标示符哪些是合法的(B )

A、$time

B、_date

C、8sum

D、mux#

2、如果线网类型变量说明后未赋值,起缺省值是(D )

A、x

B、1

C、0

D、z

3、现网中的值被解释为无符号数。

在连续赋值语句中,assign

addr[3:0]=-3;addr被赋予的值是( A )

A、4’b1101

B、4’b0011

C、4’bxx11

D、4’bzz11

4、reg[7:0] mema[255:0]正确的赋值是(A )

A、mema[5]=3’d0,

B、8’d0;

C、1’b1;

D、

mema[5][3:0]=4’ d1

5、在code模块中参数定义如下,请问top模块中d1模块delay1、

delay2的值是( D )

module code(x,y); module top;

paramee

delay1=1,delay2=1; …………….………………………………

code #(1,5) d1(x1,y1);

endmodule endmodule

A、(1,1)

B、(5,5)

C、(5,1)

D、(1,5)

6、“a=4’ b11001,b=4’ bx110”选出正确的运算结果(B )

A、a&b=0

B、a&&b=1

C、b&a=x

D、b&&a=x

7、时间尺度定义为timescale 10ns/100ps,选择正确答案(C )

A、时间精度10ns

B、时间单位100ps

C、时间精度100ps

D、时间精度不确定

8、若a=9,执行$display(“current value=%0b,a=%0d”,a,a)正确显示为(B )

A、current value=1001,a=09

B、current vale=1001,a=9

C、1001,9

D、current vale=00…001001,a=9

9、aways begin #5 clk=0;#10 clk=~clk;end产生的波形( A )

A、占空比1/3

B、clk=1

C、clk=0

D、周期为10

10、在Verilog中定义了宏名 `define sum a+b+c 下面宏名引用正确的是(C )

A、out=’sum+d;

B、out=sum+d;

C、out=`sum+d;

D、都正确

二、填空题:(共15分,每小题3分)

1、某一纯组合电路输入为in1,in2和in3,输入出为out,则该电路描述中always的事件表达式应写为always@(in1,in2,in3 );若某一时序电路由时钟clk信号上升沿触发,同步高电平复位信号rst清零,该电路描述中always的事件表达是应该写为always @( posedge clk )。

2、在模块中对任务进行了定义,调用此任务,写出任务的调用mytast(f,g,m,n,p) 。

task mytast; 要求:变量的传递关系如下output x,y; m——a,n——b,p——c,x ——f,y——g

input a,b,c;

…….

endtask

3、if(a) out1<=int1; 当a= 1 执行out1<=int1

else out1<=int2; 当a= 0 执行out1<=int2

4、4’b1001<<2= 4’b100100 ,4’b1001>>2= 4’b0010 。

5、下面程序中语句5、

6、

7、11是并行执行,语句9、10是顺序执行

1 module M(……);

2 input ……. ;

3 output ……;

4 reg a,b……;

5 always@(……..)

6 assign f=c&d;

7 always@(……..)

8 begin

9 a=…….;

10 b=…….;

end

11 mux mux1(out,in0,in1);

endmodule

四、简答题:(共30分)

1、always语句和initial语句的关键区别是什么能否相互嵌套(5分)

always语句是循环语句,initial只执行一次。

它们不能嵌套。

2、画出下面程序段中r(reg型)的仿真波形 (6分)

fork

#20 r=1’ b0;

#10 r=1’ b1;

#15 r=1’ b1;

#25 r=1’ b1;

#5 r=1’ b0;

join

3、画出下面程序综合出来的电路图。

(7分)

always@(posedge clk)

begin

q0<=~q2;

q1<= q0;

q2<= q1;

end

4、HA模块程序如下,写出引用HA模块描述FA模块的Verilog程序。

(7分)

module HA(A,B,S,C); input A,B;

output S,C;

assign {C,S}=A+B;

endmodule

module FA(A,B,Ci,Co,S);

input A,B,Ci;

output Co,S;

wire Sl,C1,C2;

HA a(A,B,Sl,C1);

HA b(Sl,Ci,C2,S);

assign Co=C1|C2;

endmodule

5、写出下面程序中变量x,y,cnt,m,q的类型(5分)

begin

cnt=m+1;

q=~q;

end

五、编程题:(6分)

1、设计一奇偶校验位生成电路,输入八位总线信号bus,输出

及校验位odd,偶校验位even。

(6分)

2、设计一个带复位端且对输入时钟clk进行二分频模块,并画出仿真波形。

(9分)

设计要求:复位信号为同步、高电平有效,时钟的下降沿触发

3、设计一带异步复位端、异步置数段(低电平有效)的四位加

法计数器,时钟clk上升沿有效),复位信号clr,置数信号load、

输入数据data、输出qout。

并画出仿真波形。

(20分)五题答案1. module parity(even,odd,bus);

output even,odd;

input[7:0] bus; module m2(out,clk,reset);

input reset,clk;

output out;

reg out;

always @(negedge clk)

begin

if(reset)

out<=0;

else

out<=~out;

end

endmodule

3. module adder_4(qout,clr,clk,load,data);

output[3:0] qout;

input[3:0] data;

input load,clr,clk;

reg[3:0] qout;

always @(posedge clk or negedge load or negedge clk) begin

仿真波形

if(!load)

qout<=data;

else if(!clr)

qout<=0;

else qout<=qout+1;

end

endmodule。