基于FPGA的快速加法器的设计与实现

基于FPGA的加法器设计

基于FPGA的加法器设计一、实验目的1.熟悉用Quartus编译Verilog语言的方法。

2.掌握用Verilog HDL语言描述加法器的方法。

3.利用nios核建立加法器。

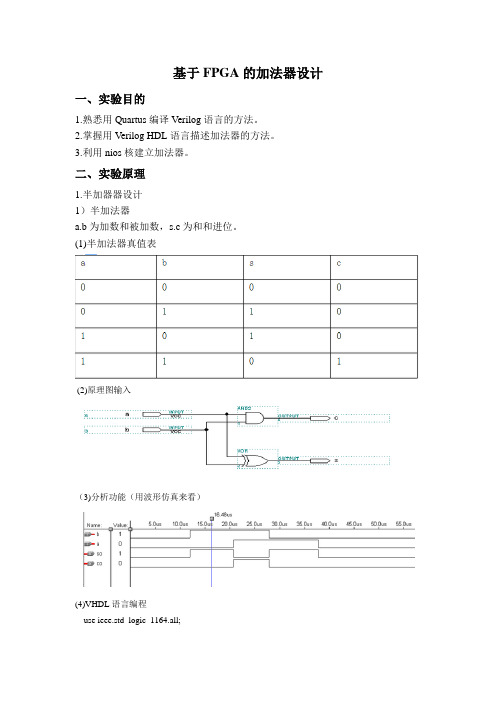

二、实验原理1.半加器器设计1)半加法器a.b为加数和被加数,s.c为和和进位。

(1)半加法器真值表(2)原理图输入(3)分析功能(用波形仿真来看)(4)VHDL语言编程use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity hjfq isport(a,b: in std_logic;s,c: out std_logic);end hjfq;architecture behave of hjfq isbegins<=not(a xor (not b));c<=a and b;end behave;2、全加法器a.b.c为加数、被加数和低位进位,so.co为和与进位。

(1)全加法器真值表(2)全加法器原理图:(3)波形仿真时序图:(4)VHDL语言编程:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity jfq isport(a,b,c: in std_logic;so,co: out std_logic);end jfq;architecture behave of jfq issignal bb: std_logic_vector(2 downto 0);beginbb<=a&b&c;process(b)begincase b iswhen "000"=>co<='0';so<='0';when "001"=>co<='0';so<='1';when "010"=>co<='0';so<='1';when "011"=>co<='1';so<='0';when "100"=>co<='0';so<='1';when "101"=>co<='1';so<='0';when "110"=>co<='1';so<='0';when "111"=>co<='1';so<='1';when others => null;end case;end process;end behave;三、实验步骤(1)打开QuartusⅡ软件,熟悉软件界面及窗口命令。

fpga并行加法运算

fpga并行加法运算

FPGA并行加法运算。

在计算机科学和工程领域,FPGA(现场可编程门阵列)是一种

灵活的硬件平台,它可以被重新配置为执行特定的计算任务。

FPGA

在许多领域都有广泛的应用,其中之一就是并行加法运算。

并行加法是一种通过同时处理多个数据来加速加法运算的方法。

在传统的串行加法中,每个数字位的相加都需要等待上一位的运算

结果,这限制了加法运算的速度。

而在FPGA中,我们可以利用其并

行计算的能力,实现更高效的加法运算。

FPGA中的并行加法通常是通过利用硬件资源来同时处理多个数

位来实现的。

FPGA可以配置成多个加法器并行工作,每个加法器处

理输入数据的不同部分,从而实现加法运算的并行化。

这种并行化

的方法可以大大提高加法运算的速度,特别是在需要处理大量数据

的情况下。

除了提高加法运算的速度外,FPGA还可以通过灵活的编程和配置,实现定制化的加法运算逻辑,满足不同应用的需求。

这使得

FPGA成为了一种非常强大和灵活的加速硬件平台,特别适用于需要

高性能并行加法运算的应用场景,比如数字信号处理、密码学和通

信系统等领域。

总的来说,FPGA并行加法运算利用其灵活的硬件资源和并行计

算能力,实现了高效的加法运算。

随着FPGA技术的不断发展和应用

范围的扩大,相信它在并行加法运算领域将发挥越来越重要的作用。

基于FPGA的计算器设计

基于FPGA的计算器设计基于FPGA(可编程逻辑门阵列)的计算器设计是一种使用FPGA开发板和硬件描述语言来实现的计算器。

它可以进行基本的数学运算,如加法、减法、乘法和除法等。

FPGA计算器不仅具有快速的运算速度和高度的可靠性,还具有较小的体积和低功耗。

FPGA计算器通常由输入、控制单元、运算单元和输出组成。

输入可以通过按钮、键盘或其他输入设备来实现。

控制单元负责解析输入并发出相应的控制信号。

运算单元是FPGA计算器的核心组件,它负责接收控制信号,并执行相应的运算操作。

输出单元将运算结果显示在计算器的屏幕上。

使用硬件描述语言(HDL)来实现FPGA计算器的设计可以提供高度的灵活性和可扩展性。

HDL允许开发人员通过编程方式定义逻辑门和电路功能,而不是通过物理硬件组件来实现。

这意味着开发人员可以根据需要添加新的运算功能,并且可以很容易地在FPGA计算器上进行修改和更新。

FPGA计算器可以通过对数据进行二进制表示来实现各种数学运算。

例如,加法可以通过将两个二进制数相加来实现。

具体实现可以使用查找表(Look-up Table)或全加器等组合逻辑电路来完成。

除法则比较复杂,通常需要使用除法算法来实现。

除了基本的数学运算,FPGA计算器还可以实现其他功能,如逻辑运算、位操作和存储器操作等。

逻辑运算可以用于实现条件语句和循环语句等流程控制功能。

位操作可以用于提取和修改数据的特定位。

存储器操作可以用于存储和读取数据。

基于FPGA的计算器设计有许多优点。

首先,FPGA计算器具有非常快的运算速度,比软件计算器更加高效。

其次,FPGA计算器具有较小的体积和低功耗,适合嵌入式系统或低功耗应用场景。

此外,由于FPGA计算器的硬件实现,它也具有较高的稳定性和可靠性。

然而,基于FPGA的计算器设计也存在一些挑战。

首先,硬件描述语言的学习成本较高,需要开发人员具备一定的硬件设计知识。

其次,FPGA 计算器的开发过程相对复杂,需要编写和调试大量的HDL代码。

基于FPGA的四位加法器设计

基于FPGA的四位加法器设计4位加法器设计。

取开发板上的4位按键作为4位被加数,取4位拨码开关作为4位被加数,其中8个led灯取5位作为输出结果,led0-led3作为相加的结果,led4作为进位(LED亮表示低电平0,LED灭表示高电平1,)数码管以十进制数显示被加数,加数和相加的结果。

包括vhdl文件、和vwf文件。

利用两组按键作为两个加数输入,用数码管做加数显示和结果显示,开发板上只有4个数码管,但加数都是两位的,所以只能做轮流显示,用“=”键做显示切换。

程序如下:library ieee;use ieee.std_logic_unsigned.all;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;entity adder_4 isport(clk:in std_logic; --时钟输入,应该输入分频后的clkenter:in std_logic; --显示切换,可以理解位“=”键clear:in std_logic; --清除键,预留接口可扩展key_num1:in std_logic_vector(3 downto 0); --加数1key_num2:in std_logic_vector(3 downto 0); --加数2duan:out std_logic_vector(6 downto 0); --输出结果wei:out std_logic_vector(3 downto 0);led5:out std_logic_vector(4 downto 0) --led结果显示);end entity;architecture fun of adder_4 issignal num1,num2:std_logic_vector(3 downto 0); --中间信号定义signal add_num1: integer range 15 downto 0;signal add_num2: integer range 15 downto 0;signal add_sum: integer range 30 downto 0;signal ten_data:integer range 9 downto 0;signal add_num1ge,add_num1shi,add_num2ge,add_num2shi,sumge,sumshi:integer range 9 downto 0;signal wei_data:integer range 0 to 3;beginduan<="1000000"when ten_data=0 else --显示部分,数码管共阳"1111001"when ten_data=1 else"0100100"when ten_data=2 else"0110000"when ten_data=3 else"0111001"when ten_data=4 else"0010010"when ten_data=5 else"0000010"when ten_data=6 else"1111000"when ten_data=7 else"0000000"when ten_data=8 else"0010000";process(clk,clear,enter,key_num1,key_num2,num1,num2,add_num1ge,add_num1shi,add_n um2ge,add_num2shi,sumge,sumshi)beginif clear = '0' thenadd_num1<=0;add_num2<=0;add_sum<=0;else--if key_num1/="1111" or key_num2/="1111" thennum1<=not key_num1;num2<=not key_num2;--加数处理,二进制转十进制。

基于FPGA的硬件加速器设计与实现

基于FPGA的硬件加速器设计与实现一、硬件加速器概述硬件加速器是指基于专用硬件设计的加速器,其目的是提高特定应用程序的执行速度。

相对于传统的软件计算方式,硬件加速器更加高效,能够极大地提升应用程序的执行速度。

而基于FPGA的硬件加速器则是一种极其灵活可编程的硬件加速器。

二、FPGA概述FPGA(Field-Programmable Gate Array,现场可编程门阵列)是一种可编程的、集成度高的数字电路芯片。

它通过先进的加工工艺,将大量的基本逻辑单元、存储器单元、全局互联元件等组合起来,形成充分灵活的通用逻辑门阵列,并能通过编程器件即可将其转化为符合应用需求的数字电路系统。

FPGA拥有比ASIC更高的灵活性和可重配置性。

通过FPGA,硬件加速器可以高度定制化,且易于控制与修改。

三、硬件加速器的实现方式目前,实现硬件加速器的方式有两种:ASCI和FPGA。

ASCI通过特别定制化的电路设计实现对特定应用的加速。

这种高度优化的硬件能够极大地提高应用执行效率,但在设计和生产方面会带来挑战。

另外,ASIC在出现应用需求变化时无法进行动态更新和修改。

FPGA在硬件加速器方面拥有高度可编程和灵活性的优势,可以随时更新和修改,能够在应用需求不断变化的情况下,灵活地适应变化的需求。

同时,FPGA也可以拥有与ASIC相同的性能和功耗水平。

四、基于FPGA的硬件加速器设计设计基于FPGA的硬件加速器需要进行以下步骤:1.应用程序的分析和建模为了能够设计出适用于特定应用的硬件加速器,首先需要进行应用程序的细致分析和建模。

硬件加速器只能处理某些特定的模块,因此需要对原始应用程序进行分解并寻找可加速的部分。

常见的应用程序包括计算型应用,如矩阵乘法、计算流体力学、医学成像等;还有数据传输型应用,例如网络加速、磁盘控制器等。

2.算法的优化和转换在硬件加速器中,设计的算法要比原始程序简单,因为硬件加速器只能处理某些特定的模块。

FPGA一位全加器设计实验报告

FPGA一位全加器设计实验报告

本实验的目的是学习使用FPGA设计一个全加器,通过实践掌握FPGA硬件描述语言和数字电路设计的一些基础知识和技能。

一、实验背景

数字逻辑电路是计算机硬件的基础,而硬件描述语言是数字电路设计的重要手段。

FPGA是可编程逻辑器件,它可以根据用户的需求进行编程,实现不同的数电逻辑电路。

全加器是组成加法器的重要单元,也是我们学习数字逻辑的重要基础。

二、实验设计

本实验我们将采用Verilog硬件描述语言来设计一个全加器。

代码如下:

module full_add(

input A,B,Cin,

output S,Cout

);

wire w1,w2,w3;

xor(S,w1,A^B);//A异或B

xor(Cout,w2,A&Cin);//A与Cin之后异或

xor(w3,B&Cin,A&Cin);//B与Cin之后异或

xor(Cout,Cout,w3);//再次异或

endmodule

三、测试结果

我们使用Quartus II软件进行仿真和综合。

通过对代码的仿真和波形分析,我们发现该全加器符合设计要求,并且可以正确地输出结果。

四、实验总结

本实验我们学习了FPGA硬件描述语言,掌握了数字电路设计的一些基础知识和技能。

通过设计全加器,我们更深入地理解了数字逻辑电路的原理和应用。

希望在今后的学习中,能够继续深入研究数字电路的知识,为我们掌握计算机硬件设计打下坚实的基础。

加法器除法器FPGA实现总结文档

加法器除法器FPGA实现总结文档FPGA实现加法器和除法器总结文档引言FPGA(Field-Programmable Gate Array)是一种可编程逻辑芯片,可以根据需要进行配置和重新编程,具有灵活性和可重复性。

在数字电路设计中,加法器和除法器是非常常见且基础的功能模块。

本文将总结FPGA实现加法器和除法器的过程和结果,并对实现的优势和不足进行分析。

一、加法器的实现在FPGA中实现加法器有多种方法,最基本也是最常见的是使用全加器构建一个完整的加法器。

全加器是一个三输入一输出的电路,可以实现两个二进制位的加法。

通过级联多个全加器,就可以构造出任意位数的加法器。

1.实现步骤:(1)定义加法器的输入和输出位数:假设我们要实现一个4位加法器,那么就需要4个输入(A[3:0]、B[3:0])和一个4位输出(SUM[3:0])。

(2)使用VHDL或Verilog等硬件描述语言来描述全加器和加法器的逻辑。

(3)使用逻辑综合工具将硬件描述语言代码综合为逻辑电路连接。

(5)验证加法器的功能和正确性。

2.实现优势:FPGA实现加法器的优势主要体现在以下几个方面:(1)灵活性:FPGA可以根据需要重新编程,可以方便地修改加法器的位数和功能。

(2)速度:FPGA中的逻辑电路是并行计算的,可以实现高速的加法运算。

(3)资源利用:FPGA可以利用其内部的查找表(lookup table)实现逻辑运算,节省了硬件资源的使用。

3.实现不足:FPGA实现加法器也存在一些不足之处:(1)成本高:FPGA价格相对较高,成本较高,适合于需要较高性能和灵活性的应用场景。

(2)资源有限:FPGA的资源有限,实现复杂的逻辑电路可能会导致资源不足的问题。

二、除法器的实现除法器是一个更为复杂的数字电路,用于实现两个二进制数的除法运算。

在FPGA中实现除法器需要使用一种称为"非冗余算法"的方法,通过迭代运算来实现除法的功能。

一种基于FPGA的32位快速加法器设计

一种基于FPGA的32位快速加法器设计第32卷第7期四川兵工2011年7月【自动化技术】一种基于FPGA的32位快速加法器设计岳伟甲,刘昌锦(炮兵学院,合肥230031)摘要:针对采用流水线结构设计的32位加法器系统延迟时间长的问题,设计了一个4级流水线结构的32位加法器,并对这个流水线结构进行了分析改进,设计了一个两级流水线结构的32位加法器.关键词:流水线;an法器;先行进位中图分类号:TP23文献标识码:A文章编号:1006—0707(2011)07—0078—04加法器是数字电路中非常重要的一部分,其运算的速度和硬件消耗大小,直接影响着整个数字电路的性能.常见的快速加法器实现方法有先行进位加法器(carry—skipad—der),选择进位加法器(darry—se/eetadder)和进位保留加法器(Cal'ltysaveadder,CSA).每种加法器各有其特点,乘法运算中采用进位保留加法器速度较快;在单纯的加法中先行进位加法器速度最快J,但是随着参与运算的位数增大,先行进位加法器的实现结构变得非常复杂.因此在位数较长的快速加法器设计中常采用流水线把位数较小的先行进位加法器组成位数较长的加法器.本文采用4级流水线结构和8位先行进位加法器组成一个32位加法器,并对这个流水线结构进行了分析改进.14级流水线结构的32位加法器假设.Y.为2个求和二进制数,C为低位的进位,S为输出本位和,c为高位进位则根据加法的定义可得到Sl=1①Y1oC1(1)C2X1Y1+lclY1Cl(2)对应的可以得到第i级的输出函数Si=OY①C(3)Ci+l=),+c+ycf(4)对应进位进行整理得到c+1=xiY+(Y)c(5)令g:xiy~Pf=+Y则c…=g+PlC同样可以得到:ci=一+pci一.这样一直展开到0级就得到c"l:g+P…gl+PiP卜lg一2+…+PiPi—l一-p2PlgoPiPl.一P2PlPoC0(6)整理后得到卜】ci=gl一】+Pi~1g卜2+Pl一1p卜2gi一3+…+co1 :1=g+∑.(gl-m-ljII.PJ)+c0,.B(7)由此可以看到先行进位加法器的结构由两部分组成,进位计算模块和本位和计算模块.由式(7),容易求出8位先行进位加法器的公式,得到内部的设计结构如图1所示.图18位先行进位加法器内部设计结构这里采用的是4级流水线设计,每个流水线由一个8位先行进位加法器和起到延时作用的寄存器组成.32位加法数据分成4组同时加载到4个流水线上,从低到高对应.流水线1对应0到7位,流水线2对应8到15位依次类推,在第一个时钟有效沿处,先行进位加法器处理数据0到7,其它数据进入各级流水线的寄存器,下一个时钟到来后,2级流水线寄存器中的8到15数据进人先行进位加法器处理,同时新的32位输入加载到流水线,新数据的0到7位进入1流水线的先行进位加法器.依次类推,到4个时钟的时候,同时处理了4个数据.这样就实现了一个时钟处理4个8位先行进位加法数据,实现32位加法的效果.大大提高了数据的吞吐力,但是增加了最终输出结果的延时,4级流水线的最终结果要经过4个时钟周期的延迟才能输出,以后每一个时钟周期输出一个结果.采用这种结构设计出的32位先行进位加法器如图2所示.2对流水线结构的改进从上面的分析看出,虽然4级流水线结构的32位加法收稿日期:2011—04—22作者简介:岳伟甲(1981一),男,讲师,主要从事通信与信息系统研究; 刘昌锦(1958一),男,教授,硕士生导师,主要从事通信与信息系统研究. 岳伟甲,等:一种基于FPGA的32位快速加法器设计79器平均每个系统时钟完成一次32位加运算,但是系统的延时较大为4个系统时钟.不能满足对于转换速度要求较高的场合.因此采用一种新的方式,综合流水线技术和先行进位加法的优点,设计了一种采用级间进位的方法进行设计.其结构如图3所示.FINO-7FIN8—15FIN16-23FIN24—31FOUT0.7FOUT8—15FOUTl6.23F0UT24—31图24级流水线累加器结构图3改进的32位先行进位加法器结构经过分析可知8位2进制数相加,会得到一个8位本位以及一个1位的进位.只要能够把低位进位同本位数据相加就可以得到最终结果.假设二级先行进位加法器中输入,Y,32位加法分成4个模块,级问的进位分别为c,c,c此时内部进位为c,P,q,通过分析,容易发现第二级加运算中=Oi=O,1,…,7(8)Y=si=O,1,…,7(9)由此得到P:Yi=0,1,?q=0i=0,1,??(1O)(11)把式(8),(9)带入式(7)得到i—Ici=∑Y?COi=12一,8(12)下面再分析级间进位的影响.对于第一级来说cs=C8(13)后面3级的进位情况比较复杂,下面先分析2个8位2进制数相加的情况.这里假设2-58位2进制数n和b,两者相加产生一个8位数d,不考虑低位进位时进位为C,考虑低位进位时进位为C.先不考虑低位向高位的进位为.假设此时c=1,即在产生了进位的前提下,只有当n和b都取到最大值时d取到最大值四川兵工http://scbg.joursel'y.corn/aMAx=bMAx=11111111B=255D(14)dM^x:aMAx+bMAx=I1111110B=254Dc=1(15)可以看到此时无论,低位向高位的进位为何值都不会影响进位c=1的值.再假设C=O,则此时d可以取到最大值dMAx:11111111B=255DC=0(16)此时如果=l则会产生一个进位c1,其余的情况都不能改变进位.则c='do.dl'd2'd3'd4?d5'd6'd7C=0(17)综合上面两者得到C=?dodl'dz.d3?d4.d5?d6?d7+C(18)由此得到级问进位的表达式15Ctl6=c8?c.n5+c(19)c=c.'c17s+C16:1523C16?(cc.?兀s+c)兀s+CI6=8E162323cc8.c0兀s+Cl6'兀s+C16(20)c,:=c?c17+C24=232332({一716?C一8?ns+?Hs+c.)17s+c=323232~2gC16.c8?c0?nc.c8?兀C16C24?兀c(21)同先行进位加法器进位公式对比可以看到,先行进位加法器中当i=32时,整个表达式需要33个部分项,最大的部分项的长度为33.而采用本文设计的加法器中最终进位只包含4个部分项,最大部分项长度为28.显然本文的设计更容易实现.同4级流水线结构相比,系统延时由4变为2, 减少了50%.表l中列出了,本文设计同其它设计的性能对比.表1本文设计的加法器同其它加法器性能对比从表1中可以看出,采用本文的设计比采用32先行进位设计实现的难度小,同4流水线结构比较输出延时减少50%,因此本文设计的32位加法器是比较容易在FPGA中实现,且性能较好的一种设计之一.3FPGA中验证本文FPGA验证的软件环境是Altera公司Quartus8.0开发环境和Modelsim6.1g.硬件采用的是选择的是Altera公司的EP1K100QL208—2芯片.验证FPGA中设计采用的方法是编写testbench例化待测试设计,输入激励向量进行仿真,输出仿真结果.本文testbench采用verilogHDL语言编写.fb1改进后延迟2个时钟图4改进前后延迟仿真结果岳伟甲,等:一种基于FPGA的32位快速加法器设计81 (上接第73页)4结束语本文对影响巡回修理任务量的因素进行了分析,提出了先进因子M,役龄因子,并引入了斐波那契数列,定义了斐波那契因子F以及斐波那契区间R,在此基础上计算r役龄因子,构建了基于任务量的巡回修理工时分配权重因子的计算模型,并以实例验证了模型的有效性和可行性.本文的研究成果可用于装备机关制定巡回修理工时分配计划时使用,可以提高稀缺维修资源的利用率.有一定的指导意义. 下一步还要对巡回修理单元的规模以及巡回修理任务调度进行研究.参考文献:[1]杨景辉,康建设.机械设备故障规律与维修策略研究[J].科学技术工程,2007,7(】6).4143~4146.马彦恒,韩九强,李刚.电子产品寿命预测中Bs模型算法[J].兵_Y-,2007,30(5:I:551—554.杨健,刘爱东,孙翱.某型测控装备远程智能故障诊断技术[J].兵工自动化,2010,29(3).68.王崛,龚长红.装甲车辆故障诊断专家系统[J].四川兵工,2010,31(2):7—9.杨志强,李海,周建新.武器装备故障规律的"六类模式"[J].前卫装备,2008(1).46—47.张维忠.论黄金分割的文化意义[J].浙江师范大学学报,20o5,30(1):2—5.詹伟,朱光喜,彭立.利用斐波那契数列构造Qc—LD—PC码的方法[J].华中科技大学,2008,36(10).63—65.(责任编辑刘舸)1』1j234567。

基于 FPGA 的神经网络加速器设计与实现

基于 FPGA 的神经网络加速器设计与实现引言神经网络是一种模拟人脑认知机制的计算模型。

随着深度学习和人工智能的发展,神经网络在图像识别、自然语言处理、语音识别等领域得到广泛应用。

然而,神经网络的计算量巨大,传统CPU和GPU计算能力越来越难以满足需求。

因此,基于FPGA的神经网络加速器备受关注。

FPGAFPGA是可编程逻辑门阵列,是一种可编程硬件。

与CPU和GPU不同,FPGA 的硬件结构可以根据需要重新配置,因此在某些场景下可以提供更高的计算效率。

在神经网络计算中,FPGA可以利用并行计算和低延迟的特点,提供更高的计算效率。

神经网络加速器架构设计神经网络加速器一般采用流水线和并行计算的结构,以提高计算效率。

下图是一种常见的架构设计。

图1.神经网络加速器架构神经网络加速器包括输入层、隐层和输出层。

输入层接收输入数据,隐层负责计算,输出层生成输出结果。

神经网络加速器的核心是计算单元,用于并行计算神经网络中的向量乘法。

这些计算单元可以采用FPGA的硬件结构实现,利用并行计算和重配置的特性提高计算效率。

神经网络加速器实现通常,神经网络加速器的实现需要涉及到硬件设计、软件开发和算法优化等方面。

下面从这些方面分别介绍神经网络加速器的实现。

硬件设计硬件设计是神经网络加速器的关键。

硬件设计可以包括FPGA结构设计、计算单元设计、存储器管理和总线控制等方面。

FPGA结构设计需要根据神经网络的特点进行设计。

一般来说,FPGA需要支持高速存储器、流水线、并行计算和访问控制等。

计算单元设计是神经网络加速器的核心。

计算单元通常采用硬件乘法器和加法器组成,用于实现神经网络中的向量乘法和加法运算。

存储器管理也是神经网络加速器的重要组成部分。

存储器需要高速、可靠,并支持读写操作。

总线控制则需要负责从主机CPU中读取数据和将计算结果返回给CPU。

软件开发软件开发通常包括驱动程序和应用程序开发。

驱动程序是神经网络加速器与某一特定系统进行交互必不可少的一环。

基于FPGA的快速加法器的设计与实现

111 从上面的表达式可知: 所有位的进位都不依赖低位的 进位, 每一位的进位只依赖于输入的A , B 和 C 0, 可以同时 产生。若不考虑G i 和 P i 的形成时间, 则N 位超前进位加法 器的进位总延迟为 dt, 与字长无关。但随着加法器位数的 增加, C i 的表达式会越来越长, 电路结构会越来越复杂, 而 且将受到元器件扇入系数的限制, 所以完全采用并行进位 是 不可能的。实际上通常采用分组并行进位来实现, 即把 N 位字长分为许多小组 (每组通常4 位) , 在组内实现超前 进位, 在组间既可采用行波进位, 也可采用超前进位。一 般, 组内采用超前进位、组间行波进位的方式称为单级超 前进位加法器; 组内、组间均采用超前进位的方式称为多 级超前进位加法器[ 1 ]。 114 高速串行加法器

赵亚威等: 基于 FPGA 的快速加法器的设计与实现

间 (约为组合逻辑输出的10% ) , 另一方面又可以在低级进 位到达时, 更快速地输出该位的和运算结果。 此外, 在 FPGA 内部同一列的两个SL ICE 间, 还专门为进位传递保 留了一条最短连线。正是基于这样的一种结构, V irtex E 器件可以实现快速的行波进位加法器: 16 位的行波进位 加法器寄存器输入到输出的响应时间为413 n s, 64 位的行 波进位加法器为 613 n s[2]。 113 超前进位加法器

2 采用流水线结构实现的快速加法器

211 流水线结构 流水线的作用是提高硬件部件的使用率, 减少指令的

平均执行时间, 从而增强了处理器的处理能力。流水线的 流水线深度是指流水线中总的流水线的数目, 也就是处理 器可以并行处理多少条指令。流水线的每一个阶段称为流 水步、流水步骤、流水段、流水线阶段、流水功能段、功 能段、流水级、流水节拍等。一个流水阶段与另一个流水 阶段相连形成流水线。指令从流水线一端进入, 经过流水 线的处理, 从另一端流出。在流水线的每一个功能部件的 后面都要有一个缓冲器, 称为锁存器、闸门寄存器等, 他 的作用是保存本流水段的执行结果。图 1 是一个 3 级流水 线操作的示意图[5], 在第N 个指令取指时, 前面一个 (即第 N - 1 个) 指令正在译码, 而第N - 2 个指令则正在执行。

基于FPGA的全加器的设计

实验二 全加器设计一、实验目的1、设计并实现一个一位全加器。

2、编写testbench 并仿真。

二、实验原理计算机中的加法器一般就是全加器,它实现多位带进位加法。

下面以一位全加器介绍。

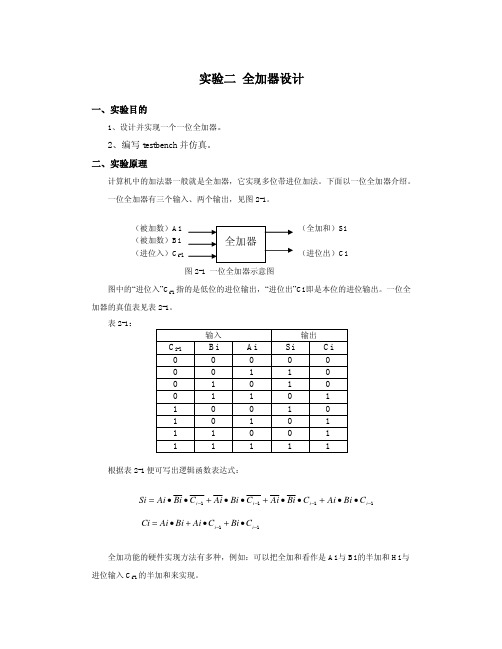

一位全加器有三个输入、两个输出,见图2-1。

图2-1 一位全加器示意图图中的“进位入”C i-1指的是低位的进位输出,“进位出”Ci 即是本位的进位输出。

一位全加器的真值表见表2-1。

表2-1:输入输出C i-1 Bi Ai Si Ci 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 01 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 11 1 1 1根据表2-1便可写出逻辑函数表达式:1111−−−−••+••+••+••=i i i i C Bi Ai C Bi Ai C Bi Ai C Bi Ai Si 11−−•+•+•=i i C Bi C Ai Bi Ai Ci全加功能的硬件实现方法有多种,例如:可以把全加和看作是Ai 与Bi 的半加和Hi 与进位输入C i-1的半加和来实现。

(被加数)Bi (被加数)Ai(进位入)C i-1(全加和)Si(进位出)Ci多位全加器就是在一位的原理上扩展而成的。

集成电路全加器有7480、7481、7483等。

实验源程序文件名是fulladder.vhd。

三、实验代码(含TESTBENCH)1、全加器代码LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY fulladder ISPORT(a,b,cin:IN STD_LOGIC;s,co:OUT STD_LOGICM : out std_logic_vector(3 downto 0));--4位功能选择位M[3:0],设置状态为0001,即16位拨码开关接到16位数据总线上。

FPGA四位加法器实验报告

题目:含异步清0和同步使能的4位加法计数器一. 实验目的.学习时序电路的设计、仿真和硬件测试,进一步熟悉VHDL技术。

二.实验原理.如图是一含计数使能、异步复位和计数值并行预置功能4位加法计数器,4位锁存器;rst是异步清0信号,高电平有效;clk是锁存信号;D[3..0]是4位数据输入端。

ENA是使能信号,当ENA为'1'时,多路选择器将加1器的输出值加载于锁存器的数据端;当ENA为'0'时将"0000"加载于锁存器。

三.实验内容.设计一个含异步清0和同步使能的4位加法计数器;实现对输入时钟(clk)的计数。

任务分析:在RST=1,ENA=1时,系统对输入时钟进行计数,所计数值输出至OUTY(3 DOWNTO 0),当计数满15时,产生一个进位,输出至COUT,同时OUTY溢出归零;如果RST=1,ENA=0时,保持原来的计数值不变。

如果RST=0,置输出信号为0;1)异步复位,则输入信号有复位信号RST2)同步使能, 则输入信号有使能信号ENA3)要求同步的时序,则输入信号有时钟CLK在QuartusII上对下列程序进行编辑、编译、综合、适配、仿真。

module CNT4B(CLK,RST,ENA,CLK_1,RST_1,ENA_1,OUTY,COUT);input CLK,RST,ENA;output CLK_1,RST_1,ENA_1;output[3:0] OUTY;output COUT;reg[3:0] OUTY;reg COUT;wire CLK_1; wire RST_1; wire ENA_1;assign CLK_1 = CLK; assign RST_1 = RST; assign ENA_1 = ENA;always@(posedge CLK or negedge RST)begin if(!RST)begin OUTY<=4'b0000;COUT<=1'b0; endelse if(ENA)Begin OUTY<=OUTY+1;COUT<=OUTY[0] & OUTY[1] & OUTY[2] & OUTY[3]; end end endmodule四.实验步骤.1.在QUARTUSII软件下创建一工程,工程名为CNT4B,芯片名为EP2C35F672C6;2.新建Verilog语言文件,输入以上Verilog语言源程序,并将程序命名为CNT4B.vhd,保存在与工程相同的文件夹中;3.进行功能仿真、全编译、时序仿真,如出现错误请按照错误提示进行修改,保证设计的正确性。

基于FPGA的加法器设计

基于FPGA的加法器设计FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,用于设计和实现数字电路。

它是通过将逻辑门、存储单元和可编程插线连接起来,以创建复杂的数字电路。

在FPGA中,加法器是最基本的基本数字电路之一、它用于将两个二进制数相加,并计算其和。

设计一个基于FPGA的加法器需要考虑以下几个方面:加法器类型、加法器位宽和加法器延迟。

首先,有几种不同类型的加法器,包括全加器、半加器和四位加法器等等。

全加器是最基本的加法器,能够对两个二进制数进行相加,并且还考虑了来自上一位的进位。

半加器只能对两个二进制数进行相加,而不考虑进位。

四位加法器是对四个二进制数进行相加的高级加法器,并且还考虑了来自上一位的进位。

其次,加法器的位宽也是设计过程中的一个关键因素。

位宽决定了加法器能够处理多少个位。

例如,一个4位加法器可以处理四个二进制数相加,并且还会考虑进位。

选择适当的位宽可以提高加法器的性能和灵活性。

最后,加法器的延迟是设计过程中另一个重要的考虑因素。

延迟是指从输入信号发生变化到输出信号变化之间的时间间隔。

较低的延迟意味着加法器可以更快地计算结果。

然而,较低的延迟可能需要更多的资源,这可能会对FPGA的资源消耗产生影响。

设计基于FPGA的加法器的过程如下:1.确定加法器类型:根据需求选择最适合的加法器类型,如全加器、半加器或者四位加法器。

2.设计加法器电路:根据选定的加法器类型,设计相应的加法器电路。

例如,在全加器中,可以使用两个异或门和一个与门来实现。

3.考虑进位:根据加法器类型,确定是否要考虑进位。

如果是全加器,需要将来自上一位的进位考虑在内。

4.确定位宽:根据需求确定所需的加法器位宽。

例如,如果需要对8位二进制数相加,需要设计一个8位加法器。

5. 实现电路:使用HDL(Hardware Description Language)编程语言如VHDL或Verilog来实现设计的电路。

基于FPGA的高速浮点加法器的实现

第一作者简介 : 秀芳(97 )女 , 族 , 士 , 授 , 究 方 向: 王 16 一 , 汉 博 教 研 无线通信。 通 讯 作 者 简 介 : 振 龙 ( 9 5 ) 男 , 族 , 士 研 究 生 , 究 方 侯 18 一 , 汉 硕 研 向 : 息 传输 及 处理 。 信

2 浮点加法器的硬件实现过程

的硬 件实 现注入 了新 的活力 。

位、 双精 度 6 4位 。以单精 度 浮点 数 为 例 , 计 了 3 设 2

位 的高 速浮 点加法 器 。

s

— 一 E —

—— —— ——— ÷ ・——— 一M — — ——— —+

文献 [ ] 计 了高速 的 F T 处 理 器 , 内部 正 2设 F1 I 其 是使用 了浮点算 法 单 元 。 由于 其 使用 的是 1 6位 浮 点算 法 , 整个设 计 的精 度 方 面还 有 待 提 高 。文 献 在 [] 3 利用 V ro D ei gH L语 言设 计 了一 种 浮点 加 法 器 , l 系统最 高 时钟频 率达 到 8 MH , 是应 用 在 实 时 信 0 z但 号处理 领 域 , 钟频 率 还有 很 大 的提 高 。文 献 [ 时 4]

Sm S i E进 行 联 合 仿 真 结 果 表 明 , 系统 的运 行 精 度 可 以达 到 1 数 量 级 , 时该 设 计 可 参 数 化 、 作 为 独 立 的 子 系统 应 用 于 其 0 同 可

他 数 字 信 号处 理 领 域 。

关键词

IE 7 4 E E 5

可 编程 逻 辑 门 阵 列

第 l 0卷

第2 5期

21 0 0年 9月

科

学

技

术

与

基于FPGA的数字电路实验报告

·4位累加器

1.设计方案

需要用两个模块,一个用来进行保存工作,即累加器,另一个用来实现数据相加,即加法器。这样即可每次把数据加到总和里,实现累加器的工作。

2.原理说明及框图

基本原理为书上的结构图。只要实现了两个主要模块,再用线网连接即可。

State1

0

0

State1

State10

State1

0

0

State10

Empty

State101

0

0

State101

State1010

State1

0

0

State1010

Empty

Empty

0

1

经过状态化简,上面状态已经为最简状态。

状态装换图:

在用HDL代码实现时,利用always块和case语句实现有限状态机。

答:用两个异或门,比较计数器的输出与一个加数的大小,若相等时则输出低电平到累加器的使能端,则可停止累加。

实验9序列检测器的设计

·实验目的

掌握利用有限状态机实现时序逻辑的方法。

1实验原理:

有限状态机(FSM)本质上是由寄存器和组合逻辑电路构成的时序电路。次态由当前状态和输入一起决定,状态之间的转移和变化总是在时钟沿进行。有限状态机分为Moore型和Mealy型。Moore型有限状态机输出仅由当前状态决定;Mealy型有限状态机输出由当前状态和输入同时决定。

·思考题

1.给出锁存器的定义,它与边沿触发器的区别是什么?

答:锁存器是一种对脉冲电平敏感的存储单元电路,它可以在特定输入脉冲电平作用下改变状态。边沿触发器只有在固定的时钟上升沿或者下降沿来临时改变状态。可以通过锁存器实现边沿触发器。

FPGA多位加法器的原理图设计

FPGA多位加法器的原理图设计实验⼆多位加法器的原理图设计⼀、实验⽬的①进⼀步掌握Qurtus II原理图输⼊法的编辑、编译(综合)、仿真和编程下载的操作过程。

②掌握⽤原理图输⼊法设计4位加法器电路的⽅法,并通过电路仿真和硬件验证,进⼀步了解4位加法器的功能。

③在Quartus II软件中,掌握⽤原理图进⾏顶层设计的⽅法。

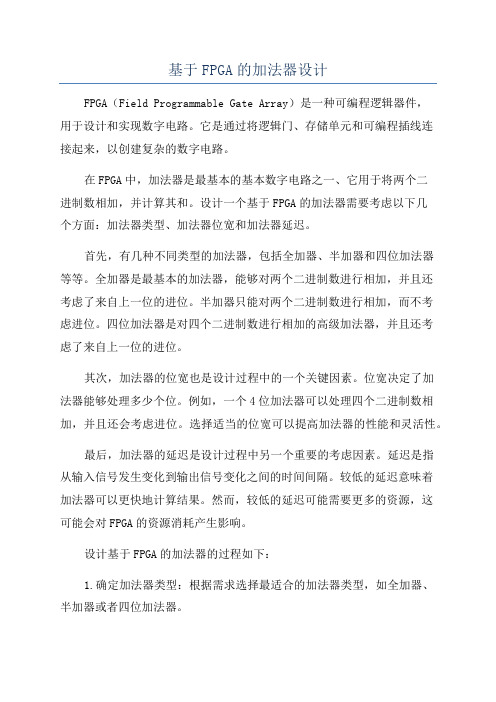

⼆、实验原理4位加法器的元件符号如图2.1所⽰,其中[A3..0]和[B3..0]是加法器的两个4位⼆进制数加数输⼊端,CIN是低位进位输⼊端,SUM[3..0]是加数之和输出端,COUT是向⾼位进位的输出端。

图2.1 4位加法器元件符号三、实验设备①EDA实训仪1台。

②计算机1台(装有QuartusⅡ软件)。

四、实验内容在QuartusⅡ软件中,将实验⼀中的1位全加器电路⽣成1个元件符号,然后新建⼀个4位加法器的⼯程,利⽤⽣成的1位全加器元件,⽤原理图的⽅法设计出4位的加法器电路,然后进⾏编辑、编译(综合)、仿真,引脚的锁定,并下载到EDA实训仪中进⾏验证。

注:⽤EDA实训仪上的拨动开关S3~S0作为加数A,S7~S4作为加数B,S8作为低位进位输⼊端CIN,⽤数码管SEG0作为和输出端SUM[3..0],⽤发光⼆极管L0作为进位输出端COUT。

五、实验预习要求①查阅资料,复习有关多位加法器的内容,并认真阅读实验指导书,分析、掌握实验原理。

②利⽤实验⼀中的1位全加器电路⽣成的元件符号,设计出4位加法器的电路图。

1、⼀位加法器的原理图输⼊:2、四位加法器的原理图输⼊:3、四位加法器引脚锁定:六、实验总结①进⼀步总结⽤QuartusⅡ软件的原理图输⼊法进⾏数字电路设计的⽅法及步骤。

答:1、建⽴⼯程项⽬(⽂件夹、⼯程名、芯⽚选择);2、编辑设计⽂件(元件、连线、输⼊输出、检查电路正确性);3、引脚锁定(参考⽂件锁定输⼊输出引脚);4、编译下载;5、硬件调试。

②对本次实验进⾏总结并完成思考题。

基于FPGA的快速加法器的设计与实现

基于FPGA的快速加法器的设计与实现

赵亚威;吴海波

【期刊名称】《现代电子技术》

【年(卷),期】2005(28)10

【摘要】加法器是算术运算的基本单元,可以有多种实现结构,采用不同的结构实现其耗用的资源和运算的速度也各不相同.本文研究了基于FPGA的常用加法器的结构及其设计方法,对各自性能加以分析比较,在此基础上采用流水线结构设计了一个8位的加法器.并在Xilinx公司的ISE 5.2i软件环境下,采用VHDL和Verilog HDL 硬件描述语言进行了设计实现并使用Modelsim进行仿真验证,在此基础上对其性能进行了比较分析.实验结果表明流水线加法器的速度高于其他结构实现的加法器.【总页数】3页(P113-115)

【作者】赵亚威;吴海波

【作者单位】沈阳理工大学,辽宁,沈阳,110045;东北大学,辽宁,沈阳,110004

【正文语种】中文

【中图分类】TP342+.2

【相关文献】

1.一种基于FPGA的32位快速加法器设计 [J], 岳伟甲;刘昌锦

2.基于SoC FPGA异构平台的魔方快速还原系统设计与实现 [J], 卢仕;张志文;张寅;万美琳

3.基于FPGA的MEWTOCOL-COM与MODBUS RTU协议快速转换的设计与实现 [J], 陈虎; 陈倩

4.基于FPGA+DSP的北斗信号快速捕获算法设计与实现 [J], 高唱;陈则王;曾庆喜;吕查德

5.基于FPGA的最佳精度定点加法器的设计与实现 [J], 黄政凯;刘冰洋;翟明明;罗二平;刘娟

因版权原因,仅展示原文概要,查看原文内容请购买。

FPGA加法器乘法器

FPGA加法器设计加法作为一种基本运算,大量运用在数字信号处理和数字通信的各种算法中。

由于加法器使用频繁,因此其速度往往影响着整个系统的运行速度。

如果可以实现快速加法器的设计,则可以提高整个系统的处理速度。

加法运算是最基本的算数运算,在多数情况下,无论是乘法、除法还是减法以及FFT等运算,最终都可以分解为加法运算来实现,因此对加法运算的实现进行一些研究是非常必要的。

实现加法运算有如下一些方法:(1)级连加法器;(2)并行加法器;(3)超前进位加法器;(4)流水线加法器。

1、级连加法器级连加法器是由1位全加器级连构成的,本位的进位输出作为下一级的进位输入。

级连加法器的结构简单,但N位级连加法运算的延时是1为全加器的N倍,延时主要是由于进位信号级连造成的。

在需要高性能的设计中,这种结构不宜采用。

module add_jl(sum,cout,a,b,cin);output [3:0] sum;output cout;input [3:0] ina,inb;input cin;wire [3:1] c;full_add1 f0 (ina[0],inb[0],cin, sum[0],c[1]); //级连描述full_add1 f1 (ina[1],inb[1],c[1],sum[1],c[2]);full_add1 f2 (ina[2],inb[2],c[2],sum[2],c[3]);full_add1 f3 (ina[3],inb[3],c[3],sum[3],cout);module full_add1(ina,inb,cin,sum,cout); //1位全加器input ina,inb,cin;output sum,cout;wire s1,m1,m2,m3;and (m1,ina,inb),(m2,inb,cin),(m3,ina,cin);xor (s1,a,b),(sum,s1,cin);or (cout,m1,m2,m3);endmodule2、并行加法器并行加法器可采用Verilog语言的加法运算符直接描述,或称为数据流描述方式,实现容易,其运算速度快,但耗费资源多,尤其是当加法运算的位数较宽时,其耗用资源将会大大增加。

快速浮点加法器的FPGA实现

—202— 快速浮点加法器的FPGA 实现郭天天,张志勇,卢焕章(国防科技大学ATR 实验室,长沙 410073)摘 要:讨论了3种常用的浮点加法算法,并在VirtexII 系列FPGA 上实现了LOP 算法。

实验结果表明在FPGA 上可以实现快速浮点加法器,最高速度可达152MHz ,资源占用也在合理的范围内。

关键词:浮点加法器;移位器;前导1预测;FPGAFPGA Implementation of Fast Floating-point AdderGUO Tiantian, ZHANG Zhiyong, LU Huanzhang(ATR Lab, NUDT, Changsha 410073)【Abstract 】Three commonly used Floating-point addition algorithms are discussed, and the LOP algorithm is implemented on VirtexII series FPGA. The implementing results show that the fast floating-point adder can be implemented on FPGA, the highest running frequency is 152MHz and the area cost is rational compare to the entire resources.【Key words 】Floating point adder ;Shifter ;Leading-one predicator ;FPGA计 算 机 工 程Computer Engineering 第31卷 第16期Vol.31 № 16 2005年8月August 2005·开发研究与设计技术·文章编号:1000—3428(2005)16—0202—03文献标识码:A中图分类号:TP302浮点加/减法是数字信号处理中的一个非常频繁并且非常重要的操作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的快速加法器的设计与实现赵亚威1吴海波2(1.沈阳理工大学,辽宁沈阳 110045;2.东北大学,辽宁沈阳 110004)E-mail: hb_0427@摘要:加法器是算术运算的基本单元,可以有多种实现结构,采用不同的结构实现其耗用的资源和运算的速度也各不相同。

本文研究了基于FPGA的常用加法器的结构及其设计方法,对各自性能加以分析比较,在此基础上采用流水线结构设计了一个8bit的加法器。

并在Xilinx 公司的ISE 5.2i 软件环境下, 采用VHDL和Verilog HDL 硬件描述语言进行了设计实现并使用Modelsim进行仿真验证,在此基础上对其性能进行了比较分析。

实验结果表明流水线加法器的速度高于其它结构实现的加法器。

关键词:加法器、进位、FPGA、Verilog HDL、流水线1. 引言算术逻辑单元(ALU) 不仅能完成算术运算也能完成逻辑运算,是微处理器芯片中的一个十分重要的部件[3]。

但是所有基本算术运算(加、减、乘、除)最终都可归结为加法运算,所以加法运算的实现显得尤为重要。

对于多位加法操作来说,因为存在进位问题,使得某一位计算结果的得出与所有低于它的位都相关。

为了减少进位传输所耗费的时间,提高计算速度,人们设计了多种类型的加法器,提出了很多实现加法器的设计方法,如行波进位加法器、快速行波进位加法器、超前进位加法器等。

以上提到的都是并行加法器,此外还有串行加法器,其具有占用资源少、设计灵活等优点。

2. 常用加法器设计方法的分析比较并行加法器中全加器的位数与操作数的位数相同,可同时对操作数的各位相加。

影响运算速度的主要是传递进位信号的逻辑线路(即进位链)。

接下来就上面提到的几种并行加法器加以分析比较。

2.1 行波进位加法器N位行波进位加法器是将N个一位全加器串联进行两个N位数的相加,进位是采用串行进位的方法来实现的,即本级的C out作为下一级的C in参与下一位的加法运算[3]。

这种加法器结构简单,但速度较慢,从其逻辑表达式: Sum i = A i⊕B i⊕C i,C i + 1 =A i B i + C i(A i⊕B i)可以看- 1 -出,串行进位链的总延迟时间与字长成正比,字长越长,延迟时间就越长。

假设每一级全加器的延迟时间为dt ,则N位加法器的进位总延迟为Ndt。

所以高性能设计中一般不用这种结构的加法器。

2.2 快速行波进位加法器从Xilinx公司的Virtex-E器件的结构可以发现,虽然行波进位加法器由于速度太慢一般不被IC设计采用,但是在这种可编程逻辑器件上,行波进位加法器由于结构最为工整,占用资源少,且速度能够满足较多应用的需求,是最适宜实现的结构形式[4]。

每一个Virtex-E的CLB包含两个SLICE,每个SLICE由两个LC构成,在每个SLICE中都有专用进位逻辑,从而为高速算术功能提供快速的算术进位能力[2]。

算术逻辑中包括一个异或门,使每个LC单元可以实现一个一位全加器。

与传统的全加器相比,它在结构上有一些适当的调整,这样一方面缩短了进位传递的时间(约为组合逻辑输出的10%),另一方面又可以在低级进位到达时,更快速地输出该位的和运算结果。

此外,在FPGA内部同一列的两个SLICE间,还专门为进位传递保留了一条最短连线。

正是基于这样的一种结构,Virtex-E器件可以实现快速的行波进位加法器:16位的行波进位加法器寄存器输入到输出的响应时间为4.3ns,64位的行波进位加法器为6.3ns[4]。

2.3 超前进位加法器影响加法器速度的关键因素是进位信号产生和传递的时间,所以要想提高加法器的速度,就必须尽可能的缩短进位时间,即改进进位方式[3]。

超前进位加法器的特点是各级进位信号同时产生,大大减少了进位产生的时间。

在加法器进位计算的表达式C i + 1 = A i B i + C i(A i⊕B i)中,令P i = A i⊕B i ,G i = A i B i ,则有C i + 1 = G i + C i P i 。

各位进位产生的逻辑表达式可写为:C1 = G1 + P1C0C2 = G2 + P2G1 + P2P1C0C3 = G3 + P3G2 + P3P2G1 + P3P2P1C0…从上面的表达式可知:所有位的进位都不依赖低位的进位,每一位的进位只依赖于输入的A、B 和C0 ,可以同时产生。

若不考虑G i和P i的形成时间,则N位超前进位加法器的进位总延迟为dt ,与字长无关。

但随着加法器位数的增加,C i的表达式会越来越长,电路结构会越来越复杂,而且将受到元器件扇入系数的限制,所以完全采用并行进位是不可能的,实际上通常采用分组并行进位来实现。

即把N位字长分为许多小组(每组通常4 位),在组内实现超前进位,在组间既可采用行波进位,也可采用超前进位。

一般地,把组内采用超前进位,组间行波进位的方式称为单级超前进位加法器;把组内、组间均采用超前进位的方式称为多级超前进位加法器[3]。

2.4 高速串行加法器串行加法器利用多个时钟周期完成一个完整的加法运算,从而使占用的资源大幅度减少。

为了使数字串行加法器具有更广泛的应用范围,设计的关键是要使电路达到尽可能高的工作频率,以取得高的数据吞吐量,从而满足系统其它部分的速度要求。

在数字串行加法器中,字长为W的操作数被分为P个位宽为N(N能被W整除,P=W/N)的数字,然后从低位开始相加,- 2 -在P个时钟内完成加法操作。

P个时钟周期称为一个采样周期。

以N=2的数字串行加法器为例,如果输入操作数的字长为8那么串行加法器可以在4个时钟周期内完成加法运算。

这个加法器只用了两个全加器的资源,比一般的8bit行波进位加法器小。

数字串行加法器的控制也比较简单,输入移位寄存器完成并行—>串行转换功能,通过移位操作不断为加法器提供位宽为N 的操作数,输出移位寄存器完成串行—>并行转换,输出计算结果。

对于特定的输入字长,通过选择不同的N可以实现速度、面积不同的数字串行加法器。

这样,设计者可以根据实际情况加以选择,提高了设计的灵活性[5]。

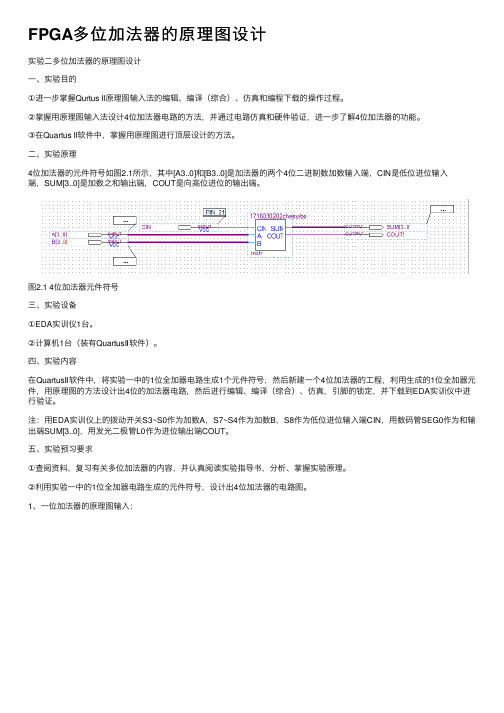

3. 采用流水线结构实现的快速加法器3.1 流水线结构流水线的作用是提高硬件部件的使用率,减少指令的平均执行时间,从而增强了处理器的处理能力。

流水线的流水线深度是指流水线中总的流水线的数目,也就是处理器可以并行处理多少条指令。

流水线的每一个阶段称为流水步、流水步骤、流水段、流水线阶段、流水功能段、功能段、流水级、流水节拍等。

一个流水阶段与另一个流水阶段相连形成流水线。

指令从流水线一端进入,经过流水线的处理,从另一端流出。

在流水线的每一个功能部件的后面都要有一个缓冲器,称为锁存器、闸门寄存器等它的作用是保存本流水段的执行结果。

图1是一个三级流水线操作的示意图[1],在第N个指令取指时,前面一个(即第N-1个)指令正在译码,而第N-2个指令则正在执行。

图1 三级流水操作3.2 基于流水线结构的加法器并行加法器速度快,只有一级门延时,对于实现4位以下的加法器比较合适[2]。

FPGA中每个逻辑单元规模小,其中实现组合逻辑的为4到5变量的查找表(LUT),当增加并行加法器的位数时,将受到查找表容量的限制,但是FPGA中具有上千个触发器,资源丰富,因此可以考虑在FPGA的设计中采用流水线结构,充分利用丰富的触发器资源从而大大提高加法器的工作速度。

流水线结构将每一步运算都用寄存器暂存,尽管单个运算需要多个时钟周期才能得出结果,但由于操作数是不断加到运算输入端的,所以总的效果是每个加法运算平均耗费的时间等于锁存时钟的周期,即加法器的速度只受时钟速度的限制。

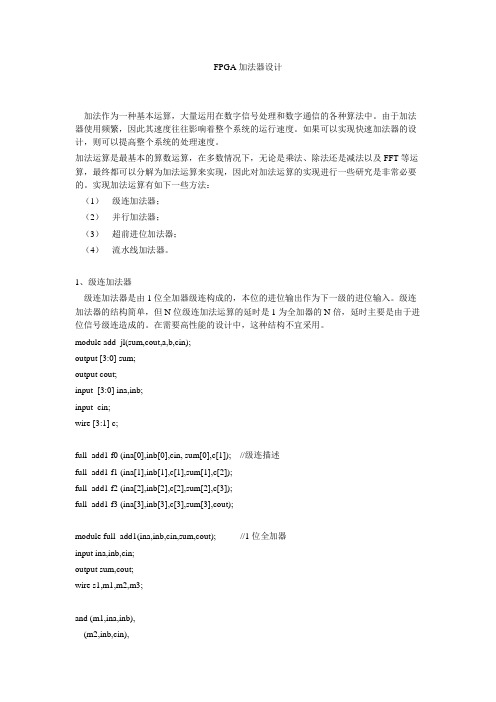

3.3 流水线加法器的实现在ISE中使用Verilog HDL语言实现了一个8位加法器,分别采用了2级和4级流水线结构进行设计,下面分别给出了8位加法器的2级和4级流水线结构图:- 3 -图2 2级流水线8位加法器结构图3 4级流水线8位加法器结构[1]在ISE中进行选用Virtex-E器件xcv50e进行综合、翻译、映射和布局布线,最后通过Modelsim进行仿真验证。

在实现过程中还通过约束编辑器对该设计加以全局约束,从而获得更高的速度。

实验结果表明对于2级流水线设计,占用SLICE数为9(1%)个,允许的最大时钟频率为202.388MHz;对于4级流水线设计,占用SLICE数为24(3%)个,允许的最大时钟频率为240.732MHz。

可见,流水深度越大加法器的速度越高,但速度的提高是以牺牲资源为代价的[2],性能(速度)和开销(资源消耗)是一对矛盾[6], 如何设计器件以提高性价比才是我们首要解决的问题。

在2级流水线设计中布线延迟和逻辑延迟所占比重基本是各50%左右,而4级流水线设计中布线延迟所占的比重已经上升到60%,因此应当注意:虽然所采用的流水线加法器流水深度同运算速度在一定程度上是成正比的,但是随着流水深度的增加,布线延迟在总的延迟中所占的比重越来越大,逻辑延迟所占比重逐渐变小,总的延迟不一定减小,而资源耗费却会迅速增加[6]。

- 4 -4. 结束语本文对于应用FPGA器件进行加法运算设计进行了有益的探索,研究了几种常用的基于FPGA的加法器的实现结构,并着重讨论了基于流水线结构的加法器,对于流水线深度不同的加法器分别进行了仿真验证。

通过试验结果得出流水深度并不是永远正比于运算速度,并且随着流水深度的增加资源耗费却会迅速增加的结论。

当然我们在设计器件时应针对具体问题进行分析,根据系统的特定要求来合理地选择不同加法器以达到提高系统性能的目的。

参考文献[1] 王金明,杨吉斌.数字系统设计与Verilog HDL[M].北京:电子工业出版社,2002 236-239[2] 徐志军,徐光辉.CPLD/FPGA的开发与应用[M].北京:电子工业出版社,2002 236-240[3] 安印龙,许琪等. 并行加法器的研究与设计[J].西安:晋中师范高等专科学校校报,2003,20(4):330-334[4] 杨靓,徐炜等. FPGA上浮点加/减法器的设计[J].计算机工程与应用,2003,(2):24-25[5] 钟信潮,薛小刚等. 高速数字串行加法器及其应用[J].电子技术应用,2004,(1):60-62[6] 伞景辉,常青. 基于FPGA 的乘法器实现结构分析与仿真[J].微处理机,2004,(3):3-7The Design and Implementation of High-Speed AdderBased on FPGAZhao Yawei1 , Wu Haibo2(1.ShenYang University of Technology,LiaoNing Shenyang 1100452.Northeastern University, LiaoNing Shenyang 110004)Abstract: Adder is the basic cell of arithmetic operation, many structures can be used to implement it, and the adder designed by different method consumes different number of resource and has a different speed respectively. This paper studies the structures and methods of adder based on the FPGA, analyses and compares the performance of each adders, moreover design an 8 bits adder based on the structure of pipeline. Carry out it by utilizing the Hard Describe Language (VHDL and Verilog HDL) and ISE software package V5. 2i from Xilinx and simulate it by Modelsim software, and evaluation and comparison the performance (area and speed) of it. The result of experiment indicates that the pipeline adder is faster others. Keywords: Adder,Carry,FPGA,Verilog HDL,Pipelining作者简介:赵亚威,女,1976年出生,沈阳工业学院应用技术学院教师,在读硕士,研究方向电工理论新技术- 5 -吴海波,男,1978年出生,东北大学在读硕士,研究方向,大规模可编程逻辑器件设计- 6 -。