实验三 双端口实验内容

试验三三点法测量二端口微波网络的散射参数

实验三 三点法测量二端口微波网络的散射参数一、 实验目的和意义双口网络参数的测量是在单口网络的基础上进行的,同时双口网络测量又是多口网络测量的基础,具有承上启下的作用。

实验要求掌握用三点法测量微波网络的散射参数的方法,为进一步学习微波网络测量打好基础。

二、实验原理和方法微波网络与参量的求法可以用计算法亦可用实验法,但计算法仅限于解决简单网络,对于复杂的网络,其S 参数的确定要用实验法。

所谓三点法是指必须的测量为3次,由3次测得的数据便可求得双口网络的全部参数。

这是因为互易双口网络只有三个参数是独立的。

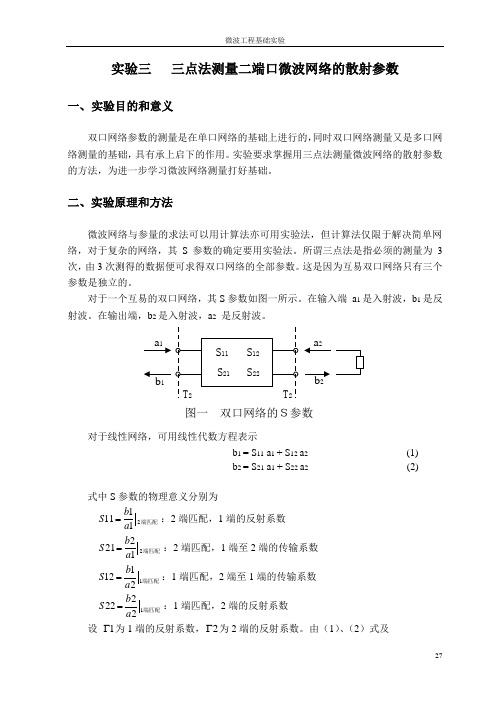

对于一个互易的双口网络,其S 参数如图一所示。

在输入端 a 1是入射波,b 1是反射波。

在输出端,b 2是入射波,a 2 是反射波。

图一 双口网络的S参数对于线性网络,可用线性代数方程表示b 1 = S 11 a 1 + S 12 a 2 (1)b 2 = S 21 a 1 + S 22 a 2 (2)式中S 参数的物理意义分别为21111b S a =端匹配:2端匹配,1端的反射系数 22211b S a =端匹配:2端匹配,1端至2端的传输系数 11122b S a =端匹配:1端匹配,2端至1端的传输系数 12222b S a =端匹配:1端匹配,2端的反射系数设 1Γ为1端的反射系数,2Γ为2端的反射系数。

由(1)、(2)式及11,1b a Γ=222a b Γ= 对于互易网络 S 12 = S 21 由此得到22111121222S S S ΓΓ=+-Γ (3)在(3)式中有三个未知数S 11、S 22 和S 12。

如果能分别测出网络输出端短路、开路和匹配时,网络输入端的反射系数Γ1S 、Γ10和1L Γ可由(3)式求得三个未知数。

2端开路时 21Γ=+1端的反射系数 2121011122S S S Γ=+- (4)2端短路时 21Γ=-1端的反射系数 212111122S S S S Γ=-+ (5)2端匹配时 20Γ=1端的反射系数 111L S Γ= (6) 由(4)、(5)、(6)式得2111022110L S S S Γ-Γ-Γ=Γ-Γ (7)由(5)式得()()21222111S S L S =+Γ-Γ (8)如果网络是对称的,则S 11=S 22,只要进行两次测量,例如一次短路,一次开路。

计算机组成原理双端口存储器实验报告

计算机组成原理实验报告实验名称双端口存储器实验专业软件工程学院计算机与软件学院姓名徐振兴班级(2)学号20111344069 指导老师任勇军实验日期2013.5.24 得分一、实验类别原理性+分析性二、实验目的⑵了解双端口静态存储器IDT7132的工作特性及其使用方法;⑵了解半导体存储器怎样存储和读取数据;⑶了解双端口存储器怎样并行读写;⑷熟悉TEC-8模型计算机中存储器部分的数据通路。

三、实验设备⑴TEC-8 实验系统1台⑵双踪示波器1台⑵直流万用表1块⑷逻辑测试笔(在TEC-8 实验台上) 1 支四、实验电路双端口RAM 电路由1 片IDT7132 及少许附加电路组成,存放程序和数据。

IDT7132 有2 个端口,一个称为左端口,一个称为右端口。

2 个端口各有独立的存储器地址线、数据线和3 个读、写控制信号: CE#、R/W#和OE#,可以同时对器件内部的同一存储体同时进行读、写。

IDT7132 容量为2048 字节,TEC-8 实验系统只使用64 字节。

在TEC-8 实验系统中,左端口配置成读、写端口,用于程序的初始装入操作,从存储器中取数到数据总线DBUS,将数据总线DBUS 上的数写入存储器。

当信号MEMW 为1 时,在T2 为1 时,将数据总线DBUS 上的数D7~D0 写入AR7~AR0 指定的存储单元;当MBUS 信号为1 时,AR7~AR0 指定的存储单元的数送数据总线DBUS。

右端口设置成只读方式,从PC7~PC0 指定的存储单元读出指令INS7~INS0,送往指令寄存器IR。

程序计数器PC 由2 片GAL22V10(U53 和U54)组成。

向双端口RAM 的右端口提供存储器地址。

当复位信号CLR#为0 时,程序计数器复位,PC7~PC0 为00H。

当信号LPC 为1 时,在T3 的上升沿,将数据总线DBUS 上的数D7~D0 写入PC。

当信号PCINC 为1 时,在T3 的上升沿,完成PC 加1。

双端口存储器实验报告

双端口存储器实验报告实验目的:1.了解双端口存储器的结构和工作原理。

2.掌握Verilog HDL语言的基本应用。

3.掌握ModelSim软件的使用方法。

实验内容:双端口存储器是指具有两个读写口的存储器,它可以通过一个端口写入数据,同时通过另一个端口读出数据,常用于数字信号处理、图像处理等领域。

本实验将通过Verilog HDL语言编写程序,使用ModelSim软件进行仿真验证,实现一个简单的双端口存储器。

具体实验内容如下:2.编写Verilog HDL程序实现简单的双端口存储器。

在程序中,定义数据存储器、读写使能信号、读写数据等变量,并利用always语句实现对数据的读写操作。

3.使用ModelSim软件进行仿真验证。

在ModelSim中创建项目,导入设计文件和仿真波形文件,进行波形仿真,验证程序的正确性。

实验步骤:双端口存储器是指具有两个读写口的存储器,其中一个读写口用于读写存储器内部的数据,另一个用于与外部系统交换数据。

在双端口存储器的结构中,存储器数据的读写可以同时进行,而无需互斥。

在读数据端口和写数据端口的操作中,存在两个读写控制信号,一个是读写使能信号,用于控制读写操作是否有效;另一个是写使能信号,用于控制数据写入操作的触发。

2.编写Verilog HDL程序实现简单的双端口存储器。

module dual_port_memory (input clk,input [3:0] addr1,input [3:0] addr2,input [7:0] data_in,input rd_en1,input rd_en2,input wr_en,output [7:0] data_out1,output [7:0] data_out2);reg [7:0] mem[0:15]; // 定义存储器数组// 读写操作always @(posedge clk) beginif (wr_en) // 写操作mem[addr1] <= data_in;else if (rd_en1) // 读操作1data_out1 <= mem[addr1];else if (rd_en2) // 读操作2data_out2 <= mem[addr2];endendmodule在程序中定义了一个16位的存储器数组mem。

实验三流水灯实验(io口和定时器实验)

实验三流水灯实验(I/O口和定时器实验)一、实验目的1.学会单片机I/O口的使用方法和定时器的使用方法;2.掌握延时子程序的编程方法、内部中断服务子程序的编程方法;3.学会使用I/O口控制LED灯的应用程序设计。

二、实验内容1.控制单片机P1口输出,使LED1~LED8右循环轮流点亮(即右流水),间隔时间为100毫秒。

2.控制单片机P1口输出,使LED1~LED8左循环轮流点亮(即左流水),间隔时间为100毫秒。

3.使用K1开关控制上面LED灯的两种循环状态交替进行;4. 用定时器使P1口输出周期为100ms的方波,使LED闪烁。

5.使用定时器定时,使LED灯的两种循环状态自动交替,每一种状态持续1.6秒钟(选作)。

三、实验方法和步骤1.硬件电路设计使用实验仪上的E1、E5和E7模块电路,把E1区的JP1(单片机的P1口)和E5区的8针接口L1~L8(LED的驱动芯片74HC245的输入端)连接起来,P1口就可以控制LED 灯了。

当P1口上输出低电平“0”时,LED灯亮,反之,LED灯灭。

E7区的K1开关可以接单片机P3.0口,用P3.0口读取K1开关的控制信号,根据K1开关的状态(置“1”还是置“0”),来决定LED进行左流水还是右流水。

综上,画出实验电路原理图。

2.程序设计实验1和实验2程序流程图如图3-1实验3程序流程图如图3-2所示。

图3-1 实验1,2程序流程图图3-2 实验3程序流程图实验4程序流程图如图3-3,3-4所示。

实验5程序流程图如图3-5,3-6所示。

图3-5 实验5主程序流程图图3-6 定时器中断服务子程序流程图图3-4 定时器中断服务子程序流程图图3-3 实验4主程序流程图编程要点:(1)Pl,P3口为准双向口,每一位都可独立地定义为输入或输出,在作输入线使用前,必须向锁存器相应位写入“1”,该位才能作为输入。

例如:MOV P1,A; P1口做输出MOV P1,#0FFHMOV A,P1;P1口做输入SETB P3.0MOV C,P3.1;从P3.1口读入数据(2)每个端口对应着一个寄存器,例:P1→90H(P1寄存器地址);P3→B0H(P3寄存器地址);寄存器的每一位对应着一个引脚,例:B0H.0→P3.0(3)对寄存器写入“0”、“1”,对应的外部引脚则输出“低电平”、“高电平”。

实验4:双端口存储器实验 ----独立方式

河北环境工程学院

《计算机组成原理》实验报告

作者:

系(部):

专业班级:

学号:

成绩:__________________

评阅教师:__________________

年月日

一、实验目的

1、了解双端口静态存储器IDT7132的工作特性及其使用方法;

2、了解半导体存储器怎样存储和读取数据;

3、了解双端口存储器怎样并行读写;

4、熟悉LK-TEC-9模型计算机存储器部分的数据通路;

二、预习内容

1.掌握双端口存储器的使用方法

2. 掌握TEC-8模型计算机存储器的部分的数据通路

三、实验环境及主要器件

1.TEC-8实验系统 1台

2. 逻辑测试笔 1支

3. 双踪示波器 1台

4. 逻辑测试笔 1支

四、实验内容

1、从存储器地址10H开始,通过左端口连续向双端口RAM中写入3个数:85H,60H,38H。

在写的过程中,在右端口检测写的数据是否正确。

2、从存储器地址10H开始,连续从双端口RAM的左端口和右端口同时读出存储器的内容。

五、实验步骤

六、实验结果分析与讨论。

双端口存储器原理实验报告

双端口存储器原理实验报告一、实验内容、方法和步骤1.接线IAR_BUS 接 GND,ALU_BUS 接 GND,RS_BUS 接GND,禁止中断地址寄存器、运算器、多端口寄存器堆 RF 向数据总线 DBUS 送数据。

AR1_INC 接GND,M3 接 VCC,使地址寄存器 AR1 和 AR2 从数据总线 DBUS 取得地址数据。

信号IAR_BUSALU_BUSRS_BUSAR1_INC M3开关GND GND GND GND VC C信号LDIRSW_BUSLDAR2LDAR1 CER LRW CEL开关K6 K5 K4 K3 K2 K1 K0 2.置 DP = 1,DB = 0,DZ = 0,使实验台处于单拍状态。

工作模式开关=“脱机”合上电源。

按复位按钮 CLR#,使实验系统处于初始状态。

置 DP = 1,DB = 0,DZ = 0,使实验台处于单拍状态。

工作模式开关=“脱机”合上电源。

按复位按钮 CLR#,使实验系统处于初始状态。

(1)写地址寄存器 AR1=00信号SW7~0 LDIRSW_BUSLDAR2LDAR1 CER LRW CEL开关K6 K5 K4 K3 K2 K1 K0状 态 / 00H 0 1 0 1 0 0 0 值 按一次 QD ,将 00H 写入 AR1。

(2)向存储器 00H 地址写数 00H 信 SW7~0 LDIR SW_B US LDAR 2 LDAR 1 CER LRW CEL 号 开关 K6 K5 K4 K3 K2 K1 K0 状 态 / 00H 0 1 0 0 0 0 1 值 按一次 QD ,将 00H 写入存储器 00H 地址。

(3)写地址寄存器 AR1=10 信号 SW7~0 LDIR SW_B US LDAR 2 LDAR 1 CER LRW CEL 开关 K6 K5 K4 K3 K2 K1 K0 状 态 / 10H 0 1 0 1 0 0 0 值按一次 QD ,将 10H 写入 AR1。

计算机组成原理实验报告

实验1 通用寄存器实验一、实验目的1.熟悉通用寄存器的数据通路。

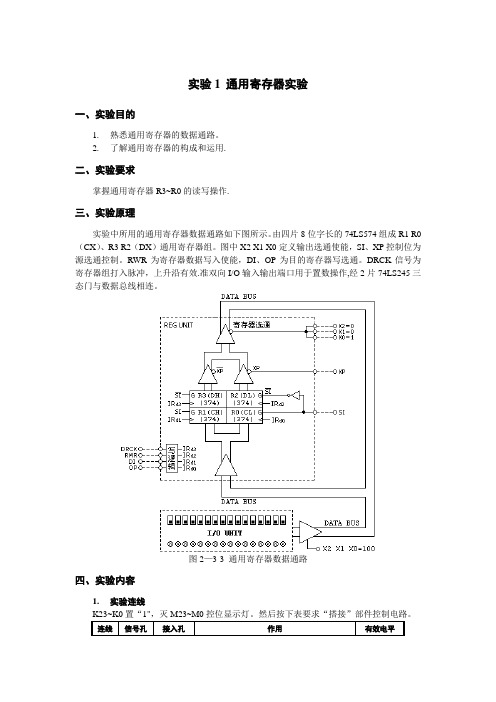

2.了解通用寄存器的构成和运用.二、实验要求掌握通用寄存器R3~R0的读写操作.三、实验原理实验中所用的通用寄存器数据通路如下图所示。

由四片8位字长的74LS574组成R1 R0(CX)、R3 R2(DX)通用寄存器组。

图中X2 X1 X0定义输出选通使能,SI、XP控制位为源选通控制。

RWR为寄存器数据写入使能,DI、OP为目的寄存器写选通。

DRCK信号为寄存器组打入脉冲,上升沿有效.准双向I/O输入输出端口用于置数操作,经2片74LS245三态门与数据总线相连。

图2—3-3 通用寄存器数据通路四、实验内容1.实验连线连线信号孔接入孔作用有效电平2.寄存器的读写操作①目的通路当RWR=0时,由DI、OP编码产生目的寄存器地址,详见下表.通用寄存器“手动/搭接”目的编码②通用寄存器的写入通过“I/O输入输出单元”向R0、R1寄存器分别置数11h、22h,操作步骤如下:通过“I/O输入输出单元”向R2、R3寄存器分别置数33h、44h,操作步骤如下:③源通路当X2~X0=001时,由SI、XP编码产生源寄存器,详见下表.通用寄存器“手动/搭接”源编码④ 通用寄存器的读出关闭写使能,令K18(RWR )=1,按下流程分别读R0、R1、R2、R3。

五、实验心得通过这个实验让我清晰的了解了通用寄存器的构成以及通用寄存器是如何运用的,并且熟悉了通用寄存器的数据通路,而且还深刻的掌握了通用寄存器R3~R0的读写操作。

实验2 运算器实验一、实验目的掌握八位运算器的数据传输格式,验证运算功能发生器及进位控制的组合功能.二、实验要求完成算术、逻辑、移位运算实验,熟悉ALU 运算控制位的运用.三、实验原理实验中所用的运算器数据通路如图2-3—1所示。

ALU 运算器由CPLD 描述。

运算器的输出FUN 经过74LS245三态门与数据总线相连,运算源寄存器A 和暂存器B 的数据输入端分别由2个74LS574锁存器锁存,锁存器的输入端与数据总线相连,准双向I/O 输入输出端口用来给出参与运算的数据,经2片74LS245三态门与数据总线相连。

实验三P3.3口输入.P1口输出

实验三 P3.3 口输入 .P1 口输出

一、实验目的

1、学习MCS-51指令系统的使用。 2、学习汇编语言程序的设计和调试方法 3、掌握P3口、P1口简单使用。 4、学习延时程序的编写和使用。

二、实验内容

1、阅读分析并掌握实验原理图。 2、编写并调试程序,下载程序到开发装置。 3、P3口做输入口,外接一脉冲,每输入一个脉冲,P1口

个机器周期时间长度12/6.0MHZ为2微秒,所以该段指令 执行时间为:(248*2+4 )*200+4=100ms。

四、程序框图

五、实验电路

六、实验步骤

1、P3.3用插针连至K1,P1.0—P1.7用插针连至L1—L8。 2、编辑程序并将程序下载到实验装置,然后连续运行程

序。 3、开关K1每拨动一次,L1—L8发光二极管按16进制方式

加一点亮。

按十六进制加一。 4、P1口做输出口,编写程序,使P1口接的8 个发光二极

管L1—L8按16进制加一方式点亮发光二极管。

三、实验说明

• 1.P3口是准双向口,它作为输出口时与一般的双向口使 用方法相同,由准双向口结构可知:当P3口作为输入口 时,必须先对它置高电平,使内部MOS管截止,因内部上 拉电阻是20KΩ—40KΩ,故不会对外部输入产生影响。 若不先确的。

双端口存储器实验

院7•实T验EC中ห้องสมุดไป่ตู้心8 系统结构实验室

六、实验步骤 ㈠独立方式 1 .将存储器模块的外部连线按参考接线,

将控制器转换开关拨到独立位置,“独立” 灯亮, 将编程开关设置为正常位置,将开关 DP拨到向上位置。打开电源。 2 .系统复位,设置存储器地址,通过左端 口写入数据,并通过左、右端口读出检测写 入的数据是否正确。

双端口存储器实验

院2•实T验EC中-心8 系统结构实验室

三、实验设备 TEC-8实验系统 1台 TDS1001数字存储示波器 1台 UT60A数字万用表 1块 逻辑测试笔(在TEC-8实验台上) 1支 四、实验电路

院3•实T验EC中-心8 系统结构实验室

院4•实T验EC中-心8 系统结构实验室

㈡微程序方式 1.将控制器转换开关拨到微程序位置,将

编程开关设置为正常位置。打开电源。 2.进行存储器读、写实验。 ⑴设置存储器读、写实验模式 ⑵设置存储器地址 ⑶依次写入第1、2、3个数 ⑷重新设置存储器地址 ⑸左、右两2个端口同时显示同一个存储器

单元的内容。

••00•5AA5AA •K1 ••10HHH 2•K1 •0•1

1

•0AA H

•K1 •1•0 •0K •0 9

•K •10 8

•55 H

•0•5A5A HH •0•5A5A HH

•0AA H

•55 H

•0AA H

•GN •0•1 •D0•3•KK11

4

•10•K1 5

院0•实T验EC中-心8 系统结构实验室

院5•实T验EC中-心8 系统结构实验室

院6•实T验EC中-心8 系统结构实验室

五、实验任务 1.从存储器地址10H开始,通过左端口连

双端口存储器实验步骤

双端口存储器实验步骤一、实验目的双端口存储器是一种非常重要的存储器类型,本实验旨在通过实际操作了解双端口存储器的工作原理和应用。

二、实验原理双端口存储器是指具有两个独立的数据输入/输出端口的存储器。

其中一个端口可以用于读取和写入数据,而另一个端口只能用于读取数据。

双端口存储器通常用于需要高速并发访问的应用中,例如视频处理、音频处理等。

三、实验设备1. FPGA开发板2. Quartus II软件3. 双端口RAM芯片四、实验步骤1. 设计电路图首先,需要使用Quartus II软件设计电路图。

在电路图中添加一个双端口RAM模块,并将其连接到FPGA开发板上。

确保电路图正确无误,并生成可编程文件。

2. 编写Verilog代码接下来,需要编写Verilog代码来控制RAM模块的读写操作。

代码需要包括以下内容:- 地址信号:用于指定要访问的内存地址。

- 数据信号:用于传输要写入或读取的数据。

- 读/写信号:用于指定当前操作是读还是写。

- 时钟信号:用于同步各个模块之间的操作。

3. 烧录可编程文件将生成的可编程文件烧录到FPGA开发板上,确保烧录成功。

4. 进行测试使用示波器等测试工具,对RAM模块进行读写测试。

确保数据能够正常读取和写入,并且能够在不同端口之间进行并发访问。

五、实验注意事项1. 在设计电路图和编写代码时,需要仔细阅读芯片的数据手册,并按照要求正确配置各个信号。

2. 在进行测试时,需要注意时钟信号的频率和稳定性,以确保数据传输的准确性。

3. 如果出现问题,应该及时检查电路图、代码和硬件连接,并进行排查。

实验二双端口存储器原理实验

实验二双端口存储器原理实验实验目的:1.了解双端口存储器的工作原理;2.了解双端口存储器的读写时序;3.掌握双端口存储器的控制方式。

实验器材:1.双端口RAM芯片;2.数字逻辑实验箱;3.示波器。

实验原理:双端口存储器是一种具有两个访问端口的存储器,其中一个端口用于读数据,另一个端口用于写数据。

两个端口可以同时进行读写操作,且可以独立操作,互不干扰。

双端口存储器广泛应用于多核处理器、高速路由器、交换机等领域,其性能优越,能提供更高的并行处理能力。

双端口存储器的读写时序如下:1.读操作时序:1)使能端CE1置低,选中读数据的端口;2)地址信号输入地址端口AD1;3)等待一段时间,取数据端口的读数据。

2.写操作时序:1)使能端CE2置低,选中写数据的端口;2)地址信号输入地址端口AD2;3)数据输入数据端口D;4)等待一段时间,完成写操作。

实验步骤:1.连接双端口RAM芯片到数字逻辑实验箱上,确保电路连接正确;2.连接示波器到仪表箱,用于监测信号波形;3.按照双端口存储器的读写时序,设置实验箱上的信号发生器;4.编写控制代码,控制实验箱上的信号发生器模拟读写操作;5.观察示波器上的波形,验证读写操作的正确性;6.分析实验结果,总结双端口存储器的工作原理和性能。

实验注意事项:1.操作实验箱时要小心谨慎,防止损坏实验箱和芯片;2.实验过程中需要观察示波器上的波形,确保信号发生器的设置正确;3.根据实验目的和步骤设定实验结果的收集和分析方式;4.实验后及时关闭实验箱和示波器,保持实验室整洁。

实验结果与分析:根据实验步骤设置好实验箱上的信号发生器,并编写相应的控制代码后,进行实验。

通过示波器监测到的信号波形可以验证读写操作的正确性。

实验结果的收集和分析主要包括以下内容:1.读操作时序的验证:通过示波器观察到CE1端信号在读操作开始时置低,地址信号AD1输入正确,数据端口读数据正确。

2.写操作时序的验证:通过示波器观察到CE2端信号在写操作开始时置低,地址信号AD2输入正确,数据端口D输入正确。

实验三P3.3口输入、P1口输出实验

实验三 4.1 P3.3口输入、P1口输出实验系别专业:电子系12级电信2班学号:3121003210姓名:李书杰指导老师:刘志群老师4.1.1 实验要求1. 复习Keil C51调试硬件的操作方法。

2. 复习单片机作为通用I/O口的注意事项。

3. 复习单片机操作I/O口的程序设计方法。

4.1.2 实验设备PC 机一台,TD-NMC+教学实验系统4.1.3 实验目的1. 熟悉单片机仿真实验软件Keil C51调试硬件的方法。

2. 了解P3、P1口作通用I/O口的使用方法。

3. 掌握延时子程序的编写和使用方法。

4. 了解单片机对简单I/O的扩展方法。

4.1.4 实验内容实验1根据TD-NMC+实验平台的单元电路,构建一个硬件系统,并编写实验程序实现如下功能:将P1口的低4位定义为输出,高4位定义为输入,数字量从P1口的高4位输入,从P1口的低4位输出控制发光二极管的亮灭。

程序如下:KEY:MOV P1,#0F0H ;令所有行为低电平KEY1:MOV R7,#0FFH ;设置计数常数DJNZ R7,KEY1 ;延时MOV A, P1 ;读取P1口的列值ANL A,#0F0H ;判别有键值按下吗?CPL A ;求反后,有高电平就有键按下JZ EKEY ;无键按下时退出LCALL DEL20 ms ;延时20 ms去抖动SKEY:MOV A,#00 ;下面进行行扫描,1行1行扫MOV R0,A ;R0作为行计数器,开始为0MOV R1,A ;R1作为列计数器,开始为0MOV R3 #0FEH ;R3暂存行扫描字,低4位为行扫描字SKEY2:MOV A,R3MOV P1,A ;输出行扫描字,高4位全1NOPNOPNOPMOV A,P1 ;读列值MOV R1,A ;暂存列值ANL A,#0F0H ;取列值CPL A ;高电平则有键闭合S123:JNZ SKEY3 ;有键按下转SKEY3INC R0 ;行计数器加1SETB C ;准备将行扫描左移1位,;形成下一行扫描字,C=1保证输出行扫描字中高4位全为1,;为列输入作准备,低4位中只有1位为0MOV A,R3 ;R3带进位C左移1位RLC AMOV R3,A ;形成下一行扫描字→R3MOV A,R0CJNE A,#04H,SKEY1 ;最后一行扫(4次)完了吗?EKEY:RET;列号译码SKEY3:MOV A,R1JNB ACC.4,SKEY5JNB ACC.5,SKEY6JNB ACC.6,SKEY7JNB ACC.7,SKEY8AJMP EKEYSKEY5:MOV A,#00HMOV R2,A ;存0列号AJMP DKEYSKEY6:MOV A,#01HMOV R2,A ;存1列号AJMP DKEYSKEY7:MOV A,#02HMOV R2,A ;存2列号AJMP DKEYSKEY8:MOV A,#03HMOV R2,A ;存3列号AJMP DKEY;键位置译码DKEY:MOV A,R0 ;取行号ACALL DECODEAJMP EKEY;键值(键号)译码DECODE:MOV A,R0 ;取行号送AMOV B,#04H ;每一行按键个数MUL AB ;行号×按键数ADD A,R2 ;行号×按键数+列号=键值RET实验2根据TD-NMC+实验平台的单元电路,构建一个硬件系统,并编写实验程序实现如下功能:将P3.3口作状态输入口(接一个逻辑开关,即拨码开关),P1口做输入口(接八只发光二极管D0~D7)。

计算机网络技术实验指导书

计算机网络技术实验指导书一、实验目的计算机网络技术实验是计算机相关专业课程的重要实践环节,旨在帮助学生深入理解计算机网络的基本原理、技术和应用,培养学生的实践能力、创新能力和解决实际问题的能力。

通过本实验课程,学生将能够掌握计算机网络的组建、配置、管理和维护等方面的技能,为今后从事计算机网络相关工作打下坚实的基础。

二、实验环境1、硬件环境计算机:若干台,配置要求不低于英特尔酷睿 i5 处理器、8GB 内存、500GB 硬盘。

网络设备:交换机、路由器、防火墙等。

网线、水晶头、压线钳等网络布线工具。

2、软件环境操作系统:Windows 10、Windows Server 2019 等。

网络模拟软件:Packet Tracer、GNS3 等。

网络管理工具:Wireshark、Sniffer 等。

三、实验内容1、网络拓扑结构的设计与搭建了解常见的网络拓扑结构,如星型、总线型、环型、树型和网状型。

根据给定的需求,设计合理的网络拓扑结构。

使用网络设备和网线,搭建实际的网络拓扑结构。

2、 IP 地址规划与子网划分掌握 IP 地址的分类、格式和表示方法。

学习子网掩码的作用和计算方法。

根据网络规模和需求,进行合理的 IP 地址规划和子网划分。

3、交换机的配置与管理了解交换机的工作原理和基本功能。

学习交换机的配置命令,如VLAN 的创建与配置、端口的设置等。

进行交换机的日常管理和维护,如查看端口状态、MAC 地址表等。

4、路由器的配置与管理掌握路由器的工作原理和路由选择算法。

学习路由器的配置命令,如静态路由、动态路由(RIP、OSPF 等)的配置。

进行路由器的网络连接和数据转发测试。

5、网络服务的配置与应用配置 DNS 服务器,实现域名解析。

配置 DHCP 服务器,为网络中的客户端自动分配 IP 地址。

配置 Web 服务器、FTP 服务器等,提供网络服务。

6、网络安全与管理了解网络安全的基本概念和常见威胁。

配置防火墙,实现网络访问控制。

实验三双音多频DTMF接收实验

实验三双⾳多频DTMF接收实验程控交换原理随堂实验报告学院计算机与电⼦信息学院专业电⼦信息⼯程班级电信xx-x 姓名xxx 学号 11034030xxx指导教师陈信实验报告评分:_______实验三双⾳多频DTMF接收实验⼀、实验⽬的1、了解电话号码双⾳多频信号在程控交换系统中的发送和接收⽅法。

2、熟悉该电路的组成及⼯作过程。

⼆、预习要求1、认真预习有关双⾳多频等相关内容。

三、实验仪器仪表1、主机实验箱⼀台2、电话单机两台3、20MHz⽰波器⼀台实验步骤1.接上交流电源线。

2.将K11~K14,K21~K24,K31~K34,K41~K44接2,3脚;K71~K75接2,3脚;K61~K63接2,3脚,K70、K60接1、2脚。

3.先打开“交流开关”,指⽰发光⼆极管亮后,再分别按下直流输出开关J8、J9,此时实验箱上的五组电源已供电,各⾃发光⼆极管亮。

4.按“复位”键进⾏⼀次上电复位,此时,CPU已对系统进⾏初始化处理,显⽰电路循环显⽰“P”,即可进⾏实验。

5.⽤户1、⽤户3接上电话单机。

6.⽤户1摘机,开始拨打号码,即按电话单机上的任意键,⽤⽰波器的直流档对以下测量点进⾏观察并记录波形:1)TPDTMF:当有键按下时有双⾳多频信号,⽆键按下时⽆信号。

按下1键时图像⽆键按下时图像2)TPSDT:当有键按下时该点是低电平,⽆键按下时该点为⾼电平。

3)TP11:当有键按下时有双⾳多频信号,⽆键按下时⽆信号。

按下1键时图像⽆键按下时图像7.按不同的键时,其双⾳多频信号的波形不⼀样,要仔细观察。

按下2键时TPDTMF图像⽆键按下时TPDTMF图像TPSDT按键2按下与⽆按时图像按下2键时TP11图像⽆键按下时TP11图像8.在按键过程中观察发光⼆极管D103~D100与所按键值的关系:(显⽰⼆极管是在该按键抬起的瞬间发⽣改变的)D103~D100对应的是8421码,如接下的键值为5时,对应的码字为0101,发光⼆极管D102,D100发光。

实验三 数据通路(总线)实验

.实验三数据通路(总线)实验一、实验目的(1)将双端口通用寄存器堆和双端口存储器模块联机;(2)进一步熟悉计算机的数据通路;(3)掌握数字逻辑电路中故障的一般规律,以及排除故障的一般原则和方法;(4)锻炼分析问题与解决问题的能力,在出现故障的情况下,独立分析故障现象,并排除故障。

二、实验电路图8示出了数据通路实验电路图,它是将双端口存储器实验模块和一个双端口通用寄存器堆模块(RF)连接在一起形成的。

双端口存储器的指令端口不参与本次实验。

通用寄存器堆连接运算器模块,本实验涉及其中的操作数寄存器DR2。

由于双端口存储器RAM是三态输出,因而可以将它直接连接到数据总线DBUS上。

此外,DBUS上还连接着双端口通用寄存器堆。

这样,写入存储器的数据可由通用寄存器提供,而从存储器RAM读出的数据也可送到通用寄存器堆保存。

双端口存储器RAM已在存储器原理实验中做过介绍,DR2运算器实验中使用过。

通用寄存器堆RF(U32)由一个ISP1016实现,功能上与两个4位的MC14580并联构成的寄存器堆类似。

RF内含四个8位的通用寄存器R0、RI、R2、R3,带有一个写入端口和两个输出端口,从而可以同时写入一路数据,读出两路数据。

写入端口取名为WR端口,连接一个8位的暂存寄存器(U14)ER,这是一个74HC374。

输出端口取名为RS端口(B端口)、RD端口(A端口),连接运算器模块的两个操作数寄存器DR1、DR2。

RS端口(B端口)的数据输出还可通过一个8位的三态门RS0(U15)直接向DBUS输出。

双端口通用寄存器堆模块的控制信号中,RS1、RS0用于选择从RS端口(B 端口)读出的通用寄存器,RD1、RD0用于选择从RD端口(A端口)读出的通用寄存器。

而WR1、WR0则用于选择从WR端口写入的通用寄存器。

WRD是写入控制信号,当WRD=1时,在T2上升沿的时刻,将暂存寄存器ER中的数据写入通用寄存器堆中由WR1、WR0选中的寄存器;当WRD=0时,ER中的数据不写入通用寄存器中。

实验2双端口存储器原理实验

三、接线1.固定接线RS_BUS#接+5V,禁止寄存器堆RF向DBUS送数。

IAR_BUS#接+5V,禁止中断地址寄存器IAR向DBUS送数。

ALU_BUS接GND,禁止运算器ALU向DBUS输出数据。

AR1_INC接GND,禁止地址寄存器进行AR1+1→AR1操作。

M3接+5V,使地址寄存器AR2从DBUS取得地址数据。

2.其他控制信号线SW_BUS#接K0;CEL接K1;LRW接K2;CER、LDIR接K3;LDAR1接K4;LDAR2接K5。

四、设置功能开关1.先置开关DB=0,DZ=0,DP=1,使系统处于单拍状态(每按一次QD按钮,顺序产生T1、T2、T3、T4各一个脉冲)2.先将IR/DBUS开关拨到DBUS位置;3.先将AR1/AR2开关拨到AR1位置;五.实验操作演示1.使用左端口,向某一存储单元写入数据。

(以向地址06H单元写入数据80H为例)1)将地址06H写入AR1a)置SW_BUS#(K0)=0;CEL#(K1)=1。

b)按下实验台上电源开关,接通电源。

c)按下复位按钮CLR#(使实验系统处于初始状态)。

d)置开关SW7~SW0为00000110B,此数据加至DBUS(数据指示灯显示00000110B)。

e)置LDAR1=1(k4);LDAR2(K5)=0。

按QD按钮(产生T4),则将DBUS的数据打入AR1,加至左端口的地址线上。

此时左端口地址指示灯显示00000110B。

2)将数据80H写入a)先后置LRW(K2)=0(写操作);CEL#(K1)=0;(片选有效)LDAR1(K4)=0;SW_BUS#(K0)=0;b)置开关SW7~SW0为10000000B(80H),按QD按钮(产生T3),则将DBUS的数据(10000000B)写入06H单元。

2.使用左端口,从某一存储单元读数据。

(以读地址06H单元为例)1)将地址06H写入AR1(步骤同上)2)读数据a)先后置sw_bus#(K0)=1;(使sw7~sw0与dbus断开)Lrw(K2)=1(读操作);Cel#(K1)=0;(片选有效);Ldar1(K4)=0;b)按qd按钮(产生T3),读出的数据送至dbus,dbus的数据指示灯显示10000000B。

实验三 双端口实验内容

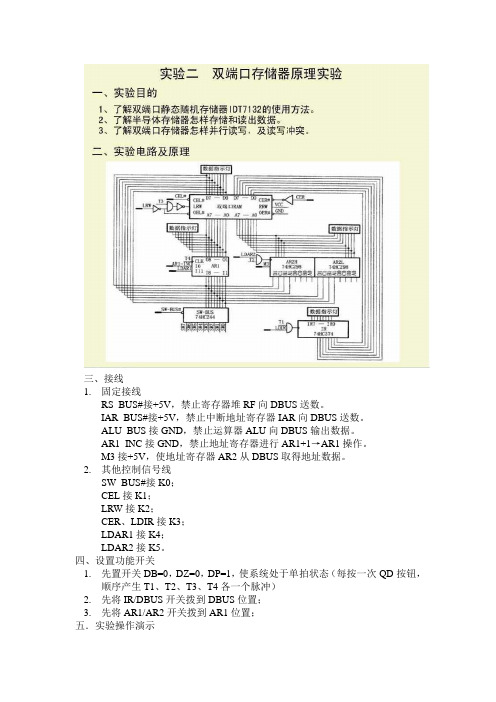

一、实验目的 1. 了解双端口静态存储器 IDT7132 的工作特性及其使用方法 2. 了解半导体存储器怎样存储和读取数据。 3. 了解双端口存储器怎样并行读写,并分析冲突产生的情况。

二、实验电路

上图示出了双端口存储器的实验电路图。这里使用了一片 IDT7132(U36)(2048 X 8位),两个端口的 地址输入 A8—A10 引脚接地,因此实际使用存储容量为 256 字节。左端口的数据部分连接数据总线 DBUS7— DBUS0,右端口的数据部分连接指令总线 IR7—IR0。一片 GAL22V10(U37)作为左端口的地址寄存器(AR1), 内部具有地址递增的功能(AR7~AR0 指示灯)。两片4位的 74HC298(U28、U27)作为右端口的地址寄存器(AR2H、 AR2L),带有选择输入地址源的功能(PC7~PC0 指示灯)。写入数据由实验台操作板上的二进制开关 SW0—SW7 设置,并经过 SW_BUS 三态门(U38)发送到数据总线 DBUS 上。指令总线 INS 上的指令代码输出到指令寄存器 IR(U20),这是一片 74HC374。

K2

K1

K0

状态/值

按一次 QD,将读出存储器 00 地址中的数据,并写入到指令寄存器 IR,指令总线指示灯显示 00H。

……依照上面步骤,先写入地址寄存器。再读出存储器中的数据。可分别读出存储器 10、20H、30H、40H 地址

中的数据并写入到 IR 寄存器。IR 总线指示灯分别显示 10H、20H、30H、40H。

1)、CEL: 为 1 时,允许对存储器左端口进行读写操作。 2)、LRW: 为 0 时,进行写操作;为 1 时,时行读操作。 3)、OEL: 为 0 时,将左端口读出的数据送到数据总线 DBUS 上。本系统 OEL 为 LRW 反向。读时送到

常规数据通路组成实验3

实验三常规数据通路组成实验一、实验目的1.在线连接双端口通用寄存器和双端口内存模块。

2.熟悉电脑的数据路径。

3.掌握数字逻辑电路故障的一般规律,以及排除故障的一般原则和方法。

4、锻炼分析和解决问题的能力,在出现故障的情况下,独立分析故障现象,并排除故障。

第二,实验类型认证类型。

第三,实验仪器1.TEC-4计算机构成原理实验仪器。

2.一个双踪示波器。

3.一个DC万用表。

4.一支逻辑测试笔。

四、实验原理图3为数据通路实验的电路图,由双端口内存实验模块和双端口通用寄存器模块(RF)连接而成。

本实验不涉及双端口内存的指令端口。

通用寄存器文件连接到运算器模块,这个实验涉及到操作数寄存器DR2。

由于双端口内存RAM是三态输出,因此可以直接连接到数据总线DBUS。

此外,DBUS还连接了一个双端口通用寄存器文件。

这样,写入内存的数据可以由通用寄存器提供,从内存RAM 读取的数据也可以发送到通用寄存器文件保存。

实验2使用了双端口RAM,实验1使用了DR2。

通用寄存器文件RF(U32)由一个ISP1016实现,功能类似于两个4位并行的MC14580组成的寄存器文件。

射频包含四个8位通用寄存器R0、R1、R2和R3,带有一个写端口和两个输出端口,因此一个通道的数据可以同时写入。

读出两种数据。

名为WR端口的写端口连接到一个8位临时寄存器(U14)ER,它是一个74HC374。

名为RS(端口b)和RD(端口a)的输出端口连接到算术单元模块的两个操作数寄存器DR1和DR2。

RS端口(B端口)的数据输出也可以通过8位三态门RSO(U15)直接输出到DBUS。

在双端口通用寄存器文件模块的控制信号中,RS1和RS0用于选择从RS端口(B端口)读取的通用寄存器,RD1和RD0用于选择从RD端口(A端口)读取的通用寄存器。

而WR1和WR0用于选择从WR端口写入的通用寄存器。

WRD是写控制信号。

当WRD=1时,在T2上升沿将临时寄存器er中的数据写入通用寄存器文件中RD1和RD0选择的寄存器;当WRD=0时,电流变位寄存器中的数据不写入通用寄存器,并且电流变位信号控制电流变位寄存器从数据总线写入数据。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

台上 OER 已固定接地,RRW 固定接高电平。 当 CER=1 且 LDIR=1 时,右端口读出的指令在 T4 的上升沿打入 IR 寄存器。 3、存储器地址 存储器的地址由地址寄存器 AR1、AR2 提供,而 AR1 和 AR2 的内容根据数码开关 SW0—SW7 设置产生,并

经三态门 SW_BUS 发送到数据总线时被 AR1 或 AR2 接收, 三态门的控制信号 SW_BUS 是低电平有效。数据总线 DBUS 有 5 个数据来源:运算器 ALU,寄存器堆 RF,控制台开关 SW0—SW7,双端口存储器 IDT7132 和中断地址 寄存器 IAR。在任何时刻,都不允许 2 个或者 2 个以上的数据源同时向数据总线 DBUS 输送数据,只允许 1 个(或 者没有)数据源向数据总线 DBUS 输送数据。在本实验中,为了保证数据的正确设置和观察,请令 RS_BUS = 0,ALU_BUS = 0,IAR_BUS = 0。AR1 的控制信号是 LDAR1 和 AR1_INC。当 LDAR1 = 1 时,AR1 从 DBUS 接收地址; 当 AR1_INC =1 时,使 AR1 中的存储器地址增加1;在 T4 的上升沿,产生新的地址;LDAR1 和 AR1_INC 两者不 可同时为1。AR2 的控制信号是 LDAR2 和 M3。当 M3 =1 时,AR2 从数据总线 DBUS 接收数据;当 M3=0 时,AR2 以 PC 总线 PC0—PC7 作为数据来源。当 LDAR2=1 时,在 T2 的下降沿,将新的 PC 值打入 AR2。 三、实验设备

按一次 QD,将 00H 写入存储器 00H 地址。

(3)写地址寄存器 AR1=10

信号

SW7~0 LDIR

SW_BUS LDAR2

LDAR1

CER

开关

K6

K5

K4

K3

K2

状态/值

按一次 QD,将 10H 写入 AR1。

(4)向存储器 10H 地址写数 10H

信号 SW7~0 LDIR

SW_BUS LDAR2

1. TEC-9 计算机组成原理实验系统 1 台 2. 逻辑测试笔一支( 在 TEC-9 实验台上) 3. 双踪示波器一台(公用) 4. 万用表一只(公用) 四、实验任务 1、按表所示,将有关控制信号和和二进制开关对应接好,仔细复查一遍,然后接通电源。 2、将数码开关 SW0—SW7(SW0 是最低位)设置为 00H,将此数据作为地址置入 AR1;然后重新设置二进 制开关控制,将数码开关 SW0—SW7 上的数 00H 写入 RAM 第0号单元。依此方法,在存储器 10H 单元写入数据 10H,20H 单元写入 20H,30H 单元写入 30H,40H 单元写入 40H,共存入5个数据。 使用双端口存储器的左端口,依次读出存储器第 00H、10H、20H、30H、40H 单元中的内容,观察上述各 单元中的内容是否与该单元的地址号相同。请记录数据。注意:总线上禁止两个以上部件同时向总线输出数 据。当存储器进行读出操作时,必须关闭 SW_BUS 三态门!而当向 AR1 送入地址时,双端口存储器不能被选中。 3、通过双端口存储器右端口(指令端口),依次把存储器第 00H、10H、20H、30H、40H 单元中的内容置 入指令寄存器 IR,观察结果是否与(2)相同,并记录数据。 4、双端口存储器的并行读写和访问冲突测试。 置 CEL=1 且 CER=1,使存储器左、右端口同时被选中。当 AR1 和 AR2 的地址不相同时,没有访问冲突; 如果左、右端口地址相同,则发生冲突。要检测冲突,可以观察指示灯 BUSYL 和 BUSYR(分别是两个端口的 “忙”信号输出)。BUSYL/R 亮时不一定发生冲突,但发生冲突时,BUSY 一定亮。当某一个端口(无论是左端 口还是右端口)的 BUSYL/R 亮时,对该端口的写操作被 IDT7132 忽略掉。 5、实验所需信号:

存储器 IDT7132 有 6 个控制引脚:CEL、LRW、OEL、CER、RRW、OER。CEL、LRW、OEL 控制左端口读、写 操作,CER、RRW、OER 控制右端口读、写操作。

(1)左端口操作 CEL 为左端口选择引脚,高有效。当 CEL =0 时,禁止左端口读、写操作;当 CEL =1 时,允许左端口读、 写操作。当 LRW 为高时,左端口进行读操作;当 LRW 为低时,左端口进行写操作。当 OEL 为低时,将左端口 读出的数据放到数据总线 DBUS 上;当 OEL 为高时,禁止左端口读出的数据放到数据总线 DBUS 上。OEL 为 LRW 反向产生。因此本实验台 OEL 信号不需单独控制。实验台上已连接 T3 到时序发生器的 T3 输出。

LDAR1

CER

开关

K6

K5

K4

K3

K2

状态/值

按一次 QD,将 10H 写入存储器 10H 地址。

(5)写地址寄存器 AR1=20

信号

SW7~0 LDIR

SW_BUS LDAR2

LDAR1

CER

开关

K6

K5

Байду номын сангаас

K4

K3

K2

状态/值

按一次 QD,将 10H 写入 AR1。

(6)向存储器 20H 地址写数 20H

信号 SW7~0 LDIR

SW_BUS LDAR2

LDAR1

CER

LRW

CEL

开关

K6

K5

K4

K3

K2

K1

K0

状态/值

按一次 QD,将 40H 写入存储器 40H 地址。

3、实验结果

(1)分别读出 00H、10H、20H、30H、40H 地址中的数据。

1)写地址寄存器 AR1=00

信号

SW7~0 LDIR

信号

SW7~0 LDIR

SW_BUS LDAR2

LDAR1

CER

LRW

CEL

开关

K6

K5

K4

K3

K2

K1

K0

状态/值

按一次 QD,将 00H 写入地址 AR2

40

2)读出存储器 00H 地址中的数据。

信号 IRBUS LDIR

SW_BUS LDAR2

LDAR1

CER

LRW

CEL

开关

K6

K5

K4

K3

1)、CEL: 为 1 时,允许对存储器左端口进行读写操作。 2)、LRW: 为 0 时,进行写操作;为 1 时,时行读操作。 3)、OEL: 为 0 时,将左端口读出的数据送到数据总线 DBUS 上。本系统 OEL 为 LRW 反向。读时送到

数据总线有效。 4)、CER: 为 1 时,右端口允许进行读写操作 5)、RRW: 为 0 时,右端口进行写操作,为 1 时,右端口进行读操作。本实验系统固定接 VCC,只能

3)写地址寄存器 AR1=10

信号

SW7~0 LDIR

SW_BUS LDAR2

LDAR1

CER

LRW

CEL

开关

K6

K5

K4

K3

K2

K1

K0

状态/值

按一次 QD,将 10H 写入 AR1。

4)读出存储器 10H 地址中的数据。

信号 DBUS LDIR

SW_BUS LDAR2

LDAR1

CER

LRW

CEL

SW_BUS LDAR2

LDAR1

CER

LRW

CEL

开关

K6

K5

K4

K3

K2

K1

K0

状态/值

按一次 QD,将 00H 写入 AR1。

2)读出存储器 00H 地址中的数据。

信号 DBUS LDIR

SW_BUS LDAR2

LDAR1

CER

LRW

CEL

开关

K6

K5

K4

K3

K2

K1

K0

状态/值

按一次 QD,将读出存储器 00H 地址中数据到数据总线,数据总线指示灯显示 00H。

LRW K1

LRW K1

LRW K1

LRW K1

LRW K1

LRW K1

LRW K1

LRW K1

CEL K0

CEL K0

CEL K0

CEL K0

CEL K0

CEL K0

CEL K0

CEL K0

39

(8)向存储器 30H 地址写数 30H

信号 SW7~0 LDIR

SW_BUS LDAR2

LDAR1

CER

K2

K1

K0

状态/值

按一次 QD,将读出存储器 00 地址中的数据,并写入到指令寄存器 IR,指令总线指示灯显示 00H。

……依照上面步骤,先写入地址寄存器。再读出存储器中的数据。可分别读出存储器 10、20H、30H、40H 地址

中的数据并写入到 IR 寄存器。IR 总线指示灯分别显示 10H、20H、30H、40H。

a、 当 CEL=1 且 LRW=1 时,左端口进行读操作,同时将读出的数据放到数据总线 DBUS 上。 b、 当 CEL=1 且 LRW=0 时,在 T3 的上升沿开始进行写操作,将数据总线上的数据写入存储器。 2、右端口操作 CER、RRW、OER 控制右端口读、写操作的方式与 CEL、LRW、OER 控制左端口读、写操作的方式类似,不 过右端口读出的数据放到指令总线上而不是数据总线上。实验台上已连接 T3 到时序发生器的 T3 输出。实验

38

信号 IAR_BUS ALU_BUS RS_BUS AR1_INC M3

开关 GND

GND

GND

GND

VCC

信号 LDIR

SW_BUS