常用电子器件管脚排列图

常用电子器件管脚排列图

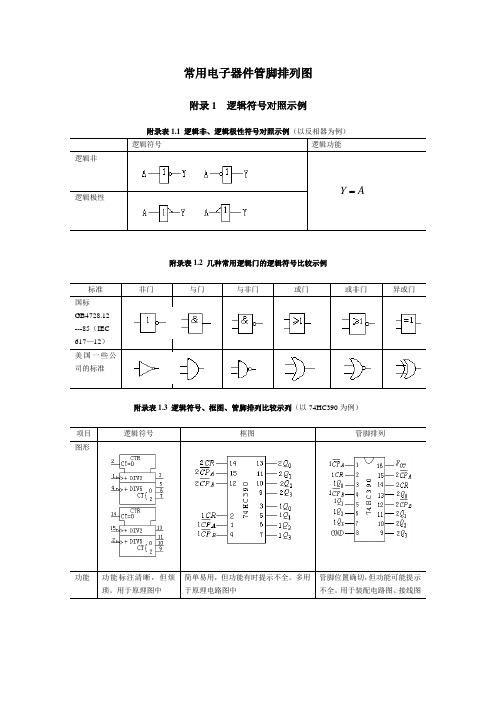

常用电子器件管脚排列图附录1 逻辑符号对照示例附录表1.1 逻辑非、逻辑极性符号对照示例(以反相器为例)附录表1.2 几种常用逻辑门的逻辑符号比较示例附录表1.3 逻辑符号、框图、管脚排列比较示列(以74HC390为例)附录2 集成电路1. 集成电路命名方法集成电路命名方法见附录表2.1附录表2.1 国产半导体集成电路型号命名法(GB3430-82)2.集成电路介绍集成电路IC 是封在单个封装件中的一组互连电路。

装在陶瓷衬底上的分立元件或电路有时还和单个集成电路连在一起,称为混合集成电路。

把全部元件和电路成型在单片晶体硅材料上称单片集成电路。

单片集成电路现在已成为最普及的集成电路形式,它可以封装成各种类型的固态器件,也可以封装成特殊的集成电路。

通用集成电路分为模拟(线性)和数字两大类。

模拟电路根据输入的各种电平,在输出端产生各种相应的电平;而数字电路是开关器件,以规定的电平响应导通和截止。

有时候集成电路标有LM (线性类型) 或DM(数字类型)符号。

集成电路都有二或三个电源接线端:用CC V 、DD V 、SS V 、V +、V -或GND 来表示。

这是一般应用所需要的。

双列直插式是集成电路最通用的封装形式。

其引脚标记有半圆形豁口、标志线、标志圆点 等,一般由半圆形豁口就可以确定各引脚的位置。

双列直插式的引脚排列图如附录图2.1所示。

3.使用TFL 集成电路与CMOS 集成电路的注意事项(1) 使用TYL 集成电路注意事项① TYL 集成电路的电源电压不能高于V 5.5+。

使用时,不能将电源与地颠倒错接,否则将会因为过大电流而造成器件损坏。

附录图 2.1双列直插式集成电路的引脚排列②电路的各输入端不能直接与高于V 5.5+和低于V 5.0-的低内阻电源连接,因为低内阻电源能提供较大的电流,导致器件过热而烧坏。

③除三态和集电极开路的电路外,输出端不允许并联使用。

如果将集电极开路的门电路输出端并联使用而使电路具有线与功能时,应在其输出端加一个预先计算好的上拉负载电阻到CC V 端。

8050-8550三极管引脚图与管脚识别

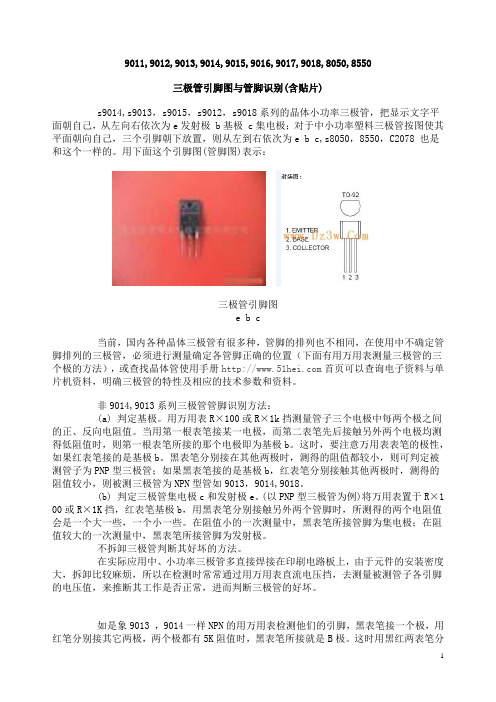

9011,9012,9013,9014,9015,9016,9017,9018,8050,8550三极管引脚图与管脚识别(含贴片)s9014,s9013,s9015,s9012,s9018系列的晶体小功率三极管,把显示文字平面朝自己,从左向右依次为e发射极 b基极 c集电极;对于中小功率塑料三极管按图使其平面朝向自己,三个引脚朝下放置,则从左到右依次为e b c,s8050,8550,C2078 也是和这个一样的。

用下面这个引脚图(管脚图)表示:三极管引脚图e b c当前,国内各种晶体三极管有很多种,管脚的排列也不相同,在使用中不确定管脚排列的三极管,必须进行测量确定各管脚正确的位置(下面有用万用表测量三极管的三个极的方法),或查找晶体管使用手册首页可以查询电子资料与单片机资料,明确三极管的特性及相应的技术参数和资料。

非9014,9013系列三极管管脚识别方法:(a) 判定基极。

用万用表R×100或R×1k挡测量管子三个电极中每两个极之间的正、反向电阻值。

当用第一根表笔接某一电极,而第二表笔先后接触另外两个电极均测得低阻值时,则第一根表笔所接的那个电极即为基极b。

这时,要注意万用表表笔的极性,如果红表笔接的是基极b。

黑表笔分别接在其他两极时,测得的阻值都较小,则可判定被测管子为PNP型三极管;如果黑表笔接的是基极b,红表笔分别接触其他两极时,测得的阻值较小,则被测三极管为NPN型管如9013,9014,9018。

(b) 判定三极管集电极c和发射极e。

(以PNP型三极管为例)将万用表置于R×1 00或R×1K挡,红表笔基极b,用黑表笔分别接触另外两个管脚时,所测得的两个电阻值会是一个大一些,一个小一些。

在阻值小的一次测量中,黑表笔所接管脚为集电极;在阻值较大的一次测量中,黑表笔所接管脚为发射极。

不拆卸三极管判断其好坏的方法。

在实际应用中、小功率三极管多直接焊接在印刷电路板上,由于元件的安装密度大,拆卸比较麻烦,所以在检测时常常通过用万用表直流电压挡,去测量被测管子各引脚的电压值,来推断其工作是否正常,进而判断三极管的好坏。

常用电子管管脚接线图

常用电子管管脚接线图(1)管脚图例管子型号管子型号(1) 管子型号(2)A 6AQ8 ECC85A 6BQ7A ECC180A 6BZ7AA 6CG7A 6FQ7(第9脚为NC)A 6DJ8 ECC88A 6922 E88CCA 7308 E188CCA 8223 E288CCA CcaA 6N1 6н1пA 6N2 6н2пA 6N6 6н6пA 6N11 6н23пA 6240G(第9脚为IC)A 6н30пA1 2C51A1 5670A1 6N3 6н3п常用电子管管脚接线图(2)管脚图例管子型号管子型号(1) 管子型号(2)B 12AT7 ECC81B 12AU7 ECC82B 12AX7 ECC83B 12BH7B 5751B 5814AB 6201 E81CCB 6189 E82CCB 6681 E83CCB 7025B 12AY7 6н4пB ECC99B E80CCB 6N4B 6N10B 2025B1 5687B1 7119 E182CC常用电子管管脚接线图(3)管脚图例管子型号管子型号(1) 管子型号(2)C 6SL7GTC 5691C 6SN7GTC 5692C 6N8P 6н8сC 6N9P 6н9сC ECC33C 6AS7GC 6080C 6N5P 6н5сC 6N13P 6н13сC 6BX7GTC 6BL7GTAD 6BQ5 EL84D 7189D 6P14 6п14п常用电子管管脚接线图(4)管脚图例管子型号管子型号(1) 管子型号(2)E 6F6GTE 6L6GE 6L6GCE 6V6GTE 5881E 6550AE KT88(第1脚为BC)E KT66E 1614E 7581AE 6P3P 6п3сE 6P6P 6п6сE 6G-B8F 2A3F 2c4cF 45F 50F 300BF 4300B常用电子管管脚接线图(5)管脚图例管子型号管子型号(1) 管子型号(2)G 211G 845H EL34 6CA7常用电子管管脚接线图(6)管脚图例管子型号管子型号(1) 管子型号(2)I 7027AK 7868常用电子管管脚接线图(7)管脚图例管子型号管子型号(1) 管子型号(2) L 807L FU-7 г-807M 6AU6 EF94M 6BA6 EF93M 6BD6M 6J4 6ж4пM 6J5 6ж5п常用电子管管脚接线图(8)管脚图例管子型号管子型号(1) 管子型号(2) M1 6AG5 EF96M1 6AK5 EF95M1 6BC5M1 6J1 6ж1пM1 6J3 6ж3пN 6267 EF86N 6J8 6ж32п常用电子管管脚接线图(9)管脚图例管子型号管子型号(1) 管子型号(2) N1 6BX6 EF80N1 6EJ7 EF184O 6SJ7GTO 5693O 6J8P 6ж8с常用电子管管脚接线图(10)管脚图例管子型号管子型号(1) 管子型号(2) P 5AR4 GZ34P 5V4GP 5Z4GT GZ30P GZ32P GZ33P GZ37P U54P 5Z4P 5ц4сQ 5U4GQ 5U4GBQ 5Z3P 5ц3с常用电子管管脚接线图(11)管脚图例管子型号管子型号(1) 管子型号(2) R 5R4GYR 5Y3GTR 274BR 5Z2PS 5Z3S 80常用电子管管脚接线图(12)管脚图例管子型号管子型号(1) 管子型号(2) T 6CA4 EZ81T EZ80U 6X4 EZ90常用电子管管脚接线图(13)管脚图例管子型号管子型号(1) 管子型号(2) U1 6Z4 6ц4пV 7591常用电子管管脚接线图(14)管脚图例管子型号管子型号(1) 管子型号(2) W 6AN8X 6BL8 ECF80X 6U8A ECF82常用电子管管脚接线图(15)管脚图例管子型号管子型号(1) 管子型号(2) Y 7199注:F----灯丝 G----栅极 G1----控制栅 G2----帘栅极 G3----抑制栅极或集射屏 H----热丝 K----阴极 P----屏极IC----管内没有电极连接的空脚,但管座上的焊片不能作中继连接端子用。

各种元器件引脚图

74LS86 异或门74LS00 与非门74LS02 或非门74LS11 三输入端与门74LS90功能:十进制计数器(÷2 和÷5)原理说明:本电路是由4 个主从触发器和用作除2 计数器及计数周期长度为除5 的3 位2 进制计数器所用的附加选通所组成。

有选通的零复位和置9 输入。

为了利用本计数器的最大计数长度(十进制),可将B 输入同QA 输出连接,输入计数脉冲可加到输入A 上,此时输出就如相应的功能表上所要求的那样。

LS90 可以获得对称的十分频计数,办法是将QD 输出接到A 输入端,并把输入计数脉冲加到B 输入端,在QA 输出端处产生对称的十分频方波。

真值表:H=高电平 L=低电平×=不定BCD 计数顺序(注1)5-2 进制计数顺序(注2)注1:对于BCD(十进)计数,输出QA 连到输入B 计数注2:对于5-2 进制计数,输出QD 连到输入A 计数74LS14 非门大部分情况下可以和74LS04非门通用74LS161 四位二进制同步加法计数器74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,这里我给大家介绍一下他的资料:74LS161 pdf 资料下载:/view.jsp?Searchword=74LS16174ls161引脚图管脚图介绍:时钟CP和四个数据输入端P0~P3清零/MR使能CEP,CET置数PE数据输出端Q0~Q3以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

数码管引脚图(常用)

由于很多多都需要这个数码管引脚图,下边介绍几种常用的二极管数码管引脚《七段数码管引脚图》数码管使用条件:a、段及小数点上加限流电阻b、使用电压:段:根据发光颜色决定;小数点:根据发光颜色决定c、使用电流:静态:总电流 80mA(每段 10mA);动态:平均电流 4-5mA 峰值电流 100mA上面这个只是七段数码管引脚图,其中共阳极数码管引脚图和共阴极的是一样的,4位数码管引脚图请在本站搜索我也提供了数码管使用注意事项说明:(1)数码管表面不要用手触摸,不要用手去弄引角;(2)焊接温度:260度;焊接时间:5S(3)表面有保护膜的产品,可以在使用前撕下来。

数码管测试方法与数字显示译码表图三、测试:同测试普通半导体二极管一样。

注意!万用表应放在R×10K档,因为R×1K档测不出数码管的正反向电阻值。

对于共阴极的数码管,红表笔接数码管的“-”,黑表笔分别接其他各脚。

测共阳极的数码管时,黑表笔接数码管的vDD,红表笔接其他各脚。

另一种测试法,用两节一号电池串联,对于共阴极的数码管,电池的负极接数码管的“-”,电池的正极分别接其他各脚。

对于共阳极的数码管,电池的正极接数码管的VDD,电池的负极分别接其他各脚,看各段是否点亮。

对于不明型号不知管脚排列的数码管,用第一种方法找到共用点,用第二种方法测试出各笔段a-g、Dp、H等。

数码管引脚图,一般都是一样的。

数字对应数码管显示控制转换字节(共阴编码)显示--HGFE,DCBA--编码0 --0011,1111--0x3F;1 --0000,0110--0x06;2 --0101,1011--0x5B;3 --0100,1111--0x4F;4 --0110,0110--0x66;5 --0110,1101--0x6D;6 --0111,1101--0x7D;7 --0000,0111--0x07;8 --0111,1111--0x7F;9 --0110,1111--0x6F;共阳为编码取反即可,接线为高低端口对应接法。

常用电子器件管脚排列图

常用电子器件管脚排列图附录1 逻辑符号对照示例附录表1.1 逻辑非、逻辑极性符号对照示例(以反相器为例)附录表1.2 几种常用逻辑门的逻辑符号比较示例附录表1.3 逻辑符号、框图、管脚排列比较示列(以74HC 390为例)附录2 集成电路1. 集成电路命名方法 集成电路命名方法见附录表2.1附录表2.1 国产半导体集成电路型号命名法(GB3430-82)2.集成电路介绍 集成电路I C 是封在单个封装件中的一组互连电路。

装在陶瓷衬底上的分立元件或电路有时还和单个集成电路连在一起,称为混合集成电路。

把全部元件和电路成型在单片晶体硅材料上称单片集成电路。

单片集成电路现在已成为最普及的集成电路形式,它可以封装成各种类型的固态器件,也可以封装成特殊的集成电路。

通用集成电路分为模拟(线性)和数字两大类。

模拟电路根据输入的各种电平,在输出端产生各种相应的电平;而数字电路是开关器件,以规定的电平响应导通和截止。

有时候集成电路标有L M (线性类型) 或DM(数字类型)符号。

集成电路都有二或三个电源接线端:用CC V 、DD V 、SS V 、V +、V -或GND 来表示。

这是一般应用所需要的。

双列直插式是集成电路最通用的封装形式。

其引脚标记有半圆形豁口、标志线、标志圆点 等,一般由半圆形豁口就可以确定各引脚的位置。

双列直插式的引脚排列图如附录图2.1所示。

3.使用TFL 集成电路与C M OS 集成电路的注意事项 (1) 使用TYL 集成电路注意事项① TYL 集成电路的电源电压不能高于V 5.5+。

附录图 2.1双列直插式集成电路的引脚排使用时,不能将电源与地颠倒错接,否则将会因为过大电流而造成器件损坏。

②电路的各输入端不能直接与高于和V 5.5+低于的低内V 5.0-阻电源连接,因为低内阻电源能提供较大的电流,导致器件过热而烧坏。

元件管脚图及功能描述

———————————————————————————————— 作者:

———————————————————————————————— 日期:

ﻩБайду номын сангаас

元件清单

74LS154 4线—16线译码器 1片

74LS160 双同步十进制计数器 1片

74LS193 同步二进制可逆计数器 1片

CC4511 驱动数码管 2片

74LS193同步二进制可逆计数器

管脚图

功能表

74LS154 4线-16线译码器

管脚图

功能表

74LS160同步十进制加法计数器

管脚图

功能表

CC4511驱动数码管

管脚图

功能表

555定时器多谐振荡器、单稳态触发器及施密特触发器

管脚图

555定时器 施密特触发器 2片

74LS00 四2输入与非门 3片

74LS05 六 6输入非门 1片

74LS08 四2输入与门 1片

74LS32 四2输入或 1片

电阻: 1KΩ 4个

元件管脚图及功能描述

74LS002输入四与非门

管脚图

74LS056输入6非门

74LS082输入四与门

74LS32 2输入四或门

器件管脚图及功能表

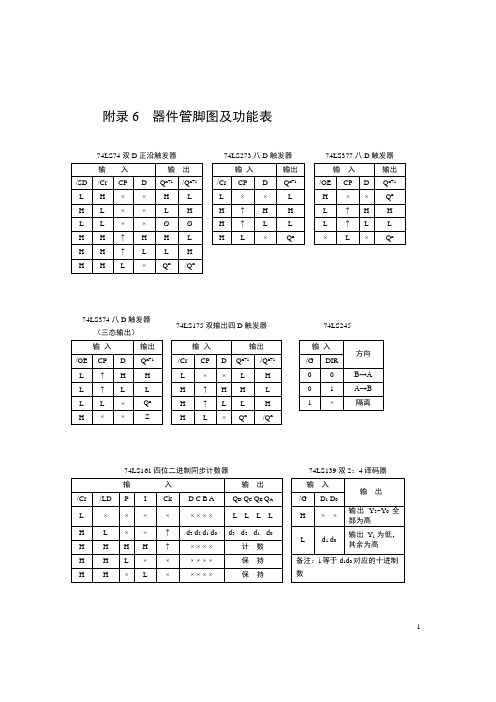

1附录6 器件管脚图及功能表74LS74双D 正沿触发器 74LS273八D 触发器 74LS377八D 触发器74LS374八D 触发器(三态输出) 74LS175双输出四D 触发器74LS24574LS161四位二进制同步计数器 74LS139双2:4译码器274LS151 八选一选择器74LS157 四个二选一选择器74LS257 四个二选一选择器(非反相三态输出)注:i 等于d 2d 1d 0对应的十进制数6116 2K*8 RAM 2716 2K*8 ROM 2732 4K*8 ROM74LS138 3:8译码器 74LS148 8:3八进制优先编码器74LS85 四位幅度比较器附录9微指令寄存器的各字段微操作信号输出去向及功能指令字段IR7~03附录10 联机通讯指南一、准备1、准备一台PC机。

2、把TEC-2机在实验台上放好打开,将TEC-2的随机电源放在TEC-2的左侧,并确认电源开关处在关断的位置。

二、连接电源线1、将TEC-2机电源的直流输出插头P8插在TEC-2机垂直板左侧的插座P8上;将TEC-2机电源的直流输出插头P9插在TEC-2水平板左侧的插座P9上。

特别提醒注意:不要接反P8和P9,否则会烧机器或电源。

2、将TEC-2电源的电源线一端接电源的交流输入插孔,另一端接220V交流电源接线盒。

注意:TEC-2电源的交流电源线必须和计算机的电源线接在同一个有地线的电源接线盒上,以保证两设备共地,否则可能烧毁电源或机器。

三、连接TEC-2和PC1、准备好随机提供的TEC-2和PC的串口通讯电缆。

该电缆一端是9孔的插头,另一端是25孔的插头。

注意:TEC-2随机提供多条通讯电缆,请务必正确选用,以免错误连接造成联机失败。

2、把串口通讯电缆的9孔插头接在TEC-2机的上板左下角V70插座上,25孔插头插在计算机的串口上(COM1或COM2)。

如果PC上没有25针的串口或者25针的串口已被其它设备占用,TEC-2 随机提供一个9转25的转换器可以把25孔的插头转换成9孔的插头,接在9针的串口上。

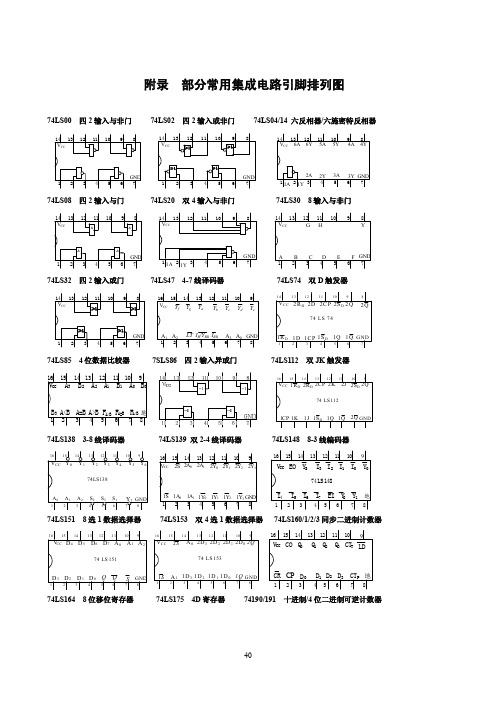

常用集成电路引脚排列图

A0 A1 A2 S2 S3 S1

1

2

3

4

56

Y7 GND

78

74LS151 8 选 1 数据选择器

16 15 14 13 12 11 10 9 VCC 2S 2A0 2A1 2Y0 2Y1 2Y2 2Y3

1S 1A0 1A1 1Y0 1Y1 1Y2 1Y3 GND 12345678

74LS153 双 4 选 1 数据选择器

VCC 1RD 2RD 2CP 2K 2J 2SD 2Q 74 LS 112

1CP 1K 1J 1SD 1Q 1Q 2Q GND

74LS138 38 线译码器

74LS139 双 24 线译码器

74LS148 83 线编码器

16 15 14 13 12 11 10 9

VCC Y0 Y1 Y2 Y3 Y4 Y5 Y6

14 13 12 11 10 9 8

VCC 2CP 2 CR 2 Q 0 2 Q1 2Q2 2 Q3

1C P 1 CR 1Q 0 1Q 1 1 Q 2 1 Q 3 地

1234

56

7

14 13 12 11 10 9 8

VDD

≥1

≥1

≥1

≥1

GND

1234567

CC4011 74LS02 四 2 输入与非门 CC4012 双 4 输入与非门 CC4013 双 D 触发器

12 3 45 6 78

A B C D E F GND 1234567

74LS74 双 D 触发器

14

13 12

11

10

9

8

VCC 2RD 2D 2CP 2S D 2Q 2Q

74 LS 74

芯片管脚排列图整理

附录7 常用集成电路引脚排列一、 集成运算放大器二、集成比较器 三、集成功率放大器五、74附录图7.1 LM741 附录图7.2 LM324附录图7.3 LM358 附录图7.4 0P07附录图7.5 LM339 附录图7.6 LM311附录图7.7 LM386 附录图7.8 LM380附录图7.9 556双时基电路 附录图7.10 555 时基电路附录图7.11 74LS00 四2输入 附录图7.12 74L S02四2 正与非门 输入正或非门 附录图7.13 74LS04 六反相器 附录图7.14 74L S08 四2 输入正与门附录图15 74LS10 三3输入 附录图16 74LS13双4输入正 正与非门 与非门(有施密特触发器) 附录图17 74LS14 六反 附录图18 74LS27 三输入 相器施密特触发器 正或非门附录图19 74LS32 四2输入 附录图20 74LS86四异或门正或门附录图7.21 74LS42、74145 附录图7.22 74LS 46、47、48、4线 – 10线 译码器 247、248249 BCD 七段译码器/ 驱动器附录图23 74LS73 双下降 附录图24 74LS74双上升沿D沿JK 触发器 触发器附录图25 74H78双主从JK 触发器 附录图26 74L S90十进制 异步计数器 (公共时钟、公共清除)附录图27 74LS138 3线– 8线 附录图.28 74LS139 双2 译码器 线–4线译码器 附录图29 74LS160 十进制 附录图30 74L S190十进制 同步计数器 同步加 / 减计数器 附录图31 74LS192 十进制同步 附录图32 74LS194 4位双向 加 / 减计数器(双时钟) 移位寄存器(并行存取)74LS193 4位二进制同步加 / 减计数器(双时钟)附录图7.33 4001四2输 附录图7.34 4002 双4入正或非门 输入正或非门六、 CMOS 集成电路附录图7.35 4011四2输入 附录图7.36 4012 双4输 正与非门 入正与非门附录图.37 4013双主从 附录图38 4017 十进制计数/ 型D 触发器 脉冲分配器 附录图7.39 4022 八进制计 附录图7.40 4023 三3输数/脉冲分配器 入正与非门附录图7.41 4071 四 附录图7.42 4070 四异 输入正或门 或门 附录图7.43 4066 四双向 附录图7.44 4069 六模拟开关 反相器 附录图7.45 40106 六施 附录图7.46 4082 双4输入密特触发器 正与门 附录图7.47 40110 计数 / 附录图7.48 40160 锁存 /七段译码 / 驱动器 十进制同步计数器 附录图7.49 40192 十进制同步加 附录图7.50 40194双向移位 / 减计数器 (双时钟) 寄存器 (并行存取) 40193 四位二进制加 / 减计数器 (双时钟)CD4060引脚排列 CD40110引脚排列 其它信息:高性能的静态C MOS 技术;150MHz(6.57ns 周期时间);低功耗(1.8V 核,135MHz ;1.9V 核,150MH z ;3.3V I /O )设计;3.3V Flas h 编程电压;片上存储;达到128K×16闪存(8×4K 和6×16K 扇区);2K×16 OTP ROM ;L0和L1:2个4K×16单存取RAM 块;H0:1个8K×16单存取RA M 块;M0和M1:2个1K×16单存取RAM 块;引导ROM (4K×16), 软件引导模块;标准匹配图标;时钟和系统控制;提供动态P LL 系数改变;片上振荡器;看门狗计时器模块;3个外部中断;提供45个外围设各中断;128位安全性开关/上锁;保护Flas h/OTP 和L0/L1单存取RAM ;主要控制外围设各;2个事件管理器(EVA ,EVB);与240×A 驱动器兼容;3个32位CPU 计时器;外围设各串行端口;串行外围设备中断;2个串行通信中断,标准UA RT ;加强控制器区域网络;具有SPI 模式的多通道缓冲串口(M cBSP );12位模数转换器,16通道;2×8通道输入多工器;2个采样保持;单个转换时间:200ns ;管道转换时间:60ns ;多达56个单独可编程,多路通用输入/输出(GPIO )引脚;先进的仿真功能;分析与断点功能;开发工具包括:AN SI C /C ++编译器/汇编器/连接器;DSP /BIOSTM ;JTAG 扫描控制器;评估模块;支持广泛的第三方合作数字电机控制;低功率模式,并节省电源;支持空闲,待机,停止模式;禁用个别外围设备时钟;封装选项:具有外部存储接口的176引脚的低轮廓四方扁平封装;温度选项:A :-40~85℃ (GHH ,ZHH ,PGF ,PBK);S/Q :-40~125℃ (GHH ,ZHH ,PGF ,P BK)附录图51 4511二进制七段 附录图52 45128选1数据选择器 译码器 附录图53 4027 双JK 触发器 附录图7.54 4025 三3输入正或非门。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

常用电子器件管脚排列图附录1 逻辑符号对照示例附录表1.1 逻辑非、逻辑极性符号对照示例(以反相器为例)附录表1.2 几种常用逻辑门的逻辑符号比较示例附录表1.3 逻辑符号、框图、管脚排列比较示列(以74HC390为例)附录2 集成电路1. 集成电路命名方法集成电路命名方法见附录表2.1附录表2.1 国产半导体集成电路型号命名法(GB3430-82)2.集成电路介绍集成电路IC 是封在单个封装件中的一组互连电路。

装在陶瓷衬底上的分立元件或电路有时还和单个集成电路连在一起,称为混合集成电路。

把全部元件和电路成型在单片晶体硅材料上称单片集成电路。

单片集成电路现在已成为最普及的集成电路形式,它可以封装成各种类型的固态器件,也可以封装成特殊的集成电路。

通用集成电路分为模拟(线性)和数字两大类。

模拟电路根据输入的各种电平,在输出端产生各种相应的电平;而数字电路是开关器件,以规定的电平响应导通和截止。

有时候集成电路标有LM (线性类型) 或DM(数字类型)符号。

集成电路都有二或三个电源接线端:用CC V 、DD V 、SS V 、V +、V -或GND 来表示。

这是一般应用所需要的。

双列直插式是集成电路最通用的封装形式。

其引脚标记有半圆形豁口、标志线、标志圆点 等,一般由半圆形豁口就可以确定各引脚的位置。

双列直插式的引脚排列图如附录图2.1所示。

3.使用TFL 集成电路与CMOS 集成电路的注意事项(1) 使用TYL 集成电路注意事项① TYL 集成电路的电源电压不能高于V 5.5+。

使用时,不能将电源与地颠倒错接,否则将会因为过大电流而造成器件损坏。

附录图 2.1双列直插式集成电路的引脚排列②电路的各输入端不能直接与高于V 5.5+和低于V 5.0-的低内阻电源连接,因为低内阻电源能提供较大的电流,导致器件过热而烧坏。

③除三态和集电极开路的电路外,输出端不允许并联使用。

如果将集电极开路的门电路输出端并联使用而使电路具有线与功能时,应在其输出端加一个预先计算好的上拉负载电阻到CC V 端。

④输出端不允许与电源或地短路。

否则可能造成器件损坏。

但可以通过电阻与地相连,提高输出电平。

⑤在电源接通时,不要移动或插入集成电路,因为电流的冲击可能会造成其永久性损坏。

⑥多余的输入端最好不要悬空。

虽然悬空相当于高电平,并不影响与非门的逻辑功能,但悬空容易受干扰,有时会造成电路的误动作,在时序电路中表现更为明显。

因此,多余输入端一般不采用悬空办法,而是根据需要处理。

例如:与门、与非门的多余输入端可直接接到CC V 上;也可将不同的输入端通过一个公用电阻 (几千欧) 连到CC V 上;或将多余的输入端和使用端并联。

不用的或门和或非门等器件的所有输入端接地,也可将它们的输出端连到不使用的与门输入端上。

如附录图2.2所示。

对触发器来说,不使用的输入端不能悬空,应根据逻辑功能接人电平。

输入端连线应尽量短,这样可以缩短时序电路中时钟信号沿传输线的延迟时间。

一般不允许将触发器的输出直接 驱动指示灯、电感负载、长线传输,需要时必须加缓冲门。

(2)使用CMOS 电路的注意事项CMOS 集成电路由于输入电阻很高,因此极易接受静电电荷。

为了防止产生静电击穿,生产CMOS 时,在输入端都要加上标准保护电路,但这并不能保证绝对安全,因此使用CMOS 集成电路时,必须采取以下预防措施。

①存放CMOS 集成电路时要屏蔽,一般放在金属容器中,也可以用金属箔将引脚短路。

②CMOS 集成电路可以在很宽的电源电压范围内提供正常的逻辑功能,但电源的上限电压(即使是瞬态电压)不得超过电路允许极限值max V ,电源的下限电压(即使是瞬态电压)不得低于系统工作所必需的电源电压最低值min V ,更不得低于SS V 。

③焊接CMOS 集成电路时,一般用20W 内热式电烙铁,而且烙铁要有良好的接地线。

也可以利用电烙铁断电后的余热快速焊接。

禁止在电路通电的情况下焊接。

④为了防止输入端保护二极管因正向偏置而引起损坏,输入电压必须处在DD V 和SS V 之间,即SS V ≤I u ≤DD V 。

附录图 2.2 TTL 电路多余的处理⑤调试CMOS 电路时,如果信号电源和电路板用两组电源,则刚开机时应先接通电路板电源,后开信号源电源。

关机时则应先关信号源电源,后断电路板电源。

即在CMOS 本身还没有接通电源的情况下,不允许有输入信号输入。

⑥多余输入端绝对不能悬空。

否则不但容易受外界噪声干扰,而且输入电位不定,破坏了正常的逻辑关系,也消耗不少的功率。

因此,应根据电路的逻辑功能需要分别情况加以处理。

例如:与门和与非门的多余输入端应接到DD V 或高电平;或门和或非门的多余输入端应接到SS V 或低电平;如果电路的工作速度不高,不需要特别考虑功耗时,也可以将多余的输入端和使用端并联。

如附录图2.3所示。

以上所说的多余输入端,包括没有被使用但已接通电源的CMOS 电路所有输入端。

例如,一片集成电路上有4个与门,电路中只用其中一个,其它三个门的所有输入端必须按多余输入端处理。

⑦输入端连接长线时,由于分布电容和分布电感的影响,容易构成LC 振荡,可能使输入保护二极管损坏,因此必须在输入端串接一个12~ K 20的保护电阻只,如附录图2.4所示。

⑧CMOS 电路装在印刷电路板上时,印刷电路板上总有输入端,当电路从机器中拔出时,输入端必须出现悬空,所以应在各输入端接入限流保护电阻,如附录图2.4所示。

如果要在印刷电路板上安装CMOS 集成电路,则必须在与它有关的其它元件安装之后再装CMOS 电路,避免CMOS 器件输入端悬空。

⑨插拔电路板插头时,应该注意先切断电源,防止在插拔过程中烧化CMOS 集成电路的输入端保护二极管。

附录图2.3 CMOS 多余端的处理 附录图2.4 输入长线保护电路附录3 半导体发光器件1. 发光二极管发光二极管的伏安特性与普通二极管类似,但是它的正向压降较大,并在正向压降达到一定值时发光。

发光颜色和构成PN 结的材料有关,通常有红、黄、绿、蓝和紫等颜色。

发光亮度近似和工作电流密度成正比,但掺杂ZnO 和GaP 的发光二极管,其发光亮度随电流密度的增加会很快趋向饱和。

另外,随结温的升高,LED 的发光亮度将会减弱。

由于发光二极管的响应时间(光信号对电信号的延迟时间)一般小于100ns ,故直流信号、交流信号或脉冲信号均可作为它的驱动信号。

国产LED 器件用654321⨯⨯⨯⨯⨯⨯FG 命名,其中X1表示材料,1⨯取值1,2,3分别对应LED 的材料为GaAsP ,GaAsAl 和GaP 。

X2表示发光颜色,2⨯取1 ~ 6时表示发光颜色为红、橙、黄、绿、蓝和复色。

3⨯表示封装形式。

4⨯表示外形,取0 ~ 6各整数时,分别指发光二极管的外形为圆形、长方形、符号形、三角形、正方形、组合形和特殊形。

65⨯⨯为序号。

使用发光二极管时,若用电压源驱动,则应在电路中串接限流电阻,以防止LED 中电流过大而损坏。

用交流信号驱动时,为防止LED 被反向击穿,可在两端反极性并连整流二极管。

几种红色发光二极管的参数见附录表3.1。

附录表3.1 几种红色发光二极管的参数2.IED 数码管附录图3.1 LED 数码管 (a )LED 数码管的正面图;(b )共阳极数码管等效电路;(c )共阴极数码管等效电路常用的LED 数码管如附录图3.1(a )所示。

它是利用发光二极管的制造工艺,由7个条状管芯和一个点状管芯的发光二极管制成。

LED 数码管有两种不同的结构形式,其等效电路分别如附录图3.1(b )和(c )所示。

图(b )中,各段发光二极管的阳极连在一起作为公共端,因此称为共阳极数码管。

工作时应当将阳极连电源正极,各驱动输入端通过限流电阻接相应的译码驱动器的输出。

当译码驱动器的输出为低电平时,数码管相应的段变亮。

LED 数码管各段发光二极管的伏安特性与普通二极管类似,只是正向压降稍大,在正向电流达到适当大小时就能发光。

在一定范 围内,发光 亮度和正向电流的大小近似成正比,但正向电流应小于允 许的最大电流,并应留有适当的裕量,一般以不超过极限 电流的70%为宜。

因此,它的驱动输入端和译码电路或电压源相连时,应当串接合适的限流电阻,以免损坏器件。

附录表3.2列出了几种数码管的参数。

LED 数码管的 大小规格很多,一般尺寸大的工作电压也大,这是因为大尺 寸数码管的每一段可能是由几个发光二极管串联组成,称 为导光柱型。

国产LED 数码管的管脚排列规格很多,因此,用时除查产品说明书外,主要采用实测的方法来确定各管脚的功能,下面以共阳极数码管为例来说明。

附录表3.2 几种LED 数码管的参数先按附录图3.2准备好测试线路,把数码管的左下角接地,再使A 端逐个和其它管脚接触。

若A 端和所有管脚都已接触过,而数码管各段全不亮,则左下角管脚即为阳极或空脚(设数码管是好的)。

若A 端接触管脚时数码管上某段变亮,则A 端接触的管脚为阳极。

然后使A 和阳极连好,用地线分别接触阳极以外的各管脚,相应的段就会变亮,从而可确定管脚和显示段间的对应关系。

附录4 半导体光敏器件半导体光敏器件能将光信号转变为电信号,因而可利用它来测量能影响光信号的非电量。

从波长响应范围来看,在红外光、可见光、紫外光和射线波长区都有相应的光敏器件。

产品主要有光敏电阻、光敏二极管、光敏三极管、色敏器件和远红外器件等。

另外,光敏器件的响应速度快,能实现非接触测量,因而很适合做计算机的接口器件。

1.光敏电阻光敏电阻主要有CdS 元件、CdSe 元件和PbS 元件。

它们的电阻率对某段波长的照度变化很敏感,当照度增加时,电阻率急剧减小,并在一定条件下,照度和电阻率可呈现线性关系。

在完全无光照时,光敏电阻也会呈现一定的电阻值,称为暗电阻,而光照时的电阻称为附录图3.2 LED 数 码管的管脚判别光电阻。

对CdS光敏电阻,暗电阻约几兆欧姆,而光电阻可小到几百欧姆。

光敏电阻的温度系数和照度有关,强光照射条件下为正,弱光照射条件下为负。

在上述三种光敏电阻中,以CdS光敏电阻应用最广。

它可以工作在交流状态,对可见光敏感,输出信号较大,价格便宜,抗噪声能力比光敏二极管强,但响应速度较慢。

附录表4.1列出了几种CdS光敏电阻的参数,其中峰值波长指光谱响应中最敏感的波长值;响应时间指光敏电阻两端加电压后,从受光照开始,电阻中的光电流从0增加到正常电流值的63%所经历的时间τt,遮光后,光电流从正常值衰减到37%时所经历的时间f t。

当选用CdS作开关元件时,应注意它的允许功耗和。

响应速度能否满足要求。

附录表4.1 几种CdS光敏电阻的参数2.光敏二极管光敏二极管又称光电二极管,目前使用最多的是Si光电二极管。