常用芯片管脚引脚图

Dsp2812芯片管脚说明(中文)

TDO

D12

127

93

O/Z

—

EMU0

D11

137

100

I/O/Z

PU

ADC 模拟输入信号 ADCINA7 ADCINA6 ADCINA5 ADCINA4 ADCINA3 ADCINA2 ADCINA1 ADCINA0 B5 D5 E5 A4 B4 C4 D4 A3 167 168 169 170 171 172 173 174 119 120 121 122 123 124 125 126 I I I I I I I I 续表 引脚号 名 字 179 针 176 针 GHH 封装 F5 D1 D2 D3 C1 B1 C3 C2 E2 PGF 封装 9 8 7 6 5 4 3 2 11 128 针 PBK 封装 9 8 7 6 5 4 3 2 11 I/O/Z PU/PDS 说 明 采样/保持 A 的 8 通道模拟输入。在器件未 上电之前 ADC 引脚不会被驱动

118 115 114 1 128

I I I

ADC 模拟电源(3.3V) ADC 数字地 ADC 数字电源(1.8V) I/O 模拟电源(3.3V) I/O 模拟地 电源信号

20 29 42 56 63 74 82 82 102 110

1.8V 或 1.9V 核心数字电源

续表 179 针 176 针 GHH 封装 VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VDDAIO VSSAIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDD3VL G4 K1 L2 P4 K6 P8 M10 L11 K13 J14 G13 E14 B14 D10 C10 B8 B2 A2 J4 L7 L10 N14 G11 E9 N8 PGF 封装 19 32 38 52 58 70 78 86 99 105 113 120 129 142 — 153 1 176 31 64 81 — 114 145 69 128 针 PBK 封装 17 26 26 39 — 53 59 62 73 — — 88 95 — 103 109 1 128 25 49 — — 83 104 52 Flash 核电源(3.3V),上电后所有时间 内都应将该引脚接至 3.3V GPIOA 或 EVA 信号 I/O 数字电源(3.3V) I/O 模拟电源(3.3V) I/O 口模拟地

74ls373引脚图管脚功用表阐明

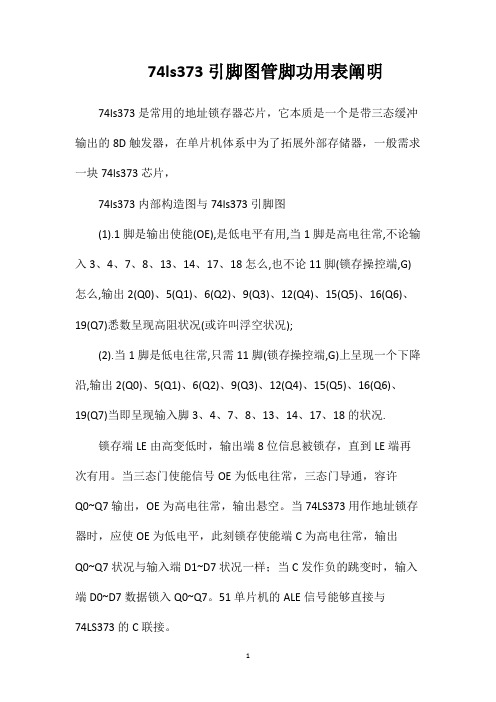

74ls373引脚图管脚功用表阐明74ls373是常用的地址锁存器芯片,它本质是一个是带三态缓冲输出的8D触发器,在单片机体系中为了拓展外部存储器,一般需求一块74ls373芯片,74ls373内部构造图与74ls373引脚图(1).1脚是输出使能(OE),是低电平有用,当1脚是高电往常,不论输入3、4、7、8、13、14、17、18怎么,也不论11脚(锁存操控端,G)怎么,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)悉数呈现高阻状况(或许叫浮空状况);(2).当1脚是低电往常,只需11脚(锁存操控端,G)上呈现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)当即呈现输入脚3、4、7、8、13、14、17、18的状况.锁存端LE由高变低时,输出端8位信息被锁存,直到LE端再次有用。

当三态门使能信号OE为低电往常,三态门导通,容许Q0~Q7输出,OE为高电往常,输出悬空。

当74LS373用作地址锁存器时,应使OE为低电平,此刻锁存使能端C为高电往常,输出Q0~Q7状况与输入端D1~D7状况一样;当C发作负的跳变时,输入端D0~D7数据锁入Q0~Q7。

51单片机的ALE信号能够直接与74LS373的C联接。

1D~8D为8个输入端。

1Q~8Q为8个输出端。

G是数据锁存操控端;当G=1时,锁存器输出端同输入端;当G由1变为0时,数据输入锁存器中。

OE为输出容许端;当OE=0时,三态门翻开;当OE=1时,三态门封闭,输出呈高阻状况。

在MCS-51单片机体系中,常选用74LS373作为地址锁存器运用,其联接办法如上图所示。

其间输入端1D~8D接至单片机的P0口,输出端供给的是低8位地址,G端接至单片机的地址锁存容许信号ALE。

输出容许端OE接地,标明输出三态门一向翻开。

80C51单片机引脚图及引脚功能介绍

80C51单片机引脚图及引脚功能介绍首先我们来介绍一下单片机的引脚图及引脚功能(如下图所示),引脚的具体功能将在下面详细介绍单片机的40个引脚大致可分为4类:电源、时钟、控制和I/O引脚。

⒈ 电源:⑴ VCC - 芯片电源,接+5V;⑵ VSS - 接地端;⒉ 时钟:XTAL1、XTAL2 - 晶体振荡电路反相输入端和输出端。

⒊ 控制线:控制线共有4根,⑴ ALE/PROG:地址锁存允许/片内EPROM编程脉冲① ALE功能:用来锁存P0口送出的低8位地址② PROG功能:片内有EPROM的芯片,在EPROM 编程期间,此引脚输入编程脉冲。

⑵ PSEN:外ROM读选通信号。

⑶ RST/VPD:复位/备用电源。

① RST(Reset)功能:复位信号输入端。

② VPD功能:在Vcc掉电情况下,接备用电源。

⑷ EA/Vpp:内外ROM选择/片内EPROM编程电源。

① EA功能:内外ROM选择端。

② Vpp功能:片内有EPROM的芯片,在EPROM编程期间,施加编程电源Vpp。

⒋ I/O线80C51共有4个8位并行I/O端口:P0、P1、P2、P3口,共32个引脚。

P3口还具有第二功能,用于特殊信号输入输出和控制信号(属控制总线)。

拿到一块单片机,想要使用它,首先必须要知道怎样去连线,我们用的一块89C51的芯片为例,我们就看一下如何给它连线。

1、电源:这当然是必不可少的了。

单片机使用的是5V电源,其中正极接40管脚,负极(地)接20管脚。

2、振蒎电路:单片机是一种时序电路,必须供给脉冲信号才能正常工作,在单片机内部已集成了振荡器,使用晶体振荡器,接18、19脚。

只要买来晶体震荡器,电容,连上就能了,按图1接上即可。

3、复位管脚:按图1中画法连好,至于复位是何含义及为何需要复要复位,在单片机功能中介绍。

4、 EA管脚:EA管脚接到正电源端。

至此,一个单片机就接好,通上电,单片机就开始工作了。

我们的第一个任务是要用单片机点亮一只发光二极管LED,显然,这个LED必须要和单片机的某个管脚相连,不然单片机就没法控制它了,那么和哪个管脚相连呢?单片机上除了刚才用掉的5个管脚,还有35个,我们将这个LED和1脚相连。

LED显示屏常用IC管脚说明

LED显示屏常用器件的介绍1.IC的管脚功能IC芯片分别:74HC245、74HC595、74HC138、74HC04、4953。

各IC管脚功能如下:A: 74HC245功能是放大及缓冲。

各引脚如图20 和1接电源(+5V)19脚和10脚接电源地(GND)当电源是以上接时:输入脚分别为2、3、4、5、6、7、8、9。

输出脚分别为11、12、13、14、15、16、17、18注:2脚输入时,18脚输出。

其它脚以此类推。

B:74HC138功能是8选1译码器,输出为8行。

控制行数据。

各引脚如图第8脚GND,电源地。

第15脚VCC,电源正极第1-3脚A、B、C,输入脚。

第4-6脚选通输入端,(一般第5脚为EN )9-15脚和第7脚输出端。

C:74HC595功能是8位串入串、并出移位寄存器。

控制列数据。

各引脚如图16脚和10脚接电源(+5V),13脚和8脚接电源地(GND)。

列信号输出脚:1、2、3、4、5、6、7、15。

第一列输出脚为7脚,以此类推。

另第八列输出脚为15脚。

数据信号输入脚(Din)为14,数据信号输出脚(Din)为9。

锁存信号脚(L)为12脚,移位信号脚为11脚。

D:74HC04功能是六带缓冲反相器,控制使零信号(EN)。

各引脚如下图15脚接电源(+5V),7脚电源地(GND)。

信号输入脚为:1、3、5、9、11、13。

信号输出脚为:2、4、6、8、10、12。

E:4953行管功能是开关作用,每个行管控制2行。

1脚和3脚接电源(+5V)。

信号输入脚:2、4。

信号输出脚:5、6、7、8。

5脚和6脚为一组输入,7脚和8脚、5脚和6脚为一组输出。

TB62726与5026 5024 16126的作用:LED驱动芯片,16位移位锁存器。

第1脚GND,电源地。

第24脚VCC,电源正极第2脚DATA,串行数据输入第3脚CLK,时钟输入.第4脚STB,锁存输入 .第23脚输出电流调整端,接电阻调整第22脚DOUT,串行数据输出第21脚EN,使能输入第5-12脚和13-20脚驱动输出端。

芯片管脚一览图

74ls00 2输入四与非门

74ls02 2输入四或非门

74ls04 六倒相器

74ls08 2输入四与门

74ls20 4输入双与非门

74ls32 2输入四或门

74ls74 正沿触发双d型触发器(带预置端和清除端) 74ls90 十进制计数器

74ls112 负沿触发双j-k触发器(带预置端和清除端) 74ls138 3-8线译码器/多路转换器

74ls153 双4选1数据选择器/多路选择器

74ls161 可预置四位二进制计数器(并清除异步)

74ls32或门74ls00与非门

74ls08 与门74ls138 3-8译码器

74ls139 四选一数据选择器74ls20 与非门

74ls112 下降沿触发j-k触发器可预置四位二进制计数器74ls161

六非门74LS04 十进制计数器74LS90

双4选1数据选择器74LS153 异或门74LS86

正沿触发双d型触发器74LS74 2输入四或非门74LS02。

74ls148管脚图引脚功能表真值表

74ls148管脚图引脚功能表真值表逻

有些单片机控制系统和数字电路中,无法对几个按钮的同时响应做出反映,如电梯控制系统在这种情况下就出出现错误,这是绝对不允许的。

于是就出现了74ls148优先编码器,先说一下他的基本原理.他允许同时输入两个以上编码信号。

不过在设计优先编码器时已经将所有的输入信号按优先顺序排了队,当几个输入信号同时出现时,只对其中优先权最高的一个进行编码。

〈74ls148管脚功能〉〈74ls148引脚图〉

74ls148优先编码器管脚功能介绍:为16脚的集成芯片,电源是VCC(16) GND(8), I0—I7为输入信号,A2,A1,A0为三位二进制编码输出信号,IE是使能输入端,OE是使能输出端,GS为片优先编码输出端。

〈74ls148逻辑图〉〈74ls148逻辑表达式〉

使能端OE(芯片是否启用)的逻辑方程:

<74ls148真值表>

由74ls148真值表可列输出逻辑方程为:

A2 = (I4+I5+I6+I7)IE

A1 = (I2I4I5+I3I4I5+I6+7)·IE

A0 = (I1I2I4I6+I3I4I6+I5I6+I7)·IE

用两个74ls148优先编码器芯片扩展为十六线-四线优先编码器的电路连线图。

74ls373引脚图管脚功能表

74ls373引脚图管脚功能表74ls373是常用的地址锁存器芯片,它实质是一个是带三态缓冲输出的8D触发器,在单片机系统中为了扩展外部存储器,通常需要一块74ls373芯片,(1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态);(2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态.锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。

当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。

当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端C为高电平时,输出Q0~Q7 状态与输入端D1~D7状态相同;当C发生负的跳变时,输入端D0~D7 数据锁入Q0~Q7。

51单片机的ALE信号可以直接与74LS373的C连接。

74ls373与单片机接口:1D~8D为8个输入端。

1Q~8Q为8个输出端。

G是数据锁存控制端;当G=1时,锁存器输出端同输入端;当G由“1”变为“0”时,数据输入锁存器中。

OE为输出允许端;当OE=“0”时,三态门打开;当OE=“1”时,三态门关闭,输出呈高阻状态。

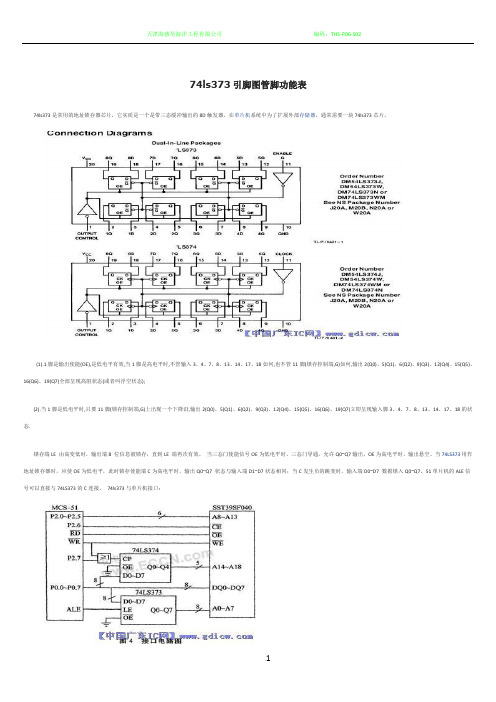

在MCS-51单片机系统中,常采用74LS373作为地址锁存器使用,其连接方法如上图所示。

其中输入端1D~8D接至单片机的P0口,输出端提供的是低8位地址,G端接至单片机的地址锁存允许信号ALE。

输出允许端OE接地,表示输出三态门一直打开。

74LS系列主要芯片引脚及参数

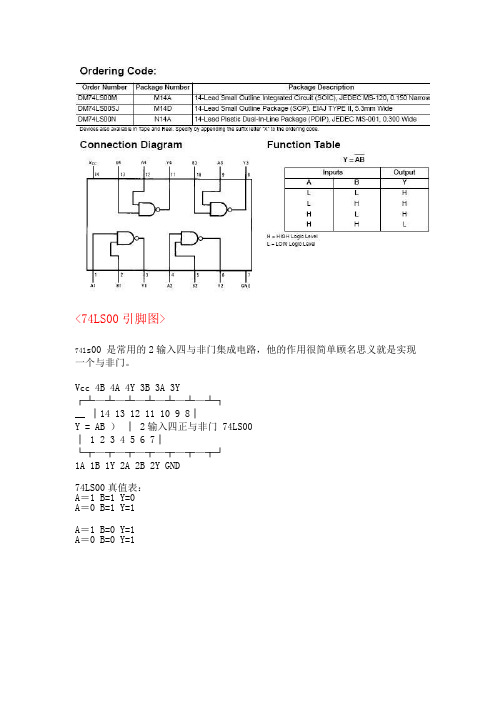

<74LS00引脚图>74l s00 是常用的2输入四与非门集成电路,他的作用很简单顾名思义就是实现一个与非门。

Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐__ │14 13 12 11 10 9 8│Y = AB )│ 2输入四正与非门 74LS00│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GND74LS00真值表:A=1 B=1 Y=0A=0 B=1 Y=1A=1 B=0 Y=1A=0 B=0 Y=174HC138基本功能74LS138 为3 线-8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,其74LS138工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

74LS138的作用:利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS138图74ls138译码器内部电路3线-8线译码器74LS138的功能表备注:这里的输入端的三个A0~1有的原理图中也用A B C表示(如74H138.pdf中所示,试用于普中科技的HC-6800 V2.2单片机开发板)。

<74ls138功能表>74LS138逻辑图无论从逻辑图还是功能表我们都可以看到74LS138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。

如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出74ls138逻辑图由上式可以看出,在同一个时间又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。