chapter2ARM7体系结构

ARM7体系结构

各ARM体系结构版本——V5

在V4版本的基础上,对现在指令的定义进行了必要的 修正,对V4版本的体系结构进行了扩展并增加了指令,具 体如下: 改进了ARM/Thumb状态之间的切换效率; 允许非T变量和T变量一样,使用相同代码生成技术; 增加计数前导零指令和软件断点指令; 对乘法指令如何设置标志作了严格的定义。

3.2 ARM7TDMI

简介

ARM7TDMI基于ARM体系结构V4版本,是目前低 端的ARM核。具有广泛的应用,其最显著的应用为 数字移动电话。

3.2 ARM7TDMI

简介

ARM7TDMI支持32位寻址范围,并弥补了ARM6 不能在低于5V电源电压下工作的不足。ARM7TDMI的 后缀意义为: ARM7 T D M I - S

乘法器 桶形移位器 写数据寄存器 32位ALU 指令管线读数据寄存器 Thumb指令译码器

该系列包括ARM7TDMI、ARM7TDMI-S、带有高 速缓存处理器宏单元的ARM720T和扩充了Jazelle 的ARM7EJ-S。该系列处理器提供Thumb 16位压缩 指令集和EmbededICE软件调试方式,适用于更大规 模的SoC设计中。 ARM7系列广泛应用于多媒体和嵌入式设备,包 括Internet设备、网络和调制解调器设备,以及移 动电话、PDA等无线设备。

ADDR[31:0] 扫描调试 控制 指令译码 和 控制逻辑 CLK CLEN CFGBIGEND nIRQ nFIQ nRESET ABORT LOCK WRITE

地址寄存器

地址增加器

寄存器组 31*32位寄存器 (6个状态寄存器)

SIZE[1:0] PROT[1:0] TRANS[1:0]

DBG输出 DBG输入 CP控制 CP握手

第2章 ARM7体系结构PPT课件

支持64位乘法;

支持片上调试;

28.07.2020

支持高密度16位的Thumb指令集;

华中科技大学计算机学院

7

2.2 ARM7TDMI

三级流水线

ARM7TDMI处理器使用流水线来增加处理器指 令流的速度。这样可使几个操作同时进行,并使处 理和存储器系统连续操作,能提供0.9MIPS/MHz的 指令执行速度。

PC

PC

PC-4

PC-2

PC-8

PC-4

流水线工位 取指 译码

执行

描述

指令从存储器中取出 对指令使用的寄存器进行译码 从寄存器组中读出寄存器,执行移位 和ALU操作,寄存器被写回到寄存器 组中

28.07.2020

华中科技大学计算机学院

9

2.2 ARM7TDMI

存储器访问

ARM7TDMI处理器使用了冯·诺依曼(Von Neumann)结构,指令和数据共用一条32位总线。 只有装载、存储和交换指令可以对存储器中的数据 进行访问。

15.协处理器接口

7.内部寄存器

16.调试接口简介

8. 程序状态寄存器

17.ETM接口简介

28.07.2020

华中科技大学计算机学院

4

2.1 ARM简介

ARM公司简介

ARM是Advanced RISC Machines的缩写,它是 一家微处理器行业的知名企业,该企业设计了大量 高性能、廉价、耗能低的RISC (精简指令集)处 理器。

ARM7TDMI的流水线分3级,分别为: 取指译码执行

28.07.2020

华中科技大学计算机学院

8

2.2 ARM7TDMI

三级流水线

正常操作过程中,在执行一条指令的同时对下 一条指令进行译码,并将第三条指令从存储器中取 出。这三条指令之间的位置关系如下表所示:

ARM7体系结构概述

PC

状态寄 存器 CPSR

R15

CPSR

注意:括号内为ATPCS中寄存器的命名,可以使用RN汇编伪指令将寄存器 定义多个名字。其中ADS1.2的汇编程序直接支持这些名称,但注意a1~a4, v1~v4必须用小写。

周立功单片机

Thumb状态下的通用寄存器

寄存器 寄存器在汇编 类别 中的名称 R0(a1) R1(a2) R2(a3) R3(a4) 通用寄 存器和 程序计 数器 R4(v1) R5(v2) R6(v3) R7(v4,wr) SP LR R13 R14 R13_svc 各模式下实际访问的寄存器 用户 系统 管理 中止 R0 R1 R2 R3 R4 R5 R6 R7 R13_abt R13_und R13_irq R13_fiq 未定义 中断 快中断

Xscale

周立功单片机

2.1 ARM简介

• ARM处理器核简介——ARM7

该系列包括ARM7TDMI、ARM7TDMI-S、带 有高速缓存处理器宏单元的ARM720T和扩充了 Jazelle的ARM7EJ-S。该系列处理器提供Thumb 16 位压缩指令集和EmbededICE软件调试方式,适用 于更大规模的SoC设计中。 ARM7系列广泛应用于多媒体和嵌入式设备, 包括Internet设备、网络和调制解调器设备,以及 移动电话、PDA等无线设备。

周立功单片机

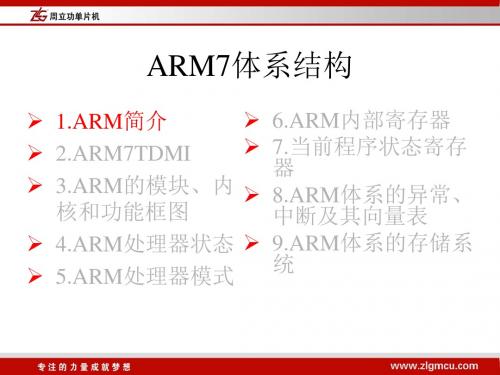

第2章 目录

1.简介 2.ARM7TDMI 3.ARM7TDMI的模块和 内部框图 4.体系结构直接支持的 数据类型 5.处理器状态 6.处理器模式 7.内部寄存器 8. 程序状态寄存器 9.异常 10.中断延迟 11.复位 12.存储器及存储器映射 I/O

所以最好避免使用STR和STM指令来保存R15, 如果很难做到,那么应当在程序中计算出该芯片的 偏移量。

第章ARM7体系结构ppt课件

1.1 ARM简介

• ARM处理器核简介——SecurCore

该系列涵盖了SC100、SC110、SC200和SC210 处理核。该系列处理器主要针对新兴的安全市场, 以一种全新的安全处理器设计为智能卡和其它安全 IC开发提供独特的32位系统设计,并具有特定反伪 造方法,从而有助于防止对硬件和软件的盗版。

1.2 ARM7TDMI

• 存储器访问

ARM7TDMI处理器使用了冯·诺依曼(Von Neumann)结构,指令和数据共用一条32位总线。 只有装载、存储和交换指令可以对存储器中的数据 进行访问。

数据可以是字节( 8位)、半字( 16位)或者 字(32位)。

1.2 ARM7TDMI

• 存储器访问

第1章 ARM7体系结构

第1章 目录

1.简介

9.异常

2.ARM7TDMI

10.中断延迟

3.ARM7TDMI的模块和 11.复位

内部框图

12.存储器及存储器映射

4.体系结构直接支持的 I/O

数据类型

13.寻址方式简介

5.处理器状态

14.ARM7指令简介

6.处理器模式

内部周期; 非连续的周期; 连续 的周期; 协处理器寄存器的传输周期。

第1章 目录

1.简介

9.异常

2.ARM7TDMI 10 Nhomakorabea中断延迟

3.ARM7TDMI的模块和 11.复位

内部框图

12.存储器及存储器映射

4.体系结构直接支持的 I/O

数据类型

13.寻址方式简介

LOCK

DBGINSTRVALID DBGRQ DBGBREAK DBGACK DBGnEXEC DBGEXT[1] DBGEXT[0] DBGEN DBGRNG[1] DBGRNG[0] DBGCOMMRX DBGCOMMTX

第2章ARM7体系结构.

1.ARM简介 2.ARM7TDMI 3.ARM的模块、内 核和功能框图 4.ARM处理器状态 5.ARM处理器模式 6.ARM内部寄存器 7.当前程序状态寄存 器 8.ARM体系的异常、 中断及其向量表 9.ARM体系的存储系 统

2.1 ARM简介

2.2 ARM7TDMI

• 思考题

地址

PC

指令

0x4000 0x4004 0x4008 0x400C

ADD PC,PC,#4 …… …… ……

PC PC-4

一般来说,人们习惯 程序计数器 执行 PC 指向 ADD 0x4008 PC,PC,#4 R15(PC) 地址, 指 性约定将“正在执行” PC 指向 0x4000 0x4004 地址, 总是指向“正在取指” 令后, 执行 ADD PC 指令,所以指 的值为多少? 的指令作为参考点,则: 取指 译码 ADD 指令。 的指令,而不是指向 令执行的结果为 : PC值=当前程序执行位置+ 8 “正在执行”的指令或 PC=PC+4=0x4008+4 注:ARM “正在译码”的指令。 =0x400C 。 状态时, 每条指令为4字节长。

ARM7TDMI-S

ARM7TDMI 的可综合(synthesizable) 版本(软核),对应用工程师来说其编 程模型与ARM7TDMI 一致;

支持EmbededICE观察硬件;

支持64位乘法; 支持片上调试; 支持高密度16位的Thumb指令集;

2.2 ARM7TDMI

• 存储器的字与半字

从偶数地址开始的连续2个字节构成一个半字;

2.1 ARM简介

• Xscale简介

Intel Xscale微控制器则提供全性能、高性价比、 低功耗的解决方案,支持16位Thumb指令并集成数字 信号处理(DSP)指令。 主要应用于手提式通讯和消费电子类设备。

第二章ARM处理器基础ARM7

半字:从地址0x0000处取一个半字数据,则取出来的内容为3412;从 地址0x0001处取一个半字数据,则取出来的内容为5634; 字:从地址0x0000处取一个字数据,则取出来的内容为78563412;从 地址0x0001处取一个字数据,则取出来的内容为9A785634。

注意:ARM7处理器在对数据操作时要边界对齐,要找到正确的地址。

各条件码标志位的具体含义

标志位 N Z 含义 运算结果的符号位。对于有符号二进制补码,结果为负时,N=1;结果为正或零时, N=0。 Z=1表示运算的结果为零(通常表示比较结果“相等”);Z=0表示运算的结果不为 零。 分4种情况设置C的值 - 加法运算 当运算结果产生进位时,C=1;否则C=0 - 减法运算 当运算产生借位时,C=0;否则C=1 - 包含移位操作的非加/减运算指令 C为移出值的最后一位 - 其他的非加/减运算指令 C的值通常不变 分2种情况设置V的值 - 加/减法运算指令 当发生有符号溢出时,V=1;否则,V=0 - 其他的非加/减运算指令 V的值通常不变

3、和51系列相似的中断向量结构; 4、支持协处理器。

ARM7微处理器核功能 框图

A[31:0]:地址总线。 D[31:0]:数据总线。 ABORT:存储器中止逻辑。 BIGEND:数据格式大端、小 端控制逻辑。 MAS[1:0]:决定数据字长的 控制逻辑。 nFIQ:快速中断请求逻辑。 nIRQ:通用中断请求逻辑。 DM[4:0]:处理器工作模式控 制逻辑。

AHB外设 VPB外设

0xFFFF FFFF 0xF000 0000 0xE000 0000

保留给外部存储器 0x8000 0000

2.0GB

Boot Block (从片内Flash存储器重新映射) 保留给片内存储器

第章ARM7体系结构ppt课件

5.处理器状态

14.ARM7指令简介

6.处理器模式

15.协处理器接口

7.内部寄存器

16.调试接口简介

8. 程序状态寄存器

17.ETM接口简介

• 1.3 ARM7TDMI的模块和内核框图

DBGRNG(0) DBGRNG(1) DBGEXT(0) DBGEXT(1)

LOCK WRITE SIZE[1:0] PROT[1:0] TRANS[1:0] ADDR[31:0]

1.2 ARM7TDMI

• 存储器访问

ARM7TDMI处理器使用了冯·诺依曼(Von Neumann)结构,指令和数据共用一条32位总线。 只有装载、存储和交换指令可以对存储器中的数据 进行访问。

数据可以是字节( 8位)、半字( 16位)或者 字(32位)。

1.2 ARM7TDMI

• 存储器访问

高的指令吞吐量; 出色的实时中断响应; 小的、高性价比的处理器宏单元。

1.2 ARM7TDMI

• 三级流水线

ARM7TDMI处理器使用流水线来增加处理器指 令流的速度。这样可使几个操作同时进行,并使处 理和存储器系统连续操作,能提供0.9MIPS/MHz的 指令执行速度。

ARM7TDMI的流水线分3级,分别为: 取指译码执行

1.1 ARM简介

• ARM处理器核简介——Xscale

Intel Xscale微控制器则提供全性能、高性价比、 低功耗的解决方案,支持16位Thumb指令并集成数 字信号处理(DSP)指令。

第3章 目录

1.简介

9.异常

2.ARM7TDMI

10.中断延迟

3.ARM7TDMI的模块和 11.复位

ARM7系列广泛应用于多媒体和嵌入式设备, 包括Internet设备、网络和调制解调器设备,以及 移动电话、PDA等无线设备。

ARM7体系结构详细介绍

ARM7体系结构详细介绍简介ARM(Advanced RISC Machines)是一种32位的RISC(Reduced Instruction Set Computer)处理器架构,广泛应用于嵌入式系统、智能手机和平板电脑等领域。

ARM7是ARM体系结构中的一代经典产品,采用了精简指令集,具有低功耗、高效能和高性价比等特点。

架构特性处理器核心ARM7处理器核心是一个半导体芯片,包含了用于指令解码、执行、访存等任务的硬件单元。

ARM7采用了5级流水线架构,可以实现超过20万条指令每秒的处理性能。

此外,ARM7支持可选的乘法器、除法器和调试接口,以满足不同的应用需求。

寄存器ARM7提供了一组寄存器来存放指令和数据。

寄存器分为通用寄存器和特殊目的寄存器两种。

通用寄存器包括16个32位的寄存器,用于存储临时数据和计算结果。

特殊目的寄存器包括程序计数器(PC)、堆栈指针(SP)等,用于指导程序执行和管理堆栈。

存储器ARM7的存储器包括内部存储器和外部存储器两部分。

内部存储器分为指令存储器和数据存储器,用于存放程序指令和数据。

外部存储器通常是闪存、RAM等,用于扩展存储容量。

ARM7支持32位的地址总线,可以寻址最多4GB的内存空间。

性能与功耗ARM7采用了先进的CMOS工艺,使得它具有低功耗和高性能的特性。

ARM7的功耗通常在几个毫瓦到几十个毫瓦之间,可以满足嵌入式系统对功耗的严格要求。

同时,ARM7的高性能使得它可以处理复杂的计算任务,例如图像处理、音视频处理等。

调试与开发ARM7支持ARM公司定义的JTAG调试接口,可以通过调试器进行程序的单步调试、断点设置等操作。

此外,ARM7还提供了丰富的开发工具和软件支持,开发者可以使用C语言、汇编语言等进行编程,方便快捷地开发ARM7的应用程序。

应用领域由于ARM7具有低功耗、高效能和高性价比等特点,因此广泛应用于各种嵌入式系统和移动设备。

下面是一些主要的应用领域:嵌入式系统ARM7在嵌入式系统中得到了广泛的应用,例如工业控制、智能家居、汽车电子等领域。

ARM7体系结构详细说明

922T:带有独立的8位 数据和指

多到35%;

令;

在0.13µm工艺下最高性能可达到300( 2.1

940T–包括更小数据和指令和一

测试标准);

个

集成了数据和指令;

32位总线接口的支持;

可在0.18µm、 0.15µm和0.13µm工艺的硅芯

片上实现。

3.1 简介

9E

926: 技术,有,可配置的数据和 9E是针对微控制器、和的单处理器解决方案;

公司开发了很多系列的处理器核,目前最新的 系列已经是11了,而6核以及更早的系列已经很罕 见了。目前应用比较广泛的系列是:

7

9

9E

10

11

3.1 简介

ARM7

预取

译码

执行

(Fetch) (Decode) (Execute)

ARM9

预取

译码

执行

访存

写入

(Fetch) (Decode) (Execute) (Memory) (Write)

3.1 简介

各体系结构版本

体系结构从最初开发到现在有了很大的改进, 并仍在完善和发展。为了清楚的表达每个应用实例 所使用的指令集,公司定义了6种主要的指令集体 系结构版本,以版本号V1~V6表示。

3.1 简介

各体系结构版本——V1

该版本的体系结构,只有26位的寻址空间,没 有商业化,其特点为: 基本的数据处理指令(不包括乘法); 字节、字和半字加载/存储指令; 具有分支指令,包括在子程序调用中使用的分支和 链接指令; 在操作系统调用中使用的软件中断指令。

ቤተ መጻሕፍቲ ባይዱ

预取

发送

译码

执行

访存

写入

ARM10 (Fetch) (Issue) (Decode) (Execute) (Memory) (Write)

《微机原理与嵌入式系统基础》课件第2章

第 2 章 ARM7 体系结构

ARM7采用ARM v4T结构,分为三级流水线,具有如下 特点:

(1) RISC处理器结构。 (2) 具有嵌入式ICE-RT逻辑,调试开发方便。 (3) 极低的功耗,适合对功耗要求较高的应用,如便携式 产品。 (4) 能够提供0.9 MIPS/MHz的三级流水线结构。 (5) 支持32位的ARM指令集和16位的Thumb指令集。 (6) 直接支持8 bit、16 bit和32 bit数据操作。 (7) 对操作系统的支持广泛,包括WinCE、Linux、Palm OS等。

第 2 章 ARM7 体系结构

在计算机体系结构中,另外一个重要的内容是存储器体系 结构。现在常用的有两种:冯·诺依曼存储器体系结构和哈佛 存储器体系结构。传统的计算机采用冯·诺依曼结构存储体系, 也称为普林斯顿结构,是一种将程序指令存储器和数据存储器 合并在一起编址的存储器结构,其主要特征是:程序和数据共 用一个存储空间,只是安排在不同的地址空间位置;取指和取 数操作使用同一套总线,只是在不同的时间访问不同的目标存 储单元。目前使用冯·诺依曼结构的MPU(微处理器)和MCU(微 控制器)有很多,如Intel 8086、ARM公司的ARM7、MIPS公司 的MIPS处理器等。

第 2 章 ARM7 体系结构

第2章 ARM7 体系结构

2.1 概述 2.2 ARM7的状态与模式 2.3 ARM7的寄存器 2.4 ARM7当前程序状态寄存器(CPSR) 2.5 ARM7的异常与异常处理 2.6 ARM7的存储系统 本章小结 习题

第 2 章 ARM7 体系结构

2.1 概 述

所谓处理器的“体系结构”(或称为“系统结构”),是 处理器的逻辑抽象,是指程序员在使用某处理器编制程序时, 所“看到”从而可以在程序中使用的处理器资源构成、使用方 式、工作原理及其相互间的关系。其中最为重要的就是处理器 所提供的指令系统和寄存器组模型。

chapter2ARM7体系结构

系统

(sys)

用于支持操作系统的特 与用户模式类似,但具有可以

权任务等 这五种模式直称接为切换异到常其它模模式式等。特权

快快中中断断 ((ffiiqq)) 支 道持处它高理们速数除据了传输可及以通通过FIQ程异常序响切应时换进进入此入模外式 ,

中中断断 ((iirrqq)) 用于也通可用中以断由处理特定的异IRQ常异常进响入应时。进当入此特模定式

冯·诺依曼存储器体系结构和哈佛存储器体 系结构

2020/4/11

西安邮电学院 计算机系

page 6

1. RISC处理器

RISC是精简指令集计算机的缩写,其目标是设计出 在高时钟频率下单周期执行,简单而有效的指令集。 RISC处理器具有以下特点: ① 采用LOAD/STORE结构。因为访问存储器指令所需 要的时间比较长,在指令系统中要尽量减少这类指 令,所以RISC指令中只保留不可再少的 LOAD/STORE两种存储器访问指令; ② 硬布线控制逻辑。使得大多数指令在单周期内执行 完成,以减少微程序技术中的指令解释开销; ③ 减少指令和寻址方式的种类。寻址方式简单,指令 系统小; ④ 指令长度固定。

(abt) 用 存于 储可资支 器以源持保虚护使。拟用内存这和个/或模式在A访RM问7TD一M些I没有受大控用处的

(und)

支持硬件协处理器的软 件仿真

未定义指令异常响应时进入此 模式

2020/4/11

西安邮电学院 计算机系

page 19

ARM7处理器约定了进入到5种异常模式的 对应事件:

① 管理模式(svc):复位或执行SWI软中断指 令时,进入该模式。

Power/Power PC 9% MIPS 6%

2020/4/11

嵌入式系统及应用第2章 ARM7及其体系结构2

2.9 异常

• 进入异常

在异常发生后,ARM7TDMI内核会作以下工作: 2.将CPSR复制到适当的SPSR中; 3. 将CPSR模式位强制设置为与异常类型相对应的值; 4.强制PC从相关的异常向量处取指。

2.9 异常

• 进入异常

ARM7TDMI内核在中断异常时置位中断禁止标 志,这样可以防止不受控制的异常嵌套。 注:异常总是在ARM状态中进行处理。当处理器处 于Thumb状态时发生了异常,在异常向量地址装入 PC时,会自动切换到ARM状态。

中断处理代码的开始部分和退出部分

SUB LR,LR,#4

;计算返回地址

STMFD SP!,{R0-R3,LR} ;保存使用到的寄存器

...

LDMFD SP!,{R0-R3,PC}^ ;中断返回

2.9 异常

• 异常的入口和出口处理

如果异常处理程序已经把返回地址拷贝到堆栈, 那么可以使用一条多寄存器传送指令来恢复用户寄 存器并实现返回。

2.9 异常

• 进入异常

在异常发生后,ARM7TDMI内核会作以下工作:

1.在适当的LR中保存下一条指令的地址,当异常入 口来自:

ARM状态,那么ARM7TDMI将当前指令地址 加4或加8复制(取决于异常的类型)到LR中; 为 Thumb 状 态 , 那 么 ARM7TDMI 将 当 前 指 令 地址加4或加8 (取决于异常的类型)复制到LR 中;异常处理器程序不必确定状态。

2.9 异常

• 简介

只要正常的程序流被暂时中止,处理器就进入 异常模式。例如响应一个来自外设的中断。在处理 异常之前,ARM7TDMI内核保存当前的处理器状 态,这样当处理程序结束时可以恢复执行原来的程 序。

如果同时发生两个或更多异常,那么将按照固 定的顺序来处理异常,详见“异常优先级”部分。

第2章 ARM7-9体系结构

主讲人:吴贵芳

2019/11/29

电子信息工程学院

吴贵芳 easyfancy@ qq:6974784

主要内容

1.ARM简介

6.ARM内部寄存器

2.ARM7/9TDMI

7.当前程序状态寄存 器

3.ARM的模块、内 核和功能框图

8.ARM体系的异常、 中断及其向量表

• M系列为微控制核,针对成本敏感的嵌入 式控制应用

Henan University of Sci. & Tech.

11

电子信息工程学院

吴贵芳 easyfancy@ qq:6974784

内核

MIPS 32位处理器内核系列和特点

特点

M4KTM系列

针对多CPU集成的SOC应用领域为下一代消 费类产品、下一代网络和宽带产品

Henan University of Sci. & Tech.

10

电子信息工程学院

吴贵芳 easyfancy@ qq:6974784

ARMv7 Cortex系列

ARMv7版体系结构定义了3种不同的微处 理器系列:

• A系列为面向应用的微处理器核,支持复 杂操作系统和用户应用

• R系列为深度嵌入的微处理器核,针对实 时系统应用

Cortex-M3主要应用于汽车车身系统,工业控制系 统和无线网络等对功耗和成本敏感的嵌入式应用领域。 目前最便宜的基于该内核的ARM单片机售价为1美元。

Henan University of Sci. & Tech.

15

电子信息工程学院

吴贵芳 easyfancy@ qq:6974784

Henan University of Sci. & Tech.

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ARM处理器使用流水线来增加处理器指令流 的速度,这样可使几个操作同时进行,并使处理 和存储器系统连续操作,能提供0.9MIPS/MHz的 指令执行速度。

ARM7TDMI的流水线分3级,分别为:

取指

译码

执行

完成该指令对应的操作 对已取入到处理器的指令进行译码分析

从存储器取指令到处理器

06.12.2020

page 13

处理器状态

ARM7TDMI处理器内核包含2套指令系统, 分别为ARM指令集和Thumb指令集,并且 各自对应1种处理器的状AR态M指:令集

ARM状态:32位,处理器执行字方式的ARM 指令,处理器默认为此Th状um态b ;指令集

Thumb状态:16位,处理器执行半字方式的 Thumb指令。

使用地址自增和自减支的持寻Em址bed方edI式CE观优察化硬件程;序循环; 支持64位乘法;

装载/保存指令对数据支的持片批上量调试传;输,实现最大数据吞

吐量;

支持高密度16位的Thumb指令集;

大多数指令的条件执行,实现最快速的代码执行。

06.12.2020

可编辑ppt

page 9

3. ARM7处理器的三级流水线

注意:两个状态之间切换并不影响处理器模式或寄存器内容。

; PC+4=0x400C

7. …

06.12.2020

可编辑ppt

page 12

第2章 目录

1. ARM7体系结构 2. ARM7的状态与模式 3. ARM7的寄存器 4. ARM7当前程序状态

寄存器(CPSR) 5. ARM7的异常与异常处理 6. ARM7的存储系统

06.12.2020

可编辑ppt

ARM公司的特点是只设计芯片,而不生产。 它将技术授权给世界上许多著名的半导体、 软件和OEM厂商,并提供服务。

06.12.2020

可编辑ppt

page 4

将技术授权给其它芯片厂商 ...

形成各具特色的ARM芯片

在目前的嵌入式系统开发中,你选用的是基于以下哪种架构的

X86 21%

芯片?

SH3/SH4 1%

06.12.2020

可编辑ppt

page 7

2. ARM7 体系结构

ARM7采用ARM v4T结构,分为三级流水,具 有如下特点:

① RISC处理器结构; ② 能够提供0.9MIPS/MHz的三级流水线结构; ③ 支持32位的ARM指令集和16位的Thumb指令集; ④ ARM7所有的指令都可以条件执行,使得程序设计

更适合流水线的工作特点; ⑤ 专用的存储器访存指令(Load/Store)。其它所有

指令都是寄存器操作指令。

06.12.2020

可编辑ppt

page 8

为了使ARM能够更好地满足嵌入式应用 的需要,ARM体系结构还有以下特点:

每条数AR据M7处TD理M指I-S令可A版同R本M时(7T软包D核M含)I 的,算可对综术应合用逻(工s辑y程n师th单e来si说z元ab其l(e编)ALU) 的运算和移位处理,程实模现型与AALRUM和7TD移MI位一致器;的最大利用;

可编辑ppt

page 10

三级流水线结构的指令执行顺序

PC PC-8 4

PC+4

…… 指令1 指令2 指令3 指令4 ……

程序存储器

周期1 周期2 周期3 周期4 周期5 周期6

处理器执行一条 取指 译码 执行 指令的三个阶段

取指 译码 执行

取指 译码 执行

取指 译码 执行

1234 在第1234个个周周期期,,P指PCC令指指1向向执指指行令令完123成,,,此此指时时令指指2令令和1 进 1指进入 令入3三三流级级水流流线水水推线线进的的一取译 执级指码 行,阶阶同段段时。,开同指始时令指取2令进出4入的指译取 令 码 指阶 处2。段 理, 。取出指令3。

Power/Power PC 9% MIPS 6%

06.12.2020

可编辑ppt

ARM 63%

page 5

2.1 ARM7体系结构

“体系结构”(或称为“系统结构”), 是处理器的逻辑抽象,是指程序员在使用 某处理器编制程序时,所“看到”从而可 以在程序中使用的处理器资源构成、使用 方式、工作原理及其相互间的关系。其中 最为重要的就是处理器所提供的指令系统 和寄存器组模型。

第2章 ARM7体系结构

06.12.2020

可编辑ppt

page 1

第2章 目录

1. ARM7体系结构 2. ARM7的状态与模式 3. ARM7的寄存器 4. ARM7当前程序状态寄存器(CPSR) 5. ARM7的异常与异常处理 6. ARM7的存储系统

06.12.2020

可编辑ppt

page 2

冯·诺依曼存储器体系结构和哈佛存储器 体系结构

06.12.2020

可编辑ppt

page 6

1. RISC处理器

RISC是精简指令集计算机的缩写,其目标是设计出 在高时钟频率下单周期执行,简单而有效的指令集。 RISC处理器具有以下特点: ① 采用LOAD/STORE结构。因为访问存储器指令所需 要的时间比较长,在指令系统中要尽量减少这类指 令,所以RISC指令中只保留不可再少的 LOAD/STORE两种存储器访问指令; ② 硬布线控制逻辑。使得大多数指令在单周期内执行 完成,以减少微程序技术中的指令解释开销; ③ 减少指令和寻址方式的种类。寻址方式简单,指令 系统小; ④ 指令长度固定。

06.12.2020

可编辑ppt

page 11

程序清单 2-1

1. 0x4000 ADD PC , PC , #4 ; 正在被执行的指令

2.

+4

;PC ← PC当前值

3. 0x4004 cmd2

; 正在被译码的指令;

4. 0x4008 cmd3

; 正在被取指的指令

5.

;PC = 0x4008

6. 0x400C cmd4

第2章 目录

1. ARM7体系结构 2. ARM7的状态与模式 3. ARM7的寄存器 4. ARM7当前程序状态

寄存器(CPSR) 5. ARM7的异常与异常处理 6. ARM7的存储系统

06.12.2020

可编辑ppt

page 3

ARM简介

ARM公司简介

ARM是Advanced RISC Machines的缩写, 它是一家微处理器行业的知名企业,该企 业设计了大量高性能、廉价、耗能低的 RISC (精简指令集)处理器。