一份通用 Makefile示例

makefile -d 用法

makefile -d 用法Makefile 文件用于构建和管理项目,指导make 工具完成自动化编译、链接和部署等工作。

下面是一个示例的Makefile 文件的用法:1. 定义变量:CC = gccCFLAGS = -Wall -Werror可以通过定义变量来设置编译器和编译选项,方便后续的使用。

2. 定义目标和规则:all: targettarget: dependencies(CC) (CFLAGS) -o target dependency_files`all` 是Makefile 的默认目标,当直接运行make 命令时,会执行all 目标下的规则。

`target` 是需要生成的目标文件,例如可执行程序等。

`dependencies` 是生成`target` 所依赖的文件,也可以是其他目标。

`(CC) (CFLAGS)` 是编译器和编译选项。

`-o target` 指定生成的目标文件名。

`dependency_files` 是`target` 的依赖文件,即需要编译的源文件。

3. 添加其他规则:例如,可以添加clean 规则用于清理生成的文件:clean:rm -f target其中`clean` 是目标名,`rm -f target` 是执行的命令,用于删除生成的`target` 文件。

4. 执行make 命令:在终端中执行`make` 命令即可根据Makefile 文件中的规则自动编译、链接和生成目标文件。

以上是Makefile 文件的一些基本用法,根据具体需求可以添加其他规则和变量。

详细使用方式可以参考GNU make 的官方文档。

Makefile万能通用版(C++和C混合编译也适用)

Makefile万能通用版(C++和C混合编译也适用)

1.、该Makefile 是我自己写的,可用于编译均是.c文件的工程,基本不用修改什么东西。

2、将该文件拷贝到工程文件夹下,在终端执行:

#make create (将会在根目录下创建出include, src, bin 三个目录)

#make 即可编译

#make clean 删除所有生成的中间文件和可执行文件

3、如果需要编译C++的.cpp和C语言的.c文件,即C 、C++混合编译,将CC=gcc 改为CC=g++即可。

(如果还不行,那就需要在.cpp文件的extern “C”中将被调用的.c声明一下,或者将所有.c 文件做成成静态库,后者适合.c文件较多的情况)CC=gcc CFLAGS=-o

PARAM=-Wall

CUR=$(shell pwd)

SRC=$(CUR)/src

SRCS=$(SRC)/*.c

TARGET=$(CUR)/bin/exe

.PHONY:$(TARGET)

all:$(TARGET)

$(TARGET):$(SRCS)

$(CC) $^ $(CFLAGS) $@ $(PARAM)

clean:

@-rm -rf $(TARGET)

@-rm -rf $(CUR)/include/*~

@-rm -rf $(SRC)/*~

@-rm -rf $(CUR)/*~

create:

@-mkdir src/

@-mkdir include/ @-mkdir bin/。

gmake语法

gmake语法GNU Make(通常简称为gmake)是一种构建工具,用于自动化构建程序和软件。

它使用一个名为Makefile的文件来描述构建过程。

下面是一个简单的gmake语法示例:'''makefile# 定义编译器CC = gcc# 定义编译选项CFLAGS = -Wall -g# 定义目标文件TARGET = myprogram# 定义依赖文件DEPS = myprogram.h# 定义规则all: $(TARGET)$(TARGET): $(DEPS)$(CC) $(CFLAGS) -o $@ $^clean:rm -f $(TARGET)'''这是一个简单的Makefile,它包含了一些基本的规则和变量。

下面是对每个部分的解释:1. 'CC':定义编译器,这里使用gcc。

2. 'CFLAGS':定义编译选项,这里使用-Wall和-g。

3. 'TARGET':定义目标文件,这里是myprogram。

4. 'DEPS':定义依赖文件,这里是myprogram.h。

5. 'all':定义默认规则,它依赖于目标文件$(TARGET)。

当只输入gmake命令时,会执行此规则。

6. '$(TARGET)':定义一个目标规则,它依赖于依赖文件$(DEPS)。

当需要构建目标文件时,会执行此规则。

规则中的'$(CC) $(CFLAGS) -o $@ $^'表示使用编译器和编译选项来编译依赖文件,并将输出命名为目标文件。

'$@'表示目标文件名,'$^'表示所有依赖文件的列表。

7. 'clean':定义一个清理规则,当输入gmake clean命令时,会执行此规则。

它会删除目标文件。

这只是gmake语法的一个简单示例,实际的Makefile可能会更复杂,包含更多的规则和变量。

[转]makefile文件的编写规则及实例

![[转]makefile文件的编写规则及实例](https://img.taocdn.com/s3/m/b6cc746d0a1c59eef8c75fbfc77da26925c596a1.png)

[转]makefile⽂件的编写规则及实例1.⼀个简单的makefile例⼦假设⼀个程序有两个⽂件file1.c,file2.c,每个⽂件都包含head.h,⽣成file可执⾏⽂件file:file1.o file2.o 附属⾏(⽂件的依存关系)gcc -o file1.o file2.o 命令⾏file1.o:file1.c head.hgcc -c file1.cfile2.o:file2.c head.hgcc -c file2.c从file最终的⽬标⽂件开始倒推,依次列出⽂件的依存关系,make在执⾏时:(1)判断file可执⾏⽂件是否存在,若不存在,则执⾏命令⾏,向下寻找依存关系(2)若file存在,则检查依靠⽂件,是否存在更新,若存在更新则执⾏命令⾏,若没有更新则给出提⽰:make:'file' is up to date.2.makefile中的宏定义及内部变量宏定义:OBJS = file1.o file2.oCC = gccCFLAGS = -wall -O -g引⽤:file:$(OBJS)$(CC) $(OBJS) -o filefile1.o:file1.c head.h$(CC) $(FLAGS) -c file1.cfile2.o:file2.c head.h$(CC) $(FLAGS) -c file2.c内部变量:$@:当前规则的⽬的⽂件名$<:依靠列表中的第⼀个依靠⽂件$^:整个依靠列表file:$(OBJS)$(CC) $^ -o $@file1.o:file1.c head.h$(CC) $(FLAGS) -c $< -o $@file2.o:file2.c head.h$(CC) $(FLAGS) -c $< -o $@"$(CC) $(FLAGS) -c $< -o $@"是隐含规则,可以不写,默认使⽤此规则3.假象假设⼀个项⽬要⽣成两个可执⾏⽂件file1和file2,这两个⽂件是相与独⽴的,则在makefile开始处:all:file1 file2make总是假设all要⽣成,去检查它的依赖⽂件4.清除由make产⽣的⽂件clean:rm *.orm file执⾏:make clean则会清除由make⽣成的*.o和file⽂件如果有clean⽂件存在,则清除不会执⾏(因clean没有可依赖的⽂件,永远是最新的)使⽤PHONY⽬标,避免同名⽂件相冲突,不会检查clean⽂件存在与否,都要执⾏清除操作.PHONY : cleanclean:rm *.orm file5.makefile函数搜索当前⽬录,⽣成由*.c结尾的⽂件列表,wildcard--函数名SOURCE = $(wildcard *.c)⽤%.o替换$(SOURCE)中的%.c⽂件OBJS = $(patsubst %.c,%.O,$(SOURCE))6.产⽣新规则SOURCE = $(wildcard *.c)depends:$(SOURCE)gcc -M $(SOURCE) > depends(为每⼀个.c⽂件产⽣规则,c⽂件和相关头⽂件为依靠)在makefile⽂件中:include depends7.⼀个有效的makefile⽂件可以完成⼤部分我们所需要的依靠检查,不⽤做太多的修改就可⽤在⼤多数项⽬⾥功能:搜索当前⽬录,寻找源码⽂件,放⼊SOURCE变量⾥,利⽤patsubst产⽣⽬标⽂件(*.o)CC = gccCFLAGS = -Wall -O -gSOURCE = $(wildcard *.c,*.cc)OBJS = $(patsubst %.c,%.o,$(patsubst,%.cc,%.o,$(SOURCE)))file:$(OBJS)$(CC) $^ -o $@⽤默认规则产⽣⽬标⽂件(*.o)1:编译可执⾏程序。

python makefile 用法

python makefile 用法Python Makefile可用于自动化编译,构建和测试Python项目。

它是一个命令脚本,帮助程序员在不同的操作系统上拥有相同的构建环境,减少了跨平台应用的开发难度。

本文将详细介绍Python Makefile的使用方法,包括如何创建,配置和使用Makefile,以及常见的Makefile命令和技巧。

创建Python Makefile要创建Python Makefile,您需要使用任何文本编辑器创建一个Makefile文件。

Makefile文件通常命名为Makefile或makefile,并位于项目根目录中。

在Makefile文件中,您需要定义一组规则,以指定每个目标的依赖关系,命令和操作。

以下是一个简单的Makefile示例,用于编译和执行名为myapp.py的Python 应用程序。

```make # Makefile for the myapp Python application# Define the application file APPNAME = myapp.py # Define the Python interpreter PYTHON = python3all: $(PYTHON) $(APPNAME)# Define the clean rule clean: rm -f *.pyc ```在上面的Makefile中,我们定义了两个规则,一个是`all`,另一个是`clean`。

`all`规则定义如何构建我们的应用程序,`clean`规则定义如何清理构建期间生成的文件。

配置Python Makefile在编写Python Makefile时,您需要配置Python解释器和其他环境变量。

以下是一些常见的Makefile变量和用法:- **PYTHON**:Python解释器的命令。

在大多数情况下,它需要设置为python3。

- **PYFLAGS**:Python解释器的选项和参数,例如“-O”(优化),“-m”(运行包的主模块)等。

【最新】makefile范例-word范文 (23页)

本文部分内容来自网络整理,本司不为其真实性负责,如有异议或侵权请及时联系,本司将立即删除!== 本文为word格式,下载后可方便编辑和修改! ==makefile范例篇一:实例—使用make及Makefile文件2.3 实例—使用make及Makefile文件一个工程有3个头文件(head1.h、head2.h、exam2.h)和8个C文件(main.c、exam1.c、exam2.c、exam3.c、exam4.c、exam5.c、exam6.c、exam7.c),建立一个Makefile文件(文件名为makefile),内容如下。

注意,上述12个文件位于同一个目录中。

gcc -o example main.o exam1.o exam2.o exam3.o exam4.o exam5.o exam6.o exam7.omain.o : main.c head1.hgcc -c main.cexam1.o : exam1.c head1.h exam2.hgcc -c exam1.cexam2.o : exam2.c head1.h exam2.hgcc -c exam2.cexam3.o : exam3.c head1.h head2.hgcc -c exam3.cexam4.o : exam4.c head1.h head2.hgcc -c exam4.cexam5.o : exam5.c head1.h head2.hgcc -c exam5.cexam6.o : exam6.c head1.h head2.h exam2.hgcc -c exam6.cexam7.o : exam7.c head1.hgcc -c exam7.cclean :rm example main.o exam1.o exam2.o exam3.o exam4.o exam5.o exam6.o exam7.omakefile文件告诉make命令如何编译和链接这几个文件。

一些通用的makefile模板

一些通用的makefile模板

以下是一个简单的通用Makefile模板,用于编译C/C++程序: Makefile.

# 定义编译器。

CC = gcc.

CXX = g++。

# 定义编译选项。

CFLAGS = -Wall.

CXXFLAGS = -Wall.

# 定义链接选项。

LDFLAGS =。

# 定义目标文件。

TARGET = program.

# 定义源文件。

SRCS = main.c file1.c file2.c. # 生成目标文件列表。

OBJS = $(SRCS:.c=.o)。

# 默认目标。

all: $(TARGET)。

# 生成可执行文件。

$(TARGET): $(OBJS)。

$(CC) $(LDFLAGS) -o $@ $^。

# 生成目标文件。

%.o: %.c.

$(CC) $(CFLAGS) -c -o $@ $<。

# 清理生成的文件。

clean:

rm -f $(OBJS) $(TARGET)。

这个模板包含了常见的Makefile设置,包括了编译器的定义、编译选项、链接选项、目标文件、源文件、生成目标文件和可执行文件的规则,以及清理生成文件的规则。

你可以根据自己的需求对其进行调整和扩展。

python makefile编写规则

Python Makefile编写规则随着Python语言的流行和应用范围的不断扩大,开发人员在日常工作中经常会用到Makefile来管理代码的编译和部署过程。

Makefile 是一个用于组织代码编译和部署流程的工具,它可以帮助开发人员自动化代码构建的过程,提高工作效率。

在Python项目中,编写规范的Makefile可以帮助开发人员管理项目中繁杂的编译和部署过程,本文将介绍Python Makefile编写的规则和技巧。

一、Makefile简介Makefile是一个包含一系列规则的文件,用于指定代码的编译和部署过程。

它通常由一系列规则、依赖关系和命令组成,它告诉make命令如何编译和信息代码。

Makefile通常用于C/C++项目的编译,但在Python项目中同样有着广泛的应用。

二、Python Makefile编写规则1. 定义变量在编写Python Makefile时,首先需要定义一些变量,这些变量可以用于存储编译器、编译选项、源文件目录、目标文件目录等。

下面是一个简单的Python Makefile示例:```MakefileCC = pythonCFLAGS = -O2SRC_DIR = srcOBJ_DIR = obj```2. 定义规则在Makefile中,可以定义一系列规则来指定如何编译和信息代码。

在Python项目中,通常会定义编译规则、信息规则和清理规则。

下面是一个简单的Python Makefile示例:```Makefileall: $(OBJ_DIR)/m本人n.o$(CC) $(CFLAGS) $(OBJ_DIR)/m本人n.o -o app$(OBJ_DIR)/m本人n.o: $(SRC_DIR)/m本人n.py$(CC) $(CFLAGS) -c $(SRC_DIR)/m本人n.py -o $(OBJ_DIR)/m本人n.oclean:rm -f $(OBJ_DIR)/*.o app```在上面的示例中,定义了三个规则:all规则用于编译信息代码生成可执行文件,$(OBJ_DIR)/m本人n.o规则用于编译源文件生成目标文件,clean规则用于清理生成的目标文件和可执行文件。

makefile 链接动态库的写法

makefile 链接动态库的写法在Makefile 中链接动态库时,你需要使用`-l` 标志指定要链接的库的名称。

同时,还需要使用`-L` 标志指定库文件的搜索路径(如果库文件不在标准路径中)。

以下是一个简单的Makefile 示例,演示如何链接动态库:```make# Makefile 示例# 编译器CC = gcc# 编译选项CFLAGS = -Wall -O2# 目标文件TARGET = my_program# 源文件SOURCE = main.c# 动态库名称LIBRARY = my_library# 动态库搜索路径LIBRARY_PATH = /path/to/library# 目标文件生成规则$(TARGET): $(SOURCE)$(CC) $(CFLAGS) -o $(TARGET) $(SOURCE) -L$(LIBRARY_PATH) -l$(LIBRARY)# 清理规则clean:rm -f $(TARGET)```在这个示例中:- `CC` 定义了编译器为`gcc`。

- `CFLAGS` 定义了编译选项,你可以根据需要进行调整。

- `TARGET` 定义了目标文件的名称。

- `SOURCE` 定义了源文件的名称。

- `LIBRARY` 定义了要链接的动态库的名称(不包括前缀`lib` 和后缀)。

- `LIBRARY_PATH` 定义了动态库的搜索路径。

在目标文件生成规则中,使用了`-L` 标志指定了库文件的搜索路径,使用`-l` 标志指定了要链接的库的名称。

请确保在实际路径中替换`LIBRARY_PATH` 和`LIBRARY` 的值,并根据需要修改其他参数。

使用`make` 命令执行这个Makefile,将会编译`main.c` 并链接到动态库,生成`my_program` 可执行文件。

省事之通用Makefile模版

省事之通⽤Makefile模版

现在编译⽅案都偏爱使⽤cmake解决问题,这两条做unity插件,还是⽤Makefile,居然忘得光光,好记性不如烂笔头。

后⾯,翻箱倒柜找到以前为炼⾦术写的Makefiel,发现还真是挺好⽤,贴出来,当万能Makefile模板挺好的。

PROJECT_DIR = ..

#PATH:=${ALCHEMY_HOME}/achacks:${PATH}

CC = gcc

AR = ar

CFLAGS := -Wall -W -std=gnu99 -g

LDFLAGS =

INCLUDE_DIR = -I$(PROJECT_DIR)/luajit/src

LIBNAME = libz.a

OBJS = $(patsubst ./%.c, %.o,$(wildcard ./*.c))

.PHONY: all clean

.SUFFIXES: .c .o

.c.o:

$(CC) $(CFLAGS) -c $< $(INCLUDE_DIR)

all: $(LIBNAME)

$(LIBNAME):$(OBJS)

@$(AR) rcs $(LIBNAME) $(OBJS)

ranlib $(LIBNAME)

clean:

@rm -rf $(LIBNAME) $(OBJS)

修改LIBNAME为你想要库名

在源码⽬录⽂件名为Makefile

只实现make 和make clean

如果c++的⾃⼰实现⼀下⾃动推导规则,看着也简单

另外,也改善⼀下对MinGW的印象,其实也挺好⽤的,不⼀定要⽤cmake⽣成vc解决⽅案,既然喜欢linux,为什么不能接受mingw呢?。

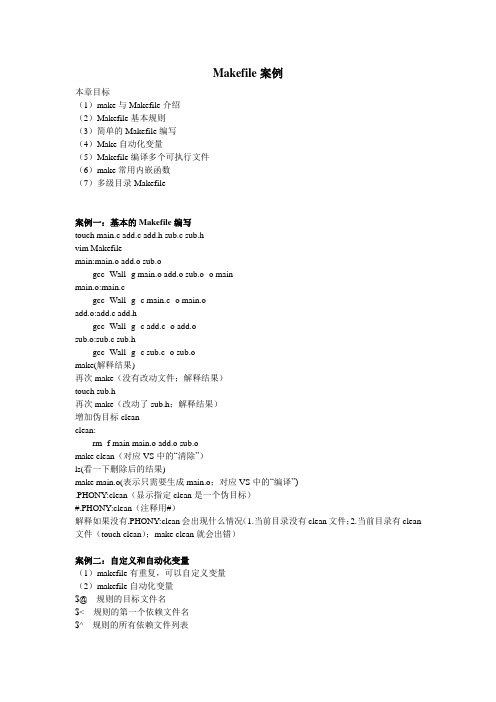

Makefile案例

Makefile案例本章目标(1)make与Makefile介绍(2)Makefile基本规则(3)简单的Makefile编写(4)Make自动化变量(5)Makefile编译多个可执行文件(6)make常用内嵌函数(7)多级目录Makefile案例一:基本的Makefile编写touch main.c add.c add.h sub.c sub.hvim Makefilemain:main.o add.o sub.ogcc -Wall -g main.o add.o sub.o -o mainmain.o:main.cgcc -Wall -g -c main.c -o main.oadd.o:add.c add.hgcc -Wall -g -c add.c -o add.osub.o:sub.c sub.hgcc -Wall -g -c sub.c -o sub.omake(解释结果)再次make(没有改动文件;解释结果)touch sub.h再次make(改动了sub.h;解释结果)增加伪目标cleanclean:rm -f main main.o add.o sub.omake clean(对应VS中的“清除”)ls(看一下删除后的结果)make main.o(表示只需要生成main.o;对应VS中的“编译”).PHONY:clean(显示指定clean是一个伪目标)#.PHONY:clean(注释用#)解释如果没有.PHONY:clean会出现什么情况(1.当前目录没有clean文件;2.当前目录有clean 文件(touch clean);make clean就会出错)案例二:自定义和自动化变量(1)makefile有重复,可以自定义变量(2)makefile自动化变量$@ 规则的目标文件名$< 规则的第一个依赖文件名$^ 规则的所有依赖文件列表main:main.o add.o sub.omain 规则的目标文件名main.o 规则的第一个依赖文件名main.o add.o sub.o 规则的所有依赖文件列表.PHONY:cleanOBJECTS=main.o add.o sub.o #自定义变量CC=gccCFLAGS=-Wall -gmain:$(OBJECTS)$(CC) $(CFLANGS) $^ -o $@main.o:main.c$(CC) $(CFLANGS) -c $< -o $@add.o:add.c add.h$(CC) $(CFLANGS) -c $< -o $@sub.o:sub.c sub.h$(CC) $(CFLANGS) -c $< -o $@clean:rm -f main $(OBJECTS)makefile文件名(1)Makefile(2)makefile(3)其他文件名:如Make.makefile(使用的时候需要选项-f)为了演示清楚:clean:echo “begin to delete...”对比:@echo “begin to delete...”@gcc ...案例三:Makefile编译多个可执行文件例子:test1.c和test2.c都有main函数.PHONY:clean all或.PHONY:cleanBIN=test1 test2all:$(BIN)clean:rm -f $(BIN)make后就可以生成可执行文件test1 test2查看输出:cc test1.c -o test1cc test2.c -o test2解释:(all是一个伪目标)隐含推导规则:同名的.c文件生成同名的可执行文件(不使用隐含规则,使用显式规则).PHONY:clean allBIN=test1 test2all:$(BIN)test1:test1.ogcc -Wall -g $^ -o $@test2:test2.ogcc -Wall -g $^ -o $@clean:rm -f *.o $(BIN)make之后观察输出,并解释tes1.o和tes2.o的产生也依赖自动推导规则案例四:模式规则和后缀规则模式规则:%.o:%.c后缀规则:.c.o:.PHONY:clean allBIN=test1 test2all:$(BIN)%.o:%.cgcc -Wall -g -c $< -o $@test1:test1.ogcc -Wall -g $^ -o $@test2:test2.ogcc -Wall -g $^ -o $@clean:rm -f *.o $(BIN)解释输出结果用.c.o:gcc -Wall -g -c $< -o $@结果类似%.o:%.c(增加变量CC=gcc CFLAGS=-Wall -g)注释掉下面信息,看结果test1:test1.ogcc -Wall -g $^ -o $@test2:test2.ogcc -Wall -g $^ -o $@增加test3.c增加pub.c pub.h(test3依赖文件test3.c pub.h pub.c)增加test4.c(作为测试程序;在BIN后加test4就行,轻松)make常用内嵌函数(1)函数调用$(function arguments)(2)$(wildcard PA TTERN)当前目录下匹配模式的文件如src=$(wildcard *.c)(3)$(patsubst PA TTERN,REPLACEMENT,TEXT) 模式替换函数如$(patsubst %.c,%.o,$src)等价于$(src:.c=.o)(4)shell函数执行shell命令如$(shell ls -d */)(显示目录)案例五:多级目录Makefile二级或三级目录例子// main.c// bll目录:bll.c bll.h// bll/test目录:test.c test.h// ui目录:ui.c ui.h// dal目录:dal.c dal.hMakefile.PHONY:cleanCC=gccCFLAGS=-Wall -gBIN=mainSUBDIR=$(shell ls -d */)ROOTSRC=$(wildcard *.c)ROOTOBJ=$(ROOTSRC:%.c=%.o)SUBSRC=$(shell find $(SUBDIR) -name '*.c')SUBOBJ=$(SUBSRC:%.c=%.o)$(BIN):$(ROOTOBJ) $(SUBOBJ)$(CC) $(CFLAGS) -o $(BIN) $(ROOTOBJ) $(SUBOBJ) .c.o:$(CC) $(CFLAGS) -c $< -o $@clean:rm -f $(BIN) $(ROOTOBJ) $(SUBOBJ)解释和演示案例六:多级目录的Makefile//test1目录:Makefile test1.c//test2目录:Makefile test2.cpp先看MakefileSUBDIRS=test1 test2.PHONY:default all clean $(SUBDIRS)all clean:$(MAKE) $(SUBDIRS) TARGET=$@$(SUBDIRS):$(MAKE) -C $@ $(TARGET)再看makefile的输出结果,进行解释结果:make test1 test2 TARGET=allmake[1]: Entering directory `/home/panlei/linux/makefile/mulmakefile'make -C test1 allmake[2]: Entering directory `/home/panlei/linux/makefile/mulmakefile/test1'----- make all in /home/panlei/linux/makefile/mulmakefile -----gcc -c test1.cgcc test1.o -o test1make[2]: Leaving directory `/home/panlei/linux/makefile/mulmakefile/test1'make -C test2 allmake[2]: Entering directory `/home/panlei/linux/makefile/mulmakefile/test2'----- make all in /home/panlei/linux/makefile/mulmakefile -----g++ -Wall -g -c -o test2.o test2.cppg++ -Wall -g test2.o -o test2make[2]: Leaving directory `/home/panlei/linux/makefile/mulmakefile/test2'make[1]: Leaving directory `/home/panlei/linux/makefile/mulmakefile'解释:make test1 test2 TARGET=all ($(MAKE)=make)make -C test1 all (-C:等价于make all test1/Makefile;传递all,执行test/Makefile)test1/MakefileCC=gccBIN=test1OBJS=test1.o.PHONY:all clean printall:print $(BIN)print:@echo "----- make all in $(PWD) -----"$(BIN):$(OBJS)$(CC) $(OBJS) -o $@%.o:%.c$(CC) -c $<clean:@echo "----- make clean in $(PWD) -----"rm -f $(BIN) $(OBJS)test2/MakefileCXX=g++OBJS=test2.oCPPFLAGS=-Wall -g.PHONY:all clean printall:print $(BIN)print:@echo "----- make all in $(PWD) -----"$(BIN):$(OBJS)$(CXX) $(OBJS) -o $@%.o:%.cpp$(CXX) -c $<clean:@echo "----- make clean in $(PWD) -----"rm -f $(BIN) $(OBJS)只看编译顺序:make -n一般来说,如果存在多级目录,那么再用makefile的时候,最好在每个目录下也写一个简单的子makefile,这样在总目录下写一个总的makefile,然后再总的makefile中调用子makefile,这样写起来就会比较清晰,编译顺序是要看总makefile中的步骤。

通用Makefile模板及实例

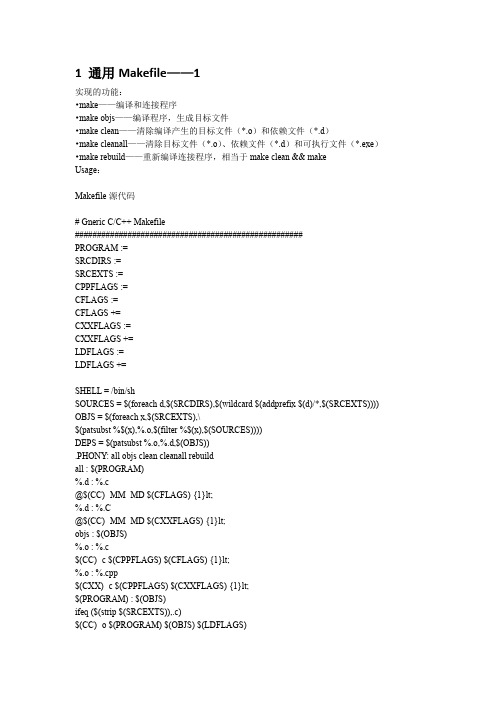

1 通用Makefile——1实现的功能:•make——编译和连接程序•make objs——编译程序,生成目标文件•make clean——清除编译产生的目标文件(*.o)和依赖文件(*.d)•make cleanall——清除目标文件(*.o)、依赖文件(*.d)和可执行文件(*.exe)•make rebuild——重新编译连接程序,相当于make clean && makeUsage:Makefile源代码# Gneric C/C++ Makefile####################################################PROGRAM :=SRCDIRS :=SRCEXTS :=CPPFLAGS :=CFLAGS :=CFLAGS +=CXXFLAGS :=CXXFLAGS +=LDFLAGS :=LDFLAGS +=SHELL = /bin/shSOURCES = $(foreach d,$(SRCDIRS),$(wildcard $(addprefix $(d)/*,$(SRCEXTS)))) OBJS = $(foreach x,$(SRCEXTS),\$(patsubst %$(x),%.o,$(filter %$(x),$(SOURCES))))DEPS = $(patsubst %.o,%.d,$(OBJS)).PHONY: all objs clean cleanall rebuildall : $(PROGRAM)%.d : %.c@$(CC) -MM -MD $(CFLAGS) {1}lt;%.d : %.C@$(CC) -MM -MD $(CXXFLAGS) {1}lt;objs : $(OBJS)%.o : %.c$(CC) -c $(CPPFLAGS) $(CFLAGS) {1}lt;%.o : %.cpp$(CXX) -c $(CPPFLAGS) $(CXXFLAGS) {1}lt;$(PROGRAM) : $(OBJS)ifeq ($(strip $(SRCEXTS)),.c)$(CC) -o $(PROGRAM) $(OBJS) $(LDFLAGS)else$(CXX) -o $(PROGRAM) $(OBJS) $(LDFLAGS)endif-include $(DEPS)rebuild: clean callclean:@$(RM) *.o *.dcleanall: clean@$(RM) $(PROGRAM) $(PROGRAM).exe2 通用Makefile——2############################################################################### ## Generic Makefile for C/C++ Program## Author: whyglinux (whyglinux AT hotmail DOT com)# Date: 2006/03/04# Description:# The makefile searches in <SRCDIRS> directories for the source files# with extensions specified in <SOURCE_EXT>, then compiles the sources# and finally produces the <PROGRAM>, the executable file, by linking# the objectives.# Usage:# $ make compile and link the program.# $ make objs compile only (no linking. Rarely used).# $ make clean clean the objectives and dependencies.# $ make cleanall clean the objectives, dependencies and executable.# $ make rebuild rebuild the program. The same as make clean && make all.#===================================================================== =========## Customizing Section: adjust the following if necessary.##==================================================================== =========# The executable file name.# It must be specified.# PROGRAM := a.out # the executable namePROGRAM :=# The directories in which source files reside.# At least one path should be specified.# SRCDIRS := . # current directorySRCDIRS :=# The source file types (headers excluded).# At least one type should be specified.# The valid suffixes are among of .c, .C, .cc, .cpp, .CPP, .c++, .cp, or .cxx.# SRCEXTS := .c # C program# SRCEXTS := .cpp # C++ program# SRCEXTS := .c .cpp # C/C++ programSRCEXTS :=# The flags used by the cpp (man cpp for more).# CPPFLAGS := -Wall -Werror # show all warnings and take them as errorsCPPFLAGS :=# The compiling flags used only for C.# If it is a C++ program, no need to set these flags.# If it is a C and C++ merging program, set these flags for the C parts.CFLAGS :=CFLAGS +=# The compiling flags used only for C++.# If it is a C program, no need to set these flags.# If it is a C and C++ merging program, set these flags for the C++ parts.CXXFLAGS :=CXXFLAGS +=# The library and the link options ( C and C++ common).LDFLAGS :=LDFLAGS +=## Implict Section: change the following only when necessary.##==================================================================== =========# The C program compiler. Uncomment it to specify yours explicitly.#CC = gcc# The C++ program compiler. Uncomment it to specify yours explicitly.#CXX = g++# Uncomment the 2 lines to compile C programs as C++ ones.#CC = $(CXX)#CFLAGS = $(CXXFLAGS)# The command used to delete file.#RM = rm -f## Stable Section: usually no need to be changed. But you can add more.##==================================================================== =========SHELL = /bin/shSOURCES = $(foreach d,$(SRCDIRS),$(wildcard $(addprefix $(d)/*,$(SRCEXTS))))OBJS = $(foreach x,$(SRCEXTS), \$(patsubst %$(x),%.o,$(filter %$(x),$(SOURCES))))DEPS = $(patsubst %.o,%.d,$(OBJS)).PHONY : all objs clean cleanall rebuildall : $(PROGRAM)# Rules for creating the dependency files (.d).#---------------------------------------------------%.d : %.c@$(CC) -MM -MD $(CFLAGS) $<%.d : %.C@$(CC) -MM -MD $(CXXFLAGS) $<%.d : %.cc@$(CC) -MM -MD $(CXXFLAGS) $<%.d : %.cpp@$(CC) -MM -MD $(CXXFLAGS) $<%.d : %.CPP@$(CC) -MM -MD $(CXXFLAGS) $<%.d : %.c++@$(CC) -MM -MD $(CXXFLAGS) $<%.d : %.cp@$(CC) -MM -MD $(CXXFLAGS) $<%.d : %.cxx@$(CC) -MM -MD $(CXXFLAGS) $<# Rules for producing the objects.#---------------------------------------------------objs : $(OBJS)%.o : %.c$(CC) -c $(CPPFLAGS) $(CFLAGS) $<%.o : %.C$(CXX) -c $(CPPFLAGS) $(CXXFLAGS) $<%.o : %.cc$(CXX) -c $(CPPFLAGS) $(CXXFLAGS) $<%.o : %.cpp$(CXX) -c $(CPPFLAGS) $(CXXFLAGS) $<%.o : %.CPP$(CXX) -c $(CPPFLAGS) $(CXXFLAGS) $<%.o : %.c++$(CXX -c $(CPPFLAGS) $(CXXFLAGS) $<%.o : %.cp$(CXX) -c $(CPPFLAGS) $(CXXFLAGS) $<%.o : %.cxx$(CXX) -c $(CPPFLAGS) $(CXXFLAGS) $<# Rules for producing the executable.#---------------------------------------------- $(PROGRAM) : $(OBJS)ifeq ($(strip $(SRCEXTS)), .c) # C file$(CC) -o $(PROGRAM) $(OBJS) $(LDFLAGS) else # C++ file$(CXX) -o $(PROGRAM) $(OBJS) $(LDFLAGS) endif-include $(DEPS)rebuild: clean allclean :@$(RM) *.o *.dcleanall: clean@$(RM) $(PROGRAM) $(PROGRAM).exe### End of the Makefile ## Suggestions are welcome ## All rights reserved ################################################################################## 下面提供两个例子来具体说明上面 Makefile 的用法。

makefile典型模板

makefile典型模板Makefile典型模板Sunny.man1.写在前⾯在这篇⽂章之前,曾经因为⾃⼰学习makefile⽂件写了⼀个笔记,笔记中简单的传述了⽂件的书写规范,我把此笔记上传⾯了⼀个⽂档,此⽂档不能称为⼀个合格的⽂档。

我在实际的使⽤过程中才发现,⽤上述⽂档来编写⼀个合格的makefile⽂件是远远不够的,为此我写了⼀个makefile模块供⼤家改写,毕竟我们要写的是应⽤程序⽽不是⼀个makefile⽂件。

我在学习makefile的过程中查阅了很多的资料,⾛了不少的弯路。

为了同⾏们把宝贵的时间⽤在⾃⼰的应⽤程序开发上,我写了这篇⽂档。

Makefile的要求如下1.快速编译,不更新的⽂件不重新编译。

2.当⼀个.c⽂件做修改时不需要⼿动添加依赖。

3.源⽂件放⼀个⽬录,头⽂件放⼀个⽬录,依赖放⼀个⽬录,⽬标⼀个⽬录。

4.头⽂件的修改会⾃动重新编译所有引⽤它的.c⽂件5.这个makefile⽂件⼀定是没有错误可以运⾏的,我认为这⼀点太重要的。

我在⽹上查的许多⽂件都根本不能运⾏,好多的⽂章代码部分都是⼀样的,难道只是转载的吗?2.直接上代码3.⼀些必要的解译3.1宏定义其实make本⾝已有许多的default的macro,如果要查看这些macro的话,可以⽤make -p的命令.这⾥不做过多解释。

3.2>debug.txt 2>&1把输出和错误重新定位到⽂件debug.txt3.3makefile中的函数makefile⾥的函数使⽤,和取变量的值类似,是以⼀个‘$’开始,然后是⼀个括号⾥⾯是函数名和需要的参数列表,多个变量⽤逗号隔开,像这样return = $(functionname arg1,arg2,arg3...)。

3.4$(wildcard $(SRCPATH)*.c)$(wildcard PATTERN...) ,在Makefile中,它被展开为已经存在的、使⽤空格分开的、匹配此模式的所有⽂件列表。

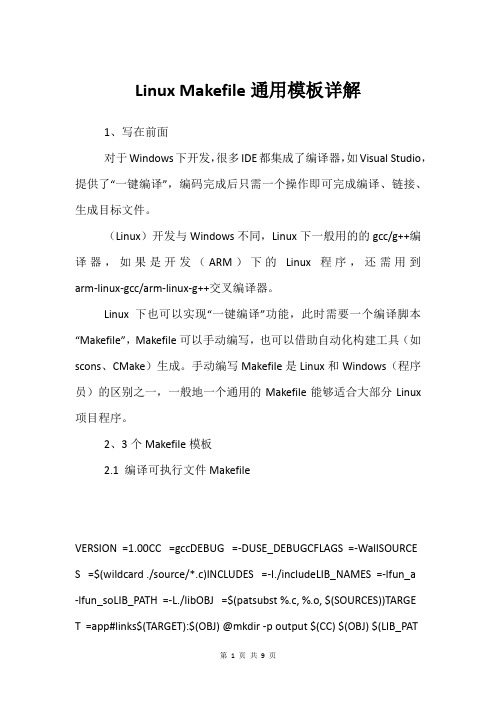

Linux Makefile通用模板详解

Linux Makefile通用模板详解1、写在前面对于Windows下开发,很多IDE都集成了编译器,如Visual Studio,提供了“一键编译”,编码完成后只需一个操作即可完成编译、链接、生成目标文件。

(Linux)开发与Windows不同,Linux下一般用的的gcc/g++编译器,如果是开发(ARM)下的Linux程序,还需用到arm-linux-gcc/arm-linux-g++交叉编译器。

Linux下也可以实现“一键编译”功能,此时需要一个编译脚本“Makefile”,Makefile可以手动编写,也可以借助自动化构建工具(如scons、CMake)生成。

手动编写Makefile是Linux和Windows(程序员)的区别之一,一般地一个通用的Makefile能够适合大部分Linux 项目程序。

2、3个Makefile模板2.1 编译可执行文件MakefileVERSION=1.00CC=gccDEBUG=-DUSE_DEBUGCFLAGS=-WallSOURCES=$(wildcard./source/*.c)INCLUDES=-I./includeLIB_NAMES=-lfun_a-lfun_soLIB_PATH=-L./libOBJ=$(patsubst%.c,%.o,$(SOURCES))TARGET=app#links$(TARGET):$(OBJ)@mkdir -p output$(CC)$(OBJ)$(LIB_PATH)$(LIB_NAMES) -o output/$(TARGET)$(VERSION)@rm -(rf)$(OBJ)#com(pi)le%.o:%.c$(CC)$(INCLUDES)$(DEBUG) -c$(CFLAGS)$【要点说明】【1】程序版本开发调试过程可能产生多个程序版本,可以在目标文件后(前)增加版本号标识。

VERSION=1.00$(CC)$(OBJ)$(LIB_PATH)$(LIB_NAMES) -o output/$(TAR GET)$(VERSION)【2】编译器选择Linux下为gcc/g++;arm下为arm-linux-gcc;不同(CPU)(厂商)提供的定制交叉编译器名称可能不同,如Hisilicon“arm-hisiv300-linux-gcc”。

makefile 语法

makefile 语法Makefile是一种常用的构建工具,用于自动化构建和管理软件项目。

它是一种文本文件,包含一系列规则,用于指定如何编译、链接和构建源代码。

本文将介绍 Makefile 的语法和使用方法。

一、Makefile 的基本语法Makefile 文件由一系列规则组成,每个规则由一个目标和一个或多个依赖项组成。

目标是要生成的文件名,依赖项是生成目标所需要的文件或命令。

当目标文件不存在或依赖项的时间戳比目标文件的时间戳更晚时,Makefile 将自动执行规则中的命令,生成目标文件。

一个简单的 Makefile 示例:```hello: main.cgcc -o hello main.c```这个 Makefile 包含了一个规则,目标是 hello,依赖项是main.c。

当 main.c 文件的时间戳比 hello 文件的时间戳更晚时,Makefile 将执行 gcc 命令编译 main.c 文件,并生成可执行文件hello。

Makefile 的规则语法如下:```target: dependenciescommand1command2...```其中,target 是规则的目标,dependencies 是规则的依赖项,command1、command2 等是要执行的命令。

命令必须以一个制表符或多个空格开头,否则 Makefile 将无法识别。

二、Makefile 的变量Makefile 中可以定义变量,用于存储常用的值或命令。

变量以$ 符号开头,可以在规则中使用。

变量的定义语法如下:```VARNAME = value```或者```VARNAME := value```其中,等号和冒号加等号的区别在于,等号定义的变量是递归展开的,而冒号加等号定义的变量是简单展开的。

递归展开的变量可以包含其他变量的引用,而简单展开的变量只能包含直接的值。

示例:```CC = gccCFLAGS = -Wall -O2hello: main.c$(CC) $(CFLAGS) -o hello main.c```这个 Makefile 中定义了两个变量 CC 和 CFLAGS,用于存储编译器和编译选项。

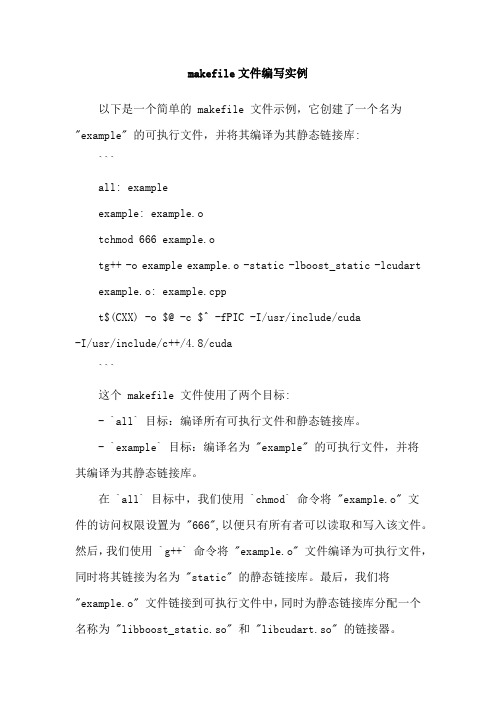

makefile文件编写实例

makefile文件编写实例以下是一个简单的 makefile 文件示例,它创建了一个名为"example" 的可执行文件,并将其编译为其静态链接库:```all: exampleexample: example.otchmod 666 example.otg++ -o example example.o -static -lboost_static -lcudart example.o: example.cppt$(CXX) -o $@ -c $^ -fPIC -I/usr/include/cuda-I/usr/include/c++/4.8/cuda```这个 makefile 文件使用了两个目标:- `all` 目标:编译所有可执行文件和静态链接库。

- `example` 目标:编译名为 "example" 的可执行文件,并将其编译为其静态链接库。

在 `all` 目标中,我们使用 `chmod` 命令将 "example.o" 文件的访问权限设置为 "666",以便只有所有者可以读取和写入该文件。

然后,我们使用 `g++` 命令将 "example.o" 文件编译为可执行文件,同时将其链接为名为 "static" 的静态链接库。

最后,我们将"example.o" 文件链接到可执行文件中,同时为静态链接库分配一个名称为 "libboost_static.so" 和 "libcudart.so" 的链接器。

在 `example` 目标中,我们使用 `$(CXX)` 命令来编译"example.cpp" 文件,并将其链接为静态链接库。

我们还指定了要链接的静态库和 CUDA 库。

这个 makefile 文件假定您已经在 "usr/include/cuda" 和"usr/include/c++/4.8/cuda" 文件夹中放置了必要的 CUDA 库。

一套的实用完整Makefile参考模板

∙一套的实用完整Makefile参考模板∙近来,经常看到有人询问makefile的写法,这里根据本人经验给出一个应用系统的完整例子,便于各位参考。

应用系统的目录结构如下:代码:~/bin 可执行程式目录~/etc 设置文件目录~/inc 头文件目录~/lib 函数库文件目录~/log 日志文件目录~/src 源程式文件目录~/src/lib 函数库源程式目录~/src/lib/LIB_1 函数库libLIB_1源程式目录~/src/APP_A 子系统APP_A源程式目录~/src/APP_A/mod_a 子系统APP_A模块mod_a源程式目录~/.profile~/makefile∙~/makefile文件内容如下:代码:all:@MakeSubDir() \{ \for DIR in `ls|grep ’lib’;ls|grep -v ’lib’`; do \if [ -d ${DIR} ]; then \cd ${DIR}; \MakeSubDir; \if [ -f makefile -o -f Makefile ]; then \echo ""; \pwd; \make all; \fi; \cd ..; \fi; \done; \}; \MakeSubDirtar:@tar -cf `date +%Y%m%d-%H%M%S`.tar .profile `ls|grep -v ’.tar’`~/src/lib/LIB_1/makefile文件内容如下:代码:ALL: INFO allBASEDIR = $(HOME)INC = $(BASEDIR)/incLIB = $(BASEDIR)/libPRDNAME = $(LIB)/libLIB_1PRODUCT = $(PRDNAME).a $(PRDNAME).soOBJS = LIB_1_f1.o LIB_1_f2.oAR = ar <特定平台ar可选参数>CC = cc <特定平台cc可选参数>all: $(PRODUCT)$(PRDNAME).a: $(OBJS)@echo " Making $@ ..."@$(AR) -r $@ $(OBJS)$(PRDNAME).so: $(OBJS)@echo " Making $@ ..."@$(CC) -G -o $@ $(OBJS).c.o: *.h $(INC)/*.h@echo " Compiling $< ..."@$(CC) -c -I$(INC) $<INFO:@echo " make all - same with ’make’ except this message"@echo " make clear - remove object files"@echo " make clean - remove all object and target files"@echo ""clear: FORCE@rm -f *.oclean: FORCE clear@rm -f $(PRODUCT)FORCE:~/src/APP_A/mod_a/makefile文件内容如下:代码:ALL: INFO allBASEDIR = $(HOME)INC = $(BASEDIR)/incLIB = $(BASEDIR)/libBIN = $(BASEDIR)/binMODULE = $(BIN)/APP_A_mod_aTESTER = APP_A_mod_a_tPRODUCT = $(SERVER) $(TESTER)CC = cc <特定平台cc可选参数>all: $(PRODUCT)$(MODULE): APP_A_mod_a.o@echo " Making $@ ..."@$(CC) $? -o$@ -L$(LIB) -lLIB_1APP_A_mod_a_t: APP_A_mod_a_t.o@echo " Making $@ ..."@$(CC) $? -o$@ -L$(LIB) -lLIB_1.c.o: *.h $(INC)/*.h@echo " Compiling $< ..."@$(CC) -c -I$(INC) $<INFO:@echo " make all - same with ’make’ except this message"@echo " make clear - remove object files"@echo " make clean - remove all object and target files"@echo ""clear: FORCE@rm -f *.oclean: FORCE clear@rm -f $(PRODUCT)FORCE:使用方法:1.在主目录下使用’make’命令能够首先建立函数库,然后建立所有目标。

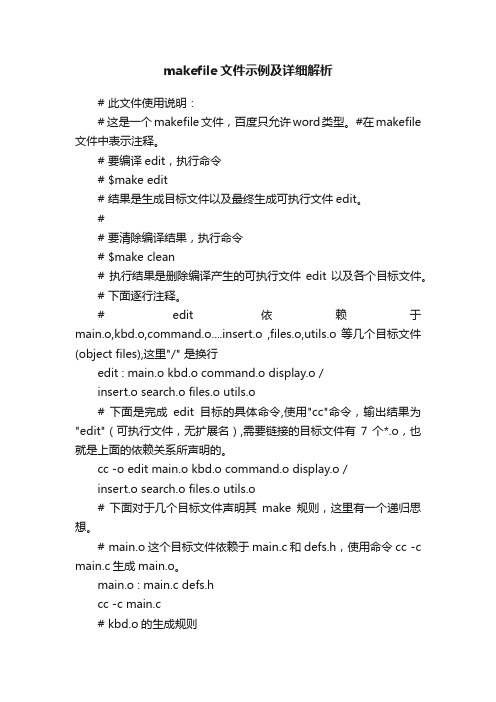

makefile文件示例及详细解析

makefile文件示例及详细解析# 此文件使用说明:# 这是一个makefile文件,百度只允许word类型。

#在makefile 文件中表示注释。

# 要编译edit,执行命令# $make edit# 结果是生成目标文件以及最终生成可执行文件edit。

## 要清除编译结果,执行命令# $make clean# 执行结果是删除编译产生的可执行文件edit以及各个目标文件。

# 下面逐行注释。

# edit 依赖于main.o,kbd.o,command.o....insert.o ,files.o,utils.o 等几个目标文件(object files),这里"/" 是换行edit : main.o kbd.o command.o display.o /insert.o search.o files.o utils.o# 下面是完成edit目标的具体命令,使用"cc"命令,输出结果为"edit"(可执行文件,无扩展名),需要链接的目标文件有7个*.o,也就是上面的依赖关系所声明的。

cc -o edit main.o kbd.o command.o display.o /insert.o search.o files.o utils.o# 下面对于几个目标文件声明其make规则,这里有一个递归思想。

# main.o这个目标文件依赖于main.c和defs.h,使用命令cc -c main.c生成main.o。

main.o : main.c defs.hcc -c main.c# kbd.o的生成规则kbd.o : kbd.c defs.h command.hcc -c kbd.c# command.o的生成规则command.o : command.c defs.h command.hcc -c command.c# display.o的生成规则display.o : display.c defs.h buffer.hcc -c display.c# insert.o的生成规则insert.o : insert.c defs.h buffer.hcc -c insert.c# search.o的生成规则search.o : search.c defs.h buffer.hcc -c search.c# files.o的生成规则files.o : files.c defs.h buffer.h command.hcc -c files.c# utils.o的生成规则utils.o : utils.c defs.hcc -c utils.c# 注意,这里声明另一个目标,使用make跟参数调用这个目标。

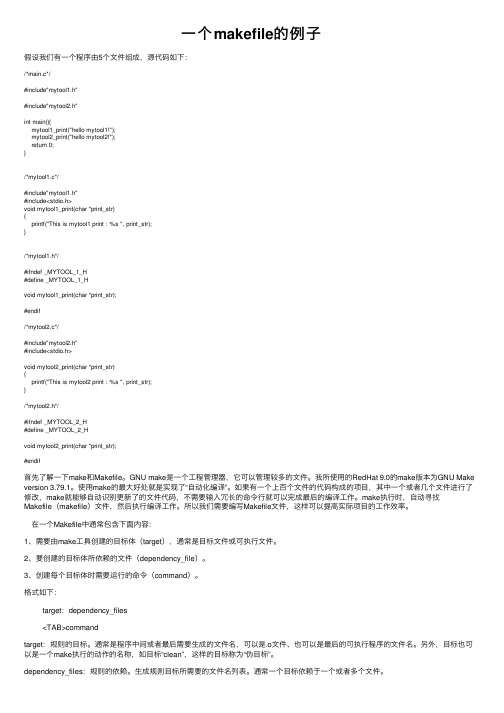

一个makefile的例子

⼀个makefile的例⼦假设我们有⼀个程序由5个⽂件组成,源代码如下:/*main.c*/#include"mytool1.h"#include"mytool2.h"int main(){mytool1_print("hello mytool1!");mytool2_print("hello mytool2!");return 0;}/*mytool1.c*/#include"mytool1.h"#include<stdio.h>void mytool1_print(char *print_str){printf("This is mytool1 print : %s ", print_str);}/*mytool1.h*/#ifndef _MYTOOL_1_H#define _MYTOOL_1_Hvoid mytool1_print(char *print_str);#endif/*mytool2.c*/#include"mytool2.h"#include<stdio.h>void mytool2_print(char *print_str){printf("This is mytool2 print : %s ", print_str);}/*mytool2.h*/#ifndef _MYTOOL_2_H#define _MYTOOL_2_Hvoid mytool2_print(char *print_str);#endif⾸先了解⼀下make和Makefile。

GNU make是⼀个⼯程管理器,它可以管理较多的⽂件。

我所使⽤的RedHat 9.0的make版本为GNU Make version 3.79.1。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

#----------------------#

ifneq ($(STD_FLAG),)

CFLAGS += $(STD_FLAG)

endif

#==========================================================

#SOURCES = $(foreach d,$(SRC_DIRS),$(wildcard $(addprefix $(d)/*,$(SRCEXTS))))

# options to and linker ones to

# (See Makefile.gtk+-2.0 for an example)

# * to search sources in more directories, set to <SRC_DIRS>

# * to specify your favorite program name, set to <APP>

APP = $(word $(words $(CUR_PATH_NAMES)),$(CUR_PATH_NAMES))

ifeq ($(APP),)

APP = a.out

endif

endif

#----------------------#

ifeq ($(OS),Windows_NT)

# those using other libraries. Once done, without any changes you can

# then build programs using the same or less libraries, even if source

# files are renamed, added or removed. Therefore, it is particularly

##==========================================================================

# The Compiling Mode, Options: Debug, Release

MODE = Debug

# dependencies must be up to date,Options: Yes, No

CHECK_DEPS = Yes

#==================================================================

# The pre-processor options used by the cpp (man cpp for more).

CPPFLAGS =

# convenient to use it to build codes for experimental or study use.

#

# GNU make is expected to use the Makefile. Other versions of makes

# may or may not work.

# The pre-processor and compiler options.

# Users can override those variables from the command line.

CFLAGS = -O2 -Wall

CXXFLAGS = $(CFLAGS)

# Debug flag Options: -g, -g2, -g3

# If not specified, only the current directory will be serached.

SRC_DIRS =

# The executable file name.

# If not specified, current directory name or `a.out' will be used.

CTAGSFLAGS =

## Stable Section: usually no need to be changed. But you can add more.

##==========================================================================

APP := $(APP).exe

endif

#----------------------#

ifeq ($(MODE),Debug)

CFLAGS += $(DEBUG_FLAG)

endif

#----------------------#

ifeq ($(SRC_DIRS),)

SRC_DIRS = .

# $ make NODEP=yes compile and link without generating dependencies

# $ make objs compile only (no linking)

# $ make tags create tags for Emacs editor

#

# Usage:

# ------

# 1. Copy the Makefile to your program directory.

# 2. Customize in the "Customizable Section" only if necessary:

# * to use non-standard C/C++ libraries, set pre-processor or compiler

#HEADERS = $(foreach d,$(SRC_DIRS),$(wildcard $(addprefix $(d)/*,$(HDREXTS))))

SOURCES = $(wildcard $(SRC_DIRS)/*$(SRCEXTS))

HEADERS = $(wildcard $(SRC_DIRS)/*$(HDREXTS))

SRC_CXX = $(filter-out %.c,$(SOURCES))

OBJS = $(addsuffix .o, $(basename $(SOURCES)))

DEPS = $(OBJS:.o=.d)

## Define some useful variables.

DEP_OPT = $(shell if `$(CC) --version | grep "GCC" >/dev/null`; then \

APP =

## Implicit Section: change the following only when necessary.

##==========================================================================

# The source file types (headers excluded).

DEPEND_d = $(subst $(DEBUG_FLAG),,$(DEPEND))

# $ make help get the usage of the makefile

#

#===========================================================================

## Customizable Section: adapt those variables to suit your program.

#############################################################################

#

# Generic Makefile for C/C++ Program

#

# Author: ChengMing

#

# Description:

# .c indicates C source files, and others C++ ones.

SRCEXTS = .c .C .cc .cpp .CPP .c++ .cxx .cp

# The header file types.

HDREXTS = .h .H .hh .hpp .HPP .h++ .hxx .hp

# The options used in linking as well as in any direct use of ld.

LDFLAGS =

# The lib list to be linked.

LIBS =

# The directories in which source files reside.

# makes dependencies, compiles and links to form an executable.

#

# Besides its default ability to build C/C++ programs which use only

# standard C/C++ libraries, you can customize the Makefile to build

DEBUG_FLAG = -g

# std flag Options: -std=c99,-std=iso9899:199409, -std=c89

STD_FLAG = -std=c99

# The C program compiler.

CC = gcc

# The C++ program compiler.