S3C44B0X 中文数据手册

s3c44b0寄存器

4.2 存储器管理

寄存器定义

---------BANKCONn控制寄存器

S3C44BOX具有8个BANKCONn寄存器,分别对应 着Bank—BANCONn寄存器针对操作时序进行设置,

BANK CONn 位

MT [16: 15]

Tacs

[14:13]

Tcos

[12:11]

Tacc

[10:8]

Toch

存储地址引脚

A0 A1

A0 A1

A1 A2

A2 A3

A2 A3

┇

A2 A3

┇

A3 A4

┇

A4 A5

┇

4.2 存储器管理

S3C44BOX存储系统 ---------存储器的分配 的特点 与存储器接口 BIOS 512KB×2Flash 16MB Flash硬盘 USB接口 LCD显示模块 存储器 Bank4 Bank5 Bank6 Bank7 与存储器接口 保留 保留 系统内存SDRAM 保留

[5:4]

Tpac

[3:2]

PMC

[1:0]

4.2 存储器管理

寄存器定义

---------BANKCONn控制寄存器

S3C44BOX具有8个BANKCONn寄存器,分别对应 着Bank—BANCONn寄存器针对操作时序进行设置,

BANKC ONn 位 Tacs

[14:13]

Tcos

[12:11]

当ENDIAN为L时则使用大端模式,大/小端模式 之所以存在是因为当在存储器中存储不同字长的数据 时,大/小端模式定义了不同长度的数据类型的对齐方 式。

4.2 存储器管理

S3C44BOX存储系统 ---------总线宽度 的特点

S3C44BOX 中文数据手册

S3C44B0X中文数据手册目录S3C44B0X中文数据手册 (1)13 A/D转换器 (2)13.2 S3C44B0X具备的ADC (2)13.2.1ADC转换时间计算 (2)13.2.2 ADC的分辨率的计算 (3)13.2.3 关于采样保持器 (3)13.2.4 ADC的相关寄存器 (3)13.2.4.1 A/D转换控制寄存器(ADCCON) (3)13.2.4.2 A/D转换预分频寄存器 (4)13.2.4.3 A/D转换数据寄存器 (4)13 A/D转换器13.2 S3C44B0X具备的ADCS3C44B0X具有8路模拟信号输入的10位模/数转换器(ADC),它是一个逐次逼近型的ADC,内部结构中包括模拟输入多路复用器,自动调零比较器,时钟产生器,10位逐次逼近寄存器(SAR),输出寄存器如下图所示。

这个ADC还提供可编程选择的睡眠模式,以节省功耗。

图13-2 S3C44B0X内部ADC结构图上图展示了S3C44B0X内部ADC的功能结构图。

清注意,出于对电压的稳定性的考虑,正向参考电压REFT,反向参考电压REFB和模拟共用电压VCOM应该相应地连接一个旁路电容(ARMSys上已经具备)。

它的主要特性是:-分辨率:10位;-微分线性度误差:±1 LSB-积分线性度误差:±2 LSB(最大±3 LSB)-最大转换速率: 100KSPS-输入电压范围:0-2.5V-输入带宽:0-100Hz(不具备采样保持(S/H)电路)-低功耗13.2.1ADC转换时间计算A/D转换时间即完成一次A/D转换所需要的时间。

当系统的时钟频率微64MHz且ADC 时钟源的预分频值为20时,10位数字量的转换时间如下:64MHz / 2*(20+1) / 16(10位操作至少要16个周期)= 95.2 KHz = 10.5 us S3C44B0X的这个ADC不具有采样保持电路,因此虽然它具有较高的采样速度,但为了得到精确的转换数据,输入的模拟信号的频率应该不超过100Hz。

第5章S3C44B0X接口电路设计与编程资料

@ Trp=3.5(D)or4(SD),

@ Trc=5(S), Tchr=3(D), Ref CNT)

.word 0x16

@ Bank size, 32MB/32MB

.word 0x20

@ MRSR 6(CL=2)

.word 0x20

@ MRSR 7(CL=2)

5.1 MICETEC EV44B0开发板简介

5.1 MICETEC EV44B0开发板简介

MBL介绍

第5章 目录

1.MICETEK EV44B0II6 IIC接口电路设计及编

开发板

程

2.存储器电路设计及编 7 其他接口电路设计及

程

编程

3.网络、USB和IIS电路 设计及编程

4.人机接口电路设计及 编程

5.串行接口电路设计及 编程

端口G

rPUPG=0x0;

rSPUCR=0x7;

//上拉禁止。

rEXTINT=0x22222022; // EINT7~EINT0下降沿触发。

5.1 MICETEC EV44B0开发板简介

电源

EV44B0II系统采用DC 3.3V(最少850mA) 供电,3.3V给MCU的I /O接口供电,3.3V经 稳压芯片产生一个2.5V电压给ARM内核供电。

5.1 MICETEC EV44B0开发板简介

存储地址空间分配

--------配置程序如下:

.word 0x00018000 @ GCS6 SDRAM(Trcd=2,SCAN=8)

.word 0x00018000 @ GCS7 SDRAM(Trcd=2,SCAN=8)

.word 0x00820591 @ Refresh(REFEN=1,TREFMD=0,

2020年三星S3C44B0X简介

嵌入式系统设计

S3C44B0X的引脚信号描述 - DRAM/SDRAM/SRAM

信号 nRAS[1:0] nCAS[3:0] nSRAS nSCAS nSCS[1:0] DQM[3:0] SCLK SCKE

类型

描述

O 行地址锁存信号

O 列地址锁存信号

O SDRAM行地址锁存信号

O SDRAM列地址锁存信号

O LCD行信号

O LCD时钟信号

2020/12/12

8

嵌入式系统设计

S3C44B0X的引脚信号描述 - TIMER/PWM控制信号

信号 TOUT[4:0] TCLK

类型 O 定时器输出 I 外部时钟输入

描述

2020/12/12

9

嵌入式系统设计

S3C44B0X的引脚信号描述 -中断控制信号

信号

类型

S3C44B0X的引脚信号描述 - ADC

信号 AIN[7:0] AREFT AREFB AVCOM

类型 AI ADC输入[7:0] AI ADC-Top-Vref AI ADC-Bottom-Vref AI ADC-Common-Vref

描述

2020/12/12

16

嵌入式系统设计

S3C44B0X的引脚信号描述 - GPIO

2020/12/12

3

嵌入式系统设计

S3C44B0X特性 供电:内核:2.5V,I/O : 3.0 V 到 3.6 V 频率:最高为66MHz 封装:160 LQFP / 160 FBGA

2020/12/12

4

嵌入式系统设计

S3C44B0X的引脚分布图

2020/12/12

5

嵌入式系统设计

杭州立泰电子 S3C44B0X 中文数据手册

S3C44B0X中文数据手册S3C44B0X中文数据手册 (1)6 处理器Wrapper和总线优先级 (2)6.1Cache的组织 (2)6.2Cache替换操作 (2)6.3 cache 禁止操作 (2)6.4 cache 刷新 (3)6.5非cache区域 (3)6.6通过使用cache来提高程序的执行速度 (3)6.7内部SRAM (3)6.8写缓冲区操作 (4)6.9总线优先级地图 (5)6.10特殊寄存器 (5)6 处理器Wrapper和总线优先级处理器wrapper包括一个cache,写入缓冲器,和CPU内核。

总线仲裁逻辑决定每个总线占用者的优先权。

处理器wrapper有一个8k直接的内部存储器。

内部存储器可以以3种方式采用。

第一是8k字节的存储空间作为8k字节的统一(指令或数据)cache(高速缓冲存储器)。

第二,内部存储器可以用作一个4k字节的统一cache和一个4k字节的内部SRAM。

第三,内部存储器可以整个地用作8k字节的内部SRAM。

内部统一(指令或数据)cache采用4种方式与某个4个字(16个字节)的行建立链接结构。

它采用一种写穿式(write-through)的原则保持数据的一致性。

当在cache中找不到相应的内容(称为cache miss),4个字的存储内容从外部存储器连续地取得。

它采用一种LRU(最近使用最少)算法来提升命中的比率。

统一cache通过有区别的方式来处理指令和数据。

内部SRAM主要用来减少ISR的执行时间。

由于内部SRAM具有最短的操作时间,因此能够减少ISR的执行时间。

当然ISR在SRAM运行也是非常有效率的因为大多数的ISR 代码都会引起cache miss。

总线仲裁逻辑可以决定总线占用者的优先级。

总线仲裁逻辑支持一种round-robin优先级模式和一种固定的优先级模式。

同样LCD_DMA, BDMA, ZDMA, nBREQ(外部总线控制器)之间的优先级可以通过软件来修改。

S3C44B0X时钟电源管理器功能及应用开发汇编

for(m=0;m<256;m++){

tmpMclk=clkXtal*(m+8)/((p+2)*pow2[s]);

if(tmpMclk= =Mclk) return;

}

}

2006-1}1

38

}

进入STOP模式

;关闭外设和LCD ;设置唤醒中断 ;r0=CLKCON=0x01

mov r2,r0 ldr r0,=REFRESH

直到向CLKCON写入有效的值

2006-11

22

停止模式(续1)

2006-11

23

停止模式(续2)

DRAM必须处在自刷新状态(Self-Refresh),以保持数据 LCD要停止显示,否则系统会挂起 所有的端口要配置好,以减少功耗(如:PCONG) 在进入停止模式时必须经过PLL打开的低速模式 在进入停止模式的最后三个时钟周期不响应唤醒请求 在进入停止模式时,MCLK的频率必须比Fin的2.5倍高 在使用电平触发的EINT模式时,进入停止模式时,不能

5

时钟发生器框图

2006-11

6

相关管脚

信号

类型

描述

OM[3:2] 输入

决定时钟产生方式

EXTCLK 输入

外时钟源,不用时接高

XTAL0 模拟输入 晶体输入,不用时接高

EXTAL0 模拟输出 晶体输出,不用时浮空

PLLCAP 模拟输入 接PLL的滤波电容

CLKout 输出

时钟输出

2006-11

7

Fout的频率 Fin/ (2xSLOW_VAL) Fin

SLOW_VAL的值 SLOW_VAL>0 SLOW_VAL=0

S3C44B0 学习板使用指南

一、S3C44B0 学习板简介 (3)二、系统上电 (5)三、测试程序 (8)四、建立 Windows 系统上虚拟 Linux 环境 Cygwin 以及 ARM 交叉编译环境 (9)五、Bootloader 装载程序(U-BOOT) (11)六、uClinux 编译与下载 (21)七、开发板的地址空间分配 (35)八、FAQ 常见问题 (36)S3C44B0 学习板使用指南三星公司推出的 16/32 位 RISC 处理器 S3C44B0X 为手持设备和一般类型的提供了一种高性能低成本的解决方案。

为了降低整个系统的成本,S3C44B0X 内部集成了丰富的片内外设,包括:8K 的 cache,可选的片内 SRAM,LCD 控制器,带有握手信号的双同道 UART,4 同道 DMA,系统管理器(片选逻辑,FP/EDO/SDRAM 控制器),带有PWM 功能的 5 通道定时器,I/O 端口,RTC 实时时钟,8 通道 10 位 ADC,IIC、IIS 总线接口,同步 SIO 接口以及用于时钟管理的PLL 锁相环。

S3C44B0X 采用了 ARM7TDMI 内核,0.25um 标准宏单元和存储编译器。

TDMI 的每一个字母代表一种功能: T(Thumb),支持 16 为压缩指令集 Thumb D(Debug),支持片上 Debug M(Multiplier),内嵌硬件乘法器 I(ICE):嵌入式 ICE,支持片上断点和调试点S3C44B0X 极低的功耗以及简单,只能的全静态设计使其非常适合对成本和功耗敏感的项目。

同时S3C44B0X 还采用了一种新的总线结构,即 SAMBAII(三星 ARM CPU 嵌入式微处理器总线结构)S3C44B0X 通过集成全面、通用的片内外设,大大减少了系统电路中除处理器外的器件需求,从而最小化系统成本。

下列是其集成的边内外设: 外部存储器控制器(FP/EDO/SDRAM 控制器,片选逻辑)控制器(最大支持 256 色 STN,LCD 具有一个专用的 DMA 通道) LCD 2个通用 DMA 通道,2 个外设 DMA 通道并有片外请求管脚个 UART,带有握手协议(支持 irDA1.0,具有 16 字节 FIFO)1 通道 SIO 2多主总线接口 IIC IIS总线控制器个 PWM 定制器和 1 通道内部定时器 5 看门狗定时器个通用 I/O 口,作多支持 8 各片外中断源 71 功耗管理:普通,慢速,空闲和停止模式 8 通道 10 位 ADC 具有日立功能的 RTC 带 PLL 的片内时钟发生器使用 S3C44B0X 来构建系统,能够降低真个系统的成本,我们列举以下一些可以采用 S3C44B0X 构建系统应用: GPS 电话 PDA(个人数字助理) 掌上游戏机 指纹识别系统 终端汽车导航系统 mp3 等手持应用一、 S3C44B0 学习板简介S3C44B0 开发板是依据三星公司评估板的基础上开发而来, 其主要硬件包括: Samsung S3C44B0X 66MHz (ARM7 内核) 8M Flash 2M SDRAM 10M Base-T 以太网接口 IDE 接口 USB1.1 设备接口 IIC 总线接口 RTC 实时时钟 LCD 接口,支持 640×480 以下单色或 320×240 以下 STN/DSTN 256 色 2 个 RS232 UART 串行口,支持 Modem 握手信号 标准 14 针 JTAG 接口 1×4 键盘,1×3 LED 灯 可扩展总线接口同时,本开发板提供完善的开发包和各种硬件测试程序(含源码),以帮助客户快速掌握 S3C44B0 的各种片内外设以及扩展接口的使用方法: ADS1.2 IDE, ARM 程序开发集成环境 GNU 工具包(包括交叉编译器、链接、汇编工具) uClinux 源码包 U-Boot1.1.1(BOIS)启动控制程序(含源码) 应用程序代码 相关技术文档,手册 键盘控制 LED 试验 实时时钟演示 IIC 测试程序 PWM 测试程序 uCOS-II 实时操作系统加载试验下图是 S3C44B0 的开发板图,我们在这里可以看到使用的板子的各种外围芯片,外设以及各种接口。

ARM开发板S3C44B0使用指南

S3C44B0 学习板使用指南重庆勤智科技有限公司三星公司推出的 16/32 位 RISC 处理器 S3C44B0X 为手持设备和一般类型的提供了一种高性能低成本的解决方案。

为了降低整个系统的成本,S3C44B0X 内部集成了丰富的片内外设,包括:8K 的 cache,可选的片内 SRAM,LCD 控制器,带有握手信号的双同道 UART,4 同道 DMA,系统管理器(片选逻辑,FP/EDO/SDRAM 控制器),带有PWM 功能的 5 通道定时器,I/O 端口,RTC 实时时钟,8 通道 10 位 ADC,IIC、IIS 总线接口,同步 SIO 接口以及用于时钟管理的PLL 锁相环。

S3C44B0X 采用了 ARM7TDMI 内核,0.25um 标准宏单元和存储编译器。

TDMI 的每一个字母代表一种功能: T(Thumb),支持 16 为压缩指令集 Thumb D(Debug),支持片上 Debug M(Multiplier),内嵌硬件乘法器 I(ICE):嵌入式 ICE,支持片上断点和调试点S3C44B0X 极低的功耗以及简单,只能的全静态设计使其非常适合对成本和功耗敏感的项目。

同时S3C44B0X 还采用了一种新的总线结构,即 SAMBAII(三星 ARM CPU 嵌入式微处理器总线结构)S3C44B0X 通过集成全面、通用的片内外设,大大减少了系统电路中除处理器外的器件需求,从而最小化系统成本。

下列是其集成的边内外设: 外部存储器控制器(FP/EDO/SDRAM 控制器,片选逻辑)控制器(最大支持 256 色 STN,LCD 具有一个专用的 DMA 通道) LCD个通用 DMA 通道,2 个外设 DMA 通道并有片外请求管脚 2个 UART,带有握手协议(支持 irDA1.0,具有 16 字节 FIFO)1 通道 SIO 2多主总线接口 IIC总线控制器 IIS个 PWM 定制器和 1 通道内部定时器 5 看门狗定时器个通用 I/O 口,作多支持 8 各片外中断源 71 功耗管理:普通,慢速,空闲和停止模式 8 通道 10 位 ADC 具有日立功能的 RTC 带 PLL 的片内时钟发生器使用 S3C44B0X 来构建系统,能够降低真个系统的成本,我们列举以下一些可以采用 S3C44B0X 构建系统应用: GPS 电话 PDA(个人数字助理) 掌上游戏机 指纹识别系统 终端汽车导航系统 mp3 等手持应用一、 S3C44B0 学习板简介S3C44B0 开发板是依据三星公司评估板的基础上开发而来, 其主要硬件包括:内核)(ARM7 Samsung66MHzS3C44B0XFlash 8M 2M SDRAMBase-T以太网接口 10M IDE 接口设备接口 USB1.1 IIC 总线接口实时时钟 RTC LCD 接口,支持 640×480 以下单色或 320×240 以下 STN/DSTN 256 色 2 个 RS232 UART 串行口,支持 Modem 握手信号 标准 14 针 JTAG 接口键盘,1×3 LED 灯 1×4 可扩展总线接口同时,本开发板提供完善的开发包和各种硬件测试程序(含源码),以帮助客户快速掌握 S3C44B0 的各种片内外设以及扩展接口的使用方法: ADS1.2 IDE, ARM 程序开发集成环境 GNU 工具包(包括交叉编译器、链接、汇编工具) uClinux 源码包 U-Boot1.1.1(BOIS)启动控制程序(含源码) 应用程序代码 相关技术文档,手册 键盘控制 LED 试验 实时时钟演示 IIC 测试程序 PWM 测试程序 uCOS-II 实时操作系统加载试验下图是 S3C44B0 的开发板图,我们在这里可以看到使用的板子的各种外围芯片,外设以及各种接口。

S3C44B0X存储控制器功能及应用概要

S3C44B0X存储控制器功能描述(续)

Bank0数据宽度选择

OM0(操作方式1) OM1(操作方式0)

ROM数据宽度

8位 16位

0 0

0 1

1

1

0

1

32位

测试模式

S3C44B0X存储控制器功能描述(续)

3.存储器(SROM/DRAM/SDRAM)地址线连接

数据宽度不同,连接方式也不同

(1)只要将CPU上的相应Bank连线接到外设芯片的片选引脚上,便可以根据相应的地址进 行存储器或外设操作了。 (2)使用Bank0上的两片512KB×2存储器来放置系统BIOS,系统上电以后,PC指针自动 指向Bank0的第一个单元,开始进行系统自举。

理上是连续的。

(四) S3C44B0X存储控制器的特殊功能寄存器

1.总线宽度/等待控制寄存器(BWSCON) BWSCON寄存器主要用来设置外接存储器的总线宽度和等 待状态。 在BWXCON中,除了Bank0,对其他7个Bank都各对应有4 个相关位的设置,分别为STx,WSx,DWx。 STx位决定SRAM映射在Bankx时是否采用UB/LB。 ① 0:不采用,1:采用。 ② WSx位决定Bank上等待的状态。0:禁止等待,1:使能等 待。 ③ DWx中的确位决定Bankx上的总线宽度。00:8位,01:16 位,10:32位。 ④ DW0位对应Bank0的总线宽度,但这里它是只读的,其中 00=8位,01=16位,10=32位。设置是通过OM[0:1]脚电 平决定总线宽度。

(3)系统自举完成以后,便从硬盘中将系统文件和用户应用程序复制到 SDRAM内存中执行。 (4)Bank1上接16MB非线性Flash,当作系统硬盘使用,可以构造文件系统,存放海量数 据。 (5)用SDRAM当作系统内存,只有Bank6/Bank7能支持SDRAM,所以将SDRAM接在 Bank6 (6)如果同时使用Bank6/Bank7,则要求连接相同容量的存储器,而且其地地址空间在物

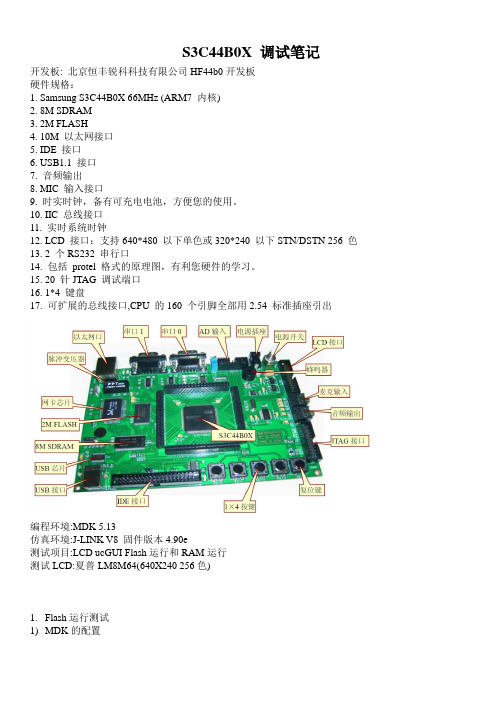

S3C44B0X 调试笔记

S3C44B0X 调试笔记开发板:北京恒丰锐科科技有限公司HF44b0开发板硬件规格:1. Samsung S3C44B0X 66MHz (ARM7 内核)2. 8M SDRAM3. 2M FLASH4. 10M 以太网接口5. IDE 接口6. USB1.1 接口7. 音频输出8. MIC 输入接口9. 时实时钟,备有可充电电池,方便您的使用。

10. IIC 总线接口11. 实时系统时钟12. LCD 接口:支持640*480 以下单色或320*240 以下STN/DSTN 256 色13. 2 个RS232 串行口14. 包括protel 格式的原理图,有利您硬件的学习。

15. 20 针JTAG 调试端口16. 1*4 键盘17. 可扩展的总线接口,CPU 的160 个引脚全部用2.54 标准插座引出编程环境:MDK 5.13仿真环境:J-LINK V8 固件版本4.90e测试项目:LCD ucGUI Flash运行和RAM运行测试LCD:夏普LM8M64(640X240 256色)1.Flash运行测试1)MDK的配置/******************************************************************************/ /* FLASH.INI: Flash Initialization File *//******************************************************************************/ /* This file is part of the uVision/ARM development tools. *//* Copyright (c) 2005-2006 Keil Software. All rights reserved. *//* This software may only be used under the terms of a valid, current, *//* end user licence from KEIL for a compatible version of KEIL software *//* development tools. Nothing else gives you the right to use this software. *//******************************************************************************/_WDWORD(0x01D30000, 0x00000000); // WTCON: Disable Watchdog_WDWORD(0x01C00000, 0x00000001); // SYSCFG: Disable Cache这里选择Flash的型号是AM29F160DB,实际型号是AM29LV160DB,但实际也好用.2.Flash运行测试1)MDK的配置//*** <<< Use Configuration !disalbe! Wizard in Context Menu >>> ***FUNC void Setup (void){_WWORD (0x1c00000, 0x00000008); //System Configuration SYSCFG_WWORD (0x01C80000, 0x11119102); //Bus Width & Wait Status Control BWSCON_WWORD (0x01C80004, 0x00000600);_WWORD (0x01C80008, 0x00007FFC);_WWORD (0x01C8000C, 0x00007FFC);_WWORD (0x01C80010, 0x00007FFC);_WWORD (0x01C80014, 0x00007FFC);_WWORD (0x01C80018, 0x00007FFC);_WWORD (0x01C8001C, 0x00018000);_WWORD (0x01C80020, 0x00018000);_WWORD (0x01C80024, 0x00860459);_WWORD (0x01C80028, 0x00000010);_WWORD (0x01C8002C, 0x00000020);_WWORD (0x01C80030, 0x00000020);// <o> Program Entry Pointpc = 0x0C001000;}//map 0x01c00000, 0x02000000 read writeLOAD ./RAM/Hello.axf INCREMENTALSetup(); // Setup for Running帮用户解决空间不够时候看的一个资料,【转】过来整理一下供大家参考:RealView MDK具有强大的编译、链接功能。

s3c44b0x定时器

POET

定时器n计数缓冲区寄存器TCNTBn 和比较缓冲区寄存器TCMPBn

• TCMPBn是16位定时器Timer0~Timer4比较缓冲 器寄存器; • TCNTBn是16位定时器Timer0~Timer5计数缓冲 寄存器; • TCNTOn是16位定时器Timer0~Timer5观察寄 存器. • 在以上的寄存器中,定时器n计数/比较缓冲寄存 器可读写寄存器,定时器n计数观察寄存器为只 读寄存器。

死区发生器

• 死区发生器用于对大功率设备进行PWM控 制。 • 该特性用于在开关设备的断开和另一个开 关设备的闭合之间插入一个时间缺口。这 个时间缺口阻止两个开关设备处于同时闭 合的状态,即使是非常短的时间。

POET

?

• TOUT0是一个PWM输出。NTOUT0是TOUT0 的一个反转输出。 • 如果死区能被使能, TOUT0和nTOUT0的输 出波形将会是TOUT0_DZ和nTOUT0_DZ。在 死区间隔中, TOUT0_DZ和nTOUT0_DZ肯定 不会同时闭合的。 POET

POET

PWM定时器概述

• PWM定时器具有6个16位定时器,每个定 时器可以按照中断模式或DMA模式工作。 • 定时器0,1,2,3和4具有PWM输出功能。 定时器5是一个内部定时器不具有对外输出 口线。定时器0具有死区发生器,通常用于 大电流设备应用

POET

PWM定时器特性

• 6个16 位定时器可以工作在中断模式或 DMA模式; • 3个8 位预分频器和2个5位分割器和1个4 位分割器; • 输出波形的占空比可编程控制(PWM) • 自动加载模式或单触发脉冲模式; • 死区产生器;

POET

PWM定时器的输入

• 每个定时器从时钟分割器的输出得到它们自己的 时钟源,时钟分割器则从对应的8位预分频器得到 时钟源。 • 8位预分频器是可编程的,它的频率通过MCLK除 以保存在TCFG0和 TCFG1寄存器中除数的结果 设定。 • 8位预分频器和一个独立的4位分割器组合起来可 以产生不同的频率定时器时钟源输出。

第4章 S3C44B0X介绍

4.3 S3C44B0X I/O端口功能及应用开发

4.3.1 S3C444B0X I/O功能概述 4.3.2 S3C444B0X 端口功能配置 4.3.3 S3C444B0X I/O端口特殊功能控制描述 4.3.5 S3C444B0X I/O端口应用编程

4.3.1 S3C44B0X I/O端口功能概述

总线宽度/等待控制寄存器(BWSCON)(1个) 用来决定存储器总线宽度、等待允许、高 低字节使能。见P.229

S3C44B0X存储控制器的特殊功能寄存器

Bank控制寄存器 ( BANKCONn )(8个) 用来确定存储器读写时序。 P.229 ⑴ (BANKCONn: nGCS0-nGCS5)

所有存储器空间的访问周期都可以通过编

程配置; 提供外部扩展总线的等待周期; 在低功耗的情况下支持DRAM/SDARM自 动刷新; 支持地址对称或非地址对称的DRAM。

三、Cache和片内SRAM

4路组相联统一的8KB指令/数据Cache; 未作为Cache使用的4/8 Kbytes Cache存

S3C44B0X存储控制器的特殊功能寄存器

Bank大小寄存器(BANKSIZE)(1个) 用来设置Bank6/Bank7的存储区大小。见P.231 表4-41

S3C44B0X存储控制器的特殊功能寄存器

Bank6—Bank7模式设置寄存器(MRSR) (2个) 用来决定Bank6、Bank7的存储模式。

二、系统(存储)管理

支持大、小端模式(通过外部引脚来选择); 地址空间:包含8个存储体,每个存储体的大小

为32M字节,总共有256M字节的地址空间; 对所有存储体的访问大小均可进行改变(8位/16 位/32位); 8个存储体中,Bank0~Bank5可以用于ROM、 SRAM等存储器,Bank6、Bank7可用于ROM、 SRAM、FP/EDO(Extended Data Out DRAM) /SDRAM等存储器; 7个存储体起始地址固定,1个存储体的起始地址 可变。

S3C44B0X内存控制器

内存控制器S3C44B0X 处理器的内存控制器可以为片外内存存取提供必要的控制信号,它主要包括以下特点:支持数据存储器的大/少端选择(通过外部引脚来选择)。

地址空间:包含8 个地址空间,每个地址空间的大小为32M 字节,总共有256M 字节的地址空间。

所有地址空间都可以通过程序设定为8 位、16 位或32 位存取方式。

8个地址空间中,Bank0~Bank5可支持ROM、SRAM 等内存,2 个用于ROM、SRAM和FP/EDO/SDRAM 等内存。

7 个地址空间的起始地址及空间大小是固定的。

1 个地址空间的起始地址和空间大小是可变的。

所有内存空间的存取周期都可以通过程序设定。

提供外部扩充总线的等待周期。

支持DRAM/SDARM 自动刷新。

支持地址对称或非地址对称的DRAM。

图5-1 S3C44B0X 复位后的内存地址分配图3-1 为S3C44B0X 复位后的内存地址分配图。

从图中可以看出,特殊功能寄存器位于0X01C00000 到0X02000000 的4M 空间内。

Bank0-Bank5 的起始地址和空间大小都是固定的,Bank6的起始地址是固定的,但是空间大小和Bank7一样是可变的,可以设定为2/4/8/16/32M。

Bank6 和Bank7 的详细的地址和空间。

大小的关系可以参考表5-1表5-1地址2M 4M 8M 16M 32MBank6开始地址0xc00_0000 0xc00_0000 0xc00_0000 0xc00_0000 0xc00_0000结束地址0xc1f_ffff 0xc3f_ffff 0xc7f_ffff 0xcff_ffff 0xdff_ffffBank7开始地址0xc20_0000 0xc40_0000 0xc80_0000 0xd00_0000 0xe00_0000结束地址0xc3f_ffff 0xc7f_ffff 0xcff_ffff 0xdff_ffff 0xfff_ffff大/小ENDIAN 模式选择处理器复位时(nRESET 为低),通过ENDIAN 引脚选择所使用的ENDIAN模式。

s3c44b0 中文技术手册

RTC, 1 ADC, 1 IIC, 1 SIO )

Vectored IRQ interrupt mode to reduce interrupt Programmable polarity of edge and level Supports FIQ (Fast Interrupt request) for very urgent interrupt request

S3C44B0X采用一种新的三星ARM CPU嵌入总线结构-SAMBA2,最大达66MHZ。 电源管理支持:Normal, Slow, Idle, and Stop mode。

系统管理功能: 1 Little/Big endian support. 2 Address space: 32Mbytes per each bank. (Total 256Mbyte)

操作电压范围:

核电压 : 2.5V

I/O电压 : 3.0 V to 3.6 V

工作频率:

Up to 66 MHz

封装:

160 LQFP / 160 FBGA

2

管脚描述

00:8-bit 01:16-bit 10:32-bit 11:Test mode

om[1:0]: 输入 om[1:0]设置S3C44B0X在测试模式和确定nGCS0的总线宽度,逻辑电平在复位期 间由这些管脚的上拉下拉电阻确定. ADDR[24:0] 输出: 地址总线 输出相应段的存储器地址. DATA[31:0] 输入输出:数据总线,总线宽度可编程为8/16/32 位 nGCS[7:0] 输出:芯片选择,当存储器地址在相应段的地址区域时被激活.存取周期和段尺寸可编 程. nWE 输出 :写允许信号,指示当前的总线周期为写周期. nWBE[3:0] 输出: 写字节允许信号 nBE[3:0] 输出:在使用SRAM情况下字节允许信号. nOE输出 :读允许信号,指示当前的总线周期为读周期.

三星的S3C44B0X中文数据手册

1产品预览介绍三星的S3C44B0X 16/32位RISC处理器被设计来为手持设备等提供一个低本钱高性能的方案。

S3C44B0X提供以下配置:2.5V ARM7TDMI 内核带有8Kcache ;可选的internal SRAM;LCD Controller(最大支持256色STN,使用LCD专用DMA);2-ch UART with handshake(IrDA1.0, 16-byte FIFO) / 1-ch SIO;2-ch general DMAs / 2-ch peripheral DMAs with external request pins;External memory controller (chip select logic, FP/ EDO/SDRAM controller);5-ch PWM timers & 1-ch internal timer;Watch Dog Timer;71 general purpose I/O ports / 8-ch external interrupt source;RTC with calendar function;8-ch 10-bit ADC;1-ch multi-master IIC-BUS controller;1-ch IIS-BUS controller;Sync. SIO interface and On-chip clock generator with PLL.。

S3C44B0X采用一种新的三星ARM CPU嵌入总线结构-SAMBA2,最大达66MHZ。

电源管理支持:Normal, Slow, Idle, and Stop mode。

系统管理功能:1 Little/Big endian support.2 Address space: 32Mbytes per each bank. (Total 256Mbyte)3 Supports programmable 8/16/32-bit data bus width for each bank.4 Fixed bank start address and programmable bank size for 7 banks.5 . 8 memory banks.- 6 memory banks for ROM, SRAM etc.- 2 memory banks for ROM/SRAM/DRAM(Fast Page, EDO, and Synchronous DRAM)6. Fully Programmable access cycles for all memory banks.7 Supports external wait signal to expend the bus cycle.8. Supports self-refresh mode in DRAM/SDRAM for power-down.9. Supports asymmetric/symmetric address of DRAM.Cache 和内部存储器功能:• 4-way set associative ID(Unified)-cache with 8Kbyte.• The 0/4/8 Kbytes internal SRAM using unused cache memory.• Pseudo LRU(Least Recently Used) Replace Algorithm.• Write through policy to maintain the coherence between main memory and cache content.• Write buffer with four depth.• Request data first fill technique when cache miss occurs.时钟和电源管理• Low power• The on-chip PLL makes the clock for operating MCU at maximum 66MHz.• Clock can be fed selectively to each function block by software.• Power mode: Normal, Slow, Idle and Stop mode.Normal mode: Normal operating mode.Slow mode: Low frequency clock without PLLIdle mode: Stop the clock for only CPUStop mode: All clocks are stopped• Wake up by EINT[7:0] or RTC alarm interrupt fromidle mode.中断控制器• 30 Interrupt sources( Watch-dog timer, 6 Timer, 6 UART, 8 External interrupts, 4 DMA , 2 RTC, 1 ADC, 1 IIC, 1 SIO )• Vectored IRQ interrupt mode to reduce interrupt latency.• Level/edge mode on the external interrupt sources• Programmable polarity of edge and level• Supports FIQ (Fast Interrupt request) for very urgent interrupt request定时器功能• 5-ch 16-bit Timer with PWM / 1-ch 16-bit internal timer with DMA-based or interrupt-based operation• Programmable duty cycle, frequency, and polarity• Dead-zone generation.• Supports external clock source.RTC 功能:• Full clock feature: msec, sec, min, hour, day,week, month, year.• 32.768 KHz operation.• Alarm interrupt for CPU wake-up.• Time tick interrupt通用输入输出口功能:• 8 external interrupt ports• 71 multiplexed input/output portsUART 功能:• 2-channel UART with DMA-based or interrupt-based operation• Supports 5-bit, 6-bit, 7-bit, or 8-bit serial data transmit/receive• Supports H/W handshaking during transmit/receive• Programmable baud rate• Supports IrDA 1.0 (115.2kbps)• Loop back mode for testing• Each channel have two internal 32-byte FIFO for Rx and Tx.DMA控制器功能:• 2 channel general purpose Direct Memory Access controller without CPU intervention.• 2 channel Bridge DMA (peripheral DMA) controller.• Support IO to memory, memory to IO, IO to IO with the Bridge DMA which has 6 type's DMA requestor: Software, 4 internal function blocks (UART, SIO, Timer, IIS), andExternal pins.• Programmable priority order between DMAs (fixed or round-robin mode)• Burst transfer mode to enhance the transfer rate on the FPDRAM, EDODRAM and SDRAM.• Supports fly-by mode on the memory to external device and external device to memory t ransfer modeA/D 转换器:• 8-ch multiplexed ADC.• Max. 100KSPS/10-bit.LCD控制器:• Supports color/monochrome/gray LCD panel• Supports single scan and dual scan displays• Supports virtual screen function• System memory is used as display memory• Dedicated DMA for fetching image data from system memory• Programmable screen size• Gray level: 16 gray levels• 256 Color levels看门狗定时器:• 16-bit Watchdog Timer• Interrupt request or system reset at time-outIIC-BUS 接口• 1-ch Multi-Master IIC-Bus with interrupt-based operation.• Serial, 8-bit oriented, bi-directional data transfers can be made at up to 100 Kbit/s in the standard mode or up to 400 Kbit/s in the fast mode.IIS-BUS接口• 1-ch IIS-bus for audio interface with DMA-based operation.• Serial, 8/16bit per channel data transfers• Supports MSB-justified data formatSIO (同步串口):• 1-ch SIO with DMA-based or interrupt –based operation.• Programmable baud rates.• Supports serial data transmit/receive operations 8-bit in SIO.操作电压范围:• 核电压: 2.5V I/O电压: 3.0 V to 3.6 V工作频率:• Up to 66 MHz封装:• 160 LQFP / 160 FBGA2管脚描述om[1:0]: 输入om[1:0]设置S3C44B0X在测试模式和确定nGCS0的总线宽度,逻辑电平在复位期间由这些管脚的上拉下拉电阻确定.00:8-bit 01:16-bit 10:32-bit 11:Test modeADDR[24:0] 输出: 地址总线输出相应段的存储器地址.DATA[31:0] 输入输出:数据总线,总线宽度可编程为8/16/32 位nGCS[7:0] 输出:芯片选择,当存储器地址在相应段的地址区域时被激活.存取周期和段尺寸可编程.nWE 输出:写允许信号,指示当前的总线周期为写周期.nWBE[3:0] 输出: 写字节允许信号nBE[3:0] 输出:在使用SRAM情况下字节允许信号.nOE输出:读允许信号,指示当前的总线周期为读周期.nXBREQ 输入: nXBREQ 总线控制请求信号,允许另一个总线控制器请求控制本地总线,nXBACK信号激活指示已经得到总线控制权。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

S3C44B0X中文数据手册S3C44B0X中文数据手册 (1)10 UART (2)特性: (2)10.1 UART操作 (2)10.1.1数据发送 (2)10.1.2数据接收 (2)10.1.3自动流控制(AFC) (3)10.1.4非自动流控制(通过软件控制nRTS和nCTS) (3)10.1.5 调制解调器接口 (4)10.2中断/DMA请求产生器 (4)10.3 UART错误状态FIFO (4)10.4波特率发生器 (5)10.5回送模式 (5)10.6红外通信模式 (5)10.7 UART寄存器 (7)10.7.1 UART线控制寄存器 (7)10.7.2 UART控制寄存器 (8)10.7.3 FIFO控制寄存器 (8)10.7.4 UART的Modem控制寄存器 (9)10.7.5 UART发送/接收状态寄存器 (9)10.7.6 UART错误状态寄存器 (9)10.7.7 UART的FIFO状态寄存器 (10)10.7.8 UART的Modem状态寄存器 (10)10.7.9 UART发送/接收保持(缓冲区)寄存器 (10)10.7.10 UART波特率除数寄存器 (10)10 UARTS3C44B0X的UART(通用异步收发器)单元提供两个独立的异步串行I/O端口,每个都可以在中断和DMA两种模式下工作。

它们支持的最高波特率为115.2Kbps。

每个UART 通道包含2个16位FIFO分别提供给接收和发送。

S3C44B0X的UART可以进行以下参数的设置:可编程的波特率,红外收/发模式,1或2个停止位,5位、6位、7位或8位数据宽度和奇偶位校验。

每个UART包含一个波特率产生器,发送器,接收器和控制单元。

波特率发生器以MCLK 作为时钟源。

发送器和接收器包含16字节的FIFOs和移位寄存器。

要被发送的数据,首先被写入FIFO然后拷贝到发送移位寄存器。

然后它从数据输出端口(TxDn)依次被移位输出。

被接收的数据也同样从数据接收端口(RxDn)移位输入到移位寄存器,然后拷贝到FIFO 中。

特性:-RxD0,TxD0,RxD1,TxD1可以以中断模式或DMA模式工作;-UART通道0符合IrDA 1.0要求,且具有16字节的FIFO;-UART通道1符合IrDA 1.0要求,且具有16字节的FIFO;-支持收发时握手模式。

10.1 UART操作以下将介绍UART的操作,包括数据发送,数据接收,中断发生,波特率发生,回送模式,自动流控制等内容。

10.1.1数据发送数据发送帧格式是可编程的。

它包含一个开始位,5到8个数据位,一个可选的奇偶位和1到2个停止位,这些都可以通过线控制寄存器(UCONn)来设置。

发送器也能够产生发送中止条件。

中止条件迫使串口输出保持在逻辑0状态,这种状态保持超过一个传输帧的时间长度。

通常在一帧传输数据完整地传输完之后,再通过这个全0状态将中止信号发送给对方。

中止信号发送之后,传送数据将持续地放入到输出FIFO中(在不使用FIFO模式下,将被放到输出保持寄存器)。

10.1.2数据接收与发送一样,接收的数据帧格式同样是可编程的。

它包括了一个起始位,5到8个数据位,一个可选的奇偶校验位和1到2个停止位,这些都可以通过线控制寄存器(UCONn)来设置。

接收器还可以检测到溢出错误,奇偶校验错误,帧错误和中止状况,每种情况下都会将一个错误标志置位。

溢出错误表示新的数据已经覆盖了旧的数据,因为旧的数据没有及时被读入;奇偶校验错误表示接收器检测到了意料之外的奇偶校验结果;帧错误表示接收到的数据没有有效的停止位;中止状况表示RxDn的输入被保持为0状态超过了一个帧传输的时间。

在FIFO模式下接收FIFO不为空,但接收器已经在3个字时间内那没有接收到任何数据,就认为发生了接收超时状况。

10.1.3自动流控制(AFC)S3C44B0X的UART通过nRTS和nCTS信号支持自动流控制,在这种情况下必须是UART与UART连接。

如果用户将UART连接到调制解调器,就应该在UMCONn寄存器中禁止自动流控制位,并通过软件控制nRTS。

在AFC中,nRTS由接收器的接收情况来控制,nCTS则控制了发送器的工作。

UART发送器在nCTS信号被置1的时候发送FIFO中的数据(在AFC中,nCTS意味着对方UART的FIFO已经准备好接收数据)。

在UART接收数据时,如果它的接收FIFO中还有多于2个字节的空余空间就必须将nRTS置1,从而告诉对方“接收准备好”;当接收FIFO的剩余空间少于1字节时,必须将nRTS清0,说明“不能再接收”。

AFC接口如下图所示:图8-1 UART AFC接口10.1.4非自动流控制(通过软件控制nRTS和nCTS)○接收操作1.选择接收模式(中断和BDMA模式)2.检查UFSTATn寄存器中接收FIFO计数器的值。

如果值小于15,用户必须设置UMCONn[0]的值为‘1’(即激活nRTS),并且如果它等于或大于15,用户必须设置该位值为‘0’(即失活nRTS)。

3.重复第2步。

○发送操作1.选择发送模式(中断或BDMA模式)2.检查UMSTATn[0]的值,如果为‘1’(nCTS被激活),用户就可以写数据到输出缓冲区或输出FIFO寄存器。

10.1.5 调制解调器接口如果用户要连接到调制解调器接口,就需要nRTS,nCTS,nDSR,nDTR,DCD和nRI 信号。

在这种情况下,用户可以通过通用其它I/O口来由软件控制这些信号,因为AFC是不支持RS-232C接口的。

10.2中断/DMA请求产生器S3C44B0X的每个UART都有7个状态信号:溢出错误,奇偶校验错误,帧错误,中止,接收FIFO/缓冲区数据准备好,发送FIFO/缓冲区空,发送移位寄存器空,所有这些状态都由对应的UART状态寄存器(UTRSTATn/UERSTATn)中的相应位来表现。

溢出错误,奇偶校验错误,帧错误和中止状况都被认为是接收错误状态,如果UCONn 中的“接收错误状态中断使能位”被置位,它们中的每一个都能够引发接收错误中断请求。

当“接收错误状态中断请求”被检测到,引发请求的信号可以通过读取UERSTATn来识别。

当接收器要将接收移位寄存器的数据送到接收FIFO,它会激活接收FIFO满状态信号,如果控制寄存器中的接收模式选为中断模式,就会引发接收中断。

当发送器从发送FIFO中取出数据到发送移位寄存器,那么FIFO空状态信号将会被激活。

如果控制寄存器中的发送模式选为中断模式,就会引发发送中断。

如果接收/发送模式被选为DMA模式,“接收FIFO满”和“发送FIFO空”状态信号同样可以产生DMA请求信号。

与FIFO有关的中断如下表所示:表8-1 与FIFO有关的中断10.3 UART错误状态FIFO除了接收FIFO寄存器之外,UART还具有一个状态FIFO。

状态FIFO中表示了在FIFO 寄存器中,哪一个数据被毫无错误地接收。

假设UART的FIFO连续接收到A, B, C, D, E字符,并且在接收B字符时发生了帧错误(即该字符没有停止位),在接收D字符时发生了奇偶校验错。

虽然UART错误发生了,错误中断不会产生,因为含有错误的字符还没有被CPU读取。

当字符被读出时错误中断才会发生。

如下图所示:图8-2 UART接收5个字节其中包含2个错误的情况10.4波特率发生器每个UART的波特率发生器为传输提供了串行移位时钟。

波特率产生器的时钟源可以通过S3C44B0X的内部系统时钟来选择。

波特率时钟通过时钟源16分频和一个由UART波特率除数寄存器(UBRDIVn)指定的16位除数决定。

UBRDIVn的值可以按照下式确定:UBRDIVn =(取整)(MCLK/(bps×16))-1除数的范围为1到(216-1)。

例如,如果波特率为115200 bps且系统主频(MCLK)为64MHz,则UBRDIVn为:UBRDIVn = (int)(64000000/(115200×16))-1=35-1 =3410.5回送模式S3C44B0X的UART提供一个测试模式,即回送模式。

在这种模式下,发送的数据会立即被接收。

这一特性运行处理器校验内部发送和接收通道的功能。

这种模式可以通过设置UART控制寄存器(UCONn)中的回送位来设定。

10.6红外通信模式S3C44B0X的UART模块支持红外线(IR)发送和接收。

可以通过设置UART控制寄存器(ULCONn)中的红外模式位来选择这一模式。

在IR发送模式下,发送阶段通过正常串行发送占空比3/16的脉冲波调制(当传送的数据位为0);在IR接收模式下,接收必须检测3/16脉冲波来识别0值。

如下图:通常情况下传输帧的时序红外线接收模式下时序图图8-3 红外线传输模式时序10.7 UART寄存器寄存器名称中的n表示0~1,例如ULCONn对应串口0为ULCON0, 对应串口1为ULCON1。

10.7.1 UART线控制寄存器前面我们多次提到了线控制控制寄存器,它主要用来规定传输帧的格式。

下面就来看看线控制寄存器的位定义:10.7.2 UART控制寄存器10.7.3 FIFO控制寄存器10.7.4 UART的Modem控制寄存器10.7.5 UART发送/接收状态寄存器10.7.6 UART错误状态寄存器10.7.7 UART的FIFO状态寄存器10.7.8 UART的Modem状态寄存器10.7.9 UART发送/接收保持(缓冲区)寄存器UART接收保持(缓冲区)寄存器和FIFO寄存器:URXH0, URXH1注意:如果发生了溢出错误,必须读一次URXHn 。

如果不读,即使USTATn中的溢出错误位被清除了,下一个接收的数据仍然会发生一个溢出错误。

10.7.10 UART波特率除数寄存器。