ARM嵌入式系统中双口RAM的驱动开发及应用_图文.

1ARM和嵌入式系统介绍PPT课件

ARM Cortex

ቤተ መጻሕፍቲ ባይዱ

A应用处理器(Application Processor )系列 R实时控制处理(Real Time Control )系列 M微控制器(Micro Controller )系列

2021

10

1. ARM7微处理器系列

该系列包括ARM7TDMI、ARM7TDMI-S、带有高速 缓存处理器宏单元的ARM720T和扩充了Jazelle的 ARM7EJ-S。该系列处理器提供Thumb 16位压缩指 令集和EmbeddedICE软件调试方式,适用于更大规 模的SoC设计中。

2021

8

1.1.3 ARM微处理器系列

ARM公司开发了很多系列的ARM处理器核,目前最 新的系列是Cortex,而ARM6核以及更早的系列已经很 罕见了。当前应用比较多的ARM处理器核系列有:

V4T版本

V5TE版本

V6版本 V7、V8版本

ARM7

ARM9

ARM9E

ARM10E

ARM11

Cortex

Intel StrongARM

Xscale

T变量代表支持16位Thumb指令集; E变量代表增强型(Enhanced)DSP算法指令。

2021

9

ARM公司在经典处理器ARM11以后的产品改用 Cortex命名,基于ARM V7、V8版本的ARM Cortex系 列产品由A、R、M三个系列组成,具体分类延续了一 直以来ARM面向具体应用设计CPU的思路。

授权,因此既使得ARM技术获得更多的第三方工具、制造、软

件的支持,又使得整个系统成本降低,使产品更容易被消费者

所接受,更具有竞争力。

2021

6

1.1.2 ARM微处理器的应用领域及特点

双口RAM在嵌入式系统调试中的应用

路 板面 积 。配台 IA总 线采 用 中 S

不仅可 满 足上 位 机 多任务控 制 系统 的需要

, ,

还

可 提 高本 系统 实时数 据 的处 理时 1l I 序 中 睦 时 效

。

I 7 3 ( ) 上位机 地址 DT 1 0U6 在

信方式, 或因结构复杂, 或因 传递

B

,

种 插 卡 式 可 编程 控 制 器 a该 嵌 入 式

I T 10 美 国I T 司采用 高 为与 上位机 共享 的通信 数据 区 如 图 D 73 是 D 公 P C实 质是 一个 智能 化 I L / O接 口卡 , 性 能 的 c s Mo 工艺生 产 的高速 1 K 2 所示 i 轰器件 的高集 成 度大大 简化

维普资讯

、

\

置 与 ] ■ 茸 结 E :

双 口 RAM 在 嵌 入 式 系 统 调 试 中 的 应 用

羲 毫 文 台 牡 曲 点 夼 t 渔 八 P 毒 辕 | 本 蛄 糕 采 特 , 甥 它 嵌 成 L 蜕 硬 I e

:: #

j

该片用别同的断志 芯 运 有 于 类 中标 进

行总线仲裁: 存储阵列中的 ×3E FH

和 ×3F F H单元被用做通信 “ 邮箱 ,

择调磷 竹萋席 怠媾了 _ 《 霉溉 箕罐虢攫神 强 鲥 调,

黪嚣 l中嘲貔蔫戮婚 . 谚 试 最。

j 嘲 R M ^ { 统 试 ≤ | 藏口 ^ j 或 摹 调 嵌

芯片却 独具特 点 :①具 有两套 完垒

卜 上 — — 003 、 8:04F - — — — 一 0.F 00003 — 0-F D 00-F - 0 - 1

00 00

~

ARM嵌入式系统原理及应用开发 第4章 ARM嵌入式系统程序设计及调试基础

格式:标号 DCD(或DCDU) 表达式

用途:分配一片连续的字存储单元并用伪指令指定的表达式初

始化。其中,表达式可以为程序标号或数字表达式。DCD伪指令

也可用“&”代替。DCD伪指令和DCDU伪指令的区别仅在于用

DCD伪指令分配的字存储单元是字对齐的,而用DCDU伪指令分配

的字存储单元并不严格字对齐。例如:

FdataTest DCD 4,5,6 ;分配一片连续的字存储单元并初

始化

4)DCFD(或DCFDU)

格式:标号 DCFD(或DCFDU) 表达式

用途:为双精度的浮点数分配一片连续的字存储单元并用伪指

令中指定得表达式初始化。每个双精度的浮点数占据2个字单元。

DCFD伪指令和DCFDU伪指令的区别仅在于用DCFD伪指令分配的

第4章 ARM嵌入式系统程序设计及调试基础

4.1 ARM嵌入式汇编语言程序设计基础 4.2 ARM嵌入式C语言程序设计基础 4.3 ARM汇编语言与C/C++的混合编程 4.4 ARM ADS集成开发环境的使用 4.5 Embest IDE集成开发环境的使用

1

4.1 ARM嵌入式汇编语言程序设计基础

在ARM得汇编程序中,有符号定义(Symbol Defintion) 伪指令,数据定义(Data Definition)伪指令,地址读取伪 指令,汇编控制(Assembly Control)伪指令,宏指令以及 其它伪指令。

2

1.符号定义伪指令 1)GBLA、GBLL和GBLS 格式:GBLA(GBLL或GBLS) 全局变量名 用途:定义一个ARM程序中的全局变量,并将其初始化。其 中GBLA伪指令用于定义一个全局的数字变量,并初始化为0; GBLL伪指令用于定义一个全局的逻辑变量,并初始化为F(假); GBLS伪指令用于定义一个全局的字符串变量,并初始化为空。 由于以上3条伪指令用于定义全局变量,因此在整个程序范围 内变量名必须唯一。例如: GBLA Test1 ;定义一个全局的数字变量,变量名为Test1 Test1 SETA 0xAA ;将该变量赋值为0xAA GBLL Test2 ;定义一个全局的逻辑变量,变量名为Test2 Test2 SETL {TRUE} ;将该变量赋值为真 GBLS Test3 ;定义一个全局的字符串变量,变量名为 Test3 Test3 SETS “Testing” ;将该变量赋值为“Testing”

双口RAM在机载嵌入式系统中的应用

网络与信息工程2018.04双口 RAM 在机载嵌入式系统中的应用陈伊卿(航空工业计算所,陕西西安,710029)摘要:针对机载嵌入式实时系统中串行数据高速通信的需求,本文提出了一种使用双口 R A M 实现数据缓存的方案,并详细介 绍了双口 R A M 的工作原理及在本系统中的软件实现方法。

经测试验证表明,应用双口 R A M 在嵌入式系统中进行数据通信,实时 性强、准确率高、性能稳定。

关键词:双口 R A M ; CPU ; DSPApplication of Dual Port RAM in Airborne Embedded SydtemChen Yiqing(Xi/ an Aeronautics Computing Technique Research Institute, AV I C , X i ? an Shaanxi, 710029)Abstract: To t he r e q u i r e m e n t of h i g h s p e e d serial d a t a c o m m u n i c a t i o n in a i r b o r n e e m b e d d e d r e a l -t i m e system,this p a p e r p r e s e n t s a s c h e m e of u s i n g dual p o r t R A M to r e a l i z e d a t a cache, a n d i n t r o d u c e s in deta i l the w o r k i n g p r i n c i p l e of d u a l p o r t R A M a n d t he s o f t w a r e r e a l i z a t i o n method. T h e tes t r e s u l t s s h o w tha t the a p p l i c a t i o n of dual p o r t R A M in the e m b e d d e d s y s t e m fo r d a t a communication, real-time, h i g h a c c u r a c y a nd s t a b l e performance.Keywords: Dual P ort R A M ;C P U ;D S P〇引言在机载嵌入式实时系统中,串行数据的采集及交换是影响系 统开销的瓶颈之一。

双端口RAM在单片机系统中的应用

摘要阐述了双端口RAM使用的一种方法,当其应用于双机容错系统时,可简化电路,提高系统的可靠性。

本方案经实践证明是有效且实用的。

关键词双端口RAM 双机容错切换系统硬件冗余1引言在对产品可靠性要求高的系统中,往往需要硬件冗余。

有些设备不仅要求其在各种恶劣的天气下工作,而且要求长期不间断工作。

为提高可靠性往往采用双CPU系统。

平时主单片机系统工作,并将所处理的数据存储在外存,一旦主CPU系统出现故障,副CPU可切换上来,并利用公共外存的数据继续工作,而不需要人工干预。

这时双端口RAM做为外存就是两个CPU之间信息传递的最好渠道。

本文以美国IDT公司生产的IDT7130为例,阐述双端口RAM在最常用的80C31双机系统中的应用。

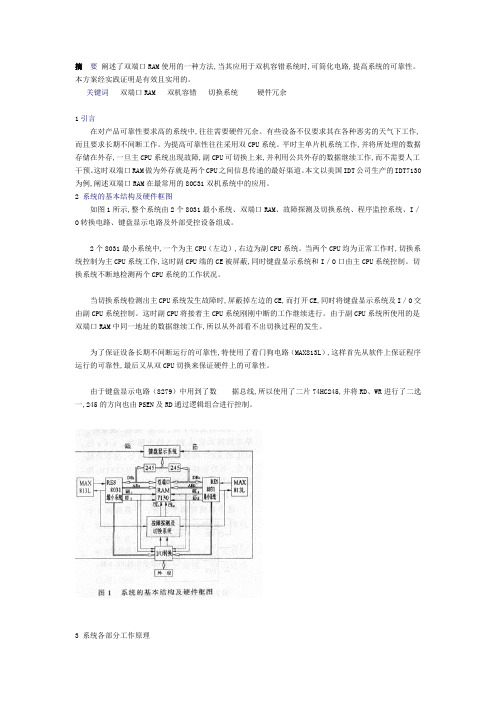

2 系统的基本结构及硬件框图如图1所示,整个系统由2个8031最小系统、双端口RAM、故障探测及切换系统、程序监控系统、I/O转换电路、键盘显示电路及外部受控设备组成。

2个8031最小系统中,一个为主CPU(左边),右边为副CPU系统。

当两个CPU均为正常工作时,切换系统控制为主CPU系统工作,这时副CPU端的CE被屏蔽,同时键盘显示系统和I/O口由主CPU系统控制。

切换系统不断地检测两个CPU系统的工作状况。

当切换系统检测出主CPU系统发生故障时,屏蔽掉左边的CE,而打开CE,同时将键盘显示系统及I/O交由副CPU系统控制。

这时副CPU将接着主CPU系统刚刚中断的工作继续进行。

由于副CPU系统所使用的是双端口RAM中同一地址的数据继续工作,所以从外部看不出切换过程的发生。

为了保证设备长期不间断运行的可靠性,特使用了看门狗电路(MAX813L),这样首先从软件上保证程序运行的可靠性,最后又从双CPU切换来保证硬件上的可靠性。

由于键盘显示电路(8279)中用到了数据总线,所以使用了二片74HC245,并将RD、WR进行了二选一,245的方向也由PSEN及RD通过逻辑组合进行控制。

双端口RAM在ARM与DSP通信系统中的应用

一

入式作为主设备 ,主要完成数据处理 、存储 与网络传

输工作, DS 作为从设备需要负责复杂的算法 实现 。 而 P 在此高速数据采集和处理系统 中,随着采样数据量 的

地址进行 读写操作时,会因为数据 的冲突 而造 成存

储或读 取的错 误。对 同一存储单元的操作存在 以下四 种情况 : ()两个 端 口不 同时对 同~地 址单元进行读 写数 1

据,另一个读 出数据 。

前两 种情况 不会造成对双端 口R M 的读 写错误 , A 第三种情况会造成写入数据的错误 ,第四种情况会造 成读出错误 。为了避 免对双端 口 R M 造成读写错误 , A

双端 口 S A R M, 其典 型功耗为 7 0 5 mW,它具有两个等

级 的存取时间:商业 级有 1/0 5 55 s ma) 52/ / /5 ( x ,工 23 n

()两个 端 口同 时对 同一 地 址 单元 进行 读 出数 2

据。

()两 个 端 口同时对 同一地 址 单元 进行 写 入 数 3

据。

()两个端 口同时对一个地址 单元 ,一个 写入数 4

1 I T 0 6 双端 IR M功能简介 D 72 1 3 A

I T 0 6 是美国 I D 721 DT公司生产的高速 1K ̄ 6 6 1 的

示放弃使 用权。 当左端 口要使用双端 口 R AM 时 ,先

写入 0到标 志锁存 器,然 后读 出标志锁 存器 的状态 ,

若读出的值 为 0 ,则左端 口获得 该存储单元 的使用 权; 若 读 出的值 为 1 ,表 明右端 口正在使 用该存储单元 。

此 时,左端 口要么循环检测锁存器状 态,直到右端 口 使用 结束 ,要 么 向锁存器写入 1 ,撤 销请求。 同理 , 若右端 口使用双端 口 R M 时 ,仍按照上述步骤进行 A 操作 1 ’。 一

最新ARM嵌入式系统原理及应用开发 15 第3章 ARM嵌入式处理器指令系统PPT课件

第3章 ARM嵌入式处理器指令系统

3. 逻辑右移操作 格式:通用寄存器,LSR 操作数 用途:对通用寄存器中的内容进行逻辑右移操作,按操作数所 指定的数量向右移位,左端(高位)用零来填充。其中,操作数可以 是通用寄存器中的数值,也可以是立即数(立即数的取值范围是0~3l 之间的整数)。 例如:MOV R0, R1, LSR# 2;将R1中的内容逻辑右移2位 后传送到R0中,左端用零来填充 4.算术右移操作 格式:通用寄存器,ASR 操作数 用途:对通用寄存器中的内容进行逻辑右移操作,按操作数所 指定的数量向右移位,左端(高位)用第31位的值(亦即符号位)来 填充。其中,操作数可以是通用寄存器中的数值,也可以是立即数 (立即数的取值范围是0~3l之间的整数)。 例如:MOV R0, R1, ASR#2 ;将R1中的内容算术右移2位 后传送到R0中,左端用第31 位的值来填充

2

第3章 ARM嵌入式处理器指令系统

第3章 ARM嵌入式处理器指令系统

第3章 ARM嵌入式处理器指令系统

第3章 ARM嵌入式处理器指令系统

第3章 ARM嵌入式处理器指令系统

7

第3章 ARM嵌入式处理器指令系统

8

第3章 ARM嵌入式处理器指令系统

3.1.3 ARM指令中的Fra bibliotek作数符号1. 立即数符号"#" “#”符号表示立即数,该符号后的数据可以是二进制数, 也可以是十进制数或十六进制数,如果操作数为十进制数, 则前面除了#外,没有其他符号。 2. 二进制符号"%" "%"符号后面的数字表示二进制数,如%10010101表 示二进制数10010101,即十进制数149。 3. 二进制符号"2_" "2_"符号是二进制前缀的另一种形式,如2_10010101 也表示二进制数10010101,与%10010101等效。

ARM嵌入式技术原理与应用解析课件

2023/12/29

◆ DSP是运算密集处理器,一般用在快速执行算

法,做控制比较困难。为了追求高执行效率,不

适合运行操作系统,核心代码使用汇编。

应用领域:

数字滤波

频谱分析

FFT

流行的嵌入式DSP:

TMS320C2000系列(TI)

MCS-296(Intel)

2023/12/29

4)混合处理器和片上系统(SOC)

5) 嵌入式系统分散而不可垄断

通用计算机行业被微软和因特尔垄断(软件和硬件)

嵌入式系统领域的芯片、操作系统、软件,充满了竞

争、发展和机遇,呈现一种百花齐放的景象。

2023/12/29

3. 嵌入式系统开发特点

需要软硬件综合开发,二者密切相关。

任何一个嵌入式产品都是软件和硬件的结合体

一旦嵌入式产品研发完成,软件就固化在硬件环境中,

半,生产厂家20多个,350多种衍生产品,仅

Philips就有近百种。处理速度从0.1MIPS到

2000MIPS,寻址空间从64KB到4GB。

2023/12/29

嵌入式微处理器发展趋势

▉

经济性(成本)

▉

微型化(封装、功耗)

▉

智能化(功能、速度)

嵌入式微处理器主要分类如下:

2023/12/29

◆ 微控制器(MCU)

SRAM

看门狗及复

位电路

软件

实时操作系统(RTOS)

SOC/SOPC

GPIO

处理器/ARM核

IIS

MMU/Cache

Timer/RTC

ADC/DAC

输入输

出接口

CAN

以太网

基于双口RAM实现双核通信模块的驱动设计

基于双口RAM实现双核通信模块的驱动设计潘必超;曹彪【摘要】The flexibility of process control is greatly affected by the relatively closed hardware architecture and limited amount of control parameters. It is a trend to develop a smart controller with open hardware architecture which can make it possible of control process network. With the use of Dual-Port RAM CY7C024AV2,A dual-core solution with DSP and ARM is presented,as long as the driver development under embedded Linux for the dual-core controller module. The driver presented provided software basis for intelligent network control methods. Experiment result shows that the driver can achieve a good performance on inter-core communication.%传统单核心控制器受制于硬件结构相对封闭,可控参数有限,一定程度上影响了工艺过程控制的灵活性。

设计一种开放式的控制器,实现过程控制网络化是当今物联网发展的趋势。

文章基于嵌入式Linux系统平台,使用高速双端口RAM芯片CY7C024AV2,提出一种模块化的DSP与ARM的双核通信模块方案及其驱动程序的设计,实现了控制器的双核数据通信功能,为控制器的网络智能控制建立了软件基础。

双口RAM原理及应用实例PPT

双口RAM在FPGA中的实现

选用Xilinx公司的Spartan-6 FPGA器件, 基于低功耗45 nm、9-金属铜层、双栅极氧 化层工艺技术,提供高级功耗管理技术, 150 000个逻辑单元,集成式PCI Express模 块,高级存储器支持。250 MHz DSPslice和 3.125 Gb/s低功耗收发器。 通过Verilog HDL语言对双口RAM功能的 描述就能在一片FPGA器件内实现8位16字 节的双口RAM,并进行读写操作控制。双 口RAM读写操作控制采用Verilog HDL代码。

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、 GAL、CPLD等可编程器件的基础上进一步 发展的产物。它是作为专用集成电路 (ASIC)领域中的一种半定制电路而出现 的,既解决了定制电路的不足,又克服了 原有可编程器件门电路数有限的缺点。

FPGA采用了逻辑单元阵列LCA(Logic Cell Array) 这样一个概念,内部包括可配置逻辑模块CLB (Configurable Logic Block)、输入输出模块IOB (Input Output Block)和内部连线(Interconnect) 三个部分。 现场可编程门阵列(FPGA)是可编程器件,与传 统逻辑电路和门阵列(如PAL,GAL及CPLD器件)相比, FPGA具有不同的结构。FPGA利用小型查找表 (16×1RAM)来实现组合逻辑,每个查找表连接到一 个D触发器的输入端,触发器再来驱动其他逻辑电路或 驱动I/O,由此构成了既可实现组合逻辑功能又可实现 时序逻辑功能的基本逻辑单元模块,这些模块间利用 金属连线互相连接或连接到I/O模块。FPGA的逻辑是 通过向内部静态存储单元加载编程数据来实现的,存 储在存储器单元中的值决定了逻辑单元的逻辑功能以 及各模块之间或模块与I/O间的联接方式,并最终决定 了FPGA所能实现的功能,FPGA允许无限次的编程。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CY7C027的驱动开发

3.1驱动程序功能概述

为了在Linux2.6操作系统下实现本文所述的功能,必须为阿尔泰嵌入式开发板、嵌入式工控板、核心板

嵌入式开发板:包含ARM7、ARM9、Xscal、CPU为核心的教学开发板和企业评估板:

嵌入式工控板:以工业级嵌入式微控制器为核心的数据采集和现场控制、远程通讯为一体的高端工业控制产品。

址到虚拟地址的映射,这个工作在每次打开设备时执行。对于

3.2.3虚拟地址资源的分配

的中断并唤醒读进程。驱动程序整体结构框图见图2。具体的在Linux中,无法直接访问某一物理地址空间,而是必须访

file_operations结构被初始化为:struct

file_operations

问经过映射的虚拟地址。在dpram_open例程中实现了物理地

dpram_fops={

图1系统连接框图

张震:硕士研究生

另一方面,ARM从以太网获得远端处理机下达的命令,解析后通过DPRAM转达给前端的CPLD。使数据源采集端执行相应的命令。系统连接方式如图1:

ARM处理器选用AT91RM9200。这是一款ARM920T核心的处理器,工作时钟180MHz时可达到200MIPS。它拥有以太网

间断、快速的数据传输。

关键词:嵌入式系统;双端口RAM;Linux2.6;驱动程序中图分类号:1.1B鹞.1文献标识码:A

Abstract:RISCprocessorsbasedon

nvariousdigitalsystems.Thisarticletook

AT91RM9200

控制器等丰富的外设,比较适合本文的应用。

本应用选用的CY7C027是CYPRESS公司采用0.35一mi—cronCMOS工艺生产的一款高性能32K

X

16bit双端口静态

RAM。CY7C027的两个端口各有一套控制线(nCE片选,nOE输出使能,R/W读写信号)控制两个端口独立地对片上资源进行访问。最高的两个地址(7FFE和7FFF)作为左右两端的邮箱。当左端向右端邮箱7FFF写入16bit“信件”时,在右端产生INT中断信号;当右端读取邮箱时,中断信号被清除。同理,右端也可以写左端邮箱7FFE使左端产生中断信号。利用这种机制就可以方便地实现左右端口的信息交流。

调用提供接口。对于本应用,驱动程序实现的主要功能有:读时进行的注册和申请,必须在卸载模块时注销。即在dpr砌_exit

DPRAM数据至用户空间、把用户空间的数据写入DPRAM、把

函数中执行unregister_chrdev和free_irq来释放资源。

用户空间的命令写入DPRAM右端邮箱以及响应DPRAM产生

核心板:提供模块化构建嵌入式系统、快速开发、轻松定制。公司目前已形成以产品为主导。以技术服务为支撑的产品研发、销售、服务体系。

一134—360元,年邮局订阅号:82-946

万方数据

ARM开发与应用

CY7C027提供一个驱动程序。在Hnux中,所有的硬件设备都

针;SAINTERRUPT表示这是一个“快速”中断处理例程,它运像常规文件一样看待,它们可以使用和操作文件相同的,标准

ARM开发与应用

中文核心期刊《微计算机信息>(嵌入式与SOC)2007年第23卷第3—2期

文章编"号:1008-0570(2007)03—2—0134—03

ARM嵌入式系统中双口RAM的驱动开发及应用

Applicationanddriverdevelopmentofdual-port

RAM

inembeddedsystem

as

systemplat・

form,anddesigned

a

real-timedatainterfacebased

on

dual-port

RAM(DPRAM),and

also

developedthedriverforLinux2.6

to

implementthe“Ping-Pong”transmissionoftheDPRAM.Moreover,continuesandfast

datatransmissionbetweendatasource

and

processorWasimplemented.

Keywords:Elnbeddedsystem。dual-portRAM,Linux2.6,driver

1引言

基于ARM技术的32位RISC处理器由于具有高性能、高集成、低功耗、外设丰富、指令精简的优点广泛应用于各种嵌入式系统中。在很多嵌入式应用场合中,需要处理器间进行实时高速不问断的数据传输,传统的传输方式或者速度不够,或者容易受外界干扰,或者容易丢失数据。因此我们常采用双端口

2模块整体架构

在本文应用中,ARM作为主控制器,DPRAM作为ARM处

理器与前端数据源之间的通信桥梁。数据源端从传感器获得数

据,通过CPLD产生读写时序写入DPRAM中的两个区,ARM

以“乒乓”方式进行读取后对数据重新封装。通过以太网发送到

远端处理机。

AT91R_Ad9200

CY7C027

EP狮512

行在中断禁用的状态下。这样做是因为并没有其他设备共享的系统调用来进行打开、关闭和读写。用户程序通过相应的系IRQO;”@ram”表示中断的拥有者,这可以:[!E/pme/interrupts中显统调用来访问硬件设备,设备驱动程序的作用正是为这些系统示;最后的NULL表示没有强制使用共享方式。在装载驱动模块

RAM(Dual—Port

RAM即DPRAM)作为数据传输的桥梁。由于其

接口简单,使用方便,此类芯片已经广泛应用于嵌入式领域,为

处理器间的通信提供了很好的解决方案。本文在AT91RM9200处理器平台的基础上,通过双口RAMCY7C027与数据源进行通信,并描述了在嵌入式Ⅱnux2.6中其驱动程序的开发过程。

(1.中国科学院声学研究所;2.中国科学院研究生院)张震1,2李淑秋1

ZHANGZHEN

LISHUQIU

摘要:基于ARM的RISC处理器广泛应用于各种数字系统中.本文以AT91RM9200为系统平台,设计了一种基于双口RAM的

实时数据接口,针对双口RAM的“乒乓”传输方式在Linux2.6下设计并开发了其驱动程序,最终实现了数据源与处理器问不