LDO工作原理详解

ldo电源原理

ldo电源原理

LDO(低压差稳压器)电源原理是一种用于将高电压转换为较低电压的线性稳压器件。

它通过引入电流源和功率晶体管来实现。

LDO有三个主要部分:参考电压源、差分放大器和功率晶体管。

参考电压源提供一个固定的、稳定的电压作为基准。

差分放大器比较输入电压与参考电压,并产生一个差分电压作为控制信号。

功率晶体管根据控制信号来调整输出电压,以维持稳定。

当输入电压高于输出电压时,差分放大器会通过控制信号将功率晶体管逐渐关闭。

这使得输出电压不断下降,直到与参考电压相等为止。

反之,如果输入电压低于输出电压,则差分放大器会逐渐打开功率晶体管,使输出电压上升。

LDO的优点是具有低静态电流和低输出噪声。

由于其基于线性稳压原理,LDO能够提供更稳定的输出电压,并且对负载变化的响应更快。

LDO的工作原理可以总结为:通过比较输入电压和参考电压的差异,控制功率晶体管的开关状态,以实现输出电压的稳定调整。

这种设计使LDO成为广泛应用于低压差电源中的一种理想选择。

ldo工作原理

ldo工作原理

LDO(Low Drop-Out)是一种电压稳压器,工作原理如下:

1. 电压差:LDO通过一个参考电压和输入电源之间的电压差

来工作。

输入电源电压要高于参考电压。

2. 参考电压:LDO内部包含一个参考电压源,通常为基准二

极管或参考电流源。

参考电压源的输出电压在很大程度上稳定,可提供稳定的参考电压给控制电路使用。

3. 错误放大器:LDO内部还包含一个错误放大器,用于比较

参考电压和反馈电压。

反馈电压来自于输出端的电阻分压。

4. 控制电路:错误放大器将参考电压和反馈电压进行比较,并产生一个误差信号,通过控制电路调整LDO的输出。

控制电

路通常包括一个误差放大器、一个误差电流源和一个输出驱动器。

5. 调整元件:LDO的调整元件可根据误差信号进行调整,以

达到输出电压的稳定。

6. 输出电压:最终,LDO将输入电压通过调整元件和控制电

路转换为稳定的输出电压供给负载使用。

需要注意的是,LDO的输入电压和输出电流之间有一定的电

压差损耗,称为“Drop-Out Voltage”。

在LDO额定电流范围内,Drop-Out Voltage越小,LDO的性能越好。

ldo工作原理通俗易懂

ldo工作原理通俗易懂

ldo工作原理通俗易懂

LDO,即低压差稳压器,是一种将高电压输入转换为较低电压输出的一种电路。

LdO有很多种类,它们都具有低压差,稳压性能良好,低噪声输出,切断电流低等特点,是很好的稳压电源,可用于微处理器,存储器,模拟电路,数字电路,传感器,电动机等系统的供电电路。

ldo的工作原理是,当输入电压较高时,ldo的控制部件开始工作,控制部件的输出将控制电流过滤电容,该电容会吸取一部分电流,从而把高电压转换为较低的电压,这就是ldo的原理。

LDO也可以稳定输出电压,当输入电压发生变化时,ldo会根据控制部件的输出,调整电流过滤电容的引脚,从而调整输出电压,使它保持在所需要的电压水平。

LDO的输出电压可以从几个mV到几千mV不等,具体是多少取决于使用ldo的电路,由于ldo具有较低的噪声,可以很好地为精密的电路提供稳定的电源电压。

总结:LDO是一种将高电压输入转换为较低电压输出的一种电路。

它的工作原理是,当输入电压较高时,控制部件的输出将控制电流过滤电容,从而把高电压转换为较低的电压。

ldo可以通过调整电流过滤电容的引脚,稳定输出电压,使其保持在所需电压水平,为精密电路提供稳定的电源电压。

- 1 -。

ldo 工作原理

ldo 工作原理LDO(Low Dropout Regulator),中文翻译为低压差稳压器,是一种常见的电压调节器件。

它是一种具有线性稳压功能的电源管理芯片,输如电压可以是高于或低于输出电压。

LD0稳压器的工作原理是利用负反馈技术,使输出电压稳定在设定值,不受输入电压的变化影响。

一个LDO稳压器通常由三个主要部分组成:参考源,误差放大器和功率级。

参考源是一个固定电压源,通常是基准二极管或Zener二极管。

误差放大器对参考电压和输出电压进行比较,生成一个反馈信号。

功率级根据反馈信号产生相应的输出电压,将输入电压降至输出电压以下的压差,这就是“低压差”的含义。

LDO稳压器的工作原理如下:1. 当输入电压高于输出电压时,LDO稳压器将输入电压通过功率级降至输出电压水平,这意味着LDO稳压器的负载特性是线性的。

2. 当输入电压下降,LDO稳压器必须增加其输出电流来保持输出电压恒定。

这可以通过功率级的控制来实现,功率级可以改变其大小以适应负载的变化。

3. 如果LDO稳压器输出电流很小,那么其负载特性会失去线性。

在这种情况下,LDO稳压器将变成一种不能控制其输出电压的电路,因此需要通过负载电流的限制来避免输出电压失控。

4. 如果输入电压超过LDO稳压器所能处理的最大电压,那么它将无法正常工作。

在这种情况下,需要使用其他保护手段来保护LDO稳压器。

LDO稳压器的主要优点是:它能够提供非常稳定和干净的输出电压,并能够在负载变化时保持较高的输出准确性和稳定性。

它还可以在噪声和干扰环境中工作,为模拟电路提供优质的电源供应,并且非常适用于需要低功耗、低成本和小体积的应用场景。

总之,随着技术的不断进步,LDO稳压器在电源管理领域发挥着越来越重要的作用。

LDO稳压器不仅能够有效解决电源问题,还能够使模拟电路性能得到显著提升,从而满足不同应用场景的需求。

ldo工作原理带宽

ldo工作原理带宽LDO(低压差线性稳压器)是一种用于调节电压的电子元件,其主要特点是输入电压与输出电压之间的差值较低。

LDO工作原理主要基于比较器、放大器和调整管等元件来实现输出电压的稳定。

LDO的工作原理如下:1. 比较器:比较器的同相输入端连接取样电阻,反相输入端连接基准电压Uref。

当输出电压Uout降低时,取样电压与基准电压的差值增大,从而使比较器的输出驱动电流增加。

2. 放大器:比较器的输出驱动电流经过放大器A放大后,控制串联调整管的压降,以达到稳定输出电压的目的。

3. 调整管:调整管VT根据放大器的输出电流调整其电阻值,从而使输出电压保持稳定。

当输出电压降低时,调整管的压降增大,以减小输出电压的下降。

4. 取样电阻:取样电阻R1和R2用于收集输入电压和输出电压之间的差值,以便比较器进行比较。

LDO的带宽是指其输出电压信号的频率响应范围。

在理想情况下,LDO的带宽越宽,输出电压信号的稳定性越好。

实际应用中,带宽受到器件参数、电路设计等因素的影响。

为了提高LDO的带宽,可以采用以下方法:1. 选用高带宽的比较器和放大器:采用性能更好的比较器和放大器,可以提高LDO的带宽。

2. 减小取样电阻的阻值:减小取样电阻的阻值可以降低比较器的输入电容,从而提高带宽。

3. 优化电路布局和元件选择:合理布局电路,选用合适的元件,可以降低电路中的寄生电容和电阻,从而提高带宽。

4. 采用多级放大器设计:通过将LDO电路设计为多级放大器结构,可以进一步提高带宽。

总之,LDO的工作原理和带宽与其电路设计、元件选择和布局等因素密切相关。

为了实现较高的带宽,需要综合考虑这些因素并进行优化。

介绍LDO的工作原理

介绍LDO的工作原理LDO是“线性低压差稳压器(Linear Low Drop-Out regulator)”的缩写。

它是一种常见的稳压器,用于将不稳定的输入电压转换为稳定的输出电压,以供给各种电子设备和电路使用。

LDO的工作原理如下:当输入电压超过稳压器的正常工作要求时,LDO器件的内部功率晶体管将打开,通过有源调节控制电路将调整过的电压输出到负载电路上。

而当输入电压低于稳压器的正常工作要求时,内部功率晶体管关闭,由控制电路切断输出,以保护稳压器和负载电路。

LDO主要由以下几个组成部分构成:1. 电压参考源(Voltage Reference):它是LDO的核心部件,为稳压器提供一个稳定的基准电压。

通常使用基准电流源、电阻分压器、电压比较器等组成来实现。

2. 误差放大器(Error Amplifier):它与电压参考源相连,用于通过比较输出电压与基准电压之间的差异来产生误差信号。

误差放大器将误差信号放大,并通过反馈回路调节功率晶体管的导通。

3. 反馈回路(Feedback Loop):它由稳压器的输出到误差放大器之间的电阻网络组成,用于将输出电压与参考电压比较,以产生误差信号。

4. 输出级(Output Stage):它通过功率晶体管将调节过的电压输出到负载电路上。

功率晶体管的导通和截止通过误差放大器的调节来实现。

LDO的主要工作过程如下:1.当输入电压高于稳压器所需的输出电压时,误差放大器将产生一个正的误差信号。

此时,反馈回路通过将误差信号反馈给误差放大器,调节功率晶体管的导通,使其降低输出电压,直到误差信号减少至零。

2.当输入电压低于稳压器所需的输出电压时,误差放大器将产生一个负的误差信号。

此时,反馈回路通过将误差信号反馈给误差放大器,将功率晶体管关闭,以避免输出电压过低。

LDO的优势和特点包括以下几点:1.低压差:LDO可以在输入电压较低的情况下仍能提供稳定的输出电压,因此可以满足低压差、高精度的稳压要求。

LDO的工作原理详细分析

LDO的工作原理详细分析LDO(Low-Dropout)是一种线性稳压器件,其工作原理是通过控制输出端与负载之间的电压差来实现稳压,将高电压的输入电源转换为所需的稳定低电压输出。

下面将详细分析LDO的工作原理。

LDO由输入级、控制级和输出级组成,其中输入级包括输入电源、输入电感和输入电容;控制级包括误差放大器、参考电压、电流源和可调电阻;输出级包括输出晶体管、输出电感和输出电容。

(一)调整阶段1.输入级:当输入电源施加在输入电感上时,输入电感起到滤波作用,去除输入电源中的噪声和纹波。

输入电容则能够提供瞬态电流,减小对输入电源的要求。

2.控制级:误差放大器将输出电压与参考电压进行比较,并将比较结果输入给电流源,电流源通过可调电阻控制输出级的输出电压。

(二)稳定阶段1.输出级:当误差放大器将输出电压与参考电压进行比较后,电流源会调整输出级的输出电流,进而调整输出电压。

输出晶体管通过调整它的截止与饱和状态来控制输出电流,将不稳定的输入电压转换为稳定的输出电压。

2.输出电容:输出电容用于滤除加载纹波和提供输出电流,它能够稳定输出电压并降低输出纹波电压。

3.反馈回路:输出电压经过反馈回路返回到误差放大器中进行比较,这样在负载变化或输入电压变化时,误差放大器可以及时调整输出电流,使输出电压保持稳定。

LDO的电源线路具有低压降特性,当输入电源电压下降时,LDO可以通过调整输出级的输出电流来保持输出电压的稳定。

因此,LDO的输出电压只需要稍高于所需输出电压,具有低的压差(低压降)特性。

LDO主要由晶体管工作在放大状态,因此在它的基极和发射极之间存在一个较小的压差,这个压差也称为基极–发射极压降(VBE)或基极–源极压降(VBE)。

通过调整输入级的输入电流,LDO的VBE可以保持在一个较小的值,以实现低压降。

总结起来,LDO的工作原理可以归结为以下几个步骤:1.输入电源电压通过输入电感和输入电容滤波后进入LDO。

ldo工作原理通俗易懂

ldo工作原理通俗易懂

低压差分放大器(Low Dropout Regulator,简称LDO)是一种常见的线性稳压器件,主要用于将高电压降至较低电压,以供给电路中的其他元件使用。

LDO的工作原理相对简单,但却是实现电路稳压功能的重要组成部分。

LDO的工作原理可以简单描述为:当输入电压高于输出电压时,LDO会通过内部的电路将多余的电压转化为热量散失,以保持输出稳定在设定值。

这种工作方式可以确保输出电压始终保持在设定的值附近,不受输入电压波动的影响。

具体来说,LDO内部包含了一个差分放大器、一个误差放大器和一个功率晶体管。

差分放大器会比较输出电压与参考电压之间的差值,将这个差值传递给误差放大器。

误差放大器会根据差值调整功率晶体管的导通状态,以调整输出电压,使其与设定值保持一致。

在实际应用中,LDO的稳压精度和负载能力是两个重要的指标。

稳压精度指的是LDO输出电压与设定值之间的偏差,通常以百分比或毫伏数值表示。

负载能力则是指LDO能够提供的最大电流,通常以安培数值表示。

设计LDO时需要根据实际需求选择合适的器件参数,以确保电路正常工作。

总的来说,LDO作为一种简单而有效的稳压器件,在各种电子设备中都有广泛的应用。

通过掌握其工作原理,可以更好地理解电路中

各个元件之间的相互作用,为电路设计和调试提供有益的参考。

希望本文对LDO的工作原理有所帮助,让读者能够更深入地了解这一重要的电子元器件。

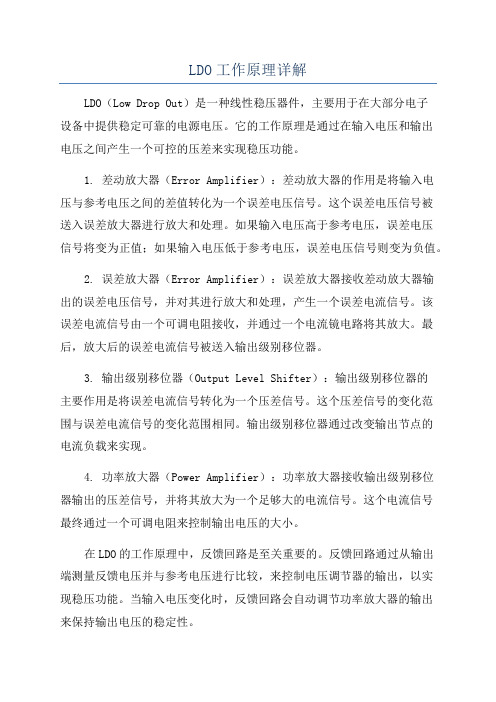

LDO工作原理详解

LDO工作原理详解LDO(Low Drop Out)是一种线性稳压器件,主要用于在大部分电子设备中提供稳定可靠的电源电压。

它的工作原理是通过在输入电压和输出电压之间产生一个可控的压差来实现稳压功能。

1. 差动放大器(Error Amplifier):差动放大器的作用是将输入电压与参考电压之间的差值转化为一个误差电压信号。

这个误差电压信号被送入误差放大器进行放大和处理。

如果输入电压高于参考电压,误差电压信号将变为正值;如果输入电压低于参考电压,误差电压信号则变为负值。

2. 误差放大器(Error Amplifier):误差放大器接收差动放大器输出的误差电压信号,并对其进行放大和处理,产生一个误差电流信号。

该误差电流信号由一个可调电阻接收,并通过一个电流镜电路将其放大。

最后,放大后的误差电流信号被送入输出级别移位器。

3. 输出级别移位器(Output Level Shifter):输出级别移位器的主要作用是将误差电流信号转化为一个压差信号。

这个压差信号的变化范围与误差电流信号的变化范围相同。

输出级别移位器通过改变输出节点的电流负载来实现。

4. 功率放大器(Power Amplifier):功率放大器接收输出级别移位器输出的压差信号,并将其放大为一个足够大的电流信号。

这个电流信号最终通过一个可调电阻来控制输出电压的大小。

在LDO的工作原理中,反馈回路是至关重要的。

反馈回路通过从输出端测量反馈电压并与参考电压进行比较,来控制电压调节器的输出,以实现稳压功能。

当输入电压变化时,反馈回路会自动调节功率放大器的输出来保持输出电压的稳定性。

另外,LDO还有一些辅助电路,用于保证其正常工作。

例如,过热保护电路可以检测芯片温度,当温度过高时会自动切断输出,以保护芯片免受损坏。

总结起来,LDO工作原理可以简单概括为:通过将输入电压与参考电压相比较,并产生一个误差电流信号,然后通过级联的误差放大器、输出级别移位器和功率放大器来调节输出电压,以实现稳压功能。

LDO的内部原理_工作过程及其应用

LDO的内部原理_工作过程及其应用LDO(Low DropOut)是一种线性稳压器件,其内部原理、工作过程以及应用如下:1.内部原理:LDO的工作原理基于负反馈机制,它通过将电源电压调整到输出端的目标电压,以保持输出电压的稳定性。

在负载电流不变的情况下,其输出电压与输入电压之间的差异很小,也即所谓的“压差”很低。

这使得LDO 能够在输入电压接近输出电压时工作,因此被称为“低压差降压器”。

LDO内部通常包含以下几个主要部件:- 参考电压发生器(Reference Voltage Generator):产生稳定的参考电压,作为输出电压的参考。

- 误差放大器(Error Amplifier):检测输出电压与参考电压之间的误差,并将其转化为控制信号。

- 电流增益放大器(Current Amplifier):将误差放大器的控制信号转化为合适的控制电流。

- 调整管(Pass Transistor):负责调整输入电压,并传递合适的电流至负载。

2.工作过程:LDO的工作过程如下:1)参考电压生成:在LDO输入电压中先经过一个稳压电路或稳压芯片,产生稳定的参考电压。

2)电压差放大:通过误差放大器检测输出电压与参考电压之间的误差,并将其放大。

3)电流放大:将误差信号通过电流增益放大器转化为合适的控制电流。

4)调整输出:通过调整管控制电压降低输出电压,根据误差放大器的输出信号控制调整管的导通程度。

5)输出稳定:当输出电压与参考电压之间的误差达到最小时,误差放大器输出信号也达到最小,调整管基本不导通,输出电压稳定在目标电压处。

3.应用:LDO的应用广泛,特别是在需要稳定的电源电压方面。

其主要应用包括以下几个方面:-电子设备中的电源稳压:如智能手机、平板电脑、电视机等。

-通信系统:如无线基站、通信设备、路由器等。

-工业自动化控制系统:如PLC、传感器、机器人等。

-电源管理芯片:作为电源管理芯片的一部分,提供稳定的电源电压给其他器件。

ldo的基本原理

ldo的基本原理LDO的基本原理LDO,即低压差线性稳压器(Low Drop Out Linear Regulator)是一种常见的电压稳压器件。

它的基本原理是通过降低输入输出之间的电压差,实现电压稳定输出。

LDO的工作原理相对简单,但它在电子设备中扮演着重要的角色。

一、基本原理LDO的基本原理是通过控制管内功耗来实现电压稳定输出。

简单来说,LDO中的输出端被连接到负载电阻上,输入端连接到电源,通过内部的稳压电路,将输入电压调整为稳定的输出电压,并将稳定的电压提供给负载电阻。

二、内部稳压电路LDO内部的稳压电路通常由参考电压源、误差放大器、功率晶体管和反馈网络组成。

参考电压源提供一个稳定的参考电压,误差放大器将输出电压与参考电压进行比较,产生误差信号。

功率晶体管根据误差信号的大小调整管内的电流,从而控制输出端的电压。

反馈网络用于将输出电压与误差放大器进行连接,形成闭环控制。

三、电压差和负载能力LDO的一个重要指标是电压差,即输入电压和输出电压之间的差值。

电压差越小,LDO的效果越好,因为输出电压更稳定。

一般来说,LDO的电压差在几百毫伏至数伏之间。

另一个重要指标是负载能力,即LDO能够提供的最大负载电流。

负载能力越大,LDO可以连接的负载越重,从而适用范围更广。

四、优点和应用LDO具有以下优点:1. 稳定性高:LDO通过负反馈控制输出电压,使其稳定性高,适用于对电压要求严格的应用场景。

2. 噪声低:LDO内部的稳压电路可以降低输入输出之间的噪声传导,提供更干净的电源。

3. 快速响应:LDO的输出电压变化能够快速响应负载的需求变化,提供稳定的电压输出。

4. 低功耗:LDO内部功耗较低,能够提供高效能力。

基于以上优点,LDO广泛应用于各种电子设备中,如移动通信设备、计算机和工业控制系统等。

在这些应用中,LDO可以提供稳定的电源,确保设备正常运行。

五、注意事项在使用LDO时,需要注意以下几点:1. 输入电压不能超过LDO的额定电压,否则可能导致稳压电路无法正常工作。

LDO工作原理

LDO工作原理

LDO(Low-dropout regulator)是一种线性稳压器件,用来将输入电

压稳定在一个较低且固定的值。

它常用于电路中需要稳定电压供应的地方,例如集成电路的供电、电池电源管理等。

1.输入电压传导:输入电压通过输入引脚进入LDO芯片。

在LDO芯片

内部,通过差分输入放大器将输入电压与参考电压进行比较。

差分输入放

大器会将这两个电压的差异放大,并将结果传送给错误放大器。

2.参考电压示波:参考电压通常由一个稳定的电阻网络产生,它是一

个内部设定的固定电压。

错误放大器会将输入电压与参考电压的差异放大,并将结果传递给一个控制放大器。

3.控制放大器调节:控制放大器中包含一个开环比较器和一个反馈电路,它负责将错误电压信号与开环参考电压进行比较。

比较结果决定了LDO的工作状态。

4.输出调整:根据比较结果,控制放大器会调整输出电压以使错误电

压趋于零。

输出电压通过一个功率放大器输出,并通过输出引脚传送到负载。

5.错误补偿:为了提高LDO的稳定性,通常会在负载电路中加入一个

错误补偿电路。

这个电路会根据负载电流的变化来调整输出电压,以保持

稳定的电压输出。

总的来说,LDO的工作原理就是通过比较输入电压和内部设定的参考

电压的差异,并通过控制放大器调整输出电压来使其稳定。

通过这种方式,LDO供应电路能够在输入电压变化较大的情况下提供稳定的电压输出。

在

实际应用中,需要根据具体的需求选择合适的LDO型号,以满足不同负载和输入电压条件下的稳定性要求。

ldo的工作原理

ldo的工作原理

LDO(Low Dropout)稳压器是一种常见的线性稳压器件,其工作原理如下:

1. 输入电压:LDO稳压器的输入电压为高于输出电压的直流电源电压。

例如,如果需要将输出电压稳定在3.3V,输入电压可以是3.7V以上的电源。

2. 参考电压:LDO稳压器内部有一个参考电压源,通常为固定的电压值。

这个参考电压用来和输出电压进行比较,以调整输出电压的稳定性。

3. 快速反馈环路:LDO稳压器有一个快速反馈环路,用来监测输出电压的变化情况并作出相应调整。

当输出电压发生波动时,快速反馈环路会迅速调整内部的控制元件,以使输出电压保持稳定。

4. 控制元件:LDO稳压器内部有一个控制元件(通常是一个PNP晶体管),用来调整电流流过稳压器的路径,从而实现输出电压的稳定。

5. 差分放大器:控制元件的控制信号由一个差分放大器提供。

差分放大器比较输出电压与参考电压的差异,并根据比较结果驱动控制元件进行调整,以使输出电压保持在预定的稳定值。

6. 调整电阻:有些LDO稳压器还包括一个调整电阻,用来调整输出电压的精确值。

通过改变调整电阻的阻值,可以微调输

出电压的大小。

综上所述,LDO稳压器通过控制元件和差分放大器实现输出电压的稳定。

它具有输入输出电压差小、纹波较小、温漂小等特点,广泛应用于各种电子设备中。

LDO工作原理详细

LDO工作原理详细LDO(Low-Dropout Regulator)是一种常用的线性稳压器件,用于将输入电压稳定地调整为目标输出电压。

LDO通常用于需要稳定电压的电子设备中,比如移动手机、电脑、无线通信设备等。

LDO的工作原理相对简单,主要包括三个部分:传感器、误差放大器和功率级。

传感器用于感测输出电压,将其与参考电压进行比较,得到误差信号。

误差放大器将误差信号放大,并将放大的误差信号与传感器反馈回路相关联。

功率级则通过放大的误差信号来控制输出电压。

具体来说,LDO首先会进行开环操作,也就是忽略反馈回路的影响。

在开环操作中,传感器将输出电压与参考电压进行比较,并将误差信号传递给误差放大器。

误差放大器将误差信号放大,并将其传递给功率级。

功率级根据放大的误差信号来调整输出电压,使其接近参考电压。

然后,在闭环操作中,反馈回路开始发挥作用。

误差放大器和功率级之间会建立一个反馈回路,在回路中添加一个电流源。

根据误差放大器的输出,电流源会增加或减少电流,从而更改功率级的输出。

理想情况下,误差放大器的输出为零,此时输出电压与参考电压相等。

然而,由于误差放大器和功率级的非线性特性,以及外部环境的干扰,实际的输出电压可能存在一定的偏差。

为了减小这种偏差,LDO通常会采用负反馈调节机制。

也就是说,在输出电压调整到预设值之后,误差放大器会通过反馈回路对功率级进行调节,以减小输出偏差。

LDO的核心是功率级,其在负载变化和输入电压变化时都能保持较为稳定的输出电压。

通常,功率级采用两个三极管结构组成的差分放大器。

差分放大器利用PNP和NPN三极管分别进行增益和调整,实现对输出电压的精确控制。

总之,LDO通过传感器感测输出电压的偏差,并通过误差放大器和功率级对偏差进行调整,以达到稳压的目的。

LDO具有工作原理简单、输出电压稳定性高等优点,广泛应用于各种需要稳定电压的电子设备中。

LDO的工作原理详细分析

LDO的工作原理详细分析LDO是指低压差线性稳压器(Low Drop Out Linear Regulator),它的工作原理是将输入电压通过内部的调节电路进行相应的调整,使得输出电压保持在设定的恒定值。

LDO的主要作用是稳定供电电压,提供稳定可靠的电压源。

1.调节阶段:调节阶段主要包括一个误差放大器和一个反馈网络。

误差放大器将参考电压与输出电压进行比较,得到误差信号,并将此信号通过反馈网络传递给功率晶体管。

反馈网络通常由电阻和电容构成,通过调整反馈信号的大小来控制功率晶体管的导通程度,从而调整输出电压的稳定性。

当误差信号超过设定的误差阈值时,反馈网络会调节功率晶体管的导通程度,使得输出电压继续保持在设定值。

2.放大器阶段:放大器阶段主要包括一个功率晶体管和一个输出电容。

当输入电压经过调节阶段后,会被功率晶体管进行放大,然后通过输出电容进行滤波,使得输出电压更加稳定。

功率晶体管的导通程度由反馈网络控制,通过调节反馈网络的电阻和电容值,可以改变功率晶体管的工作状态,从而调整输出电压的稳定度。

LDO相较于普通线性稳压器的特点之一是具有更低的压差(Drop Out Voltage),即输入电压与输出电压之间的差值。

LDO通常具有较低的压降,这意味着即使输入电压降低到接近输出电压的水平,LDO仍然可以使输出电压保持在恒定值。

这样可以在低电压条件下提供更稳定的电源。

LDO的工作原理中一个关键的组件是反馈网络。

反馈网络通过采集输出电压并将其与参考电压进行比较,产生误差信号,进而调节功率晶体管的导通程度,最终实现输出电压的稳定。

反馈网络的设计需要考虑电流稳定性、温度稳定性等因素,以确保输出电压能够在各种工作条件下保持恒定。

此外,LDO还需要满足一些性能指标,如负载调整率、线性调整率、噪声抑制等。

负载调整率表示当负载电流发生变化时,输出电压的变化情况。

线性调整率表示当输入电压发生变化时,输出电压的变化情况。

噪声抑制表示LDO能够有效抑制输入端的噪声传递到输出端,提供更加稳定的电源。

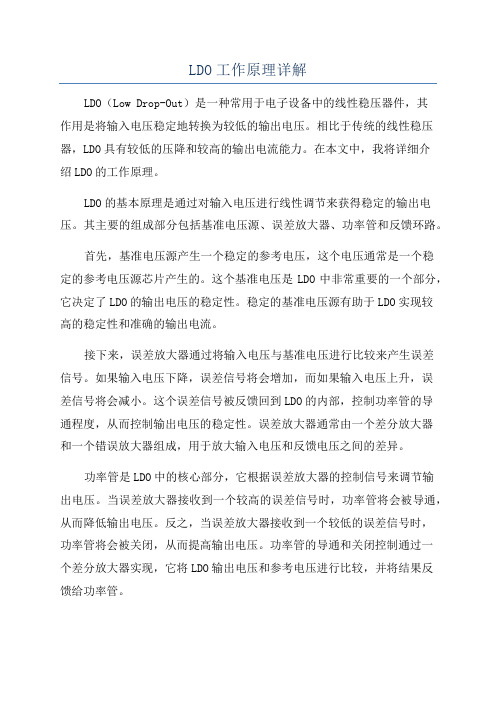

LDO工作原理详解

LDO工作原理详解LDO(Low Drop-Out)是一种常用于电子设备中的线性稳压器件,其作用是将输入电压稳定地转换为较低的输出电压。

相比于传统的线性稳压器,LDO具有较低的压降和较高的输出电流能力。

在本文中,我将详细介绍LDO的工作原理。

LDO的基本原理是通过对输入电压进行线性调节来获得稳定的输出电压。

其主要的组成部分包括基准电压源、误差放大器、功率管和反馈环路。

首先,基准电压源产生一个稳定的参考电压,这个电压通常是一个稳定的参考电压源芯片产生的。

这个基准电压是LDO中非常重要的一个部分,它决定了LDO的输出电压的稳定性。

稳定的基准电压源有助于LDO实现较高的稳定性和准确的输出电流。

接下来,误差放大器通过将输入电压与基准电压进行比较来产生误差信号。

如果输入电压下降,误差信号将会增加,而如果输入电压上升,误差信号将会减小。

这个误差信号被反馈回到LDO的内部,控制功率管的导通程度,从而控制输出电压的稳定性。

误差放大器通常由一个差分放大器和一个错误放大器组成,用于放大输入电压和反馈电压之间的差异。

功率管是LDO中的核心部分,它根据误差放大器的控制信号来调节输出电压。

当误差放大器接收到一个较高的误差信号时,功率管将会被导通,从而降低输出电压。

反之,当误差放大器接收到一个较低的误差信号时,功率管将会被关闭,从而提高输出电压。

功率管的导通和关闭控制通过一个差分放大器实现,它将LDO输出电压和参考电压进行比较,并将结果反馈给功率管。

最后,反馈环路用于将输出电压信号反馈回误差放大器,以保持稳定的输出电压。

当输出电压偏离参考电压时,反馈环路将会对误差放大器产生一个调节信号,从而调节功率管的导通程度,使输出电压恢复到设定值。

总结起来,LDO通过基准电压源、误差放大器、功率管和反馈环路的配合工作来实现输入电压的稳定转换为较低的输出电压。

基准电压源产生一个稳定的参考电压,误差放大器将输入电压和参考电压进行比较,功率管根据误差放大器的控制信号调节输出电压,反馈环路用于保持输出电压的稳定性。

LDO原理介绍

LDO原理介绍LDO(Low Dropout)是一种用于稳定输出电压的线性稳压器。

它主要用于在电源电压波动或负载变化时稳定输出电压。

LDO的工作原理是将输入电压通过调节管调节,并将其稳定在预设的输出电压。

LDO通常由三个关键组件构成:参考电压源、误差放大器和调节管。

首先,参考电压源提供参考电压给误差放大器。

这个参考电压一般设计为固定值,如1.2V或2.5V,用于与输入电压进行比较。

误差放大器的作用是将参考电压与实际输出电压之间的差异进行放大,并将其转换为驱动调节管的控制信号。

当误差放大器检测到输出电压低于设定值时,它会增大输出信号,从而驱动调节管提供更多的电流。

当输出电压高于设定值时,它会减小输出信号,从而驱动调节管提供更少的电流。

通过这种反馈机制,LDO能够实现稳定的输出电压。

调节管是LDO的最重要组成部分。

它是一种具有低压降的高功率晶体管,它能够提供稳定的输出电流。

调节管的主要作用是根据误差放大器的控制信号来调节电流大小,以保持输出电压稳定。

LDO的工作原理可以分为三个阶段:起始阶段、稳压阶段和负载变化阶段。

在起始阶段,输入电压被应用于LDO电路。

当电路开始工作时,调节管处于关闭状态,此时输出电压等于输入电压减去调节管的压降。

在稳压阶段,输入电压被调节管稳定在输出电压以上。

这是通过误差放大器对输出电压进行监测,并通过调节管的控制信号来调整电流大小,以保持输出电压在设定值范围内。

在负载变化阶段,当负载的电流产生变化时,LDO需要快速响应以保持输出电压的稳定。

这是通过误差放大器的控制信号来调节调节管的电流来实现的。

当负载电流增加时,误差放大器会增大调节管的控制信号,从而增加输出电流。

相反,当负载电流减少时,误差放大器会减小调节管的控制信号,从而减小输出电流。

通过这种方式,LDO能够快速响应负载变化,从而保持输出电压的稳定。

总结起来,LDO是一种通过误差放大器控制调节管电流的线性稳压器。

它通过反馈机制,实现对输出电压的稳定,无论在电源电压波动还是负载变化的情况下。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

用分立元件搭的LDO

误差放大

调整元件

基准电压 取样电路

工作 原理

• 电路开始启动,恒流源电路给整个电路提供偏置,基准源电 压快速建立

• 输出随着输入不断上升,输出达到规定值 • 误差放大器将输出反馈电压和基准电压之间的误差小信号进

行放大,再经调整管放大到输出,从而形成负反馈,保证了 输出电压稳定 • 输入电压变化或输出电流变化,这个闭环回路将使输出电压 保持不变

电源小2——3V(轨到轨运放输 出电压可接近电源电压)

2输.运出VD放电S=带流1.负1520载V几能毫力安很,弱大,的一也般就 100m1A.7左8V右,而且贵

+1+.18.V8V_L_LDDOO

取样电路

可以看成一个带负 载能力很强(输出 大电流)的运放

取样后接入负 端形成负反馈

共漏放大

g Vi

带启动电路的自偏置

电路开始上电,由于上半部分镜 像电流源处于零电流状态,节 点1处于高电位,同样下半部分 也处于零电流状态,节点3处于 低电位,MP1导通,2节点电位 被拉高,MN1导通,这样节点1 被拉低,说明镜像电流源中的 管子导通,有电流流过偏置

电路,电流持续上升,当到达工作点B时,节点3被拉 高,将MP1关断,节点2电位下降,直到MN1关断, 这样启动电路完全脱离偏置电路,偏置电路稳定的工 作在工作点B处。

电流(提供给误差放大器、基准电压源和采样电 阻)与调整管的驱动电流组成,可以表示为

IQ=Iin-Io

对于双级型晶体管,静态 电流随着负载电流成比例 的增加,因为双级型晶体 管是电流驱动器件

对于MOS管,静态电流很 小,几乎不随负载的变化 而变化,几乎是一个恒定 值,因为MOS管是电压驱 动器件

PNP LDO的地脚电流会比较高。在 满载时,PNP管的β值一般是15~20。 也就是说LDO的地脚电流一般达到负 载电流的7% 。达林管和准LDO的静 态电流较小。在应用中如果对静态电

VOUT=(R1+R2)/R2 * Vref

集成LDO结构图

齐纳二极管或 带隙基准源

传统线性稳压 器调整管

达林顿管 PNP管 PMOS NMOS

实际电路比原理框图多 了启动电路和保护电路

过流保护

热保护

一些复杂的LDO还会 加过压保护、欠压保 护、反接保护等

基准电压源

• 对输出电压影响最大 • 稳定性好,低温漂,高精度,内阻小 • 带隙基准电压源

线性电源

开关电源

• 优点 外围器件少,PCB面 积小,花费少 无开关噪声,纹波小

• 缺点 降压输出 效率低,功耗大

优点 可升压、可降压 效率高,功耗小

缺点 设计更复杂,外围器 件多,花费也较高 输出纹波大

线性稳压器原理框图

+

调整元件

Ui

误差放大

取

负

UL

-

基准电压

样

载

• 调整元件 • 基准电压源 • 误差放大器 • 反馈网络(取样电路)

2.6V

P2

2P.45V

P1

P5

2.4V

VGS=2.3V

1.2 1.6 2.0 VDS/V

3. 反馈电压降低,放大器输出(VG)增大

4. 共源放大,0<AV<1。VS(VO)增大,VGS 增大,VDS减小,ID增大。工作点移到P3

5. VF与VREF之差趋于0,个系统恢复了平

LDO频率补偿

• 所有稳压器都使用反馈回路(Feedback Loop)以保持输出电压的稳定。 反馈信号 在通过回路后都会在增益和相位上有所改变 ,通过在单位增益(Unity Gain,0dB)频 率下的相位偏移总量来确定回路的稳定性。

调整管

• LDO 稳压器(LDO regulators)

在LDO(Low Dropout)稳压器中,导通管是一个 PNP管。LDO的最大优势就是PNP管只会带来 很小的导通压降,满载的 跌落电压的典型值小于 500mV,轻载时的压降 仅有10~20mV。LDO 的压差为: Vdrop = Vsat

带 隙 基 准 原 理 图

VREF

n

R2 R1

ln m VT

VEB3

误差放大器

• 误差放大一般采 用三级结构,与 集成运放相似

• 差分输入级提电 路共模抑制比,并且输入电阻很大

• 电压放大级进一步提高电路增益 • 输出级一般除了提高电路增益外,最主要的作

用是提高输出摆幅,最大可能的减小输出电阻 • 偏置电路为电路的三部分提供合适的静态工作

VREF VBE KVT

K=2.2/0.085=23.5,在 理论实现零温度系数

VREF 0.65 0.026 23.5 1.26V

由于该电压等于硅的带隙电压(外推到绝对温度), 所以这类基准电路也叫“带隙”基准电路。

注:实际上利用的不是带隙电压,有些Bandgap结构输出电压与带隙电压也不一致

Vin Vout Vin

Q1 Vin+

Cin

Vin-

L1 Vin+

Cin

VinVin+

Cin Vin-

Q1 D1

L1 D1

V o ut + Cout

D1 Q1

V o ut V o ut + Cout

V o ut -

L1

D1Βιβλιοθήκη V o ut +Q2

Cout

V o ut -

线性电源、开关电源 哪个更好??

德州仪器(TI)电压差定义为输 出电压较其标称值跌落2%的输 入、输出电压的差值.其它的如, 美信(Maxim),圣邦微电子 (SGMC)电压差定义为输出电压 较其标称值小于100mV时的输 入、输出电压的差值

静态电流

• 静态电流定义为输入输出电流之差,它反映了 LDO内部电路的功率消耗,静态电流主要由偏置

Charge pump (inductor less DC-DC) DC-DC (inductor)

Charge pump(电荷泵)

• 原理

VIN

Cin

SHDN

CONTROL / CLOCK

S1

S3

S2

S4

GND

C+

Cfly

CVOUT

Cout

倍压电荷泵示意图 (Vout = 2 x Vin)

倍压电荷泵

注意:一个极点只能增加- 90°的相移,所以最少需 要两个极点来到达-180° (不稳定点)。

零点(ZEROS)

• 零点(Zero)定义为在增益曲线中斜度为+ 20dB/十倍频程的点。零点产生的相移为0到 +90°,在曲线上有+45°角的转变。必须 清楚零点就是“反极点”

(Anti-pole),它在增益 和相位上的效果与极点 恰恰相反。在LDO稳压 器的回路中添加零点可 以抵消极点。

id VDD

d

s

R

VO

Vi Vo

Vg Vo ↓

取样后接入正 端形成负反馈

调整管工作原理

ID/mA

400

3.0V 2.9V

P3 2.7V

300

2.8V

200

1.LDO正常工作在点P1

2. 负载电阻降低,输出电流增大, 输出电压Vo降低,VGS增大,VDS 增大,工作点移动到P2

100

0 0

0.4 0.8

点偏置。

调整管

• NPN 稳压器(NPN regulators) 在NPN稳压器的内部使用一个 PNP管来驱动 NPN 达林顿管(NPN Darlington pass transistor),输入输 出之间存在至少1.5V~ 2.5V的压差(dropout voltage)。这个压差为: Vdrop = 2Vbe +Vsat

LDO频率响应

1

f p1 2 ROCO

1

f 2 R C fp3

1

2 Rpoa2Cpar

ESR b

fz

1

2 RESRCO

LDO主要参数

• 压差 • 静态电流 • 待机电流 • 瞬态响应 • 线性调整率 • 负载调整率 • 电源抑制比 • 精度 • 功耗

压差

• 压差是LDO线性稳压器最重要的参数,它是指系 统能够调节地,使输出稳定在期望输出的最小输 入电压和输出电压值差,也就是说这个输入电压 将是系统能够调整地最小输入电压,比这更小的 电压,输入与输出将成线性关系下降,这一临界 输入电压值去期望输出值所得的结果,就是LD O线性稳压器的压差电压。

流的消耗比较苛刻的话,最好是采用 MOS管作为调整管的LDO

待机电流

• 待机电流是指带有使能信号的LDO,当该 信号关闭的时候LDO消耗的电流。参考电 压和误差放大器同样也处于不供电的状态 。可以进一步减小功耗。

PMOS的漏端与负载并联使得输出端是一个 高阻抗节点,LDO的输出阻抗大且受负载电 阻影响。输出端会给系统引入一个位于低频 段的极点,为系统的稳定性带来影响。

分立元件搭的LDO

LDO工作原理

基准电压

误加差三放极大管或MOS 起扩流作用

4.24V

VGS=2.46V

为什么不直接使用运放?

1.一般的调运放整输元出电件压比电源

• 引入反馈的电路必须考虑回路稳定性问题。 负反馈越深,也容易自激振荡。为了提高放 大器在深度负反馈条件下的工作稳定性,一 般采用的消振方法为频率补偿(相位补偿)

极点(POLES)

• 极点(Pole)定义为增益曲线(Gain curve)中斜度 (Slope)为-20dB/十倍频程的点(图9:波特 图中的极点)。每添加一个极点,斜度增加20dB/ 十倍频程。增加n个极点,n ×(-20dB/十倍频 程)。每个极点表示的相位偏移都与频率相关, 相移从0到-90°(增加极点就增加相移)。最 重要的一点是几乎所有由极点(或零点)引起的 相移都是在十倍频程范围内。