简易交通灯控制电路.pptx

合集下载

《交通信号灯控制》课件

交通信号灯控制技术的现状及趋势

05

交通信号灯控制应用案例

城市交通信号灯控制应用案例

城市交通信号灯控制系统的组成和功能

城市交通信号灯控制系统的运行原理和流程

城市交通信号灯控制系统的应用场景和案例分析

城市交通信号灯控制系统的优缺点和未来发展趋势

高速公路交通信号灯控制应用案例

案例背景:介绍高速公路交通信号灯控制的重要性,以及应用案例的背景和目的。

未来发展方向:推广智能交通信号灯控制系统,实现城市交通的智能化和自动化管理

07

总结与展望

对交通信号灯控制的总结

交通信号灯控制的重要性

交通信号灯控制的应用现状

交通信号灯控制的前景展望

交通信号灯控制的发展历程

对未来交通信号灯控制的展望

智能化控制:利用人工智能技术,实现交通信号灯的智能调度,提高道路通行效率。

案例描述:详细描述高速公路交通信号灯控制应用案例的具体情况,包括信号灯的布局、控制方式、运行规则等。

案例分析:对高速公路交通信号灯控制应用案例进行分析,包括对交通流量的影响、对交通安全性的提升等方面的评估。

案例总结:总结高速公路交通信号灯控制应用案例的经验和教训,提出改进和优化的建议。

06

交通信号灯控制存在的问题及解决方案

交通信号灯控制意义:保障交通安全,提高交通效率,减少交通事故的发生

04

交通信号灯控制技术

交通信号灯控制技术的发展历程

交通信号灯的智能化发展

交通信号灯的起源

交通信号灯的发展阶段

交通信号灯的未来趋势

交通信号灯控制技术的现状 - 城市交通信号灯控制系统:采用智能交通系统(ITS)技术,实现城市交通信号灯的智能化控制,提高交通运行效率。 - 农村交通信号灯控制系统:采用太阳能供电技术,实现农村交通信号灯的远程控制,提高农村交通安全水平。 - 城市交通信号灯控制系统:采用智能交通系统(ITS)技术,实现城市交通信号灯的智能化控制,提高交通运行效率。- 农村交通信号灯控制系统:采用太阳能供电技术,实现农村交通信号灯的远程控制,提高农村交通安全水平。交通信号灯控制技术的趋势 - 智能化控制:采用人工智能技术,实现交通信号灯的智能调度,提高城市交通运行效率。 - 绿色环保:采用太阳能、风能等可再生能源,实现交通信号灯的绿色环保供电。 - 远程控制:采用物联网技术,实现交通信号灯的远程控制,提高交通管理效率。- 智能化控制:采用人工智能技术,实现交通信号灯的智能调度,提高城市交通运行效率。- 绿色环保:采用太阳能、风能等可再生能源,实现交通信号灯的绿色环保供电。- 远程控制:采用物联网技术,实现交通信号灯的远程控制,提高交通管理效率。

05

交通信号灯控制应用案例

城市交通信号灯控制应用案例

城市交通信号灯控制系统的组成和功能

城市交通信号灯控制系统的运行原理和流程

城市交通信号灯控制系统的应用场景和案例分析

城市交通信号灯控制系统的优缺点和未来发展趋势

高速公路交通信号灯控制应用案例

案例背景:介绍高速公路交通信号灯控制的重要性,以及应用案例的背景和目的。

未来发展方向:推广智能交通信号灯控制系统,实现城市交通的智能化和自动化管理

07

总结与展望

对交通信号灯控制的总结

交通信号灯控制的重要性

交通信号灯控制的应用现状

交通信号灯控制的前景展望

交通信号灯控制的发展历程

对未来交通信号灯控制的展望

智能化控制:利用人工智能技术,实现交通信号灯的智能调度,提高道路通行效率。

案例描述:详细描述高速公路交通信号灯控制应用案例的具体情况,包括信号灯的布局、控制方式、运行规则等。

案例分析:对高速公路交通信号灯控制应用案例进行分析,包括对交通流量的影响、对交通安全性的提升等方面的评估。

案例总结:总结高速公路交通信号灯控制应用案例的经验和教训,提出改进和优化的建议。

06

交通信号灯控制存在的问题及解决方案

交通信号灯控制意义:保障交通安全,提高交通效率,减少交通事故的发生

04

交通信号灯控制技术

交通信号灯控制技术的发展历程

交通信号灯的智能化发展

交通信号灯的起源

交通信号灯的发展阶段

交通信号灯的未来趋势

交通信号灯控制技术的现状 - 城市交通信号灯控制系统:采用智能交通系统(ITS)技术,实现城市交通信号灯的智能化控制,提高交通运行效率。 - 农村交通信号灯控制系统:采用太阳能供电技术,实现农村交通信号灯的远程控制,提高农村交通安全水平。 - 城市交通信号灯控制系统:采用智能交通系统(ITS)技术,实现城市交通信号灯的智能化控制,提高交通运行效率。- 农村交通信号灯控制系统:采用太阳能供电技术,实现农村交通信号灯的远程控制,提高农村交通安全水平。交通信号灯控制技术的趋势 - 智能化控制:采用人工智能技术,实现交通信号灯的智能调度,提高城市交通运行效率。 - 绿色环保:采用太阳能、风能等可再生能源,实现交通信号灯的绿色环保供电。 - 远程控制:采用物联网技术,实现交通信号灯的远程控制,提高交通管理效率。- 智能化控制:采用人工智能技术,实现交通信号灯的智能调度,提高城市交通运行效率。- 绿色环保:采用太阳能、风能等可再生能源,实现交通信号灯的绿色环保供电。- 远程控制:采用物联网技术,实现交通信号灯的远程控制,提高交通管理效率。

简易的十字路口交通信号灯控制电路

卜 字路 口交通信号灯简介

十字 路 口一般 有 两条 交叉 的道 路,这 两 } 路 有 主 次 之 分 。其 中有 一 条 车流 量 很 大 , 为 主 干 道 ;另 一 条 车 流 量 较 小 , 被 称 为 次 } 。

在 主 干 道 和 次 干 道 的 交 叉 路 口,每 一边 都 } 置相 应的交通信号灯 。 交通信 号灯分为 红、 黄三种颜色 ,红灯表示禁止车辆通 行;黄 示 交 叉 路 口停 车 线 以外 的车 辆 禁 止 通 行 , 路 口停车线 以内的车辆可快速通过 :绿灯 示允许车辆通行。

上 文 已述 ,十字 路 口主干 道 红黄 绿灯 亮 的时间是 2 4秒 、4秒和 2 8 秒 ,其 比例是 6 :1 : 7 ;次干道 红黄绿灯亮 的时间是 3 2秒 、4秒 和 2 0秒, 比例 是 8 :1 :5 。按照 比例,可 以以 4 秒作为~个时间单位 ,采用分频器实现 。

道 的交 通 信 号 灯 在 具 体 的状 态 控 制 过 程 中 , 可 以用译码器来完成 ,并使用 计数器实现这 种变 化。 6 . 3倒 计 时 的 设 计 及 显 示

交通 信号 灯在 由绿 灯转 变成 为红 灯 的过 程 中,需要经过黄灯 。主干道 红灯 亮的时间等 于次干道绿灯加黄灯亮 的时间总和 。计数器的 初始值是一个变量 ,通过减法计数器 能实现 信 号 灯 的 切 换 过 程 。上 下 班 的高 峰期 是 一个 特 殊 阶段,在交通堵塞 的情况下可 以适 当改变 一条 道 路 的 通 行 时 间 ,具 体 方 法 是 增 加 减 法 计数 器

5 . 2控 制 器

控 制 器 是 电路 的 关 键 部 分 。 经 过 计 算 , 主干道和次干道交通信号灯 的工作循环周 期是 1 4个时 间单位 ,在 这里可 以采用 1 4进制计 数 器,如扭环形计数器等。

《交通灯控制器》PPT课件

东西黄灯 南北红灯

N

计时5s

Y

东西红灯 南北绿灯

N 计时60s

Y

东西红灯 南北黄灯

N

Y

计时5s

精选PPT

18

▪

结束

精选PPT

19

系统中要求有45s,60s,5s三种定时信号,定时起始 信号由主控制电路给出,定时时间结束信号也输 入到主控制电路,并通过主控制电路去开起或关 闭三色交通灯。

主控制电路实本题的核心,它的输入信号来自三

个定时信号。

精选PPT

3

东西方向 红黄绿

南北方向 红黄绿

显

译码驱动电路

示 驱

动

电

主控电路

路

45s定时

精选PPT

12

复位电路

▪ 复位电路通常采用上电自动复位和按钮复位两种方 式,此电路系统采用的是上电与按钮复位电路。

▪ 复位后P0-P3口 均置1引脚表现为 高电平,程序计 数器和特殊功能 寄存器SFR全部 清零

精选PPT

13

计时显示

分段式显示器(LED数码管)由7条线段围成8字型,每一段 包含一个发光二极管。外加正向电压时二极管导通,发出清

COQ3 Q2 Q1 Q0 CTp

1

74LS163

CTt

CR D3 D2 D1 D0

CP

精选PPT

7

返回

控制器

控制器是交通管理的核心,它能够按照交通管理规则控制信号灯 工作状态的转换。

TX=5s,TL=45s,TY=60s,

选用两个D触发器FF1、FF0

为时序寄存器产生 4种状态,

控制器状态转换的条件为

18 ARDY 16 ~ASTB 21 BRDY 17 ~BSTB

N

计时5s

Y

东西红灯 南北绿灯

N 计时60s

Y

东西红灯 南北黄灯

N

Y

计时5s

精选PPT

18

▪

结束

精选PPT

19

系统中要求有45s,60s,5s三种定时信号,定时起始 信号由主控制电路给出,定时时间结束信号也输 入到主控制电路,并通过主控制电路去开起或关 闭三色交通灯。

主控制电路实本题的核心,它的输入信号来自三

个定时信号。

精选PPT

3

东西方向 红黄绿

南北方向 红黄绿

显

译码驱动电路

示 驱

动

电

主控电路

路

45s定时

精选PPT

12

复位电路

▪ 复位电路通常采用上电自动复位和按钮复位两种方 式,此电路系统采用的是上电与按钮复位电路。

▪ 复位后P0-P3口 均置1引脚表现为 高电平,程序计 数器和特殊功能 寄存器SFR全部 清零

精选PPT

13

计时显示

分段式显示器(LED数码管)由7条线段围成8字型,每一段 包含一个发光二极管。外加正向电压时二极管导通,发出清

COQ3 Q2 Q1 Q0 CTp

1

74LS163

CTt

CR D3 D2 D1 D0

CP

精选PPT

7

返回

控制器

控制器是交通管理的核心,它能够按照交通管理规则控制信号灯 工作状态的转换。

TX=5s,TL=45s,TY=60s,

选用两个D触发器FF1、FF0

为时序寄存器产生 4种状态,

控制器状态转换的条件为

18 ARDY 16 ~ASTB 21 BRDY 17 ~BSTB

十字路口交通灯PLC控制系统课件

块。

逻辑算法

根据交通规则和控制要求,设计红 、绿、黄灯的逻辑切换算法,确保 交通流畅且安全。

程序实现

使用PLC编程语言(如Ladder Logic、Structured Text等)编写 控制程序,并进行仿真测试和调试 。

人机交互界面的设计与实现

01

02

03

界面设计

设计易于操作的人机交互 界面,包括主界面、参数 设置界面和故障诊断界面 。

PLC的CPU根据预设的程序对 输入信号进行处理,输出控制 信号。Fra bibliotek反馈调节

根据实际交通情况,通过编程 调整控制逻辑,实现交通灯的 自动调节。

交通灯PLC控制系统的编程语言与实现方式

编程语言

常用的PLC编程语言有Ladder Logic(梯形图)、Structured Text(结构化文 本)、Function Block Diagram(功能块图)等。

交通灯PLC控制系统的重要性在于能 够实现智能化、自动化的交通管理, 提高城市交通运行效率,保障交通安 全。

交通灯PLC控制系统的历史与发展

早期的交通灯控制系统采用机械式控制方式,随着技术的发展,逐渐被电子式控制 系统取代。

PLC技术的出现使得交通灯控制系统的可靠性和稳定性得到了极大的提高,目前已 经成为城市交通信号控制的主流技术。

输入模块

接收来自现场的各种输入信号, 如按钮、传感器等。

存储器

存储程序和数据。

外设

如键盘、显示器等。

交通灯PLC控制系统的信号处理流程

信号输入

将采集的信号输入到PLC的输 入模块。

信号输出

控制信号通过PLC的输出模块 输出,控制交通灯的亮灭。

信号采集

通过传感器检测路口的车流量 、人流量等信息。

逻辑算法

根据交通规则和控制要求,设计红 、绿、黄灯的逻辑切换算法,确保 交通流畅且安全。

程序实现

使用PLC编程语言(如Ladder Logic、Structured Text等)编写 控制程序,并进行仿真测试和调试 。

人机交互界面的设计与实现

01

02

03

界面设计

设计易于操作的人机交互 界面,包括主界面、参数 设置界面和故障诊断界面 。

PLC的CPU根据预设的程序对 输入信号进行处理,输出控制 信号。Fra bibliotek反馈调节

根据实际交通情况,通过编程 调整控制逻辑,实现交通灯的 自动调节。

交通灯PLC控制系统的编程语言与实现方式

编程语言

常用的PLC编程语言有Ladder Logic(梯形图)、Structured Text(结构化文 本)、Function Block Diagram(功能块图)等。

交通灯PLC控制系统的重要性在于能 够实现智能化、自动化的交通管理, 提高城市交通运行效率,保障交通安 全。

交通灯PLC控制系统的历史与发展

早期的交通灯控制系统采用机械式控制方式,随着技术的发展,逐渐被电子式控制 系统取代。

PLC技术的出现使得交通灯控制系统的可靠性和稳定性得到了极大的提高,目前已 经成为城市交通信号控制的主流技术。

输入模块

接收来自现场的各种输入信号, 如按钮、传感器等。

存储器

存储程序和数据。

外设

如键盘、显示器等。

交通灯PLC控制系统的信号处理流程

信号输入

将采集的信号输入到PLC的输 入模块。

信号输出

控制信号通过PLC的输出模块 输出,控制交通灯的亮灭。

信号采集

通过传感器检测路口的车流量 、人流量等信息。

交通红绿灯控制器的设计与制作课件

红灯 绿灯 黄灯

红灯 绿灯 黄灯

3、1.电源电路 电源电路设计的任务主要有:

• 1)完成电路的设计的任务。 • 2)完成原理图、PCB板图的绘制。 • 3)常见元件的识别与测量如:变压器、二

极体、三极管识别与测量,如: 1N4007,4700UF/50V、7805集成芯片等。 • 4)完成PCB板子的设计与制作工作: • 5)完成元件的焊接工作 • 2)完成硬件电路的调试工作

4.单片机最小系统

• 单片机最小系统主要由单片机、晶振及复 位电路组成。

• 单片机采用stc89c52单片机、晶振12Mhz、 复位电路由电阻电容构成。

引导问题:

• 1、设计制作前所需要进行的准备内容? • 答:仔细阅读设计文件的要求,确认每一个指标

的含义,认真准备硬件电路 • 2、硬件电路的设计过程? • 答:(1)整体方案的设计,包括控制器的选择、

电路参数的计算如:电源输出功率等; • (2);电源电路的设计 • (3)显示电路的设计; • (4)单片机最小系统的设计; • (5)键盘电路的设计

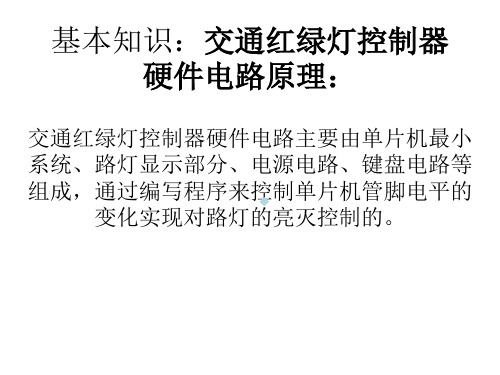

基本知识:交通红绿灯控制器 硬件电路原理:

交通红绿灯控制器硬件电路主要由单片机最小 系统、路灯显示部分、电源电路、键盘电路等 组成,通过编写程序来控制单片机管脚电平的

变化实现对路灯的亮灭控制的。

交通红绿灯控制器硬件电路图:

VCC

P10 P11 P12 P13

STC 89c52

P2

红灯 绿灯 黄灯

红灯 绿灯 黄灯

2.键盘控制电路

• 键盘控制电路采用非编码键盘中的独立式 键盘,键盘扫描电路采用中断法设计的。 采用二极管起到线或的作用,只要有按键 按下就产生中断。按键采用8*8;二极管采 用1N4007整流管即可。

交通灯的PLC控制ppt课件

任务决策——交通灯 ON交通灯的时序图

启动 OFF

南北红灯 Y0

东西绿灯 Y1

东西黄灯 Y2

东西红灯 Y3

南北绿灯 Y4

南北黄灯 Y5

时间轴

20s 3s 2s

25s

3s 2s

T0

T1 T2 T3

T4 T5 T0

资金是运动的价值,资金的价值是随 时间变 化而变 化的, 是时间 的函数 ,随时 间的推 移而增 值,其 增值的 这部分 资金就 是原有 资金的 时间价 值

任务资讯——上节回顾

图1-2 振荡电路的梯形图及输出时序图

资金是运动的价值,资金的价值是随 时间变 化而变 化的, 是时间 的函数 ,随时 间的推 移而增 值,其 增值的 这部分 资金就 是原有 资金的 时间价 值

任务分析——引例

喷泉控制设计:

有A、B、C三组喷头,要求启动后A先 喷5秒,之后B、C同时喷,5秒后B停止, 再过5秒,C停止。而A、B同时喷,再过2 秒,C也喷,A、B、C同时喷5秒后全部停 止。再过3秒,重复前面过程,当按下停 止按钮后,马上停止。试写出控制程序。

1.PLC安装连线

2.编程软件的应用

二

技能 3.定时器指令的应用

4.程序的下载与调试

5.电气设备的正确操作

1.学生的沟通能力及团队协作精神 三 职业素养 2.良好的职业道德

3.质量、成本、安全、环保意识

资金是运动的价值,资金的价值是随 时间变 化而变 化的, 是时间 的函数 ,随时 间的推 移而增 值,其 增值的 这部分 资金就 是原有 资金的 时间价 值

任务决策——交通灯 用经验法写出交通灯的控制程序

资金是运动的价值,资金的价值是随 时间变 化而变 化的, 是时间 的函数 ,随时 间的推 移而增 值,其 增值的 这部分 资金就 是原有 资金的 时间价 值

启动 OFF

南北红灯 Y0

东西绿灯 Y1

东西黄灯 Y2

东西红灯 Y3

南北绿灯 Y4

南北黄灯 Y5

时间轴

20s 3s 2s

25s

3s 2s

T0

T1 T2 T3

T4 T5 T0

资金是运动的价值,资金的价值是随 时间变 化而变 化的, 是时间 的函数 ,随时 间的推 移而增 值,其 增值的 这部分 资金就 是原有 资金的 时间价 值

任务资讯——上节回顾

图1-2 振荡电路的梯形图及输出时序图

资金是运动的价值,资金的价值是随 时间变 化而变 化的, 是时间 的函数 ,随时 间的推 移而增 值,其 增值的 这部分 资金就 是原有 资金的 时间价 值

任务分析——引例

喷泉控制设计:

有A、B、C三组喷头,要求启动后A先 喷5秒,之后B、C同时喷,5秒后B停止, 再过5秒,C停止。而A、B同时喷,再过2 秒,C也喷,A、B、C同时喷5秒后全部停 止。再过3秒,重复前面过程,当按下停 止按钮后,马上停止。试写出控制程序。

1.PLC安装连线

2.编程软件的应用

二

技能 3.定时器指令的应用

4.程序的下载与调试

5.电气设备的正确操作

1.学生的沟通能力及团队协作精神 三 职业素养 2.良好的职业道德

3.质量、成本、安全、环保意识

资金是运动的价值,资金的价值是随 时间变 化而变 化的, 是时间 的函数 ,随时 间的推 移而增 值,其 增值的 这部分 资金就 是原有 资金的 时间价 值

任务决策——交通灯 用经验法写出交通灯的控制程序

资金是运动的价值,资金的价值是随 时间变 化而变 化的, 是时间 的函数 ,随时 间的推 移而增 值,其 增值的 这部分 资金就 是原有 资金的 时间价 值

实验五交通灯控制-40页PPT资料

➢ 输出信号

• f1s、f2s:人工控制时A方向、B方向的放行 状态,驱动LED,高电平时点亮;

• s1[2..0]、s2[2..0]:交通灯信号输出,分 别用于控制A方向和B方向的红、黄、绿灯的亮 或灭,驱动LED,高电平时点亮。

14 13.04.2020

设计思路

➢ 根据其功能要求(如正常运行状态下的交通灯 自动转换规律,人工放行功能及限制规则), 确定其输出信号,以便控制两组交通灯的亮或 灭,并在交通岗内向交通警察显示人工放行的 状态。

内容概要

❖ 实验目的 ❖ 实验要求 ❖ 实验原理 ❖ 实验方案 ❖ 实验内容 ❖ 实验报告

1 13.04.2020

实验目的

了解交通红绿灯控制器的工作原理。 掌握建立状态机的逻辑模型的方法。 掌握状态机的实现和多个状态机的组合使用

方法

2 13.04.2020

实验要求

▪ 假定十字路口马路的A方向和B方向各有一 组红、黄、绿三个灯组成的交通灯,要求设 计一个交通红绿灯控制器,实现对这两组交 通灯的管理。正常时,交替放行十字交叉路 的两个方向,放行时间相等;交通堵塞时, 由交通警察人工控制某方向的放行时间,以 便按照交通负荷疏导阻塞车辆。

预习时请画出其状态转移图。

想一想,工作状态控制器为Mealy型状态

机还是Moore型状态机,为什么?

16

13.04.2020

(2)操作规则实现电路 • 功能:根据交通红绿灯控制器的功能要求,确定不

同工作状态下计时器的计数值。可用8位计数器来 实现定时计数。 • 正常运行时,计数器按照规定的定时要求加1计数; 若要人工放行某方向,只要使计时器运行到该放行 状态的最后一刻时,计时器保持此时的计数值,使 红绿灯信号生成器暂停状态的转移即可。

简易交通信号灯控制电路

参考文献

[1]何小艇.电子系统设计[M].杭州:浙江大学出版社,2001年6月

S0(00)东西干道绿,南北干道红东西干道通行,南北干道禁止通行

S1(01)东西干道黄,南北干道红东西干道停车,南北干道禁止通行

S3(11)东西干道红,南北干道绿东西干道禁止通行,南北干道通行

S2(10)东西干道红,南北干道黄东西干道禁止通行,南北干道停车

设:A:表示东西干道绿灯亮的时间间隔为30秒,定时时间到A=1,否则,A=0。

4.要求红黄绿灯用发光二极管表示,并且显示出时间。

5.

主要参考资料

1.何小艇,电子系统设计,浙江大学出版社,2001年6月

2.姚福安,电子电路设计与实践,山东科学技术出版社,2001年10月

3.王澄非,电路与数字逻辑设计实践,东南大学出版社,1999年10月

4.李银华,电子线路设计指导,北京航空航天大学出版社,2005年6月

2. 用红、绿、黄发光二极管作信号灯。

3. 东西干道亮绿灯时,南北干道亮红灯;南北干道亮绿灯时,东西干道亮红灯。

4. 东西干道每次放行45秒,南北干道每次放行25秒,设立45秒、25秒计时、显示电路。

5. 在每次由绿灯亮到红灯亮的转换过程中,要亮5秒黄灯作为过渡,设立5秒计时、显示电路。

一、设计原理与参考电路

关键字:交通灯控制器 自动

概 述

设计要求:

1要求控制一个十字路口的交通灯。

2设定南北,东西向交通灯显示时间一样。

3设定红灯绿灯均显示30秒,红灯绿灯切换时黄灯显示2秒。

4要求红黄绿灯用发光二极管表示,并且显示出时间。

根据设计要求:

1. 设计一个交通信号灯控制器,由一条东西干道和一条南北干道汇合成十字路口,在每个入口处设置红、绿、黄三色信号灯,红灯亮禁止通行,绿灯亮允许通行,黄灯亮则给行驶中的车辆有时间停车。

[1]何小艇.电子系统设计[M].杭州:浙江大学出版社,2001年6月

S0(00)东西干道绿,南北干道红东西干道通行,南北干道禁止通行

S1(01)东西干道黄,南北干道红东西干道停车,南北干道禁止通行

S3(11)东西干道红,南北干道绿东西干道禁止通行,南北干道通行

S2(10)东西干道红,南北干道黄东西干道禁止通行,南北干道停车

设:A:表示东西干道绿灯亮的时间间隔为30秒,定时时间到A=1,否则,A=0。

4.要求红黄绿灯用发光二极管表示,并且显示出时间。

5.

主要参考资料

1.何小艇,电子系统设计,浙江大学出版社,2001年6月

2.姚福安,电子电路设计与实践,山东科学技术出版社,2001年10月

3.王澄非,电路与数字逻辑设计实践,东南大学出版社,1999年10月

4.李银华,电子线路设计指导,北京航空航天大学出版社,2005年6月

2. 用红、绿、黄发光二极管作信号灯。

3. 东西干道亮绿灯时,南北干道亮红灯;南北干道亮绿灯时,东西干道亮红灯。

4. 东西干道每次放行45秒,南北干道每次放行25秒,设立45秒、25秒计时、显示电路。

5. 在每次由绿灯亮到红灯亮的转换过程中,要亮5秒黄灯作为过渡,设立5秒计时、显示电路。

一、设计原理与参考电路

关键字:交通灯控制器 自动

概 述

设计要求:

1要求控制一个十字路口的交通灯。

2设定南北,东西向交通灯显示时间一样。

3设定红灯绿灯均显示30秒,红灯绿灯切换时黄灯显示2秒。

4要求红黄绿灯用发光二极管表示,并且显示出时间。

根据设计要求:

1. 设计一个交通信号灯控制器,由一条东西干道和一条南北干道汇合成十字路口,在每个入口处设置红、绿、黄三色信号灯,红灯亮禁止通行,绿灯亮允许通行,黄灯亮则给行驶中的车辆有时间停车。

交通信号灯的PLC控制优秀PPT

30安徽蚌埠机电技师学院交通信号灯的控制三相关知识顺序控制及设计方法plcplc程序的顺序控制设计方法程序的顺序控制设计方法顺序控制设计法顺序控制设计法顺控设计法的设计步骤顺控设计法的设计步骤功能图的结构步进指令编制梯形图的方法步进指令编制梯形图的方法顺序控制的其他编程方法顺序控制的其他编程方法11顺序控制设计法顺序控制设计法它是针对顺序控制系统的一种专门的设计方法

安徽蚌埠机电技师学院

13:02:23

交通信号灯的控制

3、状态流程图

(M8002+X22)

S0

此处编写自动运行采用

并行顺序

自动

手动(强制)

( X 24· M10)

S10

白天

夜晚

(X24·M10 )

S50

东西通行

南北通行

M1

M1

S11

S40

Y2

T2

M1

T1

Y5

T1

东西方向

南北方向

K5

S20

S30

S41

3、状态流程图(用GX-Developer编程软件的SFC编写的梯形图块)

说明:

D8013 D8014 D8015 D8016 D8017 D8018 D8019

S (0~ 59) min(0~ 59) h (0~ 23) 日 (1~ 31) 月 (1~ 12) 年 (0~ 99) 星期 (0 ~ 6)

SFC内置梯形图块—续5)

安徽蚌埠机电技师学院

13:02:26

交通信号灯的控制

3、状态流程图(用GX-Developer编程软件SFC编写的

SFC内置梯形图块—续6)

安徽蚌埠机电技师学院

13:02:27

交通信号灯的控制

安徽蚌埠机电技师学院

13:02:23

交通信号灯的控制

3、状态流程图

(M8002+X22)

S0

此处编写自动运行采用

并行顺序

自动

手动(强制)

( X 24· M10)

S10

白天

夜晚

(X24·M10 )

S50

东西通行

南北通行

M1

M1

S11

S40

Y2

T2

M1

T1

Y5

T1

东西方向

南北方向

K5

S20

S30

S41

3、状态流程图(用GX-Developer编程软件的SFC编写的梯形图块)

说明:

D8013 D8014 D8015 D8016 D8017 D8018 D8019

S (0~ 59) min(0~ 59) h (0~ 23) 日 (1~ 31) 月 (1~ 12) 年 (0~ 99) 星期 (0 ~ 6)

SFC内置梯形图块—续5)

安徽蚌埠机电技师学院

13:02:26

交通信号灯的控制

3、状态流程图(用GX-Developer编程软件SFC编写的

SFC内置梯形图块—续6)

安徽蚌埠机电技师学院

13:02:27

交通信号灯的控制

任务五单片机控制简单交通灯PPT课件

第27页/共141页

(8)Debug选项卡

第28页/共141页

5.1.3 Keil μVision调试技巧

第29页/共141页

1.程序复位

• 8051芯片复位后程序计数器将从0000H重新开始,另外一些内部特殊功能寄存器在复位期间也将重新赋值, 例如A将变为00H,DPTR变为0000H,SP变为07H,I/O端口变为0FFH等。程序复位有以下方法。 ①点击图标 。 ②选择Peripherals→Reset CPU。 ③在命令输入窗口输入“RESET”。

具栏

仿真 工具栏

第45页/共141页

1. 原理图编辑窗口

• 它是用来绘制原理图的,蓝色方框内为可编辑区,元件要放到它里面。注意,这 个窗口是没有滚动条的,你可用预览窗口来改变原理图的可视范围。

• 正确的操作是:鼠标滚轮用来放缩原理图;左键放置元件;右键选择元件;按两 次右键删除元件;先右键后左键编辑元件属性;先右键后左键拖动元件;连线用 左键,删除用右键。

第35页/共141页

6.定时器/计数器的使用方法

第36页/共141页

7.外部中断的使用方法

第37页/共141页

5.2 Proteus的使用

Proteus是由Labcenter Electronics开发的功能强大的单片机仿真软件。 该软件可以仿真模拟电路、数字电路、数模混合电路,其最大的亮点在于能 够对单片机进行实物级的仿真。

教学导航

知识重点

知识难点 教

推荐教学 方式

建议学时

(1)Keil菜单功能 (2)Proteus菜单功能 (3) 单片机最小系统及复位电路 (4)硬件仿真器、烧录器

Proteus与Keil μVision的联调

(8)Debug选项卡

第28页/共141页

5.1.3 Keil μVision调试技巧

第29页/共141页

1.程序复位

• 8051芯片复位后程序计数器将从0000H重新开始,另外一些内部特殊功能寄存器在复位期间也将重新赋值, 例如A将变为00H,DPTR变为0000H,SP变为07H,I/O端口变为0FFH等。程序复位有以下方法。 ①点击图标 。 ②选择Peripherals→Reset CPU。 ③在命令输入窗口输入“RESET”。

具栏

仿真 工具栏

第45页/共141页

1. 原理图编辑窗口

• 它是用来绘制原理图的,蓝色方框内为可编辑区,元件要放到它里面。注意,这 个窗口是没有滚动条的,你可用预览窗口来改变原理图的可视范围。

• 正确的操作是:鼠标滚轮用来放缩原理图;左键放置元件;右键选择元件;按两 次右键删除元件;先右键后左键编辑元件属性;先右键后左键拖动元件;连线用 左键,删除用右键。

第35页/共141页

6.定时器/计数器的使用方法

第36页/共141页

7.外部中断的使用方法

第37页/共141页

5.2 Proteus的使用

Proteus是由Labcenter Electronics开发的功能强大的单片机仿真软件。 该软件可以仿真模拟电路、数字电路、数模混合电路,其最大的亮点在于能 够对单片机进行实物级的仿真。

教学导航

知识重点

知识难点 教

推荐教学 方式

建议学时

(1)Keil菜单功能 (2)Proteus菜单功能 (3) 单片机最小系统及复位电路 (4)硬件仿真器、烧录器

Proteus与Keil μVision的联调

简易交通灯控制的PLD设计PPT课件

A1(C Q 3• 2Q )1•Q 2 B1(BQ 21)•Q2

C1( A Q 32 •Q )1•Q 2

7

Quartus II设计流程

8

创建工程项目

9

在硬盘新建一个你自己的文件夹, 把工程项目保存在此文件夹里。

10

选择器件:EPM240T100C5

11

完成工程项目创建

12

创建原理图文件

点击

48

感谢聆听

不足之处请大家批评指导

Please Criticize And Guide The Shortcomings

演讲人:XXXXXX 时 间:XX年XX月XX日

49

简易交通灯控制电路的PLD设计

1

设计任务

某交叉路口南北方向有红灯(A1)、黄灯(B1)、绿 灯(C1),东西方向有红灯(A2)、黄灯(B2)、绿 灯(C2)。红灯亮是停车信号,绿灯亮是通车信号, 黄灯亮是右转弯信号。

N

W

E

S

2

交通规则

南北方向红灯亮及东西方向绿灯亮(3S) 南北方向黄灯亮及东西方向黄灯亮(1S) 南北方向绿灯亮及东西方向红灯亮(3S) 南北方向黄灯亮及东西方向黄灯亮(1S)

1

0

1

1

1

南北方向信号灯

A1(红)

B1(黄)

C1(绿)

1

0

0

1

0

0

1

0

0

0

1

0

0

0

1

0

0

1

0

01Biblioteka 010A2(红) 0 0 0 0 1 1 1 0

东西方向信号灯

B2(黄)

C2(绿)

0

C1( A Q 32 •Q )1•Q 2

7

Quartus II设计流程

8

创建工程项目

9

在硬盘新建一个你自己的文件夹, 把工程项目保存在此文件夹里。

10

选择器件:EPM240T100C5

11

完成工程项目创建

12

创建原理图文件

点击

48

感谢聆听

不足之处请大家批评指导

Please Criticize And Guide The Shortcomings

演讲人:XXXXXX 时 间:XX年XX月XX日

49

简易交通灯控制电路的PLD设计

1

设计任务

某交叉路口南北方向有红灯(A1)、黄灯(B1)、绿 灯(C1),东西方向有红灯(A2)、黄灯(B2)、绿 灯(C2)。红灯亮是停车信号,绿灯亮是通车信号, 黄灯亮是右转弯信号。

N

W

E

S

2

交通规则

南北方向红灯亮及东西方向绿灯亮(3S) 南北方向黄灯亮及东西方向黄灯亮(1S) 南北方向绿灯亮及东西方向红灯亮(3S) 南北方向黄灯亮及东西方向黄灯亮(1S)

1

0

1

1

1

南北方向信号灯

A1(红)

B1(黄)

C1(绿)

1

0

0

1

0

0

1

0

0

0

1

0

0

0

1

0

0

1

0

01Biblioteka 010A2(红) 0 0 0 0 1 1 1 0

东西方向信号灯

B2(黄)

C2(绿)

0

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

据译码模块黄灯闪亮控制端来输出各灯的具体状态。

1)顶层模块: 此模块只做例化,即对底层的控制模块和译码模块 进行例化,而不做逻辑设计。

2)控制模块: 此模块是本程序的主体,主要是控制各个灯颜色( 此模块并不控制黄灯的闪烁) 的转换,以及倒计时时间输出

系统时钟 sysclk_10Hz

分频

分频时钟 sub_clk_1Hz

时序说明:首先还是加上系统时钟之后,用 reset 清零,则计数器清零、所 有灯都不亮。但reset 为 1 之后模块开始工作,首先是计数器开始计数,随 之分频 时钟会根据计数器的变化而周期变化,绿

灯会先亮 40 秒,之后黄灯也会亮(闪烁 在译码模 块实现)5 秒,然后就是红灯亮20 秒,以后就是循 环以上步骤的过程, 同时在循环过程中,倒计数

1hz 时钟

系

统

程序时 总体设计

钟

信

号

分频

个位 各 个 十位 状 态 转 变

分频时钟

七段译码 七段译码

黄灯闪烁控制

绿红亮 65s 黄闪 5s

全局控制信号 reset

首先,输入的10Hz 的系统时钟和全局控制端 reset ,输出为个位数字的七段 译码,十位数字七 段译码以及各个灯最后状态。 然后由于系统时钟

25000000 之前,分频时钟都是低电位,到 25000000 的时候分频时钟 的第一个上升沿来临,

此时状态控制开始运转,先工作的是绿灯,它会经

过从 39 到0 的倒计时过程,同时译码模块也开始 工作,颜色控制colour 是100,表征绿灯的点亮, 经七段译码,这个倒计时数字也会同步显示出来

经过 40s(也就是经过 40*10 个系统时钟上升沿之

简易交通灯控制电路

12电信2班 刘超凡 李莹

设计要求 设计思路及步骤 仿真波形 预期结果

设计要求

完成简单十字路口直行的交通灯控制电路设计。 (1)十字路口,南北方向红:黄:绿为20s:5s:40s且可 调; (2)工作时钟10hz; (3)各个方向的红黄绿等可用3个单色灯替代; (4)选做黄灯1hz闪烁; (5)完成全部流程:设计规范文档、模块设计、代码输入、 功能仿真、约束与综合、布局布线、时序仿真、下载验证 等。

时序图

初始状态 black

Enable=0, Status=1

清零端为低

Enable=1

第一个状态 Green

Enable=0, Status=1

第三个状态 Red

Enable=1

Enable=0, Status=1

第二个状态 Yellow

Enable=1

假设在 0 时刻,加上系统时钟,首先要进行 reset 清零,这时在控制模块的 计数器会清零,三 个灯都是灭的状态,控制状态跳转的使能端enable 等于0,等待 着清零结束,开始工作;七段译码也 不会显示。 在 reset 变低之后,系统开始正常工作。 首先是分频时钟开始工作,在计数 器达到第一个

控制

倒计时 各位

输出

倒计时 十位

输出

Black

Reset=0

20s 之后

green 5s 之后

40s 之后

red

ห้องสมุดไป่ตู้

yellow

输出

控制三个 灯亮与灭

输入:sysclk_10Hz 全局时钟信号,10Hz Reset 全局复位端,高电平有效 输出:dout_1s 倒计时个位上数字 dout_10s 倒计时十位上数字 light_select 各个灯状态 light_select(只是控制亮与 灭,不 管黄灯闪烁)

控制模块输入

点亮对应数码管 点亮对应数码管

输入端口: sysclk_10Hz 全局时钟信号,10Hz reset 全局复位端,高电平有效 din_1s 显示器个位数据,由控制模块输入 din_10s 显示器十位数据,由控制模块输入 light_sel 选择那盏灯亮,由控制模块的输入 输出端口: colour 最终显示哪盏灯亮,可与硬件相连 led_data_1s 显示器个位数据的译码 led_data_10s 显示器十位数据的译码

频率大,第一要进行分频,使其成为1Hz 的时钟信 号,第 二利用分频后的时钟信号对电路进行控制

,开始先对状态跳转进行控制,,用 case 语句控 制三灯亮与灭,紧跟着进行倒计时的过程。

第三输出个位和 十位上的数即可,要显示倒 计时是很容易实现的,直接用两个七段译码即可。

最后要控制黄灯的闪烁,还是要先产生分频时钟, 作为控制端,控制模块各灯 亮与灭作为输入,即 可产生黄灯闪烁的效果。 另外,作为全局控制端 ,reset 信号是清零用的,在有时钟信号的地方就 有 reset 。

沿),状态转移到红灯,然后显示及七段译码过程 与绿灯相似。至此一个周期已 经完成,接下来就

是循环执行以上步骤的过程,直到有reset 清零端 打断其正常工 作。

总体上分为三个大模块,即:顶层模块、控制模块、译码模块(包括 显示模块)。

顶层模块

控制模块

译码模块

输入: sysclk 10Hz (全局时钟信号) Reset (全局复位端,高电平有效)

的数会同步输出,各灯亮与灭状态也会同步输出。

3) 译码模块: 此模块主要有两个作用,控制黄灯闪烁以及对倒计时时间进行 译码输出。

系统时 钟

控制

分频 1Hz

产生

黄灯闪 烁控制 端

绿灯 黄灯 红灯

亮 40s 闪 5s 亮 20s

各灯状态

输入

七

输入

倒计时个 位,由

段

控制模块输入

译

码

倒计时十 位,由

器

输入

后)绿灯亮的时间到,会自动转到黄灯状态,黄灯 是5 到0 的倒计时过程,译码的显示跟绿灯一样, 只是黄灯的亮会加一个1Hz 的时钟控 - 4 - 制端,1 秒内只有半秒,黄灯是亮的,从 5秒到4.5 秒之间 黄灯是亮的,然后 4.5 到 3 是灭的,如此继续下去, 直到5 秒结束。又经过 5(5*10 个系统时钟上 升

设计思路

基本原理

用Verilog实现十字路口简易交通灯控制原理。南北向红黄 绿为20s:5s:40s 工作时钟10hz 黄灯1hz闪烁。Verilog语 言被广泛的应用在电路设计中。它的设计描述可被不同 的工具支持和实现。利用其自顶向下的设计方法来实现 交通灯控制原理,使道路交通正常运转。

分频

控制

输出:color (最终各灯状态亮或闪) led_ctrl_1s (个位七段译码) led_ctrl_10s(十位七段译码

时序说明:加上时钟信号之后,首先用 reset 清零, 然后控制模块会分频产 生分频时钟,根据分频时

钟的高与低,会控制各个状态之间的跳转,译码模 块会同 步通过数码管来显示倒计时数,并且会根

1)顶层模块: 此模块只做例化,即对底层的控制模块和译码模块 进行例化,而不做逻辑设计。

2)控制模块: 此模块是本程序的主体,主要是控制各个灯颜色( 此模块并不控制黄灯的闪烁) 的转换,以及倒计时时间输出

系统时钟 sysclk_10Hz

分频

分频时钟 sub_clk_1Hz

时序说明:首先还是加上系统时钟之后,用 reset 清零,则计数器清零、所 有灯都不亮。但reset 为 1 之后模块开始工作,首先是计数器开始计数,随 之分频 时钟会根据计数器的变化而周期变化,绿

灯会先亮 40 秒,之后黄灯也会亮(闪烁 在译码模 块实现)5 秒,然后就是红灯亮20 秒,以后就是循 环以上步骤的过程, 同时在循环过程中,倒计数

1hz 时钟

系

统

程序时 总体设计

钟

信

号

分频

个位 各 个 十位 状 态 转 变

分频时钟

七段译码 七段译码

黄灯闪烁控制

绿红亮 65s 黄闪 5s

全局控制信号 reset

首先,输入的10Hz 的系统时钟和全局控制端 reset ,输出为个位数字的七段 译码,十位数字七 段译码以及各个灯最后状态。 然后由于系统时钟

25000000 之前,分频时钟都是低电位,到 25000000 的时候分频时钟 的第一个上升沿来临,

此时状态控制开始运转,先工作的是绿灯,它会经

过从 39 到0 的倒计时过程,同时译码模块也开始 工作,颜色控制colour 是100,表征绿灯的点亮, 经七段译码,这个倒计时数字也会同步显示出来

经过 40s(也就是经过 40*10 个系统时钟上升沿之

简易交通灯控制电路

12电信2班 刘超凡 李莹

设计要求 设计思路及步骤 仿真波形 预期结果

设计要求

完成简单十字路口直行的交通灯控制电路设计。 (1)十字路口,南北方向红:黄:绿为20s:5s:40s且可 调; (2)工作时钟10hz; (3)各个方向的红黄绿等可用3个单色灯替代; (4)选做黄灯1hz闪烁; (5)完成全部流程:设计规范文档、模块设计、代码输入、 功能仿真、约束与综合、布局布线、时序仿真、下载验证 等。

时序图

初始状态 black

Enable=0, Status=1

清零端为低

Enable=1

第一个状态 Green

Enable=0, Status=1

第三个状态 Red

Enable=1

Enable=0, Status=1

第二个状态 Yellow

Enable=1

假设在 0 时刻,加上系统时钟,首先要进行 reset 清零,这时在控制模块的 计数器会清零,三 个灯都是灭的状态,控制状态跳转的使能端enable 等于0,等待 着清零结束,开始工作;七段译码也 不会显示。 在 reset 变低之后,系统开始正常工作。 首先是分频时钟开始工作,在计数 器达到第一个

控制

倒计时 各位

输出

倒计时 十位

输出

Black

Reset=0

20s 之后

green 5s 之后

40s 之后

red

ห้องสมุดไป่ตู้

yellow

输出

控制三个 灯亮与灭

输入:sysclk_10Hz 全局时钟信号,10Hz Reset 全局复位端,高电平有效 输出:dout_1s 倒计时个位上数字 dout_10s 倒计时十位上数字 light_select 各个灯状态 light_select(只是控制亮与 灭,不 管黄灯闪烁)

控制模块输入

点亮对应数码管 点亮对应数码管

输入端口: sysclk_10Hz 全局时钟信号,10Hz reset 全局复位端,高电平有效 din_1s 显示器个位数据,由控制模块输入 din_10s 显示器十位数据,由控制模块输入 light_sel 选择那盏灯亮,由控制模块的输入 输出端口: colour 最终显示哪盏灯亮,可与硬件相连 led_data_1s 显示器个位数据的译码 led_data_10s 显示器十位数据的译码

频率大,第一要进行分频,使其成为1Hz 的时钟信 号,第 二利用分频后的时钟信号对电路进行控制

,开始先对状态跳转进行控制,,用 case 语句控 制三灯亮与灭,紧跟着进行倒计时的过程。

第三输出个位和 十位上的数即可,要显示倒 计时是很容易实现的,直接用两个七段译码即可。

最后要控制黄灯的闪烁,还是要先产生分频时钟, 作为控制端,控制模块各灯 亮与灭作为输入,即 可产生黄灯闪烁的效果。 另外,作为全局控制端 ,reset 信号是清零用的,在有时钟信号的地方就 有 reset 。

沿),状态转移到红灯,然后显示及七段译码过程 与绿灯相似。至此一个周期已 经完成,接下来就

是循环执行以上步骤的过程,直到有reset 清零端 打断其正常工 作。

总体上分为三个大模块,即:顶层模块、控制模块、译码模块(包括 显示模块)。

顶层模块

控制模块

译码模块

输入: sysclk 10Hz (全局时钟信号) Reset (全局复位端,高电平有效)

的数会同步输出,各灯亮与灭状态也会同步输出。

3) 译码模块: 此模块主要有两个作用,控制黄灯闪烁以及对倒计时时间进行 译码输出。

系统时 钟

控制

分频 1Hz

产生

黄灯闪 烁控制 端

绿灯 黄灯 红灯

亮 40s 闪 5s 亮 20s

各灯状态

输入

七

输入

倒计时个 位,由

段

控制模块输入

译

码

倒计时十 位,由

器

输入

后)绿灯亮的时间到,会自动转到黄灯状态,黄灯 是5 到0 的倒计时过程,译码的显示跟绿灯一样, 只是黄灯的亮会加一个1Hz 的时钟控 - 4 - 制端,1 秒内只有半秒,黄灯是亮的,从 5秒到4.5 秒之间 黄灯是亮的,然后 4.5 到 3 是灭的,如此继续下去, 直到5 秒结束。又经过 5(5*10 个系统时钟上 升

设计思路

基本原理

用Verilog实现十字路口简易交通灯控制原理。南北向红黄 绿为20s:5s:40s 工作时钟10hz 黄灯1hz闪烁。Verilog语 言被广泛的应用在电路设计中。它的设计描述可被不同 的工具支持和实现。利用其自顶向下的设计方法来实现 交通灯控制原理,使道路交通正常运转。

分频

控制

输出:color (最终各灯状态亮或闪) led_ctrl_1s (个位七段译码) led_ctrl_10s(十位七段译码

时序说明:加上时钟信号之后,首先用 reset 清零, 然后控制模块会分频产 生分频时钟,根据分频时

钟的高与低,会控制各个状态之间的跳转,译码模 块会同 步通过数码管来显示倒计时数,并且会根