Xilinx FPGA DCI的应用

XilinxFPGA引脚功能详细介绍

Xi lin X F PGA 引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

I O_LXX Y _ # 用户10弓I脚XX代表某个Bank内唯一得一对引脚,Y=[P|N ]代表对上升沿还就是下降沿敏感,# 代表ban k 号2. I0_LXXY —Z Z Z_ #多功能引脚Z ZZ代表在用户10得基本上添加一个或多个以下功能。

Dn:1/ 0(在r eadb a ck期间),在selectMAP或者BPI模式下,D [1 5 :0]配置为数据口。

在从Selec t MAP读反馈期间,如果RDWR_B= 1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚•D 0_DIN_ M ISO_M I SO1: I,在并口模式(Sel ec tMAP/ B PI)下,D0 就是数据得最低位,在Bit —se r ial模式下,DI N就是信号数据得输入;在SPI模式下,MISO就是主输入或者从输出;在SPI*2或者S PI * 4模式下,M I SO 1就是S P I总线得第二位。

D1_MISO 2 ,D2_MIS O 3: I,在并口模式下,D1与D2就是数据总线得低位;在S PI * 4模式下, MISO2 与MISO3 就是SPI 总线得MSBs.A n :O, A : 25 :0]为B PI模式得地址位。

配置完成后,变为用户I/ O口。

A WAKE: O ,电源保存挂起模式得状态输出引脚。

SU S P E ND就是一个专用引脚,A WAK E就是一个多功能引脚。

除非SUSPEND模式被使能,AWAK E被用作用户I / O。

M O SI _CSI_B_MI S O0:I/O,在SPI模式下,主输出或者从输入在Se l ectMAP模式下,CS I_B 就是一个低电平有效得片选信号;在SPI * 2或者S P I *4得模式下,M I SO 0就是S PI总线得第一位数据。

FCS_B:O,BPI flash 得片选信号.FO E _B:O,B PI flash 得输出使能信号FW E_ B : O , BP I f l a sh得写使用信号LDC : O,BP I模式配置期间为低电平HDC: 0 ,B PI 模式配置期间为高电平CSO_B :O,在并口模式下,工具链片选信号。

赛灵思芯片应用场景

赛灵思芯片应用场景

赛灵思(Xilinx)芯片是一种可编程逻辑设备(FPGA),广

泛应用于各种领域。

以下是赛灵思芯片的几个常见应用场景:

1. 通信与网络:赛灵思芯片可以被用来实现高速数据传输、协议转换、网络交换和路由等功能,适用于通信设备、网络设备以及数据中心。

2. 图像与视频处理:赛灵思芯片的高性能计算能力和并行处理架构,使其成为处理高分辨率图像和视频的理想选择,例如视频编解码、图像处理、计算机视觉等。

3. 人工智能与深度学习:赛灵思芯片的高计算密度和灵活配置能力,适用于大规模并行计算,因此被广泛用于人工智能和深度学习领域,例如神经网络加速、模式识别和自动驾驶等。

4. 工业自动化与控制:赛灵思芯片可以实现基于模型的设计和控制方法,用于工业自动化和控制系统中,例如工厂自动化、机器人控制、智能传感器等。

5. 高性能计算与科学研究:由于赛灵思芯片的可编程性和高计算性能,它被用于高性能计算领域,例如数值模拟、科学计算、天气预报、基因组学研究等。

6. 航空航天与国防:赛灵思芯片的可编程性和高可靠性使其适用于航空航天和国防领域,例如雷达信号处理、导航系统、无人机控制等。

总之,赛灵思芯片的灵活性和可编程性使其在各种应用场景下都具备强大的计算和处理能力,满足不同行业的需求。

FPGA设计应用

FPGA设计应用FPGA(可编程门阵列)是一种可重构的集成电路,它可以根据设计者的需求进行重新编程和修改。

因此,FPGA设计在各个领域中的应用非常广泛。

本文将介绍FPGA设计的一些常见应用领域,并探讨其优势和挑战。

1.通信领域:FPGA广泛应用于通信系统中。

它可以用来处理和传输数字信号,实现调制解调、码分多址、射频信号生成等功能。

FPGA在通信系统中的灵活性使得它能够应对不同的通信标准和频率要求。

此外,FPGA还可以用于实时数据压缩、误码纠正和信号处理等任务。

2.图像和视频处理:FPGA设计可用于图像和视频处理应用中,如图像压缩、图像滤波、图像识别等。

相比于使用固定功能的集成电路,FPGA可以提供更高的处理性能和更低的功耗。

此外,FPGA还支持并行处理,可以加速图像和视频处理过程。

3.工业控制和自动化:FPGA广泛应用于工业控制和自动化系统中。

它可以用于实时数据采集和处理,控制器的逻辑和状态机的实现,以及实时监控和故障检测等。

FPGA的可编程性和实时性使得它成为工业控制和自动化系统的理想选择。

4.电力系统:FPGA设计可以用于电力系统中的电力负载监测、电力调度和电能管理等应用。

它可以采集电能数据、处理电能数据并生成相应的控制信号。

FPGA还可以实现电网故障检测和电能质量监测等功能,提高电力系统的可靠性和效率。

5.数字信号处理:FPGA可以用于各种数字信号处理应用,如音频处理、声音合成、音频编解码等。

相比于使用通用微处理器进行数字信号处理,FPGA可以提供更高的性能和更低的功耗。

FPGA设计的优势在于它的灵活性和可重构性。

设计者可以通过重新编程FPGA来满足不同的需求,而不需要重新设计整个系统。

此外,FPGA 还可以提供相对低的成本和短的开发周期,使得它在敏捷开发和快速迭代的项目中具有优势。

然而,FPGA设计也面临一些挑战。

首先,FPGA设计在开发和调试方面需要较高的技术水平和经验。

其次,由于FPGA的结构和规模较大,设计者需要考虑时序、电磁兼容性和功耗等问题。

ilinfpga引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

fpga应用案例

fpga应用案例

1. 数字信号处理(DSP):FPGA是实现数字信号处理算法的

理想平台。

例如,FPGA可以用于音频处理、图像处理和视频

处理等领域。

2. 高性能计算(HPC):FPGA可以在并行计算环境中使用,

用于加速科学计算和数值模拟等计算密集型任务。

3. 网络加速:FPGA可以用于网络加速,例如协议转换、加密

解密、负载均衡等。

4. 通信系统:FPGA可以用于实现各种通信标准和协议,例如LTE、Wifi、4G等。

5. 数字信号实时处理:FPGA可以用于实时处理音视频信号,

例如音视频编解码、拼接、切换等。

6. 控制器/接口芯片:FPGA可以用于实现各种接口芯片,例

如USB、以太网、PCI、SATA等。

7. 硬件加速器:FPGA可以作为硬件加速器使用,例如加速机

器学习算法、加速数据库查询等。

8. 自动驾驶:FPGA可以用于自动驾驶系统中,例如用于图像

处理、传感器数据处理、车辆控制等。

9. 无人机:FPGA可以用于无人机系统中,例如用于图像处理、

传感器数据处理、控制系统等。

10. 医疗设备:FPGA可以用于医疗设备中,例如用于医学成像、医学数据处理、生命支持系统等。

Xilinx FPGA DCI的应用.pdf

Xilinx系列FPGA的DCI技术1、DCI技术概述随着FPGA芯片越大而且系统时钟越高,PCB板设计以及结构设计变得越难,随着速率的提高,板间的信号完整性变的非常关键,PCB板上若有关键信号,那么需要进行阻抗匹配,从而避免信号的反射和震荡。

Xilinx公司提供DCI (Digitally Controlled Impedance)可以在芯片内部进行阻抗匹配,匹配电阻更加接进芯片,可以减少元器件,节省PDB板面积,并且也更方便走线。

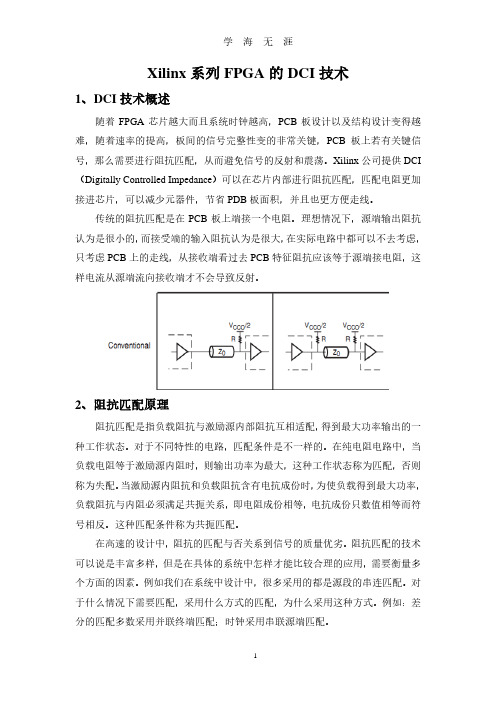

传统的阻抗匹配是在PCB板上端接一个电阻。

理想情况下,源端输出阻抗认为是很小的,而接受端的输入阻抗认为是很大,在实际电路中都可以不去考虑,只考虑PCB上的走线,从接收端看过去PCB特征阻抗应该等于源端接电阻,这样电流从源端流向接收端才不会导致反射。

2、阻抗匹配原理阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,得到最大功率输出的一种工作状态。

对于不同特性的电路,匹配条件是不一样的。

在纯电阻电路中,当负载电阻等于激励源内阻时,则输出功率为最大,这种工作状态称为匹配,否则称为失配。

当激励源内阻抗和负载阻抗含有电抗成份时,为使负载得到最大功率,负载阻抗与内阻必须满足共扼关系,即电阻成份相等,电抗成份只数值相等而符号相反。

这种匹配条件称为共扼匹配。

在高速的设计中,阻抗的匹配与否关系到信号的质量优劣。

阻抗匹配的技术可以说是丰富多样,但是在具体的系统中怎样才能比较合理的应用,需要衡量多个方面的因素。

例如我们在系统中设计中,很多采用的都是源段的串连匹配。

对于什么情况下需要匹配,采用什么方式的匹配,为什么采用这种方式。

例如:差分的匹配多数采用并联终端匹配;时钟采用串联源端匹配。

2.1 串联源端匹配串联源端匹配的理论出发点是在信号源端阻抗低于传输线特征阻抗的条件下,在信号的源端和传输线之间串接一个电阻R,使源端的输出阻抗与传输线的特征阻抗相匹配,抑制从负载端反射回来的信号发生再次反射。

fpga 实际应用

fpga 实际应用FPGA(Field-Programmable Gate Array)是一种集成电路芯片,可以根据需要重新配置其内部逻辑电路,实现不同的功能。

由于其灵活性和高性能,FPGA在各个领域都有广泛应用。

本文将介绍FPGA 在实际应用中的一些典型案例。

一、通信领域FPGA在通信领域具有重要作用。

例如,FPGA可以用于协议转换、调制解调、信号处理等方面。

在网络路由器中,FPGA可以实现高速数据包处理和路由算法。

在无线通信系统中,FPGA可以用于信号调制解调、信号处理和通信协议的实现。

由于FPGA具有高度的可重构性,可以根据不同的通信标准进行配置,因此在通信领域中广泛应用。

二、图像处理FPGA在图像处理领域有着广泛的应用。

例如,FPGA可以用于图像的采集、压缩、处理和显示。

在摄像头中,FPGA可以实现图像的采集和预处理,例如去噪、锐化等。

在数字电视中,FPGA可以实现图像的压缩和解压缩,以及图像的显示和处理。

由于FPGA具有高性能和低功耗的特点,因此在图像处理领域中得到了广泛应用。

三、工业控制FPGA在工业控制领域也有着重要的应用。

例如,FPGA可以用于逻辑控制、运动控制和数据采集等方面。

在自动化生产线中,FPGA可以实现各种传感器的数据采集和处理,以及各种执行器的控制。

在机器人控制中,FPGA可以实现运动控制和轨迹规划等功能。

由于FPGA 具有高度的可编程性和实时性,因此在工业控制领域中得到了广泛应用。

四、人工智能随着人工智能的发展,FPGA在人工智能领域也有着重要的应用。

例如,FPGA可以用于神经网络的加速和优化。

在深度学习中,FPGA可以实现神经网络的前向计算和反向计算,加速神经网络的训练和推理过程。

由于FPGA具有高度的并行计算能力和低功耗的特点,因此在人工智能领域中得到了广泛应用。

FPGA在实际应用中具有广泛的应用前景。

无论是在通信领域、图像处理领域、工业控制领域还是人工智能领域,FPGA都发挥着重要的作用。

FPGA的几种热门应用

FPGA的几种热门应用

没有一种器件可以满意全人类的众多需求,因此不用担忧FPGA没有用武之地。

必定是一系列产品的组合。

下面主要介绍一下FPGA可以作为现今热门场景的几种应用。

(1)网络存储产品,特殊是现在的NAS,或者SAN设备上,其存储的时间、接口、平安性等都要求较高,而FPGA无论处理性能还是扩展接口的力量都使其在这一领域大有作为。

现在高端FPGA单片就可以扩展32个或者更多4G或者8G的FC接口。

并且其协议处理相对的固定,也使FPGA在这一领域有大量的可能应用。

(2)高速网络设备,现在高速网络设备10G、40/100G以太网设备领域,同样FPGA也是关键的处理部件。

特殊是IPv6的商用化及大数据对于基础设施的高要求,都使这一领域的处理应用会渐渐广泛,这一领域通常是高速网络处理器(NP)+FPGA的典型架构。

(3)4G等通信设备,对于新一代通信基站的信号处理,FPGA+DSP 阵列的架构就是绝配。

特殊是在专用处理芯片面世之前,这样的架构可以保证新一代通信基础设施的快速研发和部署。

没有完善的架构,只有合适的组合,各种芯片和架构都是为应用服务,相互的渗透是趋势,也是必定。

FPGA相对处理器的可编程领域,仍旧属于小众(虽然人数也不少)。

但是正像一则笑话所说:大腿虽然比根命根子粗,但决没有命子重要。

这算开个玩笑。

FPGA的实现为以后的芯片化留下了很多可能和想象空间,从而在应用大量爆

发时通过芯片化来大幅降低成本,这这也正是其他可编程器件所不能比拟的。

fpga实际应用

fpga实际应用FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,它在许多领域都有广泛的应用。

本文将介绍FPGA的实际应用,并探讨其在不同领域的优势和应用案例。

FPGA在数字信号处理领域有着重要的应用。

数字信号处理是将模拟信号转换为数字信号,并对其进行处理和分析的过程。

FPGA通过其可编程性和并行处理能力,可以实现高效的数字信号处理算法。

例如,FPGA可以用于音频和视频编解码、图像处理和通信系统等领域。

相比于传统的专用集成电路(ASIC),FPGA具有更高的灵活性和可重构性,可以根据实际需求进行快速定制和适应性更新。

FPGA在通信领域也有广泛的应用。

通信系统需要高速数据传输和实时处理能力,而FPGA正好具备这些特点。

FPGA可以用于实现各种通信协议和算法,如以太网、无线通信和卫星通信等。

此外,FPGA还可以用于数据压缩和加密解密等功能,提高通信系统的安全性和效率。

FPGA在嵌入式系统设计中也起到了重要的作用。

嵌入式系统是指集成了计算机处理器和专用硬件的系统,用于控制和操作各种电子设备。

FPGA可以用于实现嵌入式系统的核心功能和外围接口。

例如,FPGA可以用于控制和管理机器人、自动驾驶车辆和智能家居设备等。

FPGA的可编程性使得嵌入式系统设计更加灵活和可扩展,可以满足不同应用场景的需求。

除了以上领域,FPGA还在科学研究和工业控制等领域发挥着重要作用。

在科学研究中,FPGA可以用于实现各种实验和模拟,如天文学、物理学和生物学等。

在工业控制中,FPGA可以用于实现实时控制和监测系统,提高生产效率和质量。

FPGA的高性能和可编程性使得它成为了众多应用领域的理想选择。

总结起来,FPGA在实际应用中具有广泛的应用前景。

它在数字信号处理、通信、嵌入式系统设计、科学研究和工业控制等领域都有着重要的作用。

随着技术的不断进步和FPGA的不断发展,相信FPGA的应用领域还将不断扩大,并为各行各业带来更多的创新和发展机会。

Xilinx FPGA 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_#用户IO引脚XX代表某个Bank内唯一得一对引脚,Y=[P|N]代表对上升沿还就是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_#多功能引脚ZZZ代表在用户IO得基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚.D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0就是数据得最低位,在Bit—serial模式下,DIN就是信号数据得输入;在SPI模式下,MISO就是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1就是SPI总线得第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1与D2就是数据总线得低位;在SPI*4模式下,MISO2与MISO3就是SPI总线得MSBs.An:O,A[25:0]为BPI模式得地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式得状态输出引脚。

SUSPEND就是一个专用引脚,AW A KE就是一个多功能引脚。

除非SUSPEND模式被使能,AW AKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B就是一个低电平有效得片选信号;在SPI*2或者SPI*4得模式下,MISO0就是SPI总线得第一位数据。

FCS_B:O,BPI flash 得片选信号.FOE_B:O,BPI flash得输出使能信号FWE_B:O,BPIflash 得写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

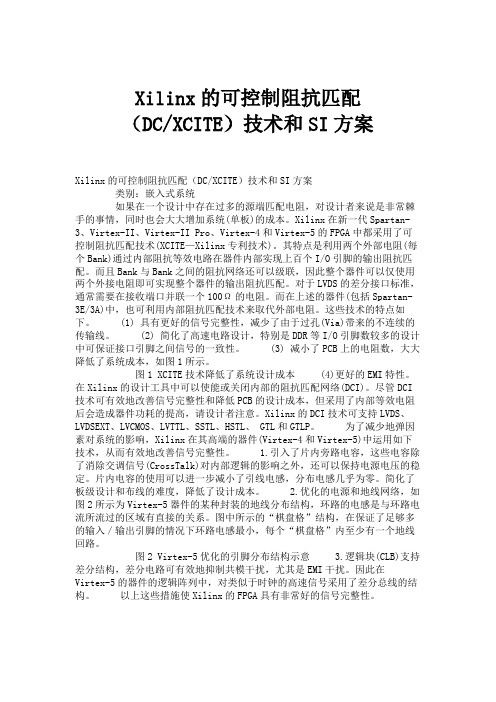

Xilinx的可控制阻抗匹配(DCXCITE)技术和SI方案.

Xilinx的可控制阻抗匹配(DC/XCITE)技术和SI方案Xilinx的可控制阻抗匹配(DC/XCITE)技术和SI方案类别:嵌入式系统如果在一个设计中存在过多的源端匹配电阻,对设计者来说是非常棘手的事情,同时也会大大增加系统(单板)的成本。

Xilinx在新一代Spartan-3、Virtex-II、Virtex-II Pro、Virtex-4和Virtex-5的FPGA中都采用了可控制阻抗匹配技术(XCITE—Xilinx专利技术)。

其特点是利用两个外部电阻(每个Bank)通过内部阻抗等效电路在器件内部实现上百个I/O引脚的输出阻抗匹配。

而且Bank与Bank之间的阻抗网络还可以级联,因此整个器件可以仅使用两个外接电阻即可实现整个器件的输出阻抗匹配。

对于LVDS的差分接口标准,通常需要在接收端口并联一个100Ω的电阻。

而在上述的器件(包括Spartan-3E/3A)中,也可利用内部阻抗匹配技术来取代外部电阻。

这些技术的特点如下。

(1) 具有更好的信号完整性,减少了由于过孔(Via)带来的不连续的传输线。

(2) 简化了高速电路设计,特别是DDR等I/O引脚数较多的设计中可保证接口引脚之间信号的一致性。

(3) 减小了PCB上的电阻数,大大降低了系统成本,如图1所示。

图1 XCITE技术降低了系统设计成本(4)更好的EMI特性。

在Xilinx的设计工具中可以使能或关闭内部的阻抗匹配网络(DCI)。

尽管DCI 技术可有效地改善信号完整性和降低PCB的设计成本,但采用了内部等效电阻后会造成器件功耗的提高,请设计者注意。

Xilinx的DCI技术可支持LVDS、LVDSEXT、LVCMOS、LVTTL、SSTL、HSTL、 GTL和GTLP。

为了减少地弹因素对系统的影响,Xilinx在其高端的器件(Virtex-4和Virtex-5)中运用如下技术,从而有效地改善信号完整性。

1.引入了片内旁路电容,这些电容除了消除交调信号(CrossTalk)对内部逻辑的影响之外,还可以保持电源电压的稳定。

(完整word版)XilinxFPGA引脚功能详细介绍

Xilinx FPGA 引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户10引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank 号2. IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户10的基本上添加一个或多个以下功能。

Dn:I/O (在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

DO_DIN_MISO_MISO1 : I,在并口模式(SelectMAP/BPI )下,D0 是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3 : I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An : O, A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O 口。

AWAKE : O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0 : I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B 是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISOO是SPI总线的第一位数据。

FCS_B: O, BPI flash 的片选信号。

FOE_B : O, BPI flash的输出使能信号FWE_B : O, BPI flash的写使用信号LDC : O,BPI模式配置期间为低电平HDC : O,BPI模式配置期间为高电平CSO_B: O,在并口模式下,工具链片选信号。

XilinxFPGA引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

模INIT_B:双向,开漏,低电平表示配置内存已经被清理;保持低电平,配置被延迟;在配置过程中,低电平表示配置数据错误已经发生;配置完成后,可以用来指示POST_CRC 状态。

SCPn:I,挂起控制引脚SCP[7:0],用于挂起多引脚唤醒特性。

CMPMOSI,CMPMISO,CMPCLK:N/A,保留。

M0,M1:I,配置模式选择。

M0=并口(0)或者串口(1),M1=主机(0)或者从机(1)。

CCLK:I/O,配置时钟,主模式下输出,从模式下输入。

USERCCLK:I,主模式下,可行用户配置时钟。

GCLK:I,这些引脚连接到全局时钟缓存器,在不需要时钟的时候,这些引脚可以作为常规用户引脚。

VREF_#:N/A,这些是输入临界电压引脚。

当外部的临界电压不必要时,他可以作为普通引脚。

当做作bank内参考电压时,所有的VRef都必须被接上。

3.多功能内存控制引脚M#DQn:I/O,bank#内存控制数据线D[15:0]M#LDQS:I/O,bank#内存控制器低数据选通脚M#LDQSN:I/O,bank#中内存控制器低数据选通NM#UDQS:I/O,bank#内存控制器高数据选通脚M#UDQSN:I/O,bank#内存控制器高数据选通NM#An:O,bank#内存控制器地址线A[14:0]M#BAn:O,bank#内存控制bank地址BA[2:0]M#LDM:O,bank#内存控制器低位掩码6.其它GND:VBATT:RAM内存备份电源。

ilin fpga 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank 号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

xilinx公司的7系列FPGA应用指南

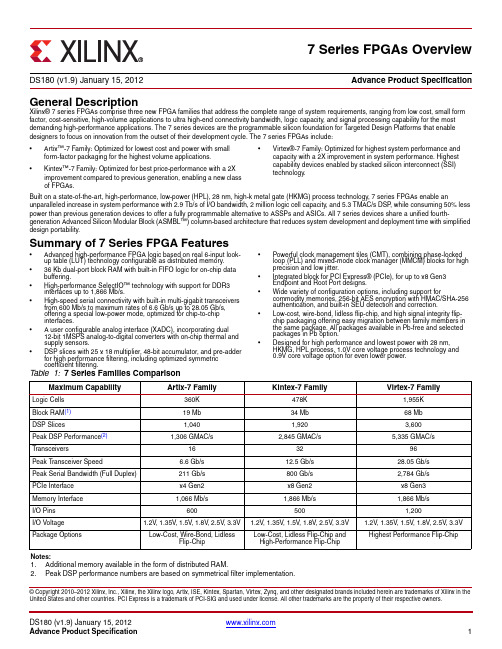

• Artix™-7 Family: Optimized for lowest cost and power with small form-factor packaging for the highest volume applications.

• Kintex™-7 Family: Optimized for best price-performance with a 2X improvement compared to previous generation, enabling a new class of FPGAs.

DS180 (v1.9) January 15, 2012

Advance Product Specification

1

7 Series FPGAs Overview

Artix-7 FPGA Feature Summary

Table 2: Artix-7 FPGA Feature Summary by Device

• Virtex®-7 Family: Optimized for highest system performance and capacity with a 2X improvement in system performance. Highest capability devices enabled by stacked silicon interconnect (SSI) technology.

• Low-cost, wire-bond, lidless flip-chip, and high signal integrity flipchip packaging offering easy migration between family members in the same package. All packages available in Pb-free and selected packages in Pb option.

Xilinx FPGA DCI的应用

Xilinx系列FPGA的DCI技术1、DCI技术概述随着FPGA芯片越大而且系统时钟越高,PCB板设计以及结构设计变得越难,随着速率的提高,板间的信号完整性变的非常关键,PCB板上若有关键信号,那么需要进行阻抗匹配,从而避免信号的反射和震荡。

Xilinx公司提供DCI (Digitally Controlled Impedance)可以在芯片内部进行阻抗匹配,匹配电阻更加接进芯片,可以减少元器件,节省PDB板面积,并且也更方便走线。

传统的阻抗匹配是在PCB板上端接一个电阻。

理想情况下,源端输出阻抗认为是很小的,而接受端的输入阻抗认为是很大,在实际电路中都可以不去考虑,只考虑PCB上的走线,从接收端看过去PCB特征阻抗应该等于源端接电阻,这样电流从源端流向接收端才不会导致反射。

2、阻抗匹配原理阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,得到最大功率输出的一种工作状态。

对于不同特性的电路,匹配条件是不一样的。

在纯电阻电路中,当负载电阻等于激励源内阻时,则输出功率为最大,这种工作状态称为匹配,否则称为失配。

当激励源内阻抗和负载阻抗含有电抗成份时,为使负载得到最大功率,负载阻抗与内阻必须满足共扼关系,即电阻成份相等,电抗成份只数值相等而符号相反。

这种匹配条件称为共扼匹配。

在高速的设计中,阻抗的匹配与否关系到信号的质量优劣。

阻抗匹配的技术可以说是丰富多样,但是在具体的系统中怎样才能比较合理的应用,需要衡量多个方面的因素。

例如我们在系统中设计中,很多采用的都是源段的串连匹配。

对于什么情况下需要匹配,采用什么方式的匹配,为什么采用这种方式。

例如:差分的匹配多数采用并联终端匹配;时钟采用串联源端匹配。

2.1 串联源端匹配串联源端匹配的理论出发点是在信号源端阻抗低于传输线特征阻抗的条件下,在信号的源端和传输线之间串接一个电阻R,使源端的输出阻抗与传输线的特征阻抗相匹配,抑制从负载端反射回来的信号发生再次反射。

DCI是什么?Xilinx 7系列FPGA的HP bank都支持DCI

DCI 是什么?Xilinx 7 系列FPGA 的HP bank 都支

持DCI

Xilinx 7 系列FPGA 的HP bank 都支持DCI,目的是在高速单板信号传输中保持信号完整性,减少反射等因素影响,那幺DCI 是什幺?digitally controlled impedance 是DCI 的缩写,应该也算上xilinx 在IO feature 上的一项技术(这不是7 系列才有的新技术)。

DCI 从字面上看含义是可控制的阻

抗,启动DCI 功能可以减少单板为阻抗匹配所需要的电阻使用,典型应用时DDR 控制器。

DCI 根据IO 标准的不同,支持输入和输出,能够精确匹配传输中的阻抗

特性。

DCI 通过挂载到VRP VRN 上的参考电阻自动校正IO 内部的阻抗匹配。

这样应用中遇到因环境温度变化和电源波动引起的阻抗不匹配都可以通

过IO 内部阻抗来补偿,这就是DCI 技术。

DCI 仅可以在HP bank 应用,HR bank 不支持DCI。

图1.xilinx MIG 开启了DCI 功能

图2.开发板DDR3 VRP VRN 的连接和阻值

图3. SSTL18_I 和SSTL18_II 两种电气标准的DCI 应用对比。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Xilinx系列FPGA的DCI技术1、DCI技术概述随着FPGA芯片越大而且系统时钟越高,PCB板设计以及结构设计变得越难,随着速率的提高,板间的信号完整性变的非常关键,PCB板上若有关键信号,那么需要进行阻抗匹配,从而避免信号的反射和震荡。

Xilinx公司提供DCI (Digitally Controlled Impedance)可以在芯片内部进行阻抗匹配,匹配电阻更加接进芯片,可以减少元器件,节省PDB板面积,并且也更方便走线。

传统的阻抗匹配是在PCB板上端接一个电阻。

理想情况下,源端输出阻抗认为是很小的,而接受端的输入阻抗认为是很大,在实际电路中都可以不去考虑,只考虑PCB上的走线,从接收端看过去PCB特征阻抗应该等于源端接电阻,这样电流从源端流向接收端才不会导致反射。

2、阻抗匹配原理阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,得到最大功率输出的一种工作状态。

对于不同特性的电路,匹配条件是不一样的。

在纯电阻电路中,当负载电阻等于激励源内阻时,则输出功率为最大,这种工作状态称为匹配,否则称为失配。

当激励源内阻抗和负载阻抗含有电抗成份时,为使负载得到最大功率,负载阻抗与内阻必须满足共扼关系,即电阻成份相等,电抗成份只数值相等而符号相反。

这种匹配条件称为共扼匹配。

在高速的设计中,阻抗的匹配与否关系到信号的质量优劣。

阻抗匹配的技术可以说是丰富多样,但是在具体的系统中怎样才能比较合理的应用,需要衡量多个方面的因素。

例如我们在系统中设计中,很多采用的都是源段的串连匹配。

对于什么情况下需要匹配,采用什么方式的匹配,为什么采用这种方式。

例如:差分的匹配多数采用并联终端匹配;时钟采用串联源端匹配。

2.1 串联源端匹配串联源端匹配的理论出发点是在信号源端阻抗低于传输线特征阻抗的条件下,在信号的源端和传输线之间串接一个电阻R,使源端的输出阻抗与传输线的特征阻抗相匹配,抑制从负载端反射回来的信号发生再次反射。

串联终端匹配后的信号传输具有以下特点:1、由于串联匹配电阻的作用,驱动信号传播时以其幅度的50%向负载端传播。

2、信号在负载端的反射系数接近+1,因此反射信号的幅度接近原始信号幅度的50%。

3、反射信号与源端传播的信号叠加,使负载端接受到的信号与原始信号的幅度近似相同。

4、负载端反射信号向源端传播,到达源端后被匹配电阻吸收。

5、反射信号到达源端后,源端驱动电流降为0,直到下一次信号传输。

相对串联匹配来说,不要求信号驱动器具有很大的电流驱动能力。

选择串联源端匹配电阻值的原则很简单,就是要求匹配电阻值与驱动器的输出阻抗之和与传输线的特征阻抗相等。

理想的信号驱动器的输出阻抗为零,实际的驱动器总是有比较小的输出阻抗,而且在信号的电平发生变化时,输出阻抗可能不同。

比如电源电压为+4.5V的CMOS驱动器,在低电平时典型的输出阻抗为37欧姆,在高电平时典型的输出阻抗为45欧姆;TTL驱动器和CMOS驱动一样,其输出阻抗会随信号的电平大小变化而变化。

因此,对TTL或CMOS电路来说,不可能有十分正确的匹配电阻,只能折中考虑。

链状拓扑结构的信号网路不适合使用串联终端匹配,所有的负载必须接到传输线的末端。

可以看出,有一段时间负载端信号幅度为原始信号幅度的一半。

显然这时候信号处在不定逻辑状态,信号的噪声容限很低。

串联匹配是最常用的终端匹配方法。

它的优点是功耗小,不会给驱动器带来额外的直流负载,也不会在信号和地之间引入额外的阻抗;而且只需要一个电阻元件。

2.2 并联源端匹配并联终端匹配的理论出发点是在信号源端阻抗很小的情况下,通过增加并联电阻使负载端输入阻抗与传输线的特征阻抗相匹配,达到消除负载端反射的目的。

实现形式分为单电阻和双电阻两种形式。

并联终端匹配后的信号传输具有以下特点:1、驱动信号近似以满幅度沿传输线传播;2、所有的反射都被匹配电阻吸收;3、负载端接受到的信号幅度与源端发送的信号幅度近似相同。

在实际的电路系统中,芯片的输入阻抗很高,因此对单电阻形式来说,负载端的并联电阻值必须与传输线的特征阻抗相近或相等。

假定传输线的特征阻抗为50欧姆,则R值为50欧姆。

如果信号的高电平为5V,则信号的静态电流将达到100mA。

由于典型的TTL或CMOS电路的驱动能力很小,这种单电阻的并联匹配方式很少出现在这些电路中。

双电阻形式的并联匹配,也被称作戴维南终端匹配,要求的电流驱动能力比单电阻形式小。

这是因为两电阻的并联值与传输线的特征阻抗相匹配,每个电阻都比传输线的特征阻抗大。

考虑到芯片的驱动能力,两个电阻值的选择必须遵循三个原则:1、两电阻的并联值与传输线的特征阻抗相等;2、与电源连接的电阻值不能太小,以免信号为低电平时驱动电流过大;3、与地连接的电阻值不能太小,以免信号为高电平时驱动电流过大。

传统的终端匹配要求电阻尽量靠近芯片管脚,不但增加了PCB的布线的难度,而且还增加了元器件的数量。

3、DCI技术根据I/O的电平标准,DCI技术可以控制驱动器的输出阻抗,也可以在驱动器或者接收器上添加并行终端。

目的都是精确的匹配传输线上的特征阻抗。

DCI 技术根据VRP和VRN上的高精度参考电阻计算I/O内部的阻抗。

并且可以持续补偿因为温度和电压变化引起的阻抗变化。

对于阻抗控制驱动器,DCI使阻抗匹配外部的两个参考电阻,或者匹配这两个参考电阻的一半。

对于并行终端,包括发送器和接收器,DCI技术让终端电阻更加接近输出驱动器或者输入buffer。

对于7系列FPGA,DCI技术只用在HP I/O bank,对HR I/Obank 并不适用。

Xilinx DCI使用两个复用管脚来调整驱动器的阻抗或者并联终端电阻。

这两个管脚分别是VRN 和VRP。

VRN必须通过一个参考电阻Rref上拉到VCCO,而VRP则必须通过一个参考电阻Rref下拉到地。

这个Rref的阻值一般等于PCB走线的特征阻抗或者是这个阻抗的2倍。

要在设计中使用DCI技术,需要满足以下条件:❖该信号管脚是在HP I/O BANK,并且在约束中声明该管脚的标准是带有DCI 的;❖在VRN上接一个高精度的参考电阻上拉到Vcco;❖在VRP上接一个高精度的参考电阻下拉到地;❖VRN和VRP都在同一个HP BANK,除非使用了DCI叠代,DCI迭代只需要HP master BANK的。

❖DCI计算可以通过DCIRESET原语进行复位。

通过发送RST高脉冲给DCIRESET,DCI开始计算阻抗值并且此时所有使用了DCI的I/O都不工作,直到LOCKED信号拉高为止。

3.1 阻抗控制驱动器对于阻抗控制驱动器,DCI提供两种阻抗匹配类型:1、和参考电阻相等2、等于参考电阻的一半这种的话,R必须等于2Z0,电平标准要选择DCI_DV2,如LVDCI_DV2_15、LVDCI_DV2_18的原语,使用这种方式主要是为了降低静态功耗。

3.2 并联终端(分立电阻)对于并联终端,DCI使用一种戴维南等效电路或者分立电阻,使用Vcco/2的电平。

戴维南等效电路:适合于分立电阻的DCI电平标准如下表:4、三态DCI对于有些电平标准,如SSTL和HSTL的一级标准仅仅支持单向信号,而二级标准既支持单向也支持双向信号,当分立终端在使用时,DCI只控制分立终端的阻抗而不是驱动器的阻抗,所以对于双向信号来说,当它作为驱动器时,需要关闭分立终端的应用。

XILINX提供了一个DCI-T的标准来满足这一要求,只需要将相应的电平标准改成这种带有DCI-T的就行。

三态DCI只适合于双向信号。

适用三态DCI的电平标准如下表:DCI所有的电平标准如下表:5、DCI迭代7系列FPGA可以使用DCI迭代,DCI迭代就是同在一列的I/O BANK可以共享一对参考电阻,即只要这一列的I/O BANK中的master BANK的RFN和RFP接了相应的电阻后,其他的slave BANK的RFN和RFP都不需要再接参考电阻了。

这样大大减少了元器件数量同时也减少了功耗。

DCI迭代需要遵循如下规则:❖需要DCI迭代的管脚必须在同一列BANK上;❖同一列BANK需要分成MASTER和SLA VE BANK,他们应该有共同的Vcco 和Vref;❖在同一列BANK上,但是没有使用DCI技术的BANK可以不遵循第二条规则;❖为了实现这个DCI迭代,需要使用DCI_CASCADE Constraint。

约束语法规则:CONFIG DCI_CASCADE = " ...";例如:CONFIG DCI_CASCADE = "11 13 15 17";总之,对于7系列FPGA要正确使用DCI技术的话,要做如下:❖Vcco必须是基于合适的电平标准;❖使用正确的DCI I/O BUFFER通过电平标准属性或者在HDL中例化的代码中;❖DCI技术要求相应的BANK中VRN和VRP管脚用来连接正确的参考电阻,对于DCI迭代技术则只要master bank中的VRN和VRP管脚用来连接正确的参考电阻。

有一种情况就是当DCI(带阻抗控制驱动器)只作为输入时,并且这些管脚又是仅有的使用了DCI电平的管脚,那么该BANK不需要将VRN和VRP接参考电阻。

这些电平标准有以下这些。

❖遵守DCI I/O BANKING规则:1)同一BANK的输入管脚或者使用了DCI迭代的同一组的BANK的输入管脚,其参考电压Vref必须是一致的;2)在同一个BANK中Vcco必须兼容所有的输入或输出管脚;3)分立终端、阻抗控制驱动器、以及半阻抗控制驱动器,可以在同一BANK中同时存在。

6、DCI使用案例注意:LVDS和LVDS25是不能使用DCI技术来进行终端匹配的,它只能通过内部终端电阻来进行匹配如下图所示。

7、总结DCI技术的主要作用:保证信号的完整性,防止信号的反射,达到匹配的功能。

(对于管脚数多的和阵列式的管脚。

)FPGA内各个模块的DCI独立,一旦DCI标准确定,那么相应的电阻必须背接到相应的管脚VRN和VRP使用了相应的标准相应的“参考电阻”也就确定了。

标准的接50欧姆由于我们使用的LVTTL,所以驱动的时候必须要有匹配电阻,所以要连上,然后在软件上再选择LVDCI_33DCI的工作模式:但是输入的LVTTL不需要DCI有的标准收发搜需要DCI:DCI的注意点:❖Vref必须对一个BANK的所有的输入管脚一致;❖VCCO必须和所有的输入输出管脚一致;❖一个bank内只允许有一个DCI标准;❖只有一个“分裂标准”能够在一个bank内;❖“一对一标准”和分裂标准可一在一个bank共存。