电子科技大学《微机原理》指定教材课后参考答案

电子科技大学《微机原理》指定教材课后参考答案

电子科技大学《微机原理》指定教材课后参考答案“微机系统原理与接口技术”第八章习题解答(部分)1. 什么叫总线和总线操作?为什么各种微型计算机系统中普遍采用总线结构?答:总线是模块与模块之间传送信息的一组公用信号线;而模块间信息传送时与总线有关的操作统称为总线操作;模块间完成一次完整信息交换的时间称为一个总线操作周期。

总线标准的建立使得各种符合标准的模块可以很方便地挂在总线上,使系统扩展和升级变得高效、简单、易行。

因此微型计算机系统中普遍采用总线结构。

2.微机总线有哪些种类?其数据传输的主要过程是什么?答:微机中目前普遍采用的总线标准包括系统内总线标准和系统外总线标准两类:系统内总线标准一般指微机主板插槽(系统扩展板)遵循的各种标准,如PC/XT总线标准、ISA 总线标准(PC/AT总线标准)、VL总线标准(VESA具备总线标准)、PCI局部总线标准等;系统外总线标准指系统互连时遵循的各种标准,多表现为微机对外的标准接口插头,有时也称为接口标准,如EIA RS-232异步串行接口标准、USB通用串行接口标准、IEEE-488通用并行接口标准等。

一个总线操作周期一般分为四个阶段,即:总线请求及仲裁阶段、寻址阶段、传数阶段和结束阶段。

在含有多个主控制器的微机系统中,这四个阶段都是必不可少的;而在仅含一个主控制器的单处理器系统中,则只需要寻址和传数两个阶段。

3.计算机系统与外部设备之间相互连接的总线称为系统外总线(通信总线);用于连接微型机系统内各插件板的总线称为系统内总线(板级总线);CPU内部连接各寄存器及运算部件之间的总线称为片内总线。

4.一次总线的信息传送过程大致可以分为4个阶段,依次为总线请求及仲裁阶段、寻址阶段、传数阶段和结束阶段。

8.同步总线有哪些优点和缺点?主要用在什么场合?答:同步并行总线时序是指总线上所有信号均以同步时钟为基准,所有接在总线上的设备的信息传输也严格与同步时钟同步。

同步并行总线的优点是简单、易实现;缺点是无法兼容总线上各种不同响应速度的设备,因为同步时钟的速度必须以最慢的响应设备为准,这样总线上的高速设备将无法发挥其高速性能。

微机原理课后习题解答

微机原理习题第一章绪论习题与答案1. 把下列二进制数转换成十进制数、十六进制数及BCD码形式;2 =解:2 = == 1001 0010 0101BCD2. 把下列十进制数转换成二进制数;1 100D =2 1000D =3 =解:1 100D = 01100100B3 =3. 把下列十六进制数转换成十进制数、二进制数;1 2B5H =2 =解:1 2B5H = 693D = 0010 1011 0101B2 = = 0100 1100 0101 B4. 计算下列各式;1 A7H+B8H =2 E4H-A6H =解:1 A7H+B8H = 15FH2 E4H-A6H = 3EH5. 写出下列十进制数的原码、反码和补码;1 +892 -37解:1 +89 原码、反码和补码为: 01011001B6.求下列用二进制补码表示的十进制数101001101补 =解:101001101补 = 77D7.请用8位二进制数写出下列字符带奇校验的ASCII码; 1C: 1000011 2O: 10011113M: 1001101 4P: 1010000解:1C:0 1000011 2O: 0 10011113M:1 1001101 4P: 1 10100008.请用8位二进制数写出下列字符带偶校验的ASCII码; 1+:0101011 2=: 01111013:0100011 4>: 0111110解:1+:0 0101011 2=: 1 01111013:1 0100011 4>: 1 01111109.叙述 CPU 中PC的作用;解:PC是CPU中的程序计数器,其作用是提供要执行指令的地址;第二章微处理器体系与结构习题与答案1. 8086/8088 CPU 由哪两大部分组成请分别叙述它们的功能;解:8086/8088 CPU均由两个独立的逻辑单元组成,一个称为总线接口单元BIUBus Interface Unit,另一个称为执行单元EUExecution Unit;总线接口单元BIU取指令时,从存储器指定地址取出指令送入指令队列排队;执行指令时,根据EU命令对指定存储器单元或I/O端口存取数据;执行单元EU任务是执行指令,进行全部算术逻辑运算、完全偏移地址的计算,向总线接口单元BIU提供指令执行结果的数据和偏移地址,并对通用寄存器和标志寄存器进行管理;2. 8086/8088与传统的计算机相比在执行指令方面有什么不同这样的设计思想有什么优点解:总线接口部分和执行部分是分开的,每当EU执行一条指令时,造成指令队列空出2个或空出一个指令字节时 ,BIU马上从内存中取出下面一条或几条指令,以添满他的指令队列;这样,一般情况下,CPU在执行完一条指令后,便可马上执行下一条指令,不像以往8位CPU那样,执行完一条指令后,需等待下一条指令;即EU从指令队列中取指令、执行指令和BIU补充指令队列的工作是同时进行的;这样大大提高了CPU利用率,降低了系统都对存储器速度的要求;3. 状态标志和控制标志有何不同8086/8088的状态标志和控制标志分别有哪些解:8086/8088 CPU设立了一个两字节的标志寄存器,共九个标志;其中标志位O、S、Z、A、P、C是反映前一次涉及ALU操作结果的状态标志,D、I、T是控制CPU 操作特征的控制标志;4. 8086/8088 CPU寻址存储器时,什么是物理地址逻辑地址它们之间有何关系解:8086/8088系统中每个存储单元都有一个物理地址,物理地址就是存储单元的实际地址编码;在CPU与存贮器之间进行任何信息交换时,需利用物理地址来查找所需要的访问的存储单元;逻辑地址由段地址和偏移地址两部分组成;逻辑地址的表示格式为:段地址:偏移地址;知道了逻辑地址,可以求出它对应的物理地址:物理地址=段地址×10H+偏移地址;5. 段寄存器CS=1200H,指令指针寄存器IP=FF00H,此时,指令的物理地址为多少指向这一物理地址的CS值和IP值是唯一的吗解:根据:物理地址=段地址×10H+偏移地址,指令的物理地址为21F00H;指向这一物理地址的CS值和IP值不唯一;6. 8086 CPU中信号和A0信号是通过怎样的组合解决存储器和外设端口的读/写的这种组合决定了8086系统中存储器偶地址体及奇地址体之间应该用什么信号区分怎样区分解:若存取一个字节的数据,总是用一个总线周期来完成该操作;若存取一个字,则依该字是规则字还是不规则字需用一个或两个总线周期来完成;对规则字,只用一个总线周期来完成16位数据的传送,而对于非规则字则用相邻两个总线周期来完成该字的存储操作,先取其奇地址字节即数据的低位字节,然后存取偶地址字节;在组成存储系统时,总是偶地址单元的数据通过AD0~AD7传送,而奇地址单元的数据通过AD8~AD15传送,即通过总线高字节传送; 信号和A0信号控制存储器读写见下表:7.什么叫总线为什么各种微型计算机系统中普遍采用总线结构答:总线是模块与模块之间传送信息的一组公用信号线;总线标准的建立使得各种符合标准的模块可以很方便地挂在总线上,使系统扩展和升级变得高效、简单、易行;因此微型计算机系统中普遍采用总线结构;8.微型计算机系统总线从功能上分为哪三类它们各自的功能是什么答:微型计算机系统总线从功能上分为地址总线、数据总线和控制总线三类;地址总线用于指出数据的来源或去向,单向;数据总线提供了模块间数据传输的路径,双向;控制总线用来传送各种控制信号或状态信息以便更好协调各功能部件的工作;9.8086/8088 CPU 分为哪两个部分如何协调工作答:EU是执行部件,主要的功能是执行指令和形成有效地址;BIU是总线接口部件,与片外存储器及I/O接口电路传输数据,主要功能是形成实际地址、预取指令和存取操作数;EU经过BIU进行片外操作数的访问,BIU为EU提供将要执行的指令;EU与BIU可分别独立工作,当EU不需BIU提供服务时,BIU可进行填充指令队列的操作;10.8086/8088 CPU的地址总线有多少位其寻址范围是多少答:8086/8088 CPU的地址总线共20 位,最大可寻址1MB空间;11.8086/8088 CPU使用的存储器为什么要分段怎么分段答:8086/8088为16位CPU,其内部的ALU、相关的地址寄存器如SP、IP以及BX、BP、SI、DI等都是16位的,因而对存储器地址的处理也只能是16位操作,即8086/8088的直接寻址能力在64KB范围内;而实际上8086/8088有20条地址线,它的最大寻址空间为1MB;这就产生了一个矛盾,即如何用16位的地址寄存器去表示一个20位的存储器物理地址实际使用的解决办法是:将1MB大小的存储空间分为若干“段”,每段不超过64KB;这样,一个20位的物理地址就可以用“16位段基址:16位偏移量”的形式称为逻辑地址来表示了,其中段地址存放在8086/8088的段寄存器中;12.8086/8088 CPU 中有几个通用寄存器有几个变址寄存器有几个指针寄存器通常哪几个寄存器亦可作为地址寄存器使用答:8086/8088 CPU 中共有:8个16位的通用寄存器AX、BX、CX、DX 、BP、SP、SI、DI;2个变址寄存器SI、DI;2个指针寄存器BP、SP;其中BX、BP、SI、DI 亦可作地址寄存器;13.Intel 8086与8088有何区别答:8086与8088的区别主要表现在以下几个方面:第一、8086的指令队列可以容纳6个字节,每个总线周期在存储器中取出2个字节指令代码填入队列;而8088只能容纳4个字节,且每个总线周期只能取出1个字节指令代码;第二、8086外部数据总线宽度为16位,8088外部数据总线宽度只有8位;注意:8086和8088外部数据总线的宽度不同将导致扩展主存储器及输入/输出接口时系统地址线和数据线连接方式的不同;第三、其他不同的引脚定义:1AD15~AD0,在8086中为地址/数据复用,而在8088中AD15~AD8 改为A15~A8只作地址线用;234、28号引脚定义不同;14.8086/8088CPU工作在最小模式时:当CPU访问存储器时,要利用哪些信号当CPU访问外设接口时,要利用哪些信号答:8086/8088 CPU工作在最小模式时,若访问存储器,需用到以下信号:IOM/、ALE、RDT/、DEN、READY、BHE、W R、RD、AD0~AD15、A19/S6~A16/S3;若访问外设,需用到以下信号:IODT/、DEN、READY、W R、RD、AD0~AD15;M/、ALE、R15.试指出下列运算后的各个状态标志,并说明进位标志和溢出标志的区别:11278H+3469H答:CF=0 AF=1 ZF=0 SF=0 OF=0 PF=1254E3H-27A0H答:CF=0 AF=0 ZF=0 SF=0 OF=0 PF=033881H+3597H答:CF=0 AF=0 ZF=0 SF=0 OF=0 PF=1401E3H-01E3H答:CF=0 AF=0 ZF=1 SF=0 OF=0 PF=1其中,进位标志CF 用于判别无符号数运算是否超出数的表示范围,而溢出标志OF 用于判别带符号数运算是否超出数的表示范围;奇偶标志PF 只能判断结果低8 位中“1”的个数为奇数还是偶数;16.什么是逻辑地址什么是物理地址它们之间有什么联系各用在何处答:逻辑地址由两个16 位的部分即段基址和偏移量组成,一般在程序中出现的地址都表示为逻辑地址形式;物理地址是一个20 位的地址,它是唯一能代表存储空间每个字节单元的地址,一般只出现在地址总线上;由于8086/8088CPU 中的寄存器只有16 位长,所以程序不能直接存放20 位的物理地址,而必须借助逻辑地址,即用两个16 位的寄存器来表示物理地址;他们之间的关系是:物理地址=段基址16+偏移量;另外,一个物理地址可对应多个逻辑地址;17.设现行数据段位于存储器0B0000H~0BFFFFH 单元,DS 段寄存器内容为多少答: DS 段寄存器内容为0B000H;18.在8086中,逻辑地址、偏移地址、物理地址分别指的是什么答:逻辑地址是在程序中对存储器地址的一种表示方法,由段基址和段内偏移地址两部分组成,都是16位的二进制代码,如1234H:0088H;偏移地址是指段内某个存储单元相对该段首地址的差值;物理地址是8086芯片引线送出的20位地址码,物理地址=段基址16+偏移地址,用来指出一个特定的存储单元;19.给定一个存放数据的内存单元的偏移地址是20C0H,DS=0C0E0H,求出该内存单元的物理地址;答:物理地址:0C2EC0H;20.8086/8088为什么采用地址/数据引线复用技术答:考虑到芯片成本和体积,8086/8088采用40条引线的封装结构;40条引线引出8086/8088的所有信号是不够用的,采用地址/数据线复用引线方法可以解决这一矛盾,从逻辑角度,地址与数据信号不会同时出现,二者可以分时复用同一组引线;21.怎样确定8086的最大或最小工作模式答:引线MXMN引线接高电平,8086 MN的逻辑状态决定8086的工作模式,MX被设定为最小模式,MXMN引线接低电平,8086被设定为最大模式;22.8086基本总线周期是如何组成的答:基本总线周期由4个时钟CLK周期组成,按时间顺序定义为T1、T2、T3、T4;23.在基于8086的微计算机系统中,存储器是如何组织的存储器是如何与处理器总线连接的BHE信号起什么作用答:8086为16位微处理器,可访问1M字节的存储器空间;1M字节的存储器分为两个512K字节的存储体,分别命名为偶存储体和奇存储体;偶体的数据线连接D7~D0,“体选”信号接地址线A0;奇体的数据线连接D15~D8,“体选”信号接BHE信号;A0信号有效时允许访问偶体中的低字节存储单元,BHE信号有效时允许访问奇体中的高字节存储单元,实现8086的低字节访问、高字节访问及字访问;24.有一个由20个字组成的数据区,其起始地址为610AH:1CE7H;试写出该数据区首末单元的实际地址PA;首单元地址:610A0H+1CE7H=62D87H末单元地址:62D87H+27H=62DAEH25.有两个16位的字31DAH、5E7FH,它们在8086系统存储器中的地址为00130H 和00135H,试画出它们的存储器示意图;地址00130H00132H00133H00134H00135H00136H26.试说明8086CPU答:8086的低位地址线与数据线复用,为保证地址线维持足够的时间,需使用ALE信号将低位地址线通过锁存器保存,以形成系统地址总线;第三章 80x86指令系统习题与答案1、指出下列指令中操作数的寻址方式8086系统;1 MOV AX,1002 MOV AX,1003 MOV DL,BP+SI4 MOV BX,CX5 MOV DX,SI6 MOV 1234HBX,DS7 MOV DI+5678H,AL 8 MOV 12BPDI,BH9 POP CX 10MOV AX,BX+SI+10解:2、指出下列指令中操作数的寻址方式80386系统;1 MOV EBX+12H,AX2 MOV EBP+EDI2,EBX3 MOV EBX4,BX4 MOV EDX,EAX+ESI8-12H解:3、指出以下指令中,哪些指令是非法的,并说明为什么8086系统;1 PUSH 1234H2 MOV CS,AX3 IN AX, 3004 MOV AX,DX+125 MOV BX,BX6 MOV DS,1000H7 XCHG AL,AL 8 MOV AL,100H9 MOV DX,AL 10LEA BL,BX+511LEA DX,BX 12MOV 1000H,12H13ADD AX,DS 14SUB 0100H,BYTE PTR 000115SHL BL,2 16SHR CL,CL17MUL AL,BL 18INT 400解:1非法,8086系统不允许PUSH指令的操作数为立即数;2非法,MOV指令中CS不能作为目的操作数;3非法,端口号大于0FFH;4非法,DX不能出现在中括号内;5合法;6非法,不能把立即数赋给段寄存器;7合法;8非法,源操作数大于0FFH,不能赋给8位寄存器AL;9非法,源操作数是8位寄存器,目的操作数却是16位寄存器,不匹配;10非法,LEA指令得到的是16位偏移量,但目的操作数是8位寄存器;11非法,LEA指令的源操作数只能是存储器操作数;12非法,指令存在歧义,无法确定传送的是字节还是字;13非法,段寄存器不能参与算术运算;14非法,源和目的寄存器不能同为存储器操作数;15非法,在8086系统中,移位次数大于1时需要将移位次数存放到CL中;16合法;17非法,在8086系统中MUL指令没有双操作数的用法;18非法,中断类型号大于0FFH;4、指出以下指令中,哪些指令是非法的,并说明为什么80386系统;1 MOV AX,12EBXSI162 RCR EAX,103 PUSH 5678H4 POP 1000H5 MOV EAX+EAX,EAX6 MOV AL,ESP+ESP27 MOV BL,AX+12 8 IMUL AL,BL,12解:1非法,比例因子只能是1、2、4、8,不能是16;2合法;3合法;4非法,POP指令的目的操作数不能是立即数;5合法;6非法,ESP只能作为基址寄存器,不能作为变址寄存器;7非法,在386系统中AX不能作为基址寄存器,也不能作为变址寄存器;8合法;5、假设AX=1234H,BX=5678H,SP=1000H,指出执行下面的程序段后,各相关寄存器及堆栈段中的内容;PUSH AX ;AX=,BX=,SP=,栈顶字节SP=, 栈顶第二字节SP+1=PUSH BX ;AX=,BX=,SP=,栈顶字节SP=, 栈顶第二字节SP+1=POP AX ;AX=,BX=,SP=,栈顶字节SP=, 栈顶第二字节SP+1=解:AX=1234H,BX=5678H,SP=0FFEH,栈顶字节SP=34H,栈顶第二字节SP+1=12H AX=1234H,BX=5678H,SP=0FFCH,栈顶字节SP=78H,栈顶第二字节SP+1=56HAX=5678H,BX=5678H,SP=0FFEH,栈顶字节SP=34H,栈顶第二字节SP+1=12H6、假设A、B、C、D、X、Y为字节变量,AA、BB、YY为字变量,试利用算术运算指令编写程序段,完成以下各算术运算题;1计算YY←A+BC,其中A、B、C都是无符号数;2计算AA+BB/C-D,商赋给X,余数赋给Y,其中AA、BB、C、D都是带符号数;3计算YY←A-BC,其中A、B、C都是未组合BCD码;解:1MOV AL,BMUL CADD AL,AADC AH,0MOV YY,AX2MOV AX,AAADD AX,BBMOV BL,CSUB BL,DIDIV BLMOV X,ALMOV Y,AH3MOV AL,ASUB AL,BAASMUL CAAMMOV YY, AX7、利用移位指令编写程序段,实现以下运算;1计算AX←AX10,其中AX为无符号数;232位带符号数存放在寄存器DX和AX中,其中DX存放高16位,AX存放低16位计算DX,AX←DX,AX2;332位带符号数存放在寄存器DX和AX中,其中DX存放高16位,AX存放低16位计算DX,AX←DX,AX/2;解:1SHL AX,1MOV BX,AXSHL AX,1SHL AX,1ADD AX,BX2SAL AX,1RCL DX,13SAR DX,1RCR AX,18、指出以下指令执行后,标志寄存器OF、SF、ZF、AF、PF、CF的状态;1AL=0FFH,BL=20H,执行指令:ADD AL,BL2AL=01H, BL=02H,执行指令:CMP AL,BL3AL=0FFH,执行指令:INC AL4AL=0,执行指令:DEC AL5AL=0F0H,BL=04H,执行指令:IMUL BL6AX=1F0H,BL=08H,执行指令:DIV BL7AL=12H, BL=34H,执行指令:TEST AL,BL8AL=98H,执行指令:SAL AL,1解:注:0表示结果为0,1表示结果为1,×表示结果不变,—表示结果不确定;9、在8086系统下,编写实现如下功能的程序段:1从地址为80H的端口中读入一个字节;2如果该字节最高位为“1”,则将字节0FFH送到地址为81H的端口中,并退出程序;3如果该字节最高位为“0”,则转向第1步,继续循环扫描;解:参考程序段:AGAIN: IN AL, 80HTEST AL, 80HJZ AGAINMOV AL, 0FFHOUT 81H, AL10、我们知道,MOV指令并不能直接修改CS、IP的值,但事实上,我们还可以通过其他方法来达到修改CS、IP的目的;试编写一个程序段,使该程序段运行后,CS=0100H,IP=0000H;解:方法一、利用段间返回指令RETF:MOV AX,0100HPUSH AX ;段基址入栈MOV AX,0PUSH AX ;偏移量入栈RETF方法二、利用JMP指令实现段间跳转,假设ADDR为双字变量:MOV WORD PTR ADDR,0 ;WORD PTR ADDR←偏移量MOV WORD PTR ADDR+2, 0100H ;WORD PTR ADDR+2←段基址JMP DWORD PTR ADDR11.写出能完成下述操作的指令;1将立即数1234H 送至DS 寄存器;2将存储单元3000H 和内容送至4000H 单元;3将累加器AX 与寄存器CX 中的内容对调;答案:1MOV AX, 1234HMOV DS, AX2 MOV AX, 3000HMOV 4000H, AX3 XCHG AX, CX12.编程:将数据段中以BX 为偏移地址的连续4 单元的内容颠倒过来;答案:MOV AL, BXXCHG AL, BX+3MOV BX, ALMOV AL,BX+1XCHG AL, BX+2MOV BX+1, AL13.将AX 寄存器清零有4 种方法,试写出这4 条指令;答案:MOV AX, 00HSUB AX, AXAND AX, 00HXOR AX, AX14.使用一条逻辑运算指令实现下列要求:1使AL 高4 位不变,低4 位为0; 2使AL 最高位置1,后7 位不变; 3使AL 中的bit3、bit4 变反,其余位不变; 4测试判断CL 中的bit2、bit5、bit7 是否都为1;答案:1 AND AL, 0F0H2OR AL, 80H3XOR AL 18H4TEST AL, 0A4H15.试分析下面的程序段完成什么功能;MOV CL, 4SHL AX, CLSHL BL, CLMOV AL, BLSHR DH, CLOR AL, DH答案:将AX 中间8 位,BX 的低 4 位,DX 的高 4 位组成一个新字存放在AX 中;16.若要将源串100 个字节数据传送到目标串单元中去,设源串首址的偏移地址为2500H, 目标串首址的偏移地址为1400H,请编写程序实现以下功能; 1完成源串到目标串的搬移; 2比较两串是否完全相同,若两串相同,则BX 寄存器内容为0;若两串不同,则BX 指向源串中第一个不相同字节的地址,且该字节的内容保留在AL 的寄存器中;答案: 1 CLDMOV CX, 100MOV SI, 2500HMOV DI, 1400HREP MOVSB2 CLDMOV CX, 100MOV SI, 2500MOV DI, 1400REPE CMPSBJZ EDEC SIMOV BX, SIMOV AL, SIJMP STOPE: MOV BX, 0STOP: HLT17.设若标志寄存器原值为0A11H,SP=0060H,AL=4;下列几条指令执行后,标志寄存器、AX、SP的值分别是多少PUSHFLAHFXCHG AH,ALPUSH AXSAHFPOPF答:指令执行后标志寄存器的值为0411H,AX=0411H ,SP=005EH;18.假如在程序的括号中分别填入指令:1 LOOP L202 LOOPNE L203 LOOPE L20试说明在三种情况下, 当程序执行完后, AX、BX、CX、DX四个寄存器的内容分别是什么BEGIN: MOV AX,01MOV BX,02MOV DX,03MOV CX,04L20: INC AXADD BX,AXSHR DX,1答案: 1AX= 5 BX= 16 CX= 0 DX= 02AX= 3 BX= 7 CX= 2 DX= 03AX= 2 BX= 4 CX= 3 DX= 119.变量N1和N2均为2字节的非压缩BCD数码,请写出计算N1与N2之差的指令序列;答案:MOV AX, 0MOV AL, N1SUB AL, N2AASMOV DL, ALMOV AL, N1+1SBB AL, N2+1AASMOV DH, AL20.在已学的指令中,可实现累加器清0的单条指令有哪些比较它们的功能;答:1MOV AX,0 ;仅将累加器清0,不会影响任何标志位2SUB AX,AX ;累加器清0的同时影响所有状态标志,具体地有:ZF、PF置1,CF、AF、SF、OF均清03AND AX,0 ;将累加器清0,ZF、PF置1,CF、OF、SF清04XOR AX,AX ;将累加器清0,ZF、PF置1,CF、OF、SF清021.已知DS=2000H,有关的内存单元值为:21000H=00H,21001H=12H,21200H=00H,21201H=10H,23200H=20H,23201H=30H,23 400H=40H,23401H=30H,23600H=60H,23601H=30H,符号COUNT的偏移地址为1200H;执行下列指令后,寄存器AX、BX、SI的值分别是多少MOV BX,OFFSET COUNTMOV SI,BXMOV AX,COUNTSIBX答:执行结果为BX=1200H,SI=1000H,AX=3040H;22.设若内存单元DATA在数据段中偏移量为24C0H处,24C0H~24C3H单元中依次存放着55H、66H、77H、88H;下列几条指令执行后,寄存器AX、BX、CL、SI、DS的值分别是多少MOV AX,DATALEA SI,DATAMOV CL,SILDS BX,DATA答:执行结果为AX=6655H,BX=6655H,CL=55H,SI=24C0H,DS=8877H;23.若AX=26D3H,CX=7908H,CF=1,执行下列指令后,寄存器AX、CX的值分别是多少CF=OF=SAL CH,1RCR AX,CLROL AL,1答:执行结果为AX=0A64CH,CX=0F208H,CF=OF=0;24.已知有程序段如下:MOV AL,35HMOV DL,ALAND DL,0FHAND AL,0F0HMOV CL,4SHR AL,CLMOV BL,10MUL BLADD AL,DL执行之后,AL的值等于多少该程序段完成了什么功能答:程序段执行后AL=23H;该程序段实现了将AL中的1个组合BCD码转换为十六进制数并存回AL中的功能;25.下面的程序执行后,DX、AX的值分别是多少;以X为首址的字单元中的数据依次为1234H、5678H;以Y为首址的字单元中的数据依次为8765H、4321HLEA SI,XLEA DI,YMOV DX,SI+2MOV AX,XADD AX,XADC DX,SI+2CMP DX,DI+2JL L2CMP AX,YJL L1JMP EXITL1: MOV AX,1JMP EXITL2: MOV AX,2EXIT:……答:执行结果为AX=2,DX=0ACF0H;26.设VAR字单元的值为x,F1字单元的值为y,试编程按以下要求给y赋值:2 x>30y = 0 30≥x≥1-2 x<1答:一种可能的程序段实现如下:MOV AX,VAR ;AX xCMP AX,30JG PLUS2 ;x>30,则转PLUS2CMP AX,1JL MIN2 ;x<1,则转MIN2MOV F1,0 ;30≥x≥1,y=0JMP GOPLUS2:MOV F1,2 ;y=2JMP GOMIN2: MOV F1,-2 ;y = -2或00FEHGO:……;后续处理简析:本例中并未说明VAR字节单元是带符号数还是无符号数,读者在使用判断转移指令时可任意选用;若当作带符号数,应使用JG、JL、JGE、JLE等指令,如参考程序;若当作无符号数,则应使用JA、JB、JAE、JBE等指令;第四章 80x86汇编语言程序设计习题与答案1、指出以下数据定义伪指令所分配的字节数8086系统; 1DATA1 DB 10,,‘A’2DATA2 DW 10 DUP2,3 DUP,13DATA3 DB ‘HELLO,WORLD’,‘$’4DATA4 DW DATA4解:13字节;2100字节;313字节;42字节;2、指出以下数据定义伪指令所分配的字节数80386系统; 1DATA1 DF 12,34,562DATA2 DF DATA23DATA3 DQ 0,10 DUP4DATA4 DT 0,1,2解:118字节;36字节; 388字节;430字节;3、指出以下指令中哪些是无效的,并说明原因;1ADDR DB $2DATA DB F0H,12H31_DATA DW 1234H4VAR DW VAR1 ;VAR1为一个字节变量5MOV AX,10-VAR1 ;VAR1为一个字变量6MOV BX,VAR22+1 ;VAR2为一个字变量解:1非法,地址计数器$是32位数;2非法,以字母开头的16进制数应在前面加“0”,即应为“0F0H”;3非法,变量名非法,不能以数字开头;4合法;5非法,地址表达式不能是“常数-地址”;6非法,地址表达式不能出现乘法;4、假设已定义数据段如下:DATA SEGMENTORG 100HDATA1 DB 10 DUP1,2,3DATA2 DW DATA1,$DATA ENDS且段寄存器DS已初始化为该数据段的段基址假设段基址为1234H;请指出以下指令执行后,相应的寄存器中的内容;1MOV AX,WORD PTR DATA1 ;AX=2MOV BX,DATA2 ;BX=3MOV CX,DATA2+2 ;CX=4MOV DX,OFFSET DATA2 ;DX=5MOV SI,SEG DATA1 ;SI=6MOV DI,LENGTH DATA1 ;DI=7MOV SP,TYPE DATA1 ;SP=8MOV BP,SIZE DATA2 ;BP=解:1AX=0201H;2BX=0100H;3CX=0120H;4DX=011EH;5SI=1234H;6DI=000AH;7SP=0001H;8BP=0002H;5、在8086系统下,编写完整程序,实现从键盘上输入8位二进制数,从显示器上显示相应的16进制数,例如从键盘上输入“00010010”,应在显示器上显示“12H”; 解:参考程序:DATA SEGMENTMSG1 DB 'Input binary numberESC to exit:','$'MSG2 DB 0AH,0DH,'Input error',0AH,0DH,'$'DATA ENDSOUTPUT MACRO ASC ;定义输出一个字符的宏MOV DL, ASCMOV AH, 2INT 21HENDMCODE SEGMENTASSUME CS:CODE, DS:DATAMAIN PROC FARPUSH DSMOV AX, 0PUSH AXMOV AX, DATAMOV DS, AXAGAIN: LEA DX, MSG1MOV AH, 9INT 21H ;提示输入信息MOV CX, 8 ;输入8位二进制数MOV BL, 0L: MOV AH, 1INT 21HSHL BL, 1CMP AL, 1BH ;ESC键退出JZ DONECMP AL, '0' ;输入“0”JZ NEXTCMP AL, '1' ;输入“1”JNZ ERROR ;输入其他则出错INC BLNEXT: LOOP LOUTPUT 0AHOUTPUT 0DHPUSH BXMOV CL, 4SHR BL, CLCALL TRAN ;显示高4位对应的16进制数POP BXAND BL, 0FHCALL TRAN ;显示低4位对应的16进制数OUTPUT 'H'OUTPUT 0AHOUTPUT 0DHJMP AGAINERROR: LEA DX, MSG2MOV AH, 9INT 21HJMP AGAINDONE: RETMAIN ENDPTRAN PROC FARCMP BL, 0AHJB BELOWADD BL, 7BELOW: ADD BL, 30HOUTPUT BLRETTRAN ENDPCODE ENDSEND MAIN6、在8086系统下,编写完整程序,实现从键盘上输入两个4位十进制数,从显示器上显示这两个数之和,例如输入“1234”、“5678”,应在显示器上显示“6912”; 解:参考程序:DATA SEGMENTMSG1 DB 'Input the first numberESC to exit:','$'MSG2 DB 'Input the second numberESC to exit:','$'MSG3 DB 0AH,0DH,'Input errorInput again:','$'DATA ENDSOUTPUT MACRO ASC ;定义输出一个字符的宏MOV DL, ASCMOV AH, 2INT 21HENDMCODE SEGMENTASSUME CS:CODE, DS:DATAMAIN: MOV AX, DATAMOV DS, AXAGAIN: LEA DX, MSG1MOV AH, 9INT 21H ;提示输入第一个数CALL INPUT ;输入过程PUSH BXOUTPUT 0AHOUTPUT 0DHLEA DX, MSG2MOV AH, 9INT 21H ;提示输入第二个数CALL INPUT ;输入过程OUTPUT 0AHOUTPUT 0DHPOP AX ;实现两个4位组合BCD码相加ADD AL, BL ;低8位相加DAA ;校正MOV CL, AL ;保存至CLADC AH, BH ;高8位相加MOV AL, AH ;移至ALDAA ;校正MOV AH, ALMOV AL, CLMOV BX, AX ;最后结果放在BX中JNC NEXTOUTPUT '1' ;如果相加结果大于9999,则显示进位“1”NEXT: PUSH BXMOV CL, 4SHR BH, CLADD BH, 30HOUTPUT BH ;显示千位数POP BXPUSH BXAND BH, 0FHADD BH, 30HOUTPUT BH ;显示百位数POP BXPUSH BXMOV CL, 4SHR BL, CLADD BL, 30HOUTPUT BL ;显示十位数POP BXAND BL, 0FHADD BL, 30HOUTPUT BL ;显示个位数OUTPUT 0AHOUTPUT 0DHJMP AGAININPUT PROC FAR ;输入一个4位十进制数的过程BEGIN: MOV CX, 4MOV BX, 0L: SHL BX, 1SHL BX, 1SHL BX, 1SHL BX, 1 ;BX的值乘以16MOV AH, 1INT 21H ;输入CMP AL, 1BH ;ESC键退出JZ DONECMP AL, '0'JB ERROR ;非数字,出错CMP AL, '9'JA ERROR ;非数字,出错SUB AL, 30HXOR AH, AHADD BX, AX ;将输入加到BX中LOOP LRETERROR: LEA DX, MSG3MOV AH, 9INT 21HJMP BEGINDONE: MOV AH, 4CHINT 21HINPUT ENDPCODE ENDSEND MAIN7、在8086系统下,编写完整程序,实现两个32位带符号数相乘;假设被乘数存放在以字变量MUL1开始的连续4个字节中,乘数存放在以字变量MUL2开始的连续4个字节中中,相乘结果存放在以字变量RES开始的连续8个字节中;解:参考程序:DATA SEGMENTMUL1 DW 0FFFFH,0FFFFH ;被乘数MUL2 DW 5678H,1234H ;乘数RES DW 4 DUP0 ;结果DATA ENDSCODE SEGMENTASSUME CS:CODE, DS:DATAMAIN PROC FARPUSH DSMOV AX, 0PUSH AXMOV AX, DATAMOV DS, AXMOV CX, MUL1MOV BP, MUL1+2MOV SI, MUL2MOV DI, MUL2+2TEST BP, 8000H ;被乘数是否为负数JZ NEXT1NOT BP ;为负数,则取反加1 NOT CXADD CX, 1ADC BP, 0NEXT1: TEST DI, 8000H ;乘数是否为负数JZ NEXT2NOT SI ;为负数,则取反加1 NOT DIADD SI, 1ADC DI, 0NEXT2: MOV AX, SI ;相乘过程MUL CXMOV RES, AXMOV AX, SIMUL BPADD RES+2, AXADC RES+4, DXMOV AX, DIMUL CXADD RES+2, AXADC RES+4, DXMOV AX, DIMUL BPADD RES+4, AXADC RES+6, DXMOV AX, MUL1+2XOR AX, MUL2+2 ;判断被乘数和乘数是否同号JNS DONE ;同号,则结果为正数,无须修改结果NOT RES ;不同号,则结果为负数,须取反加1 NOT RES+2NOT RES+4NOT RES+6ADD RES, 1ADC RES+2, 0ADC RES+6, 0DONE: RETMAIN ENDPCODE ENDSEND MAIN8、在8086系统下,编写完整程序,找出字节数组ARRAY中的最大值和最小值;假设ARRAY的长度为100个字节,每个字节为一个无符号数,程序执行后最大值将存放到字节变量MAX中,最小值则存放到字节变量MIN中;解:参考程序:DATA SEGMENTARRAY DB 100 DUP ;字节数组MAX DB ;最大值MIN DB ;最小值DATA ENDSCODE SEGMENTASSUME CS:CODE, DS:DATAMAIN PROC FARPUSH DSMOV AX, 0PUSH AXMOV AX, DATAMOV DS, AXLEA SI, ARRAYCLDMOV BH, 0 ;存放临时最大值的寄存器MOV BL, 0FFH ;存放临时最小值的寄存器MOV CX, 100AGAIN: LODSBCMP AL, BHJNA NEXT1MOV BH, AL ;如果当前数值比临时最大值大,则代替NEXT1: CMP AL, BLJNB NEXT2MOV BL, AL ;如果当前数值比临时最小值小,则代替NEXT2: LOOP AGAINMOV MAX, BHMOV MIN, BLRETMAIN ENDPCODE ENDSEND MAIN9、在8086系统下,编写完整程序,将字节数组ARRAY中的所有数据往高地址的方向移动一位,即原来存放在ARRAY中的字节移动到ARRAY+1中,原来存放在ARRAY+1中的字节移动到ARRAY+2中,……,依此类推;假设ARRAY的长度为100个字节; 解:可利用MOVSB指令实现移位,但应该注意,必须从串尾开始移动,因为假如直接从串头开始,将串头移到第二个数,那么第二个数将被覆盖;为使程序能从串尾开始移动,可令方向标志位DF=1;参考程序:DATA SEGMENTARRAY DB 100 DUP,DATA ENDSCODE SEGMENTASSUME CS:CODE, DS:DATAMAIN PROC FARPUSH DSMOV AX, 0PUSH AXMOV AX, DATAMOV DS, AXMOV ES, AXLEA SI, ARRAY+99 ;SI指向源串尾LEA DI, ARRAY+100 ;DI指向新串尾STD ;DF=1,串尾先移动MOV CX, 100REP MOVSB ;循环移动RETMAIN ENDPCODE ENDSEND MAIN10、在8086系统下,编写在长字符串L_STR中查找短字符串S_STR的完整程序,如果找到匹配的字符串,则将字节变量RES置0FFH,否则置0;例如,在字符串“ABABCD”中可找到字符串“ABC”,则RES=0FFH;解:参考程序:DATA SEGMENTL_STR DB 'ABDABABCD' ;长串L_LTH DW $-L_STR ;长串长度S_STR DB 'ABC' ;短串S_LTH DW $-S_STR ;短串长度RES DB ;存放结果DATA ENDSCODE SEGMENTASSUME CS:CODE, DS:DATAMAIN PROC FARPUSH DSMOV AX, 0PUSH AXMOV AX, DATAMOV DS, AXMOV ES, AXLEA SI, L_STRLEA DI, S_STRCLDMOV CX, L_LTHSUB CX, S_LTHINC CX ;作串比较的次数AGAIN: CALL COMP ;进行串比较INC SILOOP AGAINMOV RES, 0RETMAIN ENDPCOMP PROC FARPUSH CXPUSH SIPUSH DIMOV CX, S_LTHREPZ CMPSBJZ YES ;如果两个串相同,则说明找到POP DIPOP SIPOP CXRETYES: MOV RES, 0FFHMOV AH, 4CHINT 21HCOMP ENDPCODE ENDSEND MAIN11.执行下列指令后,AX寄存器中的内容是什么TABLE DW 10,20,30,40,50ENTRY DW 3..MOV BX,OFFSET TABLEADD BX,ENTRYMOV AX,BX答:AX=4012.指出下列程序中的错误:STAKSG SEGMENTDB 100 DUPSTA_SG ENDSDTSEG SEGMENTDATA1 DBDTSEG ENDCDSEG SEGMENTMAIN PROC FARSTART: MOV DS,DATSEGMOV AL,34HADD AL,4FHMOV DATA,ALSTART ENDPCDSEG ENDSEND答案:改正后:。

微机原理课后习题答案

微机原理课后习题答案1.3 微型计算机采⽤总线结构有什么优点?解:采⽤总线结构,扩⼤了数据传送的灵活性、减少了连接。

⽽且总线可以标准化,易于兼容和⼯业化⽣产。

2.6 IA-32结构微处理器⽀持哪⼏种操作模式?解:IA-32结构⽀持3种操作模式:保护模式、实地址模式和系统管理模式。

操作模式确定哪些指令和结构特性是可以访问的。

2.14 8086微处理器的总线接⼝不接有哪些功能?请逐⼀说明。

解:总线接⼝单元(BIU)负责与存储器接⼝;执⾏单元(EU)执⾏各种操作。

BIU主要由段寄存器、指令指针、加法器(形成20位地址)和预取的指令流队列等组成。

2.15 8086微处理器的总线接⼝不见由哪⼏部分组成?解:8086微处理器中的总线接⼝单元(BIU)负责CPU与储存器之间的信息传送。

具体地说,BIU既负责从内存的指令部分取出指令,送⾄指令队列中排队(8086的指令队列有6个字节,⽽8088的指令队列只有4个字节);也负责传送执⾏指令时所需的操作数。

执⾏单元(EU)负责执⾏指令规定的操作。

2.16 段寄存器CS=1200H,指令指针寄存器IP=FF00H,此时,指令的物理地址为多少?解:指令的物理地址=12000h+FF00H=21F00H2.17 8086微处理器的执⾏部件有什么功能?由哪⼏部分组成?解:8086微处理器的执⾏部件负责指令的执⾏。

它主要由算术逻辑单元、标志寄存器和通⽤寄存器等部分组成。

附:8086CPU从功能上分包括⼏部分,各有什么功能?3.3 写出下指令中内存操作数的所在地址。

(1)MOV AL,[BX+10](2)MOV [BP+10],AX(3)INC BYTE PTR[SI+5](4)MOV DL,ES:[BX+SI](5)MOV BX,[BP+DI+2]解:(1)数据段BX+10单元(2)堆栈段BP+10单元(3)数据段SI+5字节单元(4)附加段(ES段)BX+SI单元(5)堆栈段BP+DI+2单元3.4 判断下列指令书写是否正确。

电子科大-微机原理习题解答-chap4

Chapter44.1 阐述总线的概念。

计算机系统为什么需要采用总线结构?总线是计算机系统中的信息传输通道,由系统中各个部件所共享。

总线的特点在于公用性,总线由多条通信线路(线缆)组成采用总线结构,能:减少部件间连线的数量;扩展性好,便于构建系统;便于产品更新换代4.3 微机系统中总线层次化结构是怎样的?按总线所处位置可分为:片内总线、系统内总线、系统外总线。

按总线功能可分为:地址总线、数据总线、控制总线。

按时序控制方式可分为:同步总线、异步总线。

按数据格式可分为:并行总线、串行总线。

4.4 评价一种总线的性能有那几个方面?总线时钟频率、总线宽度、总线速率、总线带宽、总线的同步方式和总线的驱动能力等。

4.5 微机系统什么情况下需要总线仲裁?总线仲裁有哪几种?各有什么特点?总线仲裁又称总线判决,其目的是合理的控制和管理系统中多个主设备的总线请求,以避免总线冲突。

当多个主设备同时提出总线请求时,仲裁机构按照一定的优先算法来确定由谁获得对总线的使用权。

集中式(主从式)控制和分布式(对等式)控制。

集中式特点:采用专门的总线控制器或仲裁器分配总线时间,总线协议简单有效,总体系统性能较低。

分布式特点:总线控制逻辑分散在连接与总线的各个模块或设备中,协议复杂成本高,系统性能较高。

4.6总线传输方式有哪几种?同步总线传输对收发模块有什么要求?什么情况下应该采用异步传输方式,为什么?总线传输方式按照不同角度可分为同步和异步传输,串行和并行传输,单步和突发方式。

同步总线传输时,总线上收模块与发模块严格按系统时钟来统一定时收发模块之间的传输操作。

异步总线常用于各模块间数据传送时间差异较大的系统,因为这时很难同步,采用异步方式没有固定的时钟周期,其时间可根据需要可长可短。

4.7 AMBA总线定义了哪三种总线?他们各有什么特点?先进高性能总线AHB,先进系统总线ASB,先进外设总线APBAHB适用于高性能和高吞吐设备之间的连接,如CPU、片上存储器、DMA设备、DSP等。

微机原理课后习题参考答案

微机原理课后习题参考答案第1部分微型计算机基础知识1.1 微处理器、微型计算机和微型计算机系统三者之间有什么不同?【解】微处理器:指计算机内部对数据进行处理并对处理过程进行控制的部件,伴随着大规模集成电路技术的迅速发展,芯片集成密度越来越高,CPU可以集成在一个半导体芯片上,这种具有中央处理器功能的大规模集成电路器件,被统称为“微处理器”。

微型计算机:简称“微型机”、“微机”,也称“微电脑”。

由大规模集成电路组成的、体积较小的电子计算机。

由微处理机(核心)、存储片、输入和输出片、系统总线等组成。

特点是体积小、灵活性大、价格便宜、使用方便。

微型计算机系统:简称“微机系统”。

由微型计算机、显示器、输入输出设备、电源及控制面板等组成的计算机系统。

配有操作系统、高级语言和多种工具性软件等。

1.2 CPU在内部结构上由哪几部分组成?CPU应该具备哪些主要功能?【解】CPU在内部结构上由运算器、控制器、寄存器阵列和内部总线等各部分构成,其主要功能是完成各种算数及逻辑运算,并实现对整个微型计算机控制,为此,其内部又必须具备传递和暂存数据的功能。

1.3 微型计算机采用总线结构有什么优点?【解】①简化了系统结构,便于系统设计制造;②大大减少了连线数目,便于布线,减小体积,提高系统的可靠性;③便于接口设计,所有与总线连接的设备均采用类似的接口;④便于系统的扩充、更新与灵活配置,易于实现系统的模块化;⑤便于设备的软件设计,所有接口的软件就是对不同的口地址进行操作;⑥便于故障诊断和维修,同时也降低了成本。

总线的逻辑电路有些是三态的,即输出电平有三种状态:逻辑“0”,逻辑“1”和“高阻”态。

1.4计算机总线有哪些,分别是什么?【解】总线按其信号线上传输的信息性质可分为三组:①数据总线,一般情况下是双向总线;②地址总线,单向总线,是微处理器或其他主设备发出的地址信号线;③ 控制总线,微处理器与存储器或接口等之间1.5 数据总线和地址总线在结构上有什么不同之处?如果一个系统的数据和地址合用一套总线或者合用部分总线,那么要靠什么来区分地址和数据?【解】数据总线(DB)为双向结构,数据在CPU与存储器或I/O 接口之间的传送是双向的,(数据既可以读也可以写),其宽度通常与微处理器的字长相同。

电子科大-微机原理习题解答-chap3

电⼦科⼤-微机原理习题解答-chap3“微处理器系统原理与嵌⼊式系统设计”第三章习题解答3.1处理器有哪些功能?说明实现这些功能各需要哪些部件,并画出处理器的基本结构图。

处理器的基本功能包括数据的存储、数据的运算和控制等功能。

其有5个主要功能:①指令控制②操作控制③时间控制④数据加⼯⑤中断处理。

其中,数据加⼯由ALU、移位器和寄存器等数据通路部件完成,其他功能由控制器实现。

处理器的基本结构图如下:3.2处理器内部有哪些基本操作?这些基本操作各包含哪些微操作?处理器内部的基本操作有:取指、间接、执⾏和中断。

其中必须包含取指和执⾏。

取指包含微操作有:经过多路器把程序计数器的值选送到存储器,然后存储器回送所期望的指令并将其写⼊指令寄存器,与此同时程序计数器值加1,并将新值回写⼊程序计数器。

间接有4个CPU周期,包含微操作有:第1周期把指令寄存器中地址部分的形式地址转到地址寄存器中;第2周期完成从内存取出操作数地址,并放⼊地址寄存器;第3周期中累加器内容传送到缓冲寄存器,然后再存⼊所选定的存储单元。

执⾏包含微操作有:在寄存器中选定⼀个地址寄存器,并通过多路器将值送到存储器;来⾃于存储器的数据作为ALU的⼀个原操作数,另⼀个原操作数则来⾃于寄存器组中的数据寄存器,它们将⼀同被送往ALU的输⼊;ALU的结果被写⼊寄存器组。

中断包含微操作有:保护断点及现场,查找中断向量表以确定中断程序⼊⼝地址,修改程序指针,执⾏完毕后恢复现场及断点。

3.3什么是冯·诺伊曼计算机结构的主要技术瓶颈?如何克服?冯·诺伊曼计算机结构的主要技术瓶颈是数据传输和指令串⾏执⾏。

可以通过以下⽅案克服:采⽤哈佛体系结构、存储器分层结构、⾼速缓存和虚拟存储器、指令流⽔线、超标量等⽅法。

3.5指令系统的设计会影响计算机系统的哪些性能?指令系统是指⼀台计算机所能执⾏的全部指令的集合,其决定了⼀台计算机硬件主要性能和基本功能。

指令系统⼀般都包括以下⼏⼤类指令。

电子科大-微机原理习题解答-chap5

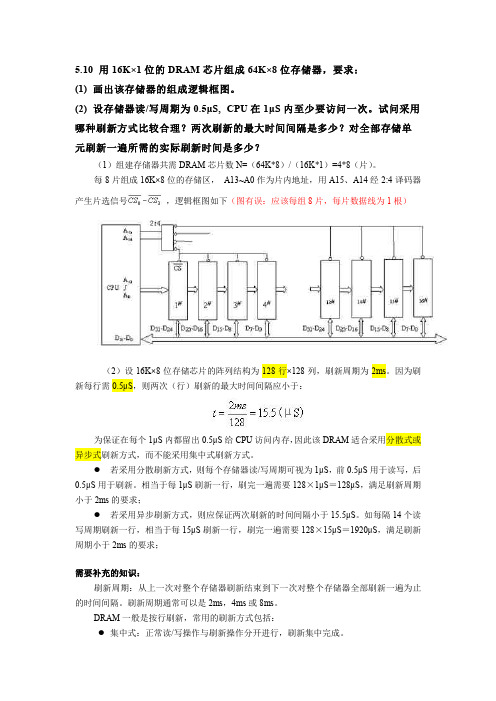

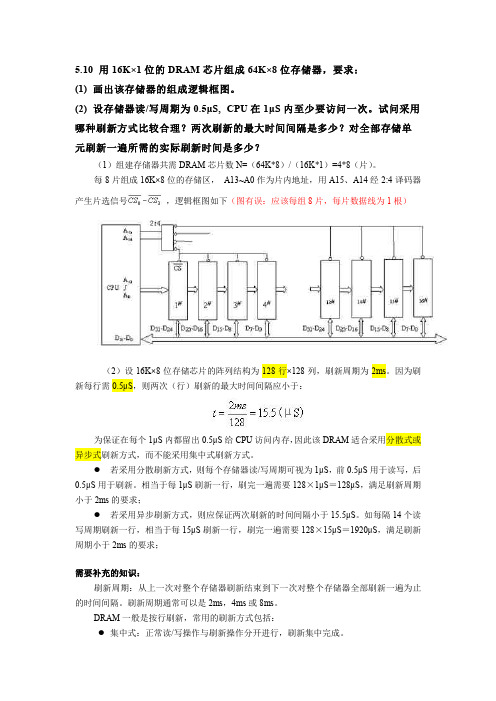

l 若采用分散刷新方式,则每个存储器读/写周期可视为 1μS,前 0.5μS 用于读写,后 0.5μS 用于刷新。相当于每 1μS 刷新一行,刷完一遍需要 128×1μS=128μS,满足刷新周期 小于 2ms 的要求;

的时间间隔。刷新周期通常可以是 2ms,4ms 或 8ms。 DRAM 一般是按行刷新,常用的刷新方式包括: l 集中式:正常读/写操作与刷新操作分开进行,刷新集中完成。

特点:存在一段停止读/写操作的死时间,适用于高速存储器。

(DRAM 共 128 行,刷新周期为 2ms,读/写/刷新时间均为 0.5μS) l 分散式:一个存储系统周期分成两个时间片,分时进行正常读/写操作和刷新操作。

查阅资料可知,2732 容量为 4K×8(字选线 12 根),6264 容量为 8K×8(字选线 13 根),

因此本系统中所需芯片数目及各芯片地址范围应如下表所示:

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1

共需 2 片 第一片 0000H~ 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 2732 构成系 地址范围 0FFFH 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1

地址范围 3FFFH 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1

其连线图如下:

方案一:

方案二:

5.13 试为某 8 位计算机系统设计一个具有 8KB ROM 和 40KB RAM 的存储 器。要求 ROM 用 EPROM 芯片 2732 组成,从 0000H 地址开始;RAM 用 S RAM 芯片 6264 组成,从 4000H 地址开始。

微型计算机原理课后习题答案,王忠民主编,DOC

王忠民主编西安电子科技大学出版部分习题答案第二章计算机中的数值和编码1、将十进制数转换为二进制和十六进制(1)129.75=10000001.11B=81.CH(2)218.8125=11011010.1101B=2、3451F.2H=103.CEH(3) 18.9+1010.1101B+12.6H-1011.1001=36.5256、选取字长n为8位和16位两种情况,求下列十进制数的补码。

(1) X=-33的补码:1101(2) Y=+33的补码:00100001,0000000000100001(3) Z=-128的补码:10000000,1111111110000000(4) N=+127的补码:01111111,0000000001111111(5) A=-65的补码:10111111,11111111101111117=-=+=-=+8并判断结果是否溢出。

(1)43+8∵ [43]补=00101011B,[8]补=00001000B∴ [43]补+[8]补=00101011B+00001000B=00110011B=33H00101011B+00001000B00110011B∵C S=0,C D=0,OF=C S⊕C D=0⊕0=0∴无溢出(无(溢9z=?,10111000B①若为无符号数②若为带符号补码数∵CF=1 ∴不正确∵CF=1,DF=1 OF=0∴不溢出x+y=0B8H x+z=61H y+z=3BH z+v=0CCH①不正确不正确不正确正确②不溢出不溢出不溢出溢出第三章80X86微处理器1.简述8086/8088CPU中BIU和EU的作用,并说明其并行工作过程。

答:(1)BIU的作用:计算20位的物理地址,并负责完成CPU与存储器将从内2.4BX(Base)称为基址寄存器。

用来存放操作数在内存中数据段内的偏移地址,CX(Counter)称为计数器。

在设计循环程序时使用该寄存器存放循环次数,可使程序指令简化,有利于提高程序的运行速度。

电子科大微机原理(新教材)1-4章习题答案

“微处理器系统原理与嵌入式系统设计”第一章习题解答1.1 什么是程序存储式计算机?程序存储式计算机指采用存储程序原理工作的计算机。

存储程序原理又称“冯·诺依曼原理”,其核心思想包括:●程序由指令组成,并和数据一起存放在存储器中;●计算机启动后,能自动地按照程序指令的逻辑顺序逐条把指令从存储器中读出来,自动完成由程序所描述的处理工作。

1.2 通用计算机的几个主要部件是什么?●主机(CPU、主板、内存);●外设(硬盘/光驱、显示器/显卡、键盘/鼠标、声卡/音箱);1.3 以集成电路级别而言,计算机系统的三个主要组成部分是什么?中央处理器、存储器芯片、总线接口芯片1.4 阐述摩尔定律。

每18个月,芯片的晶体管密度提高一倍,运算性能提高一倍,而价格下降一半。

1.5 讨论:摩尔定律有什么限制,可以使用哪些方式克服这些限制?摩尔定律还会持续多久?在摩尔定律之后电路将如何演化?摩尔定律不能逾越的四个鸿沟:基本大小的限制、散热、电流泄露、热噪。

具体问题如:晶体管体积继续缩小的物理极限,高主频导致的高温……解决办法:采用纳米材料、变相材料等取代硅、光学互联、3D、加速器技术、多内核……(为了降低功耗与制造成本,深度集成仍是目前半导体行业努力的方向,但这不可能永无止,因为工艺再先进也不可能将半导体做的比原子更小。

用作绝缘材料的二氧化硅,已逼近极限,如继续缩小将导致漏电、散热等物理瓶颈,数量集成趋势终有终结的一天。

一旦芯片上线条宽度达到纳米数量级时,相当于只有几个分子的大小,这种情况下材料的物理、化学性能将发生质的变化,致使采用现行工艺的半导体器件不能正常工作,摩尔定律也就要走到它的尽头了。

业界专家预计,芯片性能的增长速度将在今后几年趋缓,一般认为摩尔定律能再适用10年左右,其制约的因素一是技术,二是经济。

)1.6 试以实例说明计算机系统结构、计算机组成与计算机实现之间的相互关系与相互影响。

计算机系统结构主要是指程序员关心的计算机概念结构与功能特性,而计算机组成原理则偏重从硬件角度关注物理机器的组织,更底层的器件技术和微组装技术则称为计算机实现。

微机原理课后习题参考答案

微机原理课后习题参考答案第一章2、完成下列数制之间的转换。

01011100B=92D135D=10000111B 10110010B=262Q=B2H 3、组合型BCD码和非组合型BCD码有什么区别?写出十进制数254的组合型BCD数和非组合型数。

答:组合型BCD码用高四位和低四位分别对应十进制数的个位和十位,其表示范围是0~99;非组合型BCD码用一个字节的低四位表示十进制数,高四位则任意取值,表示范围为0~9。

组合型:254=BCD 非组合型:254=BCD 7、计算机为什么采用补码形式存储数据?当计算机的字长n=16,补码的数据表示范围是多少?答:在补码运算过程中,符号位参加运算,简化了加减法规则,且能使减法运算转化为加法运算,可以简化机器的运算器电路。

+32767~ -32768。

9、设计算机字长n=8,求下列各式的[X+Y]补和[X-Y]补,并验证计算结果是否正确。

X=18,Y=89 [X+Y]补=00010010+01011001=01101011B=107D 正确[X-Y]补=10111001B=00010010+10100111=补正确X=-23,Y=-11 [X+Y]补=11101001+11110101=11011110B=补正确[X-Y]补=11101001+00001011=11110100B=补正确X=18,Y=-15 [X+Y]补=00010010+11110001=00000011B=补正确[X-Y]补=00010010+00001111=00100001B=补正确X=-18,Y=120 [X+Y]补=11101110+01111000=01100110B=补正确[X-Y]补=11101110+10001000=01110110B=补于X-Y=-138 超出了机器数范围,因此出错了。

13、微型计算机的主要性能指标有哪些?答:CPU字长、存储器容量、运算速度、CPU内核和IO工作电压、制造工艺、扩展能力、软件配置。

电子科技大学微机系统原理与接口第二版课后习题答案chapter10习题解答

“微处理器系统原理与嵌入式系统设计”第十章习题解答10.2 简述以ARM微处理器为核心的最小硬件系统的组成?●ARM微处理器;●电源模块,包括CPU内核和I/O接口电源;●时钟模块,包括系统主时钟和实时时钟;●复位模块,包括系统加电复位、手动复位和内部复位;●存储器模块,包括程序保存存储器和程序运行存储器;●JTAG调试接口模块。

10.4 简述S3C2440A芯片中各模块时钟信号产生及配置的原理。

为降低系统功耗,可时钟信号进行哪些处理?系统复位信号与各时钟信号有什么关系?当系统主时钟送入S3C2440A芯片后,进入其时钟发生模块,由锁相环进行相应的处理,最终得到FCLK,HCLK,PCLK和UCLK四组时钟信号。

其中,FCLK信号主要供给ARM920T内核使用,HCLK主要供给AHB总线、存储器控制器、中断控制器、LCD控制器、DMA控制器和USB主机模块;PCLK主要供给访问APB总线的外设,例如WDT,I2S,I2C,PWM定时器,MMC接口,ADC,UART,GPIO,RTC和SPI模块;UCLK主要提供USB模块需要的48MHz 时钟。

为降低系统功耗,可对时钟信号进行门控管理。

最低功耗情况下,只开启FCLK信号,其他时钟信号关闭;若需对其他外设,只需使能相应总线及外设的时钟信号有效即可。

系统复位信号一般包括加电复位、手动复位和内部复位三类。

其中,加电复位和手动复位信号均来自外部复位电路,内部复位信号一般来自系统内部事务处理(例如看门狗复位等)。

因此,系统对外部复位信号波形有一定的要求,若不能满足要求系统将不能正常工作。

在S3C2440A芯片中,要完成正确的系统复位,在处理电源保持稳定之后,该信号必须至少维持4个FCLK时钟的低电平状态。

10.6 利用S3C2440A的GPIO端口,设计包含8个LED的流水灯电路,每个LED 间隔1S轮流点亮,试画出程序流程图并写出相关程序段。

假设利用S3C2440A芯片的GPIO端口G的第0~7引脚驱动8个LED电路,对应GPIO输出为0时LED灯亮,则相应程序流程图及相应程序段如下所示:GPGCON EQU 0x56000060GPGDAT EQU 0x56000064GPGUP EQU 0x56000068;配置GPGCON寄存器,设置相关引脚为输出功能LDR R0,=GPGCONLDR R1,[R0]BIC R1,R1,#0x0000FFFFORR R1,R1,#0x00005555STR R1,[R0];配置GPGUP寄存器,断开各上拉电阻LDR R0,=GPGUPLDR R1,[R0]ORR R1,R1,#0x00FFSTR R1,[R0];输出驱动数据,点亮对应LED等LDR R2,=GPGDATLDR R3,[R2]BIC R3,R3,#0x00FFORR R3,R3,#0x00FESTR R3,[R2]LDR R0,=0xFFFFFF ;初始计数值BL DELAY ;调用延迟子程序…LDR R2,=GPGDATLDR R3,[R2]BIC R3,R3,#0x00FFORR R3,R3,#0x007FSTR R3,[R2]LDR R0,=0xFFFFFF ;初始计数值BL DELAY ;调用延迟子程序B LOOPSTARDELAYSUB R0,R0,#1CMP R0,#0x0BNE DELAYMOV PC,LR10.7 在上题中,如果要加入一个按键,实现按键按下时流水灯停止流动,按键放开时流水灯正常流转的功能,思考应怎样修改电路和程序?在上题的基础上,添加一个GPIO口作为输入管脚(GPA的GPA[0]),按键按下GPA[0]值为1,否则为零。

完整版微机原理课后习题参考答案.doc

完整版微机原理课后习题参考答案.doc2篇微机原理课后习题参考答案(一)微机原理课后习题是帮助学生巩固所学知识,提高学习效果的一种重要方式。

通过解答习题,学生可以检验自己的理解程度和掌握技能,同时也能发现知识的不足之处,以便及时调整学习方法和加强练习。

以下是微机原理课后习题的参考答案,供学生参考:1. 请简述微机的基本组成部分。

答:微机的基本组成部分包括中央处理器(CPU)、内存、输入输出设备和总线。

其中,中央处理器是微机的控制中心,负责数据的处理和指令的执行;内存是用于存储数据和程序的地方,包括随机访问存储器(RAM)和只读存储器(ROM);输入输出设备用于与外部设备进行信息交换,包括键盘、显示器、打印机等;总线是连接中央处理器、内存和输入输出设备的通道,用于数据传输和控制信号传递。

2. 什么是存储器的地址空间?答:存储器的地址空间是计算机可寻址的存储单元的集合。

每个存储单元都有一个唯一的地址,用于在存储器中定位该存储单元。

地址空间的大小决定了计算机可以寻址的最大存储容量。

常见的存储器地址空间包括物理地址空间和逻辑地址空间。

物理地址空间是实际存在的存储单元的集合,由硬件决定;逻辑地址空间是程序员或操作系统所见到的地址空间,它可以比物理地址空间大或小,具体取决于使用的地址转换机制。

3. 简述中央处理器的主要功能。

答:中央处理器的主要功能包括指令的执行和数据的处理。

指令的执行是指根据程序中的指令,按照特定的指令集进行操作,包括数据传输、算术运算、逻辑运算等。

数据的处理是指对输入的数据进行处理,可以进行各种运算和逻辑操作,生成相应的结果。

除了执行指令和处理数据外,中央处理器还负责控制系统的运行,包括控制信号的发出和时序的控制,以确保各个组成部分协调工作。

4. 什么是总线?答:总线是微机中各个组成部分之间进行数据传输和控制信号传递的通道。

它可以看作是计算机内部各个部分之间进行信息交换的公共通道。

总线通常分为数据总线、地址总线和控制总线三种类型。

微机原理课后习题参考答案

上册第一章P91.1 微处理器、微型计算机、微型计算机系统的区别是什么?答:(1)微型计算机中的运算器和控制器合起来称为中央处理器,也就是微处理器,又称微处理机。

(2)微型计算机是由cpu、主存储器、输入/输出接口电路和系统总线构成。

(3)微型计算机系统由微型计算机、输入/输出设备、外存储器、系统软件、电源、面板和机架等组成。

1.2微型计算机由哪些基本部分构成?微型计算机是由cpu、主存储器、输入/输出接口电路和系统总线构成。

1.4 说明CISC、RISC及其主要区别。

CISC是指复杂指令系统计算机,RISC是指精简指令系统计算机。

他们的区别在于不同的CPU设计理念和方法。

RISC指令系统仅包含哪些必要的经常使用的指令,不经常使用的功能,往往通过基本指令组合来完成。

完成特殊功能时效率比较低。

CISC的指令系统比较丰富,一些特殊功能都有相应的指令。

处理特殊任务效率较高。

RISC对存储器操作相对简单,使对存储器访问的控制简化;而CISC机器的存储器操作指令较多,对存储器的访问有更多的指令直接操作,要求的控制逻辑比较复杂。

RISC在一条指令执行的适当地方可以响应中断;而CISC机器是在一条指令执行结束后响应中断。

RISC CPU的电路构成比CISC CPU简单,因此面积小、功耗也更低;CISC电路CPU电路复杂,同水平比RISC CPU面积大、功耗大。

RISC CPU结构比较简单,布局紧凑规整,设计周期较短,比较容易采用一些并行计算的最新技术;CISC CPU结构复杂,设计周期长,技术更新难度大。

从使用角度看,RISC微处理器结构简单,指令规整,性能容易把握,易学易用;CISC微处理器结构复杂,功能强大,实现特殊功能容易。

第二章2.1 8086CPU 由哪两大部分组成?简述它们的主要功能。

总线接口部件BIU跟执行部件EU。

总线接口部件(BIU)是联系微处理器内部与外部的重要通道,其主要功能是负责微处理器内部与外部的信息传递。

电子科大-微机原理习题解答-chap2

第二章习题答案2.2 完成下列逻辑运算(1)101+1.01 = 110.01(2)1010.001-10.1 = 111.101(3)-1011.0110 1-1.1001 = -1100.1111 1(4)10.1101-1.1001 = 1.01(5)110011/11 = 10001(6)(-101.01)/(-0.1) = 1010.12.3 完成下列逻辑运算(1)1011 0101∨1111 0000 = 1111 0101(2)1101 0001∧1010 1011 = 1000 0001(3)1010 1011⊕0001 1100 = 1011 01112.4 选择题(1)下列无符号数中最小的数是( A )。

A.H(1,1011,0101) (01A5)B.B(3764)C.D(2590)D.O (2)下列无符号数中最大的数是( B )。

A.B(227)(10010101)B.OC.H(143)(96)D.D(3)在机器数( A )中,零的表示形式是唯一的。

A.补码B.原码C.补码和反码D.原码和反码(4)单纯从理论出发,计算机的所有功能都可以交给硬件实现。

而事实上,硬件只实现比较简单的功能,复杂的功能则交给软件完成。

这样做的理由是( BCD )。

A.提高解题速度B.降低成本C.增强计算机的适应性,扩大应用面D.易于制造(5)编译程序和解释程序相比,编译程序的优点是( D ),解释程序的优点是( C )。

A.编译过程(解释并执行过程)花费时间短B.占用内存少C.比较容易发现和排除源程序错误D.编译结果(目标程序)执行速度快2.5通常使用逻辑运算代替数值运算是非常方便的。

例如,逻辑运算AND将两个位组合的方法同乘法运算一样。

哪一种逻辑运算和两个位的加法几乎相同?这样情况下会导致什么错误发生?逻辑运算OR和两个位的加法几乎相同。

问题在于多个bit的乘或加运算无法用AND或OR运算替代,因为逻辑运算没有相应的进位机制。

电子科大-微机原理习题解答-chap5

SRAM2114(1K*4)存储芯片组成存储系统,试问采用线选译码时需要多少个

2114 存储芯片?

该存储器的存储容量=224 *8bit=16M 字节

16M

需要 SRAM2114(1K*4)存储芯片数目:

8 = 160组

2片 / 组

1K 4

320 片

5.12 在有 16 根地址总线的机系统中画出下列情况下存储器的地址译码和连 接图。 (1)采用 8K*1 位存储芯片,形成 64KB 存储器。 (2)采用 8K*1 位存储芯片,形成 32KB 存储器。 (3)采用 4K*1 位存储芯片,形成 16KB 存储器。

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

第一片 0000H~ 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

地址范围 0FFFH 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1

共需 4 片 第二片 1000H~ 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0

为保证在每个 1μS 内都留出 0.5μS 给 CPU 访问内存,因此该 DRAM 适合采用分散式或 异步式刷新方式,而不能采用集中式刷新方式。

l 若采用分散刷新方式,则每个存储器读/写周期可视为 1μS,前 0.5μS 用于读写,后 0.5μS 用于刷新。相当于每 1μS 刷新一行,刷完一遍需要 128×1μS=128μS,满足刷新周期 小于 2ms 的要求;

(2)8K*1 位存储芯片地址长度为 13,32KB 存储器需要 4 个 8K*1 位存储芯片故总共 需要 15 根地址总线,地址译码为:

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

微机原理部分课后习题答案

微机原理(第4版)部分习题参考答案第一章绪论1、什么是冯诺依曼机?答:由运算器、控制器、存储器、输入设备、输出设备等5个部分组成,其基本原理是以存储器存储程序控制的原理。

9、将下列二进制数转化为十进制数。

(1) 1101.01B=13.25(2) 111001.0011B=57.1875(3) 101011.0101B=43.3125(4) 111.0001B=7.062510、将下列十六进制数转化为十进制数。

(1) A3.3H=163.1875(2) 129.CH=297.75(3) AC.DCH=172.859375(4) FAB.3H=4011.187511、将下列十进制数转化为二进制、八进制、十六进制。

(1) 23=10111B=27Q=17H(2) 107=1101011B=153Q=6BH(3) 1238=10011010110B=2326Q=4D6H(4) 92=1011100B=134Q=5CH12、将下列十进制数转换为8位有符号二进制数。

(1) +32=00100000B(2) -12=11110100B(3) +100=01100100B(4) -92=10100100B13、将下列十进制数转化为压缩和非压缩格式的BCD码。

压缩非压缩(1) 102=00000001 00000010 00000001 00000000 00000010(2) 44=01000100 00000100 00000100(3) 301=00000011 00000001 00000011 00000000 00000001(4) 1000=00010000 00000000 00000001 00000000 00000000 00000000 14、将下列二进制数转换为有符号十进制数。

(1) 10000000B=-128(2) 00110011B=51(3) 10010010B=-110(4) 10001001B=-119第二章8086系统结构5、要完成下述运算或控制,用什么标志位判别?其值是什么?(1)比较两数是否相等。

电子科技大学《微机原理》指定教材课后参考答案2

“微机系统原理与接口技术”第六章习题解答(部分)4.某微机系统有8个I/O接口芯片,每个接口芯片占用8个端口地址。

若起始地址为9000H,8个接口芯片的地址连续分布,用74LS138作译码器,请画出端口译码电路图,并说明每个芯片的端口地址范围。

答:分析下表所列的地址分配情况,可知系统地址信号的译码情况为(图略):●字选:A2~A0直接与接口芯片上的地址信号线连接以寻址每个接口芯片内部的8个端口;●片选:⏹A5~A3接3-8译码器输入端,译码器输出端分别作为8个接口芯片的片选信号;~A经门电路译码后形成3-8译码器的片选信号;8. 假设一台打印机的数据输出I/O口地址为378H,状态口地址为379H,状态字节的D0位为状态位(D0=0,表示打印数据缓冲区空,CPU可以向它输出新数据;D0=1,表示数据区满)。

试编写一段程序,用查询方式从内存中以BUF为首址的单元处开始,将连续1KB的数据传送给打印机,每次送1字节。

答:一种可能的程序段如下实现:……LEA BX, BUF ; BX指向第1个待打印的数据MOV CX, 1024 ; 一共要送1K个字节数据NEXT: MOV DX, 379HIN AL, DX ; 读打印机状态端口TEST AL, 01HJNZ NEXT ; 若D0位不为0,则继续查询等待MOV DX, 378HMOV AL, [BX]OUT DX,AL ; 将BX所指的数据发送到打印机INC BX ; BX指向下一个待打印的字节LOOP NEXT ; CX不为0,继续送下一个字节……9. 请用无条件传输方式编写一个完整的输入/输出程序,将首地址为40000H的内存单元中的1K个字数据从端口Output处输出,然后从端口Input处输入2KB数据到首地址为50000H的内存单元中(端口地址的实际值可自行给定)。

答:一种可能的程序如下实现:DATA1 SEGMENT AT 4000HBUFFER1 DW ……; 已存放好1K个字数据DA TA1 ENDSDA TA2 SEGMENT AT 5000HBUFFER2 DB 2048 DUP(?) ; 预留2KB单元存放读入的数据DA TA2 ENDSCODE SEGMENTASSUME CS:CODE , DS:DA TA1, ES:DA TA2START: MOV AX, DATA1MOV DS, AXMOV AX, DATA2MOV ES, AXLEA SI, BUFFER1 ; SI指向准备发送的第1个数据LEA DI,BUFFER2 ; DI指向第1个准备存放接受数据的单元CLD ; 地址增量方向MOV CX, 1024 ; 发送数据总个数MOV DX, OUTPUT ; 设OUTPUT为字输出端口地址AGAIN1: LODSW ; 将DS:SI所指数据取出准备发送,并修改SI值OUT DX, AXLOOP AGAIN1MOV CX, 2048 ; 接收数据总个数MOV DX, INPUT ; 设INPUT为字输入端口地址AGAIN2: IN AX, DLSTOSB ; 将输入数据存在ES:DI所指单元,并修改DI值LOOP AGAIN2MOV AH, 4CH ; 返回INT 21HCODE ENDSEND START。

微机原理习题答案(完整版)

第一章习题答案1-1 请说明CPU的功能以及CPU是如何执行指令和程序的。

答:CPU的功能是执行程序和统筹处理计算机系统中各类事务。

CPU执行指令分为3步:取指令、分析指令、执行指令;计算机程序是由一条条指令按一定的顺序排列组成的,CPU执行程序的过程就是一条条指令累计执行的过程,其方式分为串行作业方式和流水线作业方式。

1-2 请说明单片机内部主要是由哪些部件组成的,并说明各部件的作用。

答:CPU:由控制器和运算器构成,控制器的作用是执行指令和协调系统各部件的工作;运算器的作用是进行逻辑运算和算术运算。

存储器:存储计算机工作时使用的信息,即指令代码和数据代码。

I/O接口电路:具有数据缓冲、数据隔离及数据转换的功能。

1-3 请问对于容量位8K的存储器芯片,它的地址线是多少根?答:8K=8192=213,故地址线为13根。

另附:存储器的数据线由存储器的字长决定,例如一块32K×16(存储器容量显示格式:存储单元数×存储单元的字长)的存储器,其地址线为15根,数据线为16根。

1-4 将十进制数78,134,分别用二进制数、十六进制数和8421BCD吗表示。

答:(78)D=(1001110)B=(4E)H=(01111000)8421BCD(134)D=(10000110)B=(86)H=(000100110100)8421BCD注:8421BCD码为4位表示一个十进制数符,本质是符号不是数值,所以不可省略0。

1-5 将下列真值分别转化为用8位和16位二进制数表示的原码、补码和反码。

X=1000100;[X]8位原=[X]8位反=[X]8位补=01000100;[X]16位原=[X]16位反=[X]16位补=0000000001000100X= -1000100[X]8位原=11000100,[X]8位反=10111011,[X]8位补=10111100;[X]16位原=1000000001000100,[X]16位反=1111111110111011,[X]16位补=1111111110111100;X= -0111111[X]8位原=10111111,[X]8位反=11000000,[X]8位补=11000001;[X]16位原=1000000000111111,[X]16位反=1111111111000000,[X]16位补=1111111111000001;1-6 将下列补码转化成二进制数的真值。

微机原理课后习题答案

微机原理课后习题答案2.1 8086 CPU 在内部结构上由哪几部分组成?其功能是什么?【答】8086 的内部结构-成两部分:总线接口部件BIU,负责控制存储器读写。

执行部件EU,EU 从指令队列中取出指令并执行。

8086 是16 位微处理器,有16 根数据线、20 根地址线,内部寄存器、运算部件以及内部操作都是按16 位设计的。

2.2 8086 的总线接口部件有那几部分组成?【答】8086 的总线接口部件主要由下面几部分组成:4 个段寄存器CS/DS/ES/SS, 一个16 位的指令指针寄存器IP, 一个20 位地址加法器, 6 字节的指令队列,内部暂存器以及输入输出电路组成.2.3 8086 的执行部件有什么功能?由那几部分组成?【答】8086 的执行部件主要由下面几部分组成:(1)四个16 位通用寄存器AX、BX、CX、DX, 通用四个16 位专用寄存器,包括二个指针寄存器SP、BP, 二个变址寄存器SI、DI, 算术逻辑单元ALU,标志寄存器。

2.4 8086CPU 状态标志和控制标志又何不同?程序中是怎样利用这两类标志的? 8086 的状态标志和控制标志分别有哪些?【答】标志分两类:状态标志(6 位):反映刚刚完成的操作结果情况。

控制标志(3 位):在某些指令操作中起控制作用。

2.5 8086/8088 和传统的计算机相比在执行指令方面有什么不同?这样的设计思想有什么优点? 8086CPU 执行转移指令时,指令队列寄存器内容如何变化?【答】传统的计算机一般按照取指令、指令译码/执行指令的步骤工作。

在8086/8088 中,指令的提取与执行分别由总线接口部件BIU 与执行部件EU 完成,8086/8088 可以在取指令同时又可以执行指令,这种并行工作方式有力的提高了CPU 的工作效率。

2.6 将两数相加,即0100 1100 加0110 0101,CF、PF、AF、ZF、SF、OF 各为何值?【答】0100 1100+0110 0101=10110001CF=0,PF=1,AF=1,ZF=0,SF=1,OF=12.7 存储器的逻辑地址由哪几部分组成?存储器的物理地址是怎样形成的?一个具有20 位地址线的CPU,其最大物理地址为多少?【答】存储器的逻辑地址由段地址与段内偏移地址组成。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

“微机系统原理与接口技术”第七章习题解答(部分)

1.8086系统采用向量式中断,试简述8086系统中中断类型码、中断向量、中断向量表的含义及其之间的关系。

答:

中断类型码:用于区分不同的中断源,即系统中每个中断源都应该对应一个唯一的类型码。

8086系统中的中断类型码以8位无符号数(00H~0FFH)表示,一共可以区分256个不同的中断源。

中断向量:中断服务程序(ISR)的入口地址,也就是ISR的第一条指令在存储器中的位置。

8086系统中的中断向量由两个字(4个字节)组成,低位字表示入口的偏移地址,高位字表示入口的段基址。

显然,每个中断类型码对应一个中断向量,则8086系统中共应有256个中断向量。

中断向量表:中断向量的存放地。

8086系统将最低的1KB(00000H~003FFH)RAM 空间用于存放这256个中断向量。

三者之间的关系是:利用中断类型码n可以很容易地从中断向量表中找到该中断源所对应的中断向量,即:中断向量存放的起始地址m =n×4,从中断向量表的m地址单元开始连续取出的四个字节就是n号中断的ISR入口地址。

8086CPU正是用这种方法完成中断索引的。

2.判断下列说法是否正确,如有错,指出错误原因并改正:

(1)优先级别高的中断总是先响应、先处理。

(2)8086系统中,中断向量表存放在ROM地址最高端。

(3)PC系统中的主机总是通过中断方式获得从键盘输入的信息。

(4)80486系统和8086系统一样,将中断分为可屏蔽中断和不可屏蔽中断两种。

(5)IBM PC/XT中,RAM奇偶校验错误会引起类型码为2的NMI中断。

答:

(1)可以算对。

不过这个题说法本身就不太明确,应该是:“一个系统中有多个中断源同时提出中断请求时,优先级别高的中断总是先响应、先处理。

”

(2)错。

应该是:“8086系统中,中断向量表存放在RAM地址最低端。

”

(3)对。

(4)错。

应该是:“8086系统将中断分为内(软)中断和外(硬)中断两大类,而80486系统将广义中断分为异常和狭义中断两大类。

”

(5)对。

4. 8086系统的RAM存储单元中,从0000H:002CH开始依次存放23H、0FFH、00H和0F0H 4个字节的中断向量,该向量对应的中断类型码是多少?而中断类型码为14H的中断向量应存放在哪些存储单元中?

答:中断向量0F000:0FF23存放在0002CH双字单元中,说明其对应的中断类型码N=2CH÷4=0BH。

14H号中断向量的起始存放地址为4×14H=00050H,即该中断向量的偏移量部分存放在0050H和0051H单元中,段基址部分存放在0052H和0053H单元中。

5. 以下是PC机为某外设中断源装载中断服务子程序的代码,请问该外中断的类型码是

多少?程序段为它设置的中断向量是什么?

PUSH ES

MOV AX,0

MOV ES,AX

CLD

MOV DI,24H

MOV AX,0200H

STOSW

MOV AX,1000H

STOSW

POP ES

答:从程序可看出,该外中断的中断向量存放在ES:DI所指单元即0000:0024H单元,所以该外中断的类型码N=00024H÷4=9;该中断向量为1000H:0200H(10200H)。

6. 某系统中,要求8086CPU采用中断方式把一个长100字节的数据块从首址为AREA 的存储区传送到端口地址为37FH的接口上,每次中断只传送一个字节。

设该中断的类型码为0AH,试写出完整的主程序和中断服务子程序。

答:由题意可知,主程序在完成通常的初始化工作(如初始化段寄存器)之后,还需要完成中断向量的装载;而中断服务子程序则负责完成数据的发送。

DATA SEGMENT

AREA DB 100 DUP(?);待传送的数据块

CNT DB 0 ;已传送数据的个数

OLDOFF DW ? ;旧中断向量的偏移地址部分

OLDSEG DW ? ;旧中断向量的段基址部分

DATA ENDS

CODE SEGMENT

ASSUME CS:CODE,DS:DATA

START PROC FAR ; 主程序

; -------常规初始化-------------------------------------------------

PUSH DS

MOV AX, 0

PUSH AX

MOV AX, DATA

MOV DS, AX

; --------取0AH号中断的原中断向量并保存-----------------

CLI

MOV AL, 0AH

MOV AH, 35H

INT 21H

MOV OLDSEG,ES

MOV OLDOFF,BX

; --------设置新中断向量--------------------------------------------

PUSH DS

MOV AX, SEG RECIVE ; 取当前中断服务程序入口的段基址

MOV DS, AX

MOV DX, OFFSET RECIVE ; 取当前中断服务程序入口的偏移量

MOV AL, 0AH ; 中断类型号为0AH

MOV AH, 25H

INT 21H ; 将当前中断服务程序入口地址送向量表

POP DS

STI

; --------等待中断传送数据----------------------------------------------

WAT: CMP CNT, 100

JNZ WAT

; --------发完数据后恢复原中断向量---------------------------------

MOV DX, OLDSEG

MOV DS, OLDOFF

MOV AL, 0AH

MOV AH, 25H

INT 21H

RET

START ENDP

RECIVE PROC FAR ; 中断服务子程序

PUSH AX

PUSH DX

PUSH SI

MOV SI, OFFSET AREA ; SI指向需传送数据的首址

ADD SI, CNT

MOV AL, [SI]

MOV DX, 37FH

OUT DX, AL

INC CNT

POP SI

POP DX

POP AX

IRET

RECIVE ENDP

CODE ENDS

END MAIN。