篮球记分牌verilog设计

篮球计分器FPGA附程序

单片机接口实验篮球计分器的设计**: ***班级: 14级12班学号: ********** **: ***专业: 控制科学与工程成绩评定学生:苗茂宇学号:**********学生:苗茂宇学号:1408202007 目录摘要 (1)Abstract (1)1. FPGA及系统设计概述 (2)1.1. EDA简介 (2)1.1.1. EDA定义 (2)1.1.2. EDA发展概述 (2)1.1.3. HDL概述 (2)1.1.4. 总结 (3)1.2. FPGA简介 (3)1.2.1. FPGA概述 (3)1.2.2. FPGA原理 (4)1.3. LCD1602 (4)1.4. 产品现状及发展 (5)1.5. 总体设计要求 (5)1.5.1. 设计流程 (5)1.5.2. 设计要求 (5)1.6. 本章小结 (6)2. 实验方案设计 (6)2.1. 分频模块 (6)2.2. 计时模块 (7)2.3. 24秒计时模块 (9)2.4. 计分模块 (10)2.5. lcd驱动模块 (11)2.6. 本章小结 (17)3. 实验结论 (17)4. 结束语 (18)参考文献 (19)附录 1 (20)摘要FPGA(现场可编程逻辑器件)以其体积小、功耗低、稳定性高等优点被广泛应用于各类电子产品的设计中。

FPGA是基于硬件可编程的器件,设计者需要掌握硬件描述语言,Verilog HDL就是一种硬件描述语言。

Verilog HDL语言是在C 语言的基础上发展而来的,语法结构上与C语言有很多相似之处,继承了C语言的语法结构,但是其与C语言有着本质上的区别。

本设计是基于FPGA的篮球计时计分系统的设计,结合篮球比赛的实际过程,对系统进行了模块化设计,最终组合调试。

硬件实验表明本系统计时计分准确,实时性好,能够很好的反应比赛进度,此次设计达到了设计预期。

关键词:FPGA;Verilog HDL;计时计分;模块化AbstractFPGA (field programmable logic device) with its small size, low power consumption, high stability has been widely used in various types of electronic products design. FPGA is a programmable device based on hardware, designers need to master the hardware description language, Verilog HDL is a hardware description language. Verilog HDL language is developed on the basis of C language, grammar structure and C language have many similarities, inherited the grammar structure of C language and C language, but there's a difference between. This design is the designof FPGA basketball timing and scoring system based on the actual process, combined with the game of basketball, the system of modular design, the final assembly debugging. Hardware experiments show that the system timing accuracy, goodreal-time performance, can very good response competition schedule, the design achieves the expected design.Keywords: FPGA;Verilog HDL ; timing and scoring; modular1.FPGA及系统设计概述1.1.E DA简介1.1.1.EDA定义EDA是电子设计自动化(Electronic Design Automation)的缩写。

篮球计分器的课程设计fpga

篮球计分器的课程设计fpga一、教学目标本课程的目标是让学生了解和掌握篮球计分器的设计与实现,通过学习FPGA 的相关知识,培养学生运用数字电路设计实际应用系统的能力。

具体的教学目标包括:1.知识目标:使学生了解FPGA的基本结构和工作原理,掌握VHDL或Verilog硬件描述语言,了解数字电路设计的基本方法。

2.技能目标:培养学生能够运用FPGA设计简单的数字电路系统,如篮球计分器,并能进行相关的编程和调试。

3.情感态度价值观目标:培养学生对新技术的敏感性和好奇心,增强学生运用科学知识解决实际问题的能力,提高学生团队合作和沟通的能力。

二、教学内容本课程的教学内容主要包括以下几个部分:1.FPGA基础知识:介绍FPGA的基本结构、工作原理和编程方法。

2.数字电路设计:介绍数字电路的基本设计方法,包括组合逻辑电路、时序逻辑电路等。

3.硬件描述语言:介绍VHDL和Verilog硬件描述语言的基本语法和使用方法。

4.篮球计分器设计:通过设计一个简单的篮球计分器,使学生能够综合运用所学知识解决实际问题。

三、教学方法为了达到上述教学目标,我们将采用以下教学方法:1.讲授法:用于讲解FPGA的基础知识、数字电路设计和硬件描述语言的相关概念。

2.案例分析法:通过分析具体的篮球计分器设计案例,使学生能够将理论知识应用到实际问题中。

3.实验法:安排实验室实践环节,让学生亲自动手进行篮球计分器的设计和调试,增强学生的实践能力。

四、教学资源为了支持本课程的教学,我们将准备以下教学资源:1.教材:选择合适的FPGA教材,用于引导学生学习相关知识。

2.多媒体资料:制作课件和教学视频,帮助学生更直观地理解教学内容。

3.实验设备:提供FPGA开发板和相关的实验设备,让学生能够在实验室进行实际操作。

五、教学评估本课程的评估方式包括平时表现、作业、考试等多个方面,以全面、客观、公正地评价学生的学习成果。

具体评估方式如下:1.平时表现:通过课堂参与、提问、小组讨论等形式的评估,考察学生的学习态度和积极性。

【篮球记分牌】篮球记分牌课程设计实验报告

【篮球记分牌】篮球记分牌课程设计实验报告《【篮球记分牌】篮球记分牌课程设计实验报告》篮球记分牌课程设计实验报告XX学校电子技术课程设计报告题目学院自动化与电气工程学院专业班级学号学生姓名指导教师完成日期201X年 XX月XX日篮球记分牌摘要围绕设计要求对篮球记分牌进行设计。

首先根据功能要求提出单片机STC89S52RC为控制核心的设计方案;其次进行硬件系统和软件系统的设计,并且根据本次设计所用的V3.72开发板原理图进行设计,然后根据所设计的电路图级程序用Proteus和Keil 进行了仿真,验证了设计方案的正确性,最后,把程序烧进开发板中来完成篮球记分牌的硬件电路。

调试和测试结果表明基本上都能满足此次课程设计的要求。

本次课程设计,有效加深和巩固了单片机的基础知识,提高了我们的实际动手能力,具有及其深远的意义。

关键词:单片机独立按键蜂鸣器 at24c02 数码管一、设计要求1.比赛开始,比分能够全部清零,数码管前2位,末二位做记分用,当中2位做24秒倒计时用。

2.24秒倒计时时间到,蜂鸣器响、指示灯亮,重新开始倒计时(按下开始键),蜂鸣器停止鸣叫、指示灯灭。

3.比分进行增加后,倒计时从24秒重新开始倒计时。

任意时刻24秒可以重新开始倒计时。

必要时候能够关闭倒计时。

4.利用AT24C02或者单片机内部资源保存比分,支持复位保存,掉电保存功能。

二、系统设计及仿真2.1、系统总体设计图2-1系统结构图思想汇报专题本系统采用单片机STC89S52RC为控制核心,系统主要包括显示模块、按键控制模块、蜂鸣器报警模块等。

下面对各模块的设计进行论证。

1) 显示模块单片机系统中,往往需要多位显示。

动态显示是一种最常见的多位显示方法,应用非常广泛。

所有数码管段选都连接在一起的时候,怎么让数码管显示不一样的数字呢?动态显示是多个数码管,交替显示,利用人的视觉暂停作用使人看到多个数码管同时显示的效果。

首先我们来看一下显示模块电路原理图:图2-2 74ls138结构图图2-3 数码管段选图本实验使用的是,通过P22、P23、P24控制3-8译码器来对数码管进行位选,通过P0口经过573的驱动控制数码管的段选2) 按键控制模块方案一:采用矩阵键盘。

【免费】-》基于FPGA的篮球计时计分器的设计与实现

收稿日期:2010209210通讯作者:唐庭龙(1979-),男,讲师,硕士,主要研究方向为信号与信息处理.E 2mail :tangtinglong @基于FPGA 的篮球计时计分器的设计与实现唐庭龙1 陆 酉2(1.三峡大学计算机与信息学院,湖北宜昌 443002;2.武汉供电公司,武汉 430064)摘要:提出了基于FP GA (Field Programmable Gate Array )的篮球计时计分器的设计方案,并使用Quart us II 软件和V HDL 语言(Very High Speed Integrated Circuit Hardware Description Lan 2guage )实现了相关设计.采用计数的方法设计了计时器模块、计分器模块,结合7段数码管动态显示原理及1602液晶控制方法设计了显示模块.经过仿真及下载验证得到以下结果:计时器完成了篮球比赛4节12min 的倒计时,一次进攻时间24s 的计时;计分器实现了甲乙两队加分,分数调整的功能;显示部分完成了时间、比分的显示等.以上结果符合设计要求.关键词:篮球计时计分器; FP GA ; V HDL 中图分类号:TP391 文献标识码:A 文章编号:16722948X (2010)0620080204Design and R ealization of B asketball Timing and Scoring Device B ased on FPGATang Tinglong 1 L u Y ou 2(1.College of Comp uter &Information Technology ,China Three G orges Univ.,Yichang 443002,China ;2.Wuhan Elect ric Power Company ,Wuhan 430064,China )Abstract Based o n FP GA (Field Programmable Gate Array ),a scheme of scoring and timing device used in basket ball games is designed .The system is written by V HDL (Very High Speed Integrated Circuit Hardware Description Language )and accomplished by Quart us II.Three part s are included ,as well as t he timing mod 2ule and t he scoring module are based on met hod of counter ,t he display module is based on 72segment numeric L ED (Light Emitting Diode )and 1602L CD (Liquid Crystal Display ).The result s show t hat t he timing module can countdown f rom t he 12t h minute in t he four quarters of t he game and 24seconds of each round ,and t he scoring module can record point s of bot h teams and adjust t he result ;t he display module can show t he time and t he game scores.The design result s indicated t he scheme is feasible and correct.K eyw ords basket ball timing and scoring device ; FP GA ; V HDL 篮球比赛中,计时计分系统主要完成对比赛过程中出现的时间,比分等数据进行快速采集记录,加工处理以及显示,其对实时性、准确性以及现场效果具有一定的要求.随着FP GA 技术的发展与价格的降低,其运算速度快,管脚资源丰富,便于实现复杂的逻辑功能等优势在电子系统设计中逐渐显现.文章基于FP GA 设计并实现了满足NBA 规则基本要求的一种篮球计时计分器,具有数据处理稳定,速度快,实时性强,电路简单,便于二次开发与扩展等特点.1 总体设计该篮球计时计分系统总体上分为5个模块,功能框图如图1所示:其中,系统时钟提供其它主要模块所需的各种时钟信号;按键去抖模块处理按键的抖动;计时模块包括每节比赛的12min ,以及每次进攻的24s 计时;计分(比分)模块实现双方得分的统计,以及每次得分后,24s 计数器的清零;显示模块包括18第32卷 第6期 唐庭龙等 基于FP GA的篮球计时计分器的设计与实现28三峡大学学报(自然科学版) 2010年12月图15 按键电平抖动示意图为保证按键识别的准确性,在按键电压信号抖动的情况下不能进行状态输入,为此必须进行去抖动处理,消除抖动部分的信号,一般有硬件和软件两种方法.这里用状态机的方法设计一个去抖电路.状态机实现去抖动电路原理是:按键去抖动关键在于提取稳定的低电平状态(按键按下时为低电平),滤除前沿、后沿抖动毛刺.对于一个按键信号,可以用一个脉冲对它进行取样,如果连续3次取样为低电平,则可以认为信号已经处于稳定状态,这时输出一个低电平的按键信号.继续取样的过程中,如果不能满足连续3次取样为低,则认为键稳定状态结束,这时输出变为高电平.设计的状态转换图如图16所示,reset 信号有效时,电路进入复位态S0,这时认为取样没有检测到低电平,在输入取样的过程中,每次检测到一个低电平,发生一次向下的状态转换,直到连续检测到3个连续的低电平时,进入S3状态,这时输出置低(按键信号稳定态);在中间状态S1,S2时,一旦检测到高电平,仅进入S0状态,重新检测[2].图16 状态转换图 该部分的模块元件符号如图17所示.其中clk为检测的时钟,它与10k Hz 频率相连.cr 为复位信号,低电平有效.din[4..0]为按键信号,它有5位,表示有5个按键需要去抖动,低电平有效.dout [4..0]表示加了去抖动后的按键信号.图17 加去抖动的按键模块3 结 论设计经过编译后下载到基于Altera 公司的EP2C35F484C8芯片的开发板,能正确地实现篮球计时计分器的功能,完成比赛过程中的计时如每节12min 、每次进攻24s 、1至4节的节次自动显示;完成1分、2分、3分的得分加分、比分错误时的调整等.设计采用模块化设计,各模块通用性强,方便剪裁,在其它需要计数器、数码管、1602L CD 以及按键去抖动等模块的设计中可作参考甚至可直接使用;在需要添加其它硬件设备如大屏幕L ED ,V GA 接口设备等时能很方便扩展.设计在时间的调整,进攻时间实时转换以及遥控方式控制等功能上还可以进一步完善.参考文献:[1] 张洪润.FP GA/CPLD 应用设计200例[M ].北京:北京航空航天大学出版社,2009.[2] 刘延飞.基于Altera FP GA/CPLD 的电子系统设计及工程实践[M ].北京:人民邮电出版社,2009.[责任编辑 张 莉]38第32卷 第6期 唐庭龙等 基于FP GA 的篮球计时计分器的设计与实现。

verilog语言设计篮球计分 -回复

verilog语言设计篮球计分-回复以下是使用Verilog语言设计篮球计分的代码示例:module BasketballScore(input clk, 时钟信号input reset, 复位信号input team1_shot, 队伍1进球信号input team2_shot, 队伍2进球信号output reg [3:0] team1_score, 队伍1得分output reg [3:0] team2_score 队伍2得分);初始得分为0initial beginteam1_score = 4'b0000;team2_score = 4'b0000;end当复位信号为1时重置得分为0always @(posedge clk, posedge reset)if (reset) beginteam1_score <= 4'b0000;team2_score <= 4'b0000;end如果队伍1进球,增加1分always @(posedge clk)if (team1_shot) beginteam1_score <= team1_score + 1;end如果队伍2进球,增加1分always @(posedge clk)if (team2_shot) beginteam2_score <= team2_score + 1;endendmodule在这个示例中,我们定义了一个名为BasketballScore的模块,它有以下输入和输出:- 输入时钟信号clk和复位信号reset,以及代表队伍1和队伍2进球信号team1_shot和team2_shot。

- 输出队伍1和队伍2的得分team1_score和team2_score。

我们使用reg类型来声明输出信号,并在initial块中将其初始值设为0。

另外,我们使用always块来更新计分器,如果进球则将对应队伍的得分加1。

篮球比赛数字记分牌的设计方案

目录1 课程设计题目`内容与要求………………………1.1 设计内容1.2 具体要求2系统设计…………………………2.1 设计思路2.2 系统原理3 系统实现……………………………………………4 系统仿真……………………………………………5硬件验证(操作)说明………………………………6 总结…………………………………………………7参考书目……………………………………………一、课程设计题目、内容与要求1.1课程设计的题目:篮球比赛记分牌1.2课程设计内容:1、根据比赛实际情况记录两队得分,罚球进的1分,进球的2分;2、记分牌要具有纠错功能,能减1分、2分功能;3、利用3个译码显示管输出比赛的分;二、系统设计2.1设计思路:篮球比赛记分牌是记录两队比赛的得分情况,并能够进行纠错功能;根据系统设计的要求,篮球记分牌的电路原理框图如下:2.2 系统原理与设计说明系统各个模块的功能如下:1、D触发器电路模块实现翻转功能当出错时,输出为1,使电路回到上一个正确的状态。

2、4为二进制全加器电路模块实现加法计数功能。

3、移位寄存器电路模块保存比赛两队得分情况的4个相邻状态,出错时将调用上一个正确状态。

4、二选一数据选择器电路模块用来控制移位寄存器5、LED数码管驱动电路模块三、系统实现各模块电路的源程序如下:1、D触发器电路模块及程序:set输入(Q=1),清零应该可以用复位键reset吧(Q=0)。

library ieee;use ieee.std_logic_1164.all;entity sync_rsdff isport(d,clk : in std_logic;set : in std_logic;reset: in std_logic;q,qb : out std_logic);end sync_rsdff;architecture rtl_arc of sync_rsdff isbeginprocess(clk)beginif (clk'event and clk='1') thenif(set='0' and reset='1') thenq<='1';qb<='0';elsif (set='1' and reset='0') thenq<='0';qb<='1';elseq<=d;qb<=not d;end if;end if;end process;end rtl_arc;2、移位寄存器模块电路及程序:library IEEE;use IEEE.std_logic_1164.all;entity shft_reg isport (DIR : in std_logic;CLK : in std_logic;CLR : in std_logic;SET : in std_logic;CE : in std_logic;LOAD : in std_logic;SI : in std_logic;DATA : in std_logic_vector(3 downto 0);data_out : out std_logic_vector(3 downto 0) );end shft_reg;architecture shft_reg_arch of shft_reg issignal TEMP_data_out : std_logic_vector(3 downto 0);beginprocess(CLK)beginif rising_edge(CLK) thenif CE = '1' thenif CLR = '1' thenTEMP_data_out <= "0000";elsif SET = '1' thenTEMP_data_out <= "1111";elsif LOAD = '1' thenTEMP_data_out <= DATA;elseif DIR = '1' thenTEMP_data_out <= SI & TEMP_data_out(3 downto 1);elseTEMP_data_out <= TEMP_data_out(2 downto 0) & SI;end if;end if;end if;end if;end process;data_out <= TEMP_data_out;end architecture;3、二选一数据选择器电路模块及程序:entity mux isport(do,d1:in bit;sel:in bit;q:out bit);end mux;architecture a of mux isbeginq<=(do and sel)or(not sel and d1);end a;4、加法计数器的电路模块及程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY add4 ISPORT(a1,a2,a3,a4:IN STD_LOGIC;b1,b2,b3,b4:IN STD_LOGIC;sum1,sum2,sum3,sum4:OUT STD_LOGIC;cout4:OUT STD_LOGIC);END add4;ARCHITECTURE add_arc OF add4 ISSIGNAL cout1,cout2,cout3:STD_LOGIC;COMPONENT halfaddPORT(a,b:IN STD_LOGIC;sum,hcarry:OUT STD_LOGIC);END COMPONENT;COMPONENT fulladdPORT(in1,in2,cin:STD_LOGIC;fsum,fcarry:OUT STD_LOGIC);END COMPONENT;BEGINu1:halfadd PORT MAP(a=>a1,b=>b1,sum=>sum1,hcarry=>cout1);u2:fulladd PORT MAP(in1=>a2,in2=>b2,cin=>cout1,fsum=>sum2,fcarry=>cout2);u3:fulladd PORT MAP(in1=>a3,in2=>b3,cin=>cout2,fsum=>sum3,fcarry=>cout3);u4:fulladd PORT MAP(in1=>a4,in2=>b4,cin=>cout3,fsum=>sum4,fcarry=>cout4);END add_arc;5、七段译码电路及程序:library ieee;use ieee.std_logic_1164.all;entity deled isport(datain:in std_logic_vector(3 downto 0);qout:out std_logic_vector(6 downto 0));end deled;architecture func of deled isbeginprocess(datain)beginif datain= "0000" then qout<="1111110";elsif datain= "0001" then qout<="0110000";elsif datain= "0010" then qout<="1101101";elsif datain= "0011" then qout<="1111001";elsif datain= "0100" then qout<="0110011";elsif datain= "0101" then qout<="1011011";elsif datain= "0110" then qout<="1011111";elsif datain= "0111" then qout<="1110000";elsif datain= "1000" then qout<="1111111";elsif datain= "1001" then qout<="1111011";else null;end if;end process;end func;四、系统仿真1、D触发器电路模块仿真波形:2、移位寄存器模块电路仿真波形:3、二选一数据选择器电路模块仿真波形:4、加法计数器的电路模块仿真波形:5、七段译码电路仿真波形:五﹑硬件验证说明这次设计采用的硬件电路有芯片EP1K10TC100-3,实验板上标准时钟电路、LED 显示等,六、总结此课题说明了使用VHDL语言设计数字电路的方法以及VHDL语言在数字电路设计仿真中的重要作用,仿真结果表明VHDL 语言应用于数字电路仿真是切实可行的,该语言在电子设计领域受到了广泛的接受。

篮球赛记分牌设计

篮球赛记分牌设计前言篮球是一项充满乐趣的运动,打篮球不仅可以强身健体,而且能增进队友之间的相互信任。

现在篮球普及率已经很高,打篮球不仅仅是专业运动员的运动,也是普通老百姓的活动,不管你是走在学校里,还是公园里,或者是小区里,都能看到篮球场,都能看到打篮球的人,篮球已成为我们大部分人生活里不可缺少的一部分,每天都能听到有人在谈论篮球,说说自己喜欢的NBA巨星……因为喜欢篮球,所以打篮球,时不时会来场激烈的比赛,但是传统的记分方式如粉笔或记计分人员手动翻动记分牌给我们带来诸多不便。

随着社会的发展、科学技术的进步以及人们生活水平的不断提高,各种电子产品开始进入人们的生活,使人们的生活更加便利。

篮球赛记分牌设计的实现使得我们轻轻松松几个按钮开关就能记下分数,让我们感受到科技给我们带来的巨变。

篮球比赛的胜负是由两支队伍在规定时间里得分多少来决定。

由于比赛的不可重复性和绝对的公平性,决定了篮球赛记分牌系统是一个实用性很强、可靠性要求极高的以计算机技术为核心的电子服务系统。

这种设备是篮球比赛中不可或缺的一种电子设备,篮球赛记分牌系统设计是否合理,关系到整个篮球比赛系统运行的稳定和可靠,并直接影响到整个篮球比赛的顺利进行。

篮球赛记分牌系统是篮球比赛的重要工程项目,是关系到比赛成败的关键工程,这种记分牌还可以运用到其他体育竞赛,如足球、羽毛球。

1 系统总体设计方案随着单片机[1]广泛应用于各领域,许多用单片机作控制的球赛记时记分系统也随之产生,例如用单片机控制LCD液晶显示器记时记分器和用单片机控制LED七段显示器计时计分器等。

本设计根据所学的C语言基础知识和一些编程思想,对所需要的一些硬件在市场上进行了调查比较,选择了比较简单,容易实现的51单片机,结合运用C语言思想进行方案设计,使用keil uVision软件编写程序。

51单片机内部的定时器/计数器进行中断可以结合软件延时实现计时。

采用的硬件核心是89C51芯片,其内部采用Flash ROM,具有4KB ROM存储空间,能与3V的超低压工作,电路设计中由于不具备ISP在线编程技术,可以运用STC-ISP烧入程序。

verilog篮球24秒

华中科技大学《电子线路设计、测试与实验》实验报告实验名称:篮球24秒计时器院(系):电子与信息工程专业班级:卓越1101姓名:汪加林学号:U201113167时间:2012.12.20地点:南一楼东303实验成绩:指导教师:汪小燕2011 年12 月20 日一.实验目的1.学会将FPGA中时钟分频2.学会如何用verilog编写计时电路3.学会用verilog实现数码管的动态显示二.实验元器件三.实验原理功能块:一.计时程序:1.思路:当遇到load信号时,首先是置数24,个位从4变到0之后,从十位借位,十位变成1,个位变成9,然后各位从9变成0,从十位借位,十位变成0,个位变成9,最终个位变成0,此时发出警报指示24秒结束。

2.代码:if(stop==0) //stop信号高电平有效beginif(qh==0&&ql==0) //24秒计时完成,发出警报beginalarm<=1;endelseif(ql==0)beginqh<=qh-4'b0001;ql<=4'b1001;endelsebeginql<=ql-4'b0001;end二.复位程序:1.思路:分配一个管脚开关控制是否复位。

当外界输入为复位时,直接将数字置为24.2.代码:if(load) //异步置数beginqh<=4'b0010;ql<=4'b0100;alarm<=0;end三.译码程序:1.思路:七段数码管显示2.代码:module led_7 (BCD,out,clk); input [3:0] BCD;input clk;output[6:0] out;reg [6:0] out;always@( posedge clk) case(BCD)4'b0000:out=7'b0000001;4'b0001:out=7'b1001111;4'b0010:out=7'b0010010;4'b0011:out=7'b0000110;4'b0100:out=7'b1001100;4'b0101:out=7'b0100100;4'b0110:out=7'b0100000;4'b0111:out=7'b0001111;4'b1000:out=7'b0000000;4'b1001:out=7'b0000100; default:out=7'bx;endcaseendmodule四.动态显示程序:1.思路:由于Bysys2上4个数码管的7个led共阴极,故每次只能亮一个,采用动态扫描程序,结合人眼的视觉暂留效应,可以让人觉得两个数码管显示不一样的数字。

篮球记分牌verilog设计说明

数字逻辑设计及应用课程设计报告姓名:学号:选课号:79设计题号:23一.设计题目篮球比赛数字计分牌二.设计要求1.分别记录两队得分情况;2.进球得分加2分,罚球进球得分加1分;3.纠正错判得分减2分或1分;4.分别用三个数码管显示器记录两队的得分情况。

三.设计过程(一)设计方案1.模块设计题目中要用三个数码管来记录两队的得分情况,本文采用输出为8421bcd码,外接译码器和数码管的方式来实现。

先设计一个带有进位(co)和借位(ci)输出的模块pad,输出端(num)输出4位8421bcd码外接译码器和数码管,pad模块还带有加一输入端(a1),加二输入端(a2),减一输入端(d1),减二输入端(d2)。

输入端与开关相接,操作者按下开关即给该端口一个脉冲信号,各输入端口由上升沿触发。

如果操作者同时按下多个端口,输出端口将保持原来的信号不变。

pad模块功能图见图1-1。

图1-1 pad模块输入输出端口及功能然后将三个相同的pad模块进行级联,构造为新的模块numberpad,从而得到带有三个数码管的篮球记分牌。

甲乙两队都将分别使用这个记分牌。

级联图见图1-2。

图1-2 pad模块级联图2.模块部的算法流程每个模块有四个输入端口a1,a2,d1,d2来进行触发,触发事件太多,因此构造rem=a1|a2|d1|d2作为新的触发信号。

因此,只要a1,a2,d1,d2中任意一个按键被按下,将会发出一个脉冲,rem也就会产生一个脉冲。

但是可能出现多个按键同时按下的情况,这样会产生冲突。

所以在always语句块中,进行判断,看是否a1,a2,d1,d2中只有一个处于高电平,若同时处于高电平,则输出维持原来的值不变。

判断完端口a1,a2,d1,d2中哪一个输入了以后,就要进行加1,加2,减1,减2的操作。

加1分为以下情况:(1)若num已经计数到9即1001,再加1则num应变为0000,进位端co输出1;(2)若num不为9,则直接加1,co输出0。

篮球比赛电子记分牌设计

课题名称篮球比赛电子记分牌设计设计内容及要求设计一个篮球比赛记分牌,使用4位数码管显示倒计时的分钟、秒钟值;2位数码管显示A方得分;2位数码管显示B方得分;使用LED灯作为上、下半场的标志;单次加分值包括1分、2分和3分。

系统提供50MHZ频率的时钟源。

完成该系统的硬件和软件的设计,并制作出实物装置,调试好后并能实际运用(指导教师提供制作所需的器件),最后就课程设计本身提交一篇课程设计说明书。

设计工作量1、VHDL语言程序设计;2、波形仿真;3、在实验装置上进行硬件测试,并进行演示;4、提交一份完整的课程设计说明书,包括设计原理、程序设计、程序分析、仿真分析、硬件测试、调试过程,参考文献、设计总结等。

进度安排起止日期(或时间量)设计内容(或预期目标)备注第1天课题介绍,答疑,收集材料第2天设计方案论证第3天进一步讨论方案, 对设计方案进行必要的修正,方案确定后开始进行VHDL语言程序设计第4天设计VHDL语言程序第5天在实验装置上进行硬件测试,编写设计说明书编写设计说明书教研室意见年月日系(部)主管领导意见年月日目录一、概述................................................................ - 3 -1、EDA的介绍........................................................ - 3 -2、篮球比赛电子记分牌的介绍.......................................... - 3 -二、设计目的............................................................ - 4 -三、设计内容及要求...................................................... - 4 -四、设计思路............................................................ - 4 -五、单元模块设计........................................................ - 5 -1、分频模块.......................................................... - 5 -2、计时模块.......................................................... - 6 -3、计分模块.......................................................... - 7 -4、显示模块.......................................................... - 9 -5、消抖模块........................................................ - 10 -六、仿真结果及分析..................................................... - 14 -1、引脚分配图....................................................... - 14 -2、设计仿真图....................................................... - 15 -3、硬件测试........................................................ - 15 -4、仿真结果分析..................................................... - 15 -七、设计总结与心得..................................................... - 16 -八、参考文献........................................................... - 17 -一、概述1、EDA的介绍EDA是电子设计自动化(Electronic Design Automation)的缩写,在20世纪60年代中期从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。

篮球比赛电子记分牌设计

一设计思路分析篮球比赛计时记分系统程序多而且复杂,所以用图形设计方法来设计。

先把每一模块的程序写好,然后生成图形文件,最后新建一个顶层图形文件,把各模块联结起来。

包括的模块有分频模块、计时模块、记分模块、脉冲产生模块、滤波模块、选择模块、声光显示模块,显示模块及消抖模块等。

程序总体框图为:二单元电路设计2.112进制减法计数器这个计数器用来表示每一节比赛的分钟位,它的时钟脉冲应由前一个60进制计数器的CO提供。

具备复位功能。

可以将12进制改为任意进制的减法计数器。

当计数结束后,计数器不再计数。

当CO有效时进行减法计数,当计数器减到0之,SO输出一个高电平。

EN等于1时计数器复位,当C05等于1时实现比赛加时操作。

生成元件图:仿真波形图:2.260进制减法计数器这个计数器用来表示每一节比赛的秒钟位。

要求在完成12个60进制的计数后,计数器不再计数。

具备清零、暂停以及复位的功能。

当CLK有效时进行减法计数,CLR等于1时整个计数器清零,EN等于1时计数器复位,PAUSE等于1时计数器暂停计数,。

当计数器减到0之,CO输出一个高电平。

生成元件图:仿真波形图:2.3 99进制可逆计数器这个计数器用来表示比赛球队分别的得分。

当S 出现上升沿时开始记分,CLR 等于1时整个计数器清零。

生成元件图:仿真波形如下:是 是 是2.61对2数据选择器由于比赛两方的比分不尽相同,所以用一个数据选择器来正确的给某一方加分。

当按下P4时,给A队加分,A的输出为CO;当再次按下P4时,给B队加分,B的输出为CO。

程序流程图:生成元件图:仿真波形如下:2.7脉冲产生器由于比赛的得分分别为1分,2分,3分。

所以对应的,当得分为1时,应当产生1个脉冲,当得分为2时,产生2个脉冲,以此类推。

在输入信号CLK存在的情况下,当P1为高电平,则CO产生1个脉冲信号。

P2为高电平,产生2个脉冲信号。

P3为高电平,产生3个脉冲信号。

生成元件图仿真波形如下:2.8滤波模块从脉冲产生器仿真的波形图看出,输出脉冲会有毛刺,所以加一个滤波模块,用以消除毛刺。

Verilog-篮球30秒可控计时器设计

湖北师范学院教育信息与技术学院2010级信息工程专业综合课程设计(一)Verilog课程设计Verilog curriculum design基于Verilog的篮球30秒可控计时器设计1 设计目的随着生活水平的提高,人们对于生活品质的高要求。

对于时间的准确越来越发期盼。

比如在田径,足球等体育运动中时间的分秒必争显的更加的不可或缺。

在这样的大背景下,计时器也应运而生。

特别在于篮球比赛中通常是零点几秒可以决定各方的悲喜。

人类最早使用的定时工具是沙漏或水漏,但在钟表诞生发展成熟之后,人们开始尝试使用这种全新的计时工具来改进定时器,达到准确控制时间的目的。

在篮球比赛中,规定了球员的持球时间不能超过30秒,否则就犯规了。

本课程设计的“篮球竞赛30秒计时器”,可用于篮球比赛中,用于对球员持球时间30秒限制。

2 设计要求(1)具有30秒计时、显示功能.(2)设置外部操作开关,控制计时器的直接清零、装数、启动和暂停连续功能. (3)30s 倒计时,其时间间隔为1s.(4)计时器递减计时到零时显示器不能灭灯,同时发出报警信号. (5)能解除报警信号 (6)利用modelsim 仿真 (7)完成设计报告3 设计思路及原理原理图如下图所示。

该图包括秒脉冲发生器、计数器、译码显示电路、辅助时序控制电路(简称控制电路)和报警电路等5个部分。

其中,计数器和控制电路是系统的主要部分。

计数器完成30秒计时功能,而控制电路具有直接控制计数器的启动计数、暂停/连接计数、译码显示电路的显示和灭灯等功能。

外部操 作开关图1:30s 计时器的总体参考方案框图表一:篮球30s可控计时器示意图4 设计过程4.1 设计方案论证方案一:通过对要求的分析,在译码显示时若采用静态显示时,需要对两个七段数码管的引脚进行设置,而不需要动态扫描。

此时再进行倒计时时,显示部分的两个数码管同时点亮。

注意此种方案所用的时钟信号为1HZ,若大于或小于1HZ,则会使时间间隔大于或小于1秒。

篮球比赛记分牌电路的设计与仿真分析

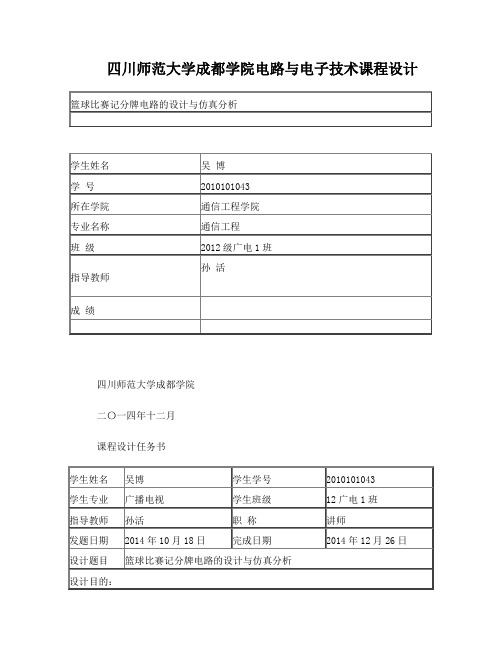

四川师范大学成都学院电路与电子技术课程设计篮球比赛记分牌电路的设计与仿真分析学生姓名吴博学号**********所在学院通信工程学院专业名称通信工程班级2012级广电1班指导教师孙活成绩四川师范大学成都学院二〇一四年十二月课程设计任务书篮球比赛记分牌电路的设计与仿真分析内容摘要:本文介绍了基于数字电路的篮球数字计分牌的设计,在硬件方面使用三片四位二进制加法器74LS161 分别组成1,2,3 进制计数器,用三个开关分别进行1分,2 分,3 分的计数,然后把数值通过逻辑电路输入到十进制加/减计数器74LS192 进行总分的累加。

使用三个七段LED 数码管来进行显示百位,十位,个位,LED 采用的是动态扫描显示,用74LS48 芯片进行驱动。

软件方面使用Multisim对可逆计数器进行仿真,整个系统能够对篮球比赛过程中比赛分数进行计数累加,实现对整个比赛的计分。

关键词:数字记分器 LED 数码管计数器仿真Design and Simulation Analysis basketball gamescoreboard circuitAbstract:This article describes the basketball digital scoreboard digital circuit-based design, using a three-piece four-bit binary adder, respectively, in terms of hardware consisting of 1,2,3 74LS161 binary counter, with three switches for 1 min, 2 min, respectively, 3 points count, then by logic input value to decimal up / down counter 74LS192 be cumulative score. Using three seven-segment LED digital display to one hundred, ten, a bit, LED uses a dynamic scanning display, driven by 74LS48 chip. Software for use Multisim simulation reversible counter, the entire system can score the basketball game during the game counts the cumulative realized for the entire game scoring.Keywords:Digital Marker LED Digital Tube Counter Simulation目录前言 (1)1 Multisim的简介 (2)2 系统总体方案及硬件设计 (3)2.1 总体方案 (3)2.2 记分器电路 (3)2.3 设计所需的元件 (4)3 各模块设计 (4)3.1 数字键盘部分 (4)3.2 编码部分 (7)3.3 数据选择器部分 (7)3.4 移位寄存器部分 (9)3.5 显示部分 (9)4 软件仿真 (11)5 结束语 (12)附录 (13)附录1: 系统原理图 (13)参考文献: (14)篮球比赛记分牌电路的设计与仿真分析前言数字记分牌在许多领域中得到普遍应用,在体育比赛、各种现场抢答比赛、各种互动游戏中均能见其身影。

使用Verilog语言编写的投篮机模块

投篮机设计实践实验目的:用数字电路设计语言编写代码,实现投篮机的基本功能实验仪器:硬件:康芯电子公司所生产的KX-7C5T00578型号开发板软件:Quartu sⅱ功能介绍:1、初始化之后进入投球状态,开始计时2、计时采用倒计时,从60秒到03、投球中一次计数一次,不中不计数4、计数累计,最多计数99次5、倒计时停止时同时停止投球计数实验流程:一、本设计实践采用verilog设计语言二、考虑到投篮机所需功能,本设计分为以下几个模块:1、核心控制模块—负责整个系统的运行,产生整个系统的各模块控制信号2、输入控制模块—负责采集输入的各种信号,并将输入信号滤波3、输出控制模块—将计数值与计时值输出到LED数码管上4、计时模块—初始化之后开始倒计时,每秒递减5、计数模块—每次投中球,计数加一三、五个模块的具体完成过程:在上完理论课之后,我们对Verilog和VHDL语言有了初步的了解,老师告诉我们这门课的关键在于自己的动手实践,于是我们实验小组着手开始了投篮机的设计实践。

首先通过查阅老师给的课件和网上的一些资料,熟悉了一下Quartusii的操作流程,并对两种硬件描述语言有了一个更深的了解,但同时也遇到很多不明白的地方,通过向老师的咨询,对投篮机模块有了一个感性的认识,并准备采用分解模块的方法,进行初步的实践。

随后我们着手进行实现投篮机功能所需模块代码的编写。

起初,我们简单的认为,投篮机无非就是一个计数模块,一个倒计时模块,因此我们只编写这两个模块的代码。

如下:计数模块:module Counter99(LED, keytouch, clr);input keytouch, clr;output[7:0] LED;reg[7:0] LED;always@(posedge keytouch or negedge clr)beginif(!clr)LED <= 8'h00;elseif(LED[3:0] == 4'd9)beginLED[3:0] <= 4'd0;if(LED[7:4] == 9)LED[7:4] = 4'd0;elseLED[7:4] <= LED[7:4] + 1'b1;endelseLED[3:0] <= LED[3:0] + 1'b1;endendmodule计时模块:module BCD_cnt59(qout, clktouch, reset);output[7:0] qout;reg[7:0]qout;input clktouch,reset;always@(posedge clktouch or negedge reset )beginif(!reset)qout <= 0;elsebeginif(qout[3:0] == 4'd0)beginqout[3:0] <= 9;if(qout[7:4] == 0)qout[7:4] <= 5;elseqout[7:4] = qout[7:4] - 1'b1;endelse qout[3:0] <= qout[3:0] - 1'b1;endendendmodule通过在Quartusii上编译,运行,波形仿真,无误。

FPGA实现篮球计数器的设计

课程设计(论文)任务书电气与电子工程学院电子信息工程专业2011- 班一、课程设计(论文)题目篮球计分器二、课程设计(论文)工作自 2014 年 1 月6 日起至2014 年1 月 17 日止。

三、课程设计(论文) 地点: 电子测控实验室四、课程设计(论文)内容要求:1)课程设计任务:设计一个篮球计分器并要求:1)具有30秒计时、显示2)可对计时器清零、置数、启动和暂停3)30秒倒计时4)两个数码管显示两队比分5)超时报警并可解除报警2)课程设计论文编写要求(1)课程设计任务及要求(2)总体电路设计(3)模块设计---给出各个模块的详细设计思路(4)管脚绑定---列表或截图给出管脚绑定情况(5)仿真及FPGA开发板调试---给出运行仿真波形截图,分析运行结果。

(6)设计体会与小结---设计遇到的问题及解决办法,通过设计学到了哪些新知识,巩固了哪些知识,有哪些提高。

(7)参考文献(必须按标准格式列出,可参考教材后面的参考文献格式)(8)报告按规定排版打印,要求装订平整,否则要求返工;(9)课设报告的装订顺序如下:封面---任务书---中文摘要---目录----正文---附录(代码及相关图片)EDA技术课程设计报告(10)严禁抄袭,如有发现,按不及格处理。

3)课程设计评分标准:(1)学习态度:10分;(2)系统设计:20分;(3)代码调试:20分;(4)回答问题:20分;(5)论文撰写:30分。

4)课程设计进度安排进度安排:本设计持续10天,其中最后一天为答辩时间。

第1-2天:讲解题目,准备参考资料,检查、调试实验软硬件,进入设计环境,开始设计方案和验证方案的准备;第3-4天:完成设计与验证方案,经指导老师验收后进入模块电路设计;第5-7天:完成模块电路设计,进行代码输入,并完成代码的初步仿真;第8-9天:代码功能仿真正确,约束设计,综合、下载,实现设计目标,并指导老师验收设计;整理设计资料,撰写报告、准备答辩;第10天:验收合格后进行答辩。

verilog课程设计篮球

verilog课程设计篮球一、教学目标本节课的教学目标是让学生掌握Verilog硬件描述语言的基本知识,学会使用Verilog进行数字电路的设计与仿真,培养学生对电子设计自动化(EDA)的兴趣和创新能力。

具体分解为以下三个目标:1.知识目标:使学生了解Verilog的基本语法、数据类型、运算符、语句和模块化设计方法;掌握基本的逻辑门电路仿真方法,以及简单的组合逻辑和时序逻辑电路设计。

2.技能目标:培养学生能够运用Verilog语言进行数字电路的设计与仿真,熟练使用至少一种EDA工具进行Verilog代码的编写、调试和测试。

3.情感态度价值观目标:培养学生对电子设计自动化的兴趣,增强其对科技创新的热情,培养其团队协作意识和自主学习能力。

二、教学内容本节课的教学内容主要包括以下几个部分:1.Verilog基本语法和数据类型:介绍Verilog的模块、端口、参数、数据类型(如integer、real、string等)和运算符(如算术运算符、关系运算符、逻辑运算符等)。

2.Verilog语句:讲解连续赋值语句、阻塞赋值语句、条件语句(如if-else、case等)、循环语句(如forever、repeat等)和任务与函数。

3.模块化设计方法:介绍模块的定义、封装和实例化,以及模块间的参数传递和端口连接。

4.逻辑门电路仿真:讲解与门、或门、非门、异或门等基本逻辑门电路的Verilog实现方法,并通过仿真验证其功能。

5.组合逻辑电路设计:介绍组合逻辑电路(如编码器、译码器、多路选择器等)的设计方法,并用Verilog实现。

6.时序逻辑电路设计:讲解时序逻辑电路(如触发器、计数器、寄存器等)的设计方法,并用Verilog实现。

三、教学方法为了达到本节课的教学目标,将采用以下几种教学方法:1.讲授法:讲解Verilog的基本语法、数据类型、运算符和语句,以及逻辑门电路仿真方法。

2.案例分析法:通过分析具体实例,使学生掌握组合逻辑和时序逻辑电路的设计方法。

fpga篮球计分器课程设计

fpga篮球计分器课程设计一、课程目标知识目标:1. 学生理解FPGA的基本原理和功能,掌握利用FPGA设计简单数字系统的能力。

2. 学生掌握篮球计分器的基本功能要求,能够运用所学知识设计出满足需求的计分器系统。

3. 学生了解数字电路中计数器、寄存器等基础模块的工作原理,并能够运用这些模块进行系统设计。

技能目标:1. 学生能够运用硬件描述语言(如VHDL/Verilog)对FPGA进行编程,完成篮球计分器的功能设计。

2. 学生通过课程实践,提升问题分析能力,能够根据实际需求设计出合理的数字电路系统。

3. 学生能够使用相关软件(如ModelSim、Quartus)进行电路仿真、调试和验证。

情感态度价值观目标:1. 学生培养对电子信息技术和创新的兴趣,激发学习主动性和创造性思维。

2. 学生在团队协作中提高沟通与协作能力,培养集体荣誉感和责任心。

3. 学生通过篮球计分器的设计,体会科技与日常生活的紧密联系,增强学以致用的意识。

课程性质分析:本课程为电子信息类课程的实践环节,强调理论与实践相结合,注重培养学生的实际操作能力和创新精神。

学生特点分析:学生为高年级中学生,具备一定的电子技术和编程基础,具有较强的逻辑思维能力和问题解决能力。

教学要求:教师需引导学生主动探索,鼓励创新,关注学生在设计过程中的个体差异,提供有针对性的指导,确保学生能够达成课程目标。

通过课程目标的实现,学生能够将所学知识综合应用于实际问题,为未来的学习和职业发展打下坚实基础。

二、教学内容本课程教学内容主要包括以下几部分:1. FPGA基础知识:介绍FPGA的原理、结构和应用,使学生了解FPGA的基本概念,为后续设计打下基础。

教材章节:第三章“可编程逻辑器件及其应用”2. 硬件描述语言编程:讲解VHDL/Verilog基本语法和编程技巧,使学生能够使用硬件描述语言对FPGA进行编程。

教材章节:第四章“硬件描述语言及其编程”3. 数字电路基础:介绍计数器、寄存器等基础模块的工作原理,为篮球计分器设计提供必要的电路知识。

篮球比赛记分牌电路的设计与仿真分析

四川师范大学成都学院电路与电子技术课程设计篮球比赛记分牌电路的设计与仿真分析学生姓名吴博学号2010101043所在学院通信工程学院专业名称通信工程班级2012级广电1班孙活指导教师成绩四川师范大学成都学院二〇一四年十二月课程设计任务书学生姓名吴博学生学号2010101043学生专业广播电视学生班级12广电1班指导教师孙活职称讲师发题日期2014年10月18日完成日期2014年12月26日设计题目篮球比赛记分牌电路的设计与仿真分析设计目的:篮球比赛记分牌电路的设计与仿真分析内容摘要:本文介绍了基于数字电路的篮球数字计分牌的设计,在硬件方面使用三片四位二进制加法器74LS161 分别组成1,2,3 进制计数器,用三个开关分别进行1分,2 分,3 分的计数,然后把数值通过逻辑电路输入到十进制加/减计数器74LS192 进行总分的累加。

使用三个七段LED 数码管来进行显示百位,十位,个位,LED 采用的是动态扫描显示,用74LS48 芯片进行驱动。

软件方面使用Multisim对可逆计数器进行仿真,整个系统能够对篮球比赛过程中比赛分数进行计数累加,实现对整个比赛的计分。

关键词:数字记分器 LED 数码管计数器仿真Design and Simulation Analysis basketball game scoreboard circuitAbstract:This article describes the basketball digital scoreboard digital circuit-based design, using a three-piece four-bit binary adder, respectively, in terms of hardware consisting of 1,2,3 74LS161 binary counter, with three switches for 1 min, 2 min, respectively, 3 points count, then by logic input value to decimal up / down counter 74LS192 be cumulative score. Using three seven-segment LED digital display to onehundred, ten, a bit, LED uses a dynamic scanning display, driven by74LS48 chip. Software for use Multisim simulation reversible counter, the entire system can score the basketball game during the game counts the cumulative realized for the entire game scoring.Keywords:Digital Marker LED Digital Tube Counter Simulation目录前言 11 Multisim的简介 22 系统总体方案及硬件设计 32.1 总体方案 32.2 记分器电路 32.3 设计所需的元件 43 各模块设计 43.1 数字键盘部分 43.2 编码部分 73.3 数据选择器部分 73.4 移位寄存器部分 93.5 显示部分 94 软件仿真 115 结束语 12附录 13附录1: 系统原理图 13参考文献: 14篮球比赛记分牌电路的设计与仿真分析前言数字记分牌在许多领域中得到普遍应用,在体育比赛、各种现场抢答比赛、各种互动游戏中均能见其身影。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字逻辑设计及应用课程设计报告

姓名:

学号:

选课号:79

设计题号:23

一.设计题目

篮球比赛数字计分牌

二.设计要求

1.分别记录两队得分情况;

2.进球得分加2分,罚球进球得分加1分;

3.纠正错判得分减2分或1分;

4.分别用三个数码管显示器记录两队的得分情况。

三.设计过程

(一)设计方案

1.模块设计

题目中要用三个数码管来记录两队的得分情况,本文采用输出为8421bcd码,外接译码器和数码管的方式来实现。

先设计一个带有进位(co)和借位(ci)输出的模块pad,输出端(num)输出4位8421bcd码外接译码器和数码管,pad模块还带有加一输入端(a1),加二输入端(a2),减一输入端(d1),减二输入端(d2)。

输入端与开关相接,操作者按下开关即给该端口一个脉冲信号,各输入端口由上升沿触发。

如果操作者同时按下多个端口,输出端口将保持原来的信号不变。

pad模块功能图见图1-1。

图1-1 pad模块输入输出端口及功能

然后将三个相同的pad模块进行级联,构造为新的模块numberpad,从而得到带有三个数码管的篮球记分牌。

甲乙两队都将分别使用这个记分牌。

级联图见图1-2。

图1-2 pad模块级联图

2.模块内部的算法流程

每个模块有四个输入端口a1,a2,d1,d2来进行触发,触发事件太多,因此构造rem=a1|a2|d1|d2作为新的触发信号。

因此,只要a1,a2,d1,d2中任意一个按键被按下,将会发出一个脉冲,rem也就会产生一个脉冲。

但是可能出现多个按键同时按下的情况,这样会产生冲突。

所以在always语句块中,进行判断,看是否a1,a2,d1,d2中只有一个处于高电平,若同时处于高电平,则输出维持原来的值不变。

判断完端口a1,a2,d1,d2中哪一个输入了以后,就要进行加1,加2,减1,减2的操作。

加1分为以下情况:(1)若num已经计数到9即1001,再加1则num应变为0000,进位端co输出1;(2)若num不为9,则直接加1,co输出0。

加2分为以下情况:(1)若num已经计数到8即1000,再加2则num应变为0000,进位端co输出1;(2)num已经计数到9即1001。

再加2则num应变为0001,进位端co 输出1;(3)若num不为8或9,则直接加2,co输出0/。

减1分为以下情况:(1)若num此时为0,再减1则num应变为9即1001,借位端ci 输出1;(2)若num不为0,则直接减1,ci输出0。

减2分为以下情况:(1)若num此时为0,再减2则num应变为8即1000,借位端ci 输出1;(2)若num此时为1,再减2则num应变为9即1001,借位端ci输出1;(3)若num不为0或1,则直接减2,ci输出0

算法流程图见图1-3

图1-3 算法流程图

(二)V erilog程序

(注:在quatus2中不能编写中文注释,这里的注释为后期编写)

//将pad级联成新的模块numberpad,其中num1,num2,num3分别输出个十百位的8421bcd码

module numberpad(a1,a2,d1,d2,num1,num2,num3);

output [3:0] num1,num2,num3;

input a1,a2,d1,d2; //a1为加1端口,a2为加2端口,d1为减1端口,d2为减2端口

wire co1,co2,co3,ci1,ci2,ci3;

pad(a1,a2,d1,d2,num1,co1,ci1); //将三个pad级联

pad(co1,0,ci1,0,num2,co2,ci2);

pad(co2,0,ci2,0,num3,co3,ci3);

endmodule

//pad模块,输出为4为8421bcd码,由a1,a2,d1,d2来实现加减1、2,有进位和借位端口module pad(a1,a2,d1,d2,num,co,ci);

output reg [3:0] num; //输出4位8421bcd码

output reg co,ci; //co 进位信号, ci is 借位信号

input a1,a2,d1,d2; ///a1为加1端口,a2为加2端口,d1为减1端口,d2为减2端口wire rem;

initial

num<=4'b0000;

assign rem=a1|a2|d1|d2;

always @(posedge rem)

begin

if(a1&&!a2&&!d1&&!d2) //仅a1输入脉冲时加1,必要时进位

begin

if(num==4'b1001)

begin

num<=4'b0000;

co<=1'b1;

end

else

begin

num<=num+4'b0001;

co<=1'b0;

end

end

else if(a2&&!a1&&!d1&&!d2) //仅a2输入脉冲时加2,必要时进位

begin

if(num==4'b1000)

begin

num<=4'b0000;

co<=1'b1;

end

else if(num==4'b1001)

begin

num<=4'b0001;

co<=1'b1;

end

else

begin

num<=num+4'b0010;

co<=1'b0;

end

end

else if(d1&&!a1&&!a2&&!d2) //仅d1输入脉冲时减1,必要时借位

begin

if(num==4'b0000)

begin

num<=4'b1001;

ci<=1'b1;

end

else

begin

num<=num-4'b0001;

ci<=1'b0;

end

end

else if(d2&&!a1&&!a2&&!d1) //仅d2输入脉冲时减2,必要时借位

begin

if(num==4'b0001)

begin

num<=4'b1001;

ci<=1'b1;

end

else if(num==4'b0000)

begin

num<=4'b1000;

ci<=1'b1;

end

else

begin

num<=num-4'b0010;

ci<=1'b0;

end

end

else //多个端口同时输入,输出保持原来的值

begin

num<=num;

co<=1'b0;

ci<=1'b0;

end

end

endmodule

(三)仿真结果

1.验证加1、加2、减1、减2端口正常,个位到十位进位正常

当输入端分别输入加1、加2、减1、减2信号时,输出了相应的结果。

18ns时,执行加1操作,个位num1由1001(即9)变成了0,同时向十位进位,十位num2变成了0001。

31ns时又有一进位,十位num2变成了0010(即2)。

(见图3-1)

图3-1 仿真图像一

2.验证十位向百位进位正常

由图3-2可得,213ns时已计数到199,即个位num1为1001,十位num2为1001,百位num3为0001。

此时输入了加2的信号,输出变成了201,即个位num1变为0001,十位num2变为0000,百位num3变为0010。

由此验证了十位向百位进位正常。

图3-2 仿真图像二

3.验证多个端口同时输入时,保持原值不变

从219ns开始到230秒都有多个端口同时输入,由图3-3可以观察到,输出端口的值并未发生改变。

图3-3 仿真图像三

四、设计结论

(一)设计结果分析

由以上的仿真图像可知,各端口工作正常,通过给a1、a2、d1、d2端口输入脉冲,可以使输出分别进行加1、加2、减1、减2的操作,且个位到十位、十位到百位进位正常,输出为8421bcd码。

当多个端口同时输入时,输出将保持原值,避免了冲突。

(二)设计中遇到的问题

由于a1、a2、d1、d2端口相互独立,刚开始设计时将它们都作为触发端口放在always@后面,发现调试总是有冲突。

后来引入了一个wire型变量rem,将其值赋为a1|a2|d1|d2,从而仅将rem作为触发的事件,然后通过if语句解决了冲突。

(三)设计心得和体会

1.设计程序时首先应该画出流程图,理清逻辑关系,做到条理清晰。

2.当程序调不出来时,不要烦躁和懊恼,更不能放弃,应该仔细阅读程序,一步一步分析、理解,看看哪里出了问题,并寻找解决的办法。

2010年6月20日。