西南交大 实验8 指令存储器与取指令部件的设计

西南交大计算机实验报告

计算机程序设计基础(C++)实验报告信息学院计算机教育中心二零一四年三月实验_0验报告教学班级:___ 7班__ 学生学号:__20133936_学生姓名:____葛劲松实验日期:_____2014.3.11______ 实验地点:______7307___(机房) 指导教师签名:___王威_______ 实验成绩:___________一、实验目的1.熟悉VS2010 集成开发环境;2.学习新建和打开控制台应用程序的方法;3.通过运行示例程序了解程序开发过程;二、实验任务1.新建源程序文件,编辑以下程序,编译,链接,得出运行结果,并保存程序:#include <iostream>using namespace std;void main( ){cout<<'a'<<endl;cout<<'\141'<<endl;cout<<'\x61'<<endl;}2.新建源程序文件,编辑以下程序,编译,链接,运行,输入36和64,得出运行结果,并保存程序:#include <iostream>using namespace std;int main(){float num1,num2,sum;cout << "Enter first number: ";cin >> num1;cout << "Enter second number: ";cin >> num2;sum=num1+num2;cout << "The sum is " << sum << endl;return 0;}三、实验结果1.:运行结果2.实验__1_实验报告一、实验目的1.熟悉C++程序的集成开发环境;2.学习新建和打开控制台应用程序的方法;3.掌握简单数据运算,以及输入与输出方法。

西南交大C++实验八

实验__8__实验报告教学班级:02 学生学号:学生姓名:实验日期:2014.5.14 实验地点:X7308(机房)指导教师签名:__________ 实验成绩:___________一、实验目的1.掌握对一组同类型的数据进行插入、删除、排序和查找等的常用算法。

二、实验任务1. 使用插入排序法将键盘输入的无序数列按升序排列。

思路分析与算法:1)从第一个元素开始,该元素可以认为已经被排序。

2)取出下一个元素,在已经排序的元素序列中从后向前扫描。

3)如果该元素(已排序)大于新元素,将该元素移到下一位置。

4)重复步骤3,直到找到已排序的元素小于或者等于新元素的位置。

5)将新元素插入到该位置中。

6)重复步骤2。

2.选举猴王问题:N 只猴子围成一圈,顺序编号1至N。

从编号为1的猴子开始依次报数,报数m 的猴子就退出圈子,接着再报,报数m 的猴子再退出圈子,依次继续下去,圈子最后所剩的一只猴子为猴王,它原先的编号是几?思路分析与算法:1)使用一维数组存放猴子从1到n的编号,定义参加选举猴王的最多猴子数为40。

2)i为每次循环时计数变量,k为按1,2,3,…m报数时的计数变量,t表示退出的猴子数。

依次将退出的猴子对应的数组元素置0,直到只剩下一只猴子。

3)找出数组中不为0的a[i],输出该数。

三、实验结果(源程序+ 注释)1.#include<iostream>using namespace std;void main (){const int M=20;int a[M],n,temp,i,k;cout<<"输入将要排序的有几个数:"<<endl; cin>>n;cout<<"输入将要排序的数分别为a:"<<endl; for(i=0;i<n;i++)cin>>a[i];for(i=1;i<n;i++){ k=i; temp=a[i];while(k>0&&temp<a[k-1]){a[k]=a[k-1]; k--; }a[k]=temp;}for(i=0;i<n;i++)cout<<a[i]<<" ";system("pause");}2.#include"stdafx.h"#include<iostream>using namespace std;void main(){ int const N=100;int n;int m;int a[N]; int i,k,t;cout<<"请输入参加选举的猴子数目:"; cin>>n;cout<<"输入报数到就退出:";cin>>m;for(i=0;i<n;i++)a[i]=i+1;i=0;k=0;t=0;while(t<n-1){if (a[i]!=0) k++;if(k==m){a[i]=0;k=0;t++;}i++;if(i==n)i=0; }i=0;while(a[i]==0) i++;cout<<"剩下第<<a[i]<<"个猴子<<endl;system("pause");}。

西安交通大学计算机组成原理实验报告

西安交通大学计算机组成原理实验报告姓名:***班级:物联网**学号:实验一存储器的访问与实现一、实验目的1、理解计算机主存储器的分类及作用;2、掌握ROM、RAM的读写方法。

二、实验原理存储器按存取方式分,可分为随机存储器和顺序存储器。

如果存储器中的任何存储单元的内容都可随机存取,称为随机存储器,计算机中的主存储器都是随机存储器。

如果存储器只能按某种顺序存取,则称为顺序存储器,磁带是顺序存储器,磁盘是半顺序存储器,它们的特点是存储容量大,存取速度慢,一般作为外部存储器使用。

如果按存储器的读写功能分,有些存储器的内容是固定不变的,即只能读出不能写入,这种存储器称为只读存储器(ROM);既能读出又能写入的存储器,称为随机读写存储器(RAM)。

实际上真正的ROM基本上不用了,用的是光可擦除可编程的ROM(EPROM)和电可擦除可编程的ROM(EEPROM)。

EEPROM用的越来越多,有取代EPROM之势,比如容量很大的闪存(FLASH)现在用的就很广泛,常说的U盘就是用FLASH做的。

按信息的可保存性分,存储器可分为非永久性记忆存储器和永久性记忆存储器。

ROM、EPROM、EEPROM都是永久记忆存储器,它们断电后存储内容可保存。

RAM则是非永久性记忆存储器,断电后存储器中存储的内容丢失。

随机读写存储器类型随机存储器按其元件的类型来分,有双极存储器和MOS存储器两类。

在存取速度和价格两方面,双极存储器比MOS存储器高,故双极存储器主要用于高速的小容量存储体系。

在MOS存储器中,根据存储信息机构的原理不同,又分为静态随机存储器(SRAM)和动态随机存储器(DRAM)。

静态随机存储器采用双稳态触发器来保存信息,只要不断电,信息就不会丢失;动态随机存储器利用记忆电容来保存信息,使用时只有不断地给电容充电才能使信息保持。

静态随机存储器的集成度较低,功耗也较大;动态随机存储器的集成度较高,功耗低。

现在计算机中,内存容量较大,常由动态随机存储器构成。

15秋西南交大《汇编语言程序设计》在线作业一答案

西南交《汇编语言程序设计》在线作业一一、多选题(共 10 道试题,共 20 分。

)1. 磁盘一般由那两部分组成(). 系统区. 功能区. 数据区. 程序区正确答案:2. 算术指令用来执行算术运算,他们中有那两类(). 双操作数. 单操作数. 三操作数. 多操作数正确答案:3. 汇编程序的主要功能有(). 检查源程序. 测出源程序中的语法错误,并给出出错信息. 产生源程序的目标程序,并可给出列表文件. 展开宏指令正确答案:4. 80X86指令系统可以分为以下几种(). 数据传输指令. 串处理指令. 算术指令及逻辑指令. 控制转移指令及处理机控制指令正确答案:5. 软件中断通常由那三种情况引起(). 由中断指令INT引起. 由于PU的某些错误而引起. 为调试程序设置的中断. 各种外部设备的中断正确答案:6. 循环程序由那三部分组成(). 设置循环的初始状态. 循环体. 循环控制部分. 循环标识正确答案:7. 操作数可以是(). 常数. 寄存器. 变量. 表达式正确答案:8. 在程序中调用子程序指令有(). LL. RET. SU. ZF正确答案:9. 为运行汇编语言程序至少要在磁盘上建立以下文件(). 编辑程序. 汇编程序. 连接程序. 调试程序正确答案:10. 计算机的指令由那两部分组成(). 操作码. 操作平台. 操作数. 操作范围正确答案:西南交《汇编语言程序设计》在线作业一二、单选题(共 20 道试题,共 40 分。

)1. 下面的数据传送指令中,错误的操作是()。

. MOV SS:[X+I],1000H. MOV X,1000H. MOV WOR PTR[X],1000H. MOV S,2000H正确答案:2. 某数据段如下: T SEGMENT ORG 20H X 12H Y W 789H T ENS 则Y 单元的偏移址是( )。

. 0. 20H. 21H. 12H正确答案:3. T SEGMENT 1 32 UP(?) 2 W 1456H,789H 3 W 2 T ENS … MOV X, 3 上述指令执行后,X 中的内容是( )。

计算机组成原理实验参考答案(西南交大)

[原创]西南交通大学计算机组成实验参考答案注1、引脚分配依照EP3C40F780C8芯片注2、一定要参照实验指导书阅读此文实验一:多路数据选择器的设计f=((~sel)a)+((sel)b)当sel=0时,f=a,否则f=b。

引脚分配参考:a[3:0] AH12 AF14 AA8 AB8b[3:0] AF12 AG12 AA10 U8f[3:0] E24 F22 E22 F21sel: AC5实验二基于原理图方式的3-8译码电路的设计f0=(~en)+(~a)(~b)(~c)f1=(~en)+(~a)(~b)cf2=(~en)+(~a)b(~c)f3=(~en)+(~a)bcf4=(~en)+a(~b)(~c)f5=(~en)+a(~b)cf6=(~en)+ab(~c)f7=(~en)+abcen为使能端,低电平有效,高电平时输出全为1。

引脚分配参考:a: AH12,b: AF14,c: AA8,en: AC5f[7:0] F24 H24 H23 L23 L24 M24 J22 AE8实验三四位加法器设计实验思路:用Verilog HDL语言编写一位全加器,再用原理图方式用四个全加器组合实现四位加法器。

Adder.vmodule Adder(a, b, cin, cout, sum);input a, b, cin;output cout, sum;assign {cout, sum}=a+b+cin; endmodule原理图:{cout, sum}=a+b+cincin为进位输入,cout为进位输出。

引脚分配参考:a[3:0] AH12 AF14 AA8 AB8b[3:0] AF12 AG12 AA10 U8sum[3:0] E24 F22 E22 F21cin: AC5,cout: F24实验四:七段LED数码管显示译码器设计本实验使用Verilog HDL实现。

module Exp4(f, clk, rst, in, out, sel);input [15:0]in; //输入input f, clk, rst; //计数开关,时钟,置零开关output reg[7:0]out; //数码管输出output reg[2:0]sel; //数码管3-8译码器输出reg[15:0]counter;reg[3:0]data;reg clk_alt;reg[9:0]l;//change frequency 变频段always @(posedge clk)beginif(l>=1023)l=0;else l=l+1;clk_alt=l[2];end//select 选择在哪一个数码管显示always @(posedge clk)beginsel=sel+1;if(sel>=4)sel=0;case(sel)0:data=counter[3:0];1:data=counter[7:4];2:data=counter[11:8];3:data=counter[15:12];endcaseend//count and reset 计数和清零always @(posedge clk_alt or posedge rst)beginif (rst==1) counter=0;else if (f==1) counter=in;else counter=counter+1;end//translate 译码段,此处可以使用二进制或十六进制,后面的实验同,不再赘述。

计算机组成原理实验八简单模型计算机实验

计算机组成原理实验八简单模型计算机实验关键信息项:1、实验目的2、实验设备3、实验原理4、实验步骤5、数据记录与分析6、注意事项7、故障处理8、实验结果评估标准11 实验目的本实验旨在通过构建和操作简单模型计算机,深入理解计算机组成原理中的核心概念,包括数据存储、运算处理、指令执行等,培养学生的实际动手能力和对计算机系统的综合理解能力。

111 具体目标1111 掌握简单模型计算机的基本结构和工作原理。

1112 熟悉各种指令的编码和执行过程。

1113 能够运用所学知识设计和实现简单的计算任务。

12 实验设备121 硬件设备计算机主机、实验箱、连接线等。

122 软件工具特定的模拟软件、编程环境等。

13 实验原理131 模型计算机结构包括运算器、控制器、存储器、输入设备和输出设备等主要部件,以及它们之间的连接和协同工作方式。

132 指令系统定义了各种操作指令的格式、功能和编码方式。

133 数据存储与传输说明数据在存储器中的存储方式和在各部件之间的传输机制。

14 实验步骤141 连接实验设备按照正确的方式将计算机主机与实验箱等设备进行连接,并确保连接稳定可靠。

142 启动软件工具打开相应的模拟软件和编程环境,进行初始化设置。

143 设计指令序列根据实验要求,设计一系列的指令来完成特定的计算任务。

144 输入指令到模型计算机通过编程环境将指令输入到模型计算机的存储器中。

145 启动模型计算机运行设置相关参数,启动模型计算机执行指令序列。

146 观察运行过程和结果密切观察模型计算机在执行指令过程中的各种状态变化,以及最终的输出结果。

15 数据记录与分析151 记录实验过程中的关键数据包括指令的执行时间、存储器的状态变化、运算结果等。

152 对数据进行分析对比预期结果,分析实验数据的准确性和合理性,找出可能存在的偏差和错误原因。

16 注意事项161 设备操作规范严格按照设备的操作说明进行连接和使用,避免因不当操作造成设备损坏。

西安交通大学操作系统原理课件第八章

– Physical address • An address viewed by the physical memory

地址重定位

将程序装入到与其地址空间不一致的物理空间,所引 起的一系列地址变换过程。

静态地址重定位

• 在装入一个作业时,把作业中的指令地址全部转换为绝对地址, 在作业执行过程中就无须再进行地址转换工作。

8.2 存储器管理方式

虚拟存储管理方式:满足用户对大容量内存的需要,提 高内存利用率。 – 请求分页管理方式 – 请求分段管理方式 – 请求段页式管理方式

8.2.1Contiguous Allocation

Main memory usually divided into two partitions: (主存通常被分为两部分) – Resident operating system, usually held in low memory with interrupt vector.(为操作系统保 留的部分,通常与中断矢量保存在内存低端。) – User processes then held in high memory.(用 户进程保存在内存高端)

Memory-Management Unit (MMU)

内外存间的数据交换

overlay覆盖

– 由用户程序控制 – 要求用户清楚地了解程序的结构,并指定各程序段调入内存

的先后次序,它是一种早期的主存扩充的方式

swapping交换

– 由操作系统控制 – 利用外存空间(进程交换区),通过对进程实体的整体交换,

固定分区(大小相同)

Operating System 8M 2M 4M 6M 8M

8M

12 M

西南交大微机

西南交大微机全书共分9章,内容安排上注重系统性、先进性与实用性,各章前后呼应,着眼于如何设计一个实用的微型机系统。

前四章介绍了微型计算机组成的一般概念及必备知识,以8086/8088为蓝本介绍了微型机系统的组成原理、体系结构、编程模型、工作模式、操作时序、寻址方式、指令系统、汇编语言程序设计方法,并介绍了从80x86到pentium系列的寄存器及指令的扩充;第五章讨论存储器的原理和使用,并对内存条及闪速存储器作了适当介绍:第六、七章论述中断系统和i/o接口技术,重点分析了中断控制器8259a、计数器/定时器8253/8254、通用并行接口82c55、通用串行接口16c550、dma控制器8237a、串行a/d转换器max1148及i2c总线模/数转换器ads1100,逐一讲解了各关键接口部件的原理和应用,并以cpld/fpga来实现这些器件的部分功能;第八章以pentium 为对象介绍现代微机系统,着重对存储管理技术、虚拟存储技术、流水线技术以及32位微型机系统的高速缓存技术作了详尽的阐述,并在此基础上对pentium的技术特点作了说明和总结;第九章论述汇编语言高级编程,尤其是c/c++与汇编混合编程技术,可视为对前面所学知识的总结和提高。

本书可作为大专院校电类非计算机专业和其他相近专业本科生的教材,也可作为计算机ⅲ级考试的培训教材,还可供从事微型计算机系统设计和应用的技术人员自学和参考。

第一章微型计算机基础第二节微型计算机的数制及其转换第三节非数值数据的编码方法第四节微型计算机的二进制数运算第五节原码、补码、反码及其适当的运算法则第六节数的定点与浮点表示第二章8086微处理器及其系统结构第一节8086微处理器的结构第二节80x86寄存器的拓展与扩展第三节8086微处理器引脚的功能第四节8086系统的存储器非政府第五节8086的时钟和总线周期第六节ibmpc/xt微机的基本布局第三章8086/8088的寻址方式和指令系统第一节指令的基本格式第二节8086/8088的寻址方式第三节8086/8088指令系统第四节80x86的寻址方式及新增的指令第五节中断指令及dos功能调用第四章汇编语言程序设计第二节汇编语言程序格式第三节程序块定义伪指令第四节masm中的表达式和运算符第五节伪指令及宏指令第六节汇编语言程序设计方法第五章存储器第一节存储器分类第二节随机存取存储器ram第三节半导体只读存储器rom第四节存储器的扩展第五节微机常用操作系统的内存管理第六章中断系统第一节中断的基本概念第二节8086/8088中断系统第三节8259a可编程中断控制器第七章基本输入输出接口第一节微型计算机USB详述第二节8086/8088cpu与外设问的数据交换方式第三节82c55循序i/oUSB第四节可编程计数器/定时器8253/8254第五节异步以太网通信及其可编程USB芯片16c550第六节串行a/d转换器及其接口第七节dma控制器8237a第八节微机外围接口电路的cpld/fpga实现习题与思考题第八章现代微处理器及其系统结构第一节现代微处理器的内部结构第二节现代微机的基本结构第三节pci总线第九章汇编语言高级编程第一节内存驻留及时钟显示程序第二节三窗口全屏幕输出程序第四节程序中运行另一个程序的程序第五节程序中继续执行dos命令的程序第六节如何加密/解密数据文件第七节fortran调用汇编语言子程序第八节pasca1和汇编语言的连接第九节c/c++与编订混合编程技术第十节彩色动态图形程度第三章aascii码点的表明输入码第三章b8086/8088指令系统一览表第三章c中断向量地址表中附录ddos功能调用第三章ebios中断调用附录f调试程度debug的主要命令参考文献。

西安交通大学-汇编语言-实验报告(2015)

汇编语言实验报告计算机xx班21x0505xxx xx2015年6月2日验结果第二题第三题第四题第五题验结果第七题:建议1.上机实验太少,可以考虑增加上机次数。

2.两次上机时间相隔太久,最好可以将上机时间提前。

3.可以增加一些选作的课程设计,满足不同需求的同学。

下附各个题目代码;第二题:data segmentm dw -1,0,0,1,-2,-3,-4,4max dw 0dizhi dw ?data endscode segmentmain proc farassume cs:code,ds:datamov ax,datastart: push dssub ax,axpush axmov ax,datamov ds,axlea bx,mmov cx,8t1: m ov ax,[bx]test ax,8000hjz t2neg axt2: c mp ax,maxjb t3mov max,axmov dizhi,bxt3: a dd bx,2loop t1mov ax,axretmain endpcode endsend start第三题:data segmentcount db 5 dup(0)data endscode segmentmain proc farassume cs:code,ds:datastart: mov ax,datamov ds,axs1: mov cx,10dcall fenleicall dispmov ax,4c00hint 21hretmain endpfenlei proc near input: mov ah,1int 21hcmp al,0dhjz exitsub al,30hcmp al,01hjb inputcmp al,05hja inputmov ah,0cbwmov bx,axdec bxinc count[bx]loop input exit: retfenlei endpdisp proc nearmov si,0mov bx,5s: mov dl,count[si]add dl,30hmov ah,2int 21hinc sidec bxcmp bx,0ja sretdisp endpcode endsend start第四题:data segmentscore dw 76,69,84,90,73,88,99,63,100,80 S6 dw 0S7 dw 0S8 dw 0S9 dw 0S10 dw 0code segmentmain proc farassume cs:code,ds:datastart: push dssub ax,axpush axmov ax,datamov ds,axs1: mov cx,10call fenleimov ax,1retmain endpfenlei proc nearmov si,0s2: mov ax,score[si]mov bx,10div blmov bl,alsub bx,6sal bx,1inc S6[bx];S6为S6,S7,S8,S9,S10的首地址add si,2;根据((socre)/10-6)*2决定该成绩送给哪一个单元loop s2retcode endsend start第五题:data segmentx db '123456'y db 0data endscode segmentmain proc farassume cs:code,ds:data start: push dssub ax,axpush axmov ax,datamov ds,axmov ax,2IF (y-x) gt 5rept 10add ax,axendmendifmov bx,1retmain endpend start第六题:datarea segmentM dw 0datarea ends;------------------------------program segmentmain proc farassume cs:program,ds:datarea start:push dssub ax,axpush axmov ax,datareamov ds,ax;get interrupt vectormov al,1chmov ah,35hint 21hpush espush bx;set interrupt vectorpush dsmov ax,seg countmov ds,axmov dx,offset count mov al,1chmov ah,25hint 21hpop ds;--------------------------int 1chint 1chint 1chint 1ch;in al,21h;and al,11111110b;out 21h,al;sti;------------------------;mov di,1000;delay:;dec di;jnz delay;reset interrupt vector pop dxpop dsmov al,1chmov ah,25hint 21hretmain endpcount proc nearstiinc Miretcount endpprogram endsend start第七题:data segmentscore db 7,5,9,1,3,6,8,0,2,4 buffer db 10 dup(1)data endscode segmentmain proc farassume cs:code,ds:data start: push dssub ax,axpush axmov ax,datamov ds,axmov si,0mov cx,10lea bx,scoreinput: mov ah,1int 21hcmp al,0dhjz exitsub al,30hjb inputcmp al,09hja inputxlat;[(bx)+(al)]->almov buffer[si],alinc siloop input exit: mov ax,axretmain endpcode endsend start。

西南交通大学,测试计量技术与仪器考研专业课

参考书目:《微型计算机原理与接口技术(第二版)》清华大学出版社冯博琴吴宁主编考试题型:选择论述程序填空存储器设计接口设计考试重点:第一章:微型计算机基础概论1:P5 冯·诺依曼的工作原理(原题)2:P8 微机系统的构成图1-4 原题3:P9 CPU的构成(有两种构成方式)原题4:P14 数制和编码必考包括逻辑计算,原码、反码、补码,P33 8位二进制的三种范围P34 溢出判断本点题型注意P35课后题第二章:微处理器与总线1: CPU两种内部结构分类的方式以及各部分的作用(EU/BIU ;运算器、控制器、寄存器组)2:P40 8086和8088的区别,P46 中部也有3:P41 内存分段管理技术,重点4:P42 最大最小模式的区别5:P43 图2-5 处理器芯片,考前应能把所有引脚的主要作用都记清楚,在后续章节中也都有涉及6:P47 图2-7 物理地址的生成方法7:P47 内部寄存器,各种重要,状态标志位的判断必考,控制标志也比较重要。

8:P49 物理地址与逻辑地址、段存储器的使用9:P51 工作时序,注意等待时钟周期80386 不考10:P74总线,不做重点,了解总线概念,分类即可第三章:8086/8088指令系统1:这一章主要是通透,从前往后都要好好看懂,特别是各种操作数的区别2:指令的执行时间、CISC和RISC指令系统不考3:寻址方式,必考4:指令系统都是重点,堆栈尤其重要,P113、120下表一般不会涉及5:串操作指令P128中源串和目标串的区别6:各种指令,有常用和不常用之分,但无法保证不常用的不考,所以应突出重点,兼顾其他。

7:P143 处理器控制指令,新增指令不考第四章:汇编语言程序设计1:程序的结构最重要,应能按照格式写出一条完整的程序,几个例子要好好研读2:指令性语句和指示性语句的区别。

3:伪指令也都挺重要,特别是几个例子例4-4,4-5 可直接忽略4:宏定义,DOS调用也会有些涉及,DOS中最重要的是指令的格式,即P166 使用方法5:章节4.4 设计基础,可仔细研读,知道不懂的地方,因为最后那几个确实很难懂,深度肯定也达不到第五章存储器系统1:P193 存储器系统的一般概念性能指标直接可忽略2:注意存储器的分类3:声明:不用记芯片标号和引脚,考试时会直接给,所以只要把书中出现的芯片大致记住各个引脚的作用即可,要牵扯存储器的设计,有画图。

西南交通大学C实验报告

计算机程序设计基础(C++)实验报告软件学院二O一O年三月11实验__1__实验报告教学班级: 6 学生学号:学生姓名:指导教师签名:王健金焕实验成绩:___________一、实验目的1.熟悉Visual studio 6.0集成开发环境;2.学习新建和打开控制台应用程序的方法;3.通过运行示例程序了解程序开发过程;二、实验任务.输出下面图形:12.输入一摄氏温度,输出显示所转换的华氏温度。

(提示:摄氏温度=(华氏温度-32)×5/9)三、实验结果(源程序+ 注释)#include<iostream>using namespace std;void main(){cout<<" * "<<endl;cout<<" * * * * "<<endl;cout<<" * * * * "<<endl;cout<<" * "<<endl;}2233#include<iostream>using namespace std;void main(){double a,b;cout<<"请输入一摄氏温度:"<<endl;cin>>a;b=a*9/5+32;cout<<"对应的华氏温度是:"<<b<<endl;}4 455实验__2__实验报告一、实验目的1.掌握对一般数据的输入和输出格式控制方法;2.掌握对实型数据输出形式的设置和小数位数的控制方法;3.了解数据输入的相关注意事项。

二、实验任务1. 输入一台计算机的编号和该计算机的价格,并输出这些信息。

(如编号为10987654321,价格为5 998.00元,注意此处计算机的编号作为一个整数而言超出了int 所定义的变量的存储范围,因此只能用double 型变量来存储,但输出时要求看见的是整数形式的编号)2. 输入三个同学的学号,计算机和英语课程的考试成绩,并输出这些信息。

8位CPU的设计

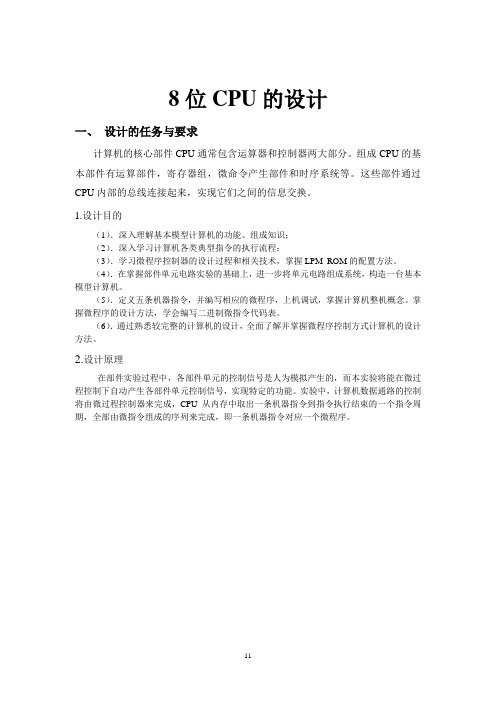

8位CPU的设计一、设计的任务与要求计算机的核心部件CPU通常包含运算器和控制器两大部分。

组成CPU的基本部件有运算部件,寄存器组,微命令产生部件和时序系统等。

这些部件通过CPU内部的总线连接起来,实现它们之间的信息交换。

1.设计目的(1).深入理解基本模型计算机的功能、组成知识;(2).深入学习计算机各类典型指令的执行流程;(3).学习微程序控制器的设计过程和相关技术,掌握LPM_ROM的配置方法。

(4).在掌握部件单元电路实验的基础上,进一步将单元电路组成系统,构造一台基本模型计算机。

(5).定义五条机器指令,并编写相应的微程序,上机调试,掌握计算机整机概念。

掌握微程序的设计方法,学会编写二进制微指令代码表。

(6).通过熟悉较完整的计算机的设计,全面了解并掌握微程序控制方式计算机的设计方法。

2.设计原理在部件实验过程中,各部件单元的控制信号是人为模拟产生的,而本实验将能在微过程控制下自动产生各部件单元控制信号,实现特定的功能。

实验中,计算机数据通路的控制将由微过程控制器来完成,CPU从内存中取出一条机器指令到指令执行结束的一个指令周期,全部由微指令组成的序列来完成,即一条机器指令对应一个微程序。

11该CPU 主要由算术逻辑单元ALU,数据暂存寄存器DR1、DR2,数据寄存器R0~R2,程序计数器PC,地址寄存器AR,程序/数据存储器MEMORAY,指令寄存器IR,微控制器uC,输入单元INPUT 和输出单元OUTPUT 所组成。

图中虚线框内部分包括运算器、控制器、程序存储器、数据存储器和微程序存储器等,实测时,它们都可以在单片FPGA 中实现。

虚线框外部分主要是输入/输出装置,包括键盘、数码管、LCD 显示器等,用于向CPU 输入数据,或CPU 向外输出数据,以及观察CPU 内部工作情况及运算结果。

二、单元电路设计1、运算部件运算部件的任务是对操作数进行加工处理。

主要由三部分组成:(1) 输入逻辑。

西南交大数电实验报告

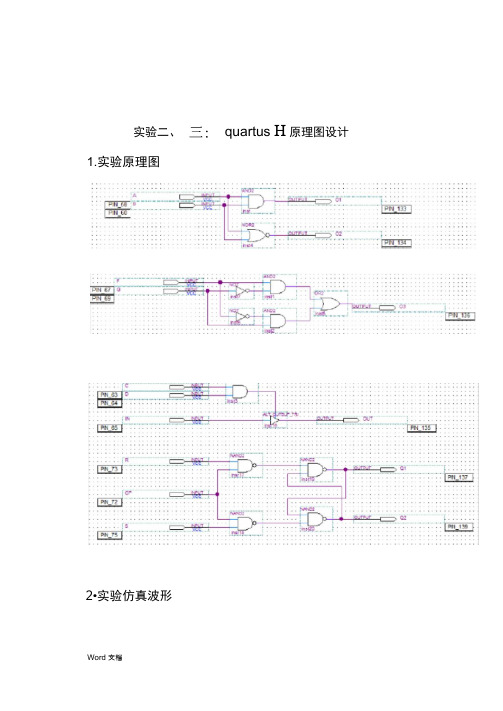

实验二、quartus H原理图设计1.实验原理图2•实验仿真波形Q 1—L .L "r rB s J2J 1 L I -.lz I:m m【1R1■勺暨HLI XJBU-JU2LXJL H JLQ1 UEkXJL D L n t I'll 0 X[ll l IL&L 1 JLD L 0 X C^L J L I IU ■£ LZL 1 I [SL a 1 WL 4IDE 、 CHJ O I [ M J3D] X mEl X I3[K'S S[|]I dt E3J J W] I [|]El I [3]2 GMj ____ i1 ___ i ___ ---------- rJ」----------- ri ---------------JF-I__l:ri mini. run. wi jtm. mi c^rrn i FI znn WCTI inr RI I TH . KJ I ITT mjt x mjiu x x si ini. TJI t PJI CSJ [Dl.、 口 ■ i CJ x r 闻a :is] l!l X [Di 9( [13 K BI 口 】X □】X Hl :[B-i x [T| i [D]J______ LL--------------1L -----------------------------r1 ---------- 1_ _| ------------------------------------------ 1_ 1 --------- 11Dffl「厂m ZnrrzzcTJt IIJ: 〔m JI cn x iWftfisa?r1实验四:Verilog描述组合逻辑电路1•一位数值比较器1.1源代码module compare(a_gt,a_eq,a_lt,a,b); in put a,b;output a_gt,a_eq,a_lt;assig n a_gt=a&~b;assig n a_eq=a&b|~a&~b; assig na_lt=~a&b;en dmodule1.2代码生成原理图2•七段译码器2.1源代码module decode4_7(codeout,i ndec); in put[3:0] in dec;output[6:0] codeout; reg[6:0] codeout;always(i ndec)begincase(i ndec)4'd0:codeout=7'b1111110;4'd1:codeout=7'b0110000;4'd2:codeout=7'b1101101;4'd3:codeout=7'b1111001;4'd4:codeout=7'b0110011;4'd5:codeout=7'b1011011;4'd6:codeout=7'b1011111;4'd7:codeout=7'b1110000;4'd8:codeout=7'b1111111;4'd9:codeout=7'b1111011;default: codeout=7'b1001111;endcaseenden dmodule2.2代码生成原理图么;气一1indec(5 .0] ™deout[Si. ft]ing-t3.总原理图4•实验仿真波形图实验五:集成触发器的应用1.原理图2•实验仿真波形图实验六:移位寄存器实验1.原理图"74193 s3i2•实验仿真波形图实验七:十进制可逆计数器1•十进制可逆计数器1.1十进制可逆计数器源代码module s2014111909(clk,ud,q,co);in put clk,ud;output reg [3:0] q;output co;assign co=((q==9)&&ud)||((q==0)&&(!ud)); always (posedge clk) beginif(ud)beginif(q>8) q<=0;else q<=q+1'd1;endelsebeginif(q==0) q<=4'd9; else q<=q-1'd1;endend en dmodule1.2代码生成原理图1.3实验仿真波形图2•总原理图3•波形图^TumnrDwtjmmuTnromnnrtJwtTUUTnnnnnjuumn砂□*.吐ocooctoi-x耶肋™坯U斗却“、QT0 衣©* 1a*毋*t>6❾丫W L:14& 1.2QAneOCQDOEOFOG曰tL冋-问讪]-110]T I——I —n i=实验八:脉冲宽度调制(PMW)实验1•实验代码module s1909(clk,h,l,out);in put clk;in put[3:0] h,l;output reg out;reg[6:0]pwmcnt; reg[11:0]fcnt;wire [6:0]乙reg clk1;assig n z=h*10+l;always(posedge clk)beginif(fcn t>=12'd2499)begi n clk1<=~clk1; fen t<=0;e nd elsebegi n fen t<=fc nt+1;e ndendalways(posedge clk1)beginif(pwmc nt<z)begi n out=1;e ndelse if(pwmc nt>=7'd99)begi n pwmc nt=0;out=0;e nd else begi n out=0;e nd pwmcnt=pwmc nt+1;enden dmodule2.波形图。

ASIC实验报告(8位CPU的设计)

ASIC设计实验报告学院:电子工程学院学号:2014*******姓名:***指导老师:***2014年11月13日一、实验目的:通过对ASIC实验课的学习,应当学会以下几点:1.熟悉Linux操作系统的应用环境,基本命令行的应用,以及对vi编辑器熟练应用。

2.熟练掌握Verilog编程语言,包括基本组合逻辑电路的实现方法,基本时序逻辑电路的实现方法,怎样使用预定义的库文件,利用always块实现组合逻辑电路的方法已经着重了解assign与always 两种组合逻辑电路实现方法之间的区别,深入了解阻塞赋值与非阻塞赋值的概念以及应用的差别,有限状态机(FSM)实现复杂时序逻辑的方法,以及学会在Linux 系统环境当中应用Synopsys工具VCS进行仿真。

3.熟悉电路设计当中的层次化、结构化的设计方法。

4.熟悉CPU当中有哪些模块组成,模块之间的关系,以及其基本的工作原理。

5.学会利用汇编语言设计程序,注意代码规范性要求。

二、实验要求:按照实验指导书上的要求即:CPU各个模块的Verilog语言代码的编写、编译及仿真正确,并在规定的时间内完成。

要求对CPU进行语言级系统仿真结果正确之后,利用该实验当中采用的八个汇编关键字,编写一个能够实现某种功能的小程序。

然后对其中的控制器电路进行综合,并检查Timing 和Power,进行门级仿真。

三、实验内容:设计一个8位RISC_CPU 系统。

(RISC: Reduced Instruction Set Computer),它是一种八十年代才出现的CPU,与一般的CPU相比,不仅只是简化了指令系统,而且通过简化指令系统使计算机的结构更加简单合理,从而提高了运算速度。

从实现的方法上,它的时序控制信号部件使用了硬布线逻辑,而不是采用微程序控制方式,故产生控制序列的速度要快的多,因为省去了读取微指令的时间。

此CPU所具有的功能有:(1)取指令:当程序已在存储器中时,首先根据程序入口地址取出一条程序,为此要发出指令地址及控制信号。

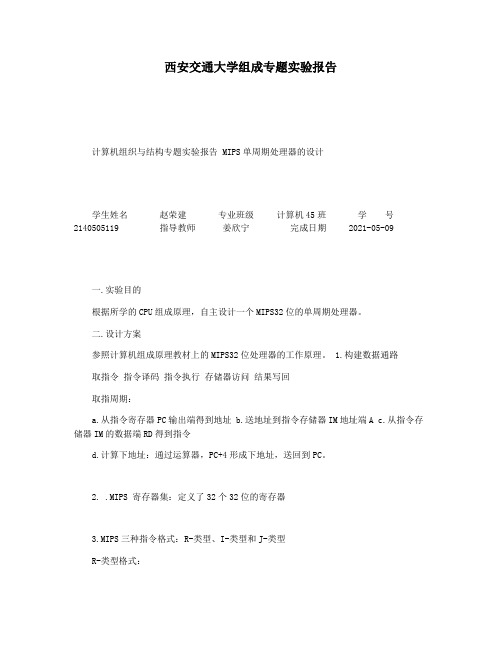

西安交通大学组成专题实验报告

西安交通大学组成专题实验报告计算机组织与结构专题实验报告 MIPS单周期处理器的设计学生姓名赵荣建专业班级计算机45班学号2140505119 指导教师姜欣宁完成日期 2021-05-09一.实验目的根据所学的CPU组成原理,自主设计一个MIPS32位的单周期处理器。

二.设计方案参照计算机组成原理教材上的MIPS32位处理器的工作原理。

1.构建数据通路取指令指令译码指令执行存储器访问结果写回取指周期:a.从指令寄存器PC输出端得到地址b.送地址到指令存储器IM地址端Ac.从指令存储器IM的数据端RD得到指令d.计算下地址:通过运算器,PC+4形成下地址,送回到PC。

2. .MIPS 寄存器集:定义了32个32位的寄存器3.MIPS三种指令格式:R-类型、I-类型和J-类型R-类型格式:* 所有指令操作吗OP都是0;特定操作由funct决定。

* 机器语言指令中,字段分配格式如上图;前两个寄存器rs、 rt是源寄存器,rd是目的寄存器。

而在汇编语言格式中,第一个寄存器是目的寄存器。

如:add $t0,$s4,$s5 #[rd]=[rs]+[rt],[t0]=[s4]+[s5]; I-类型格式:* 指令含4个字段;op, rs, rt 和 imm* 有两个寄存器操作数和一个16位立即数操作数,一些指令中,rt也可作为源寄存器。

J-类型格式:* 有一个26位立即数操作数,扩展后形成目的地址。

4.算逻单元ALU的设计<<210Add<<2JumpMemToReg4Add01ControlMemReadMemWriteBranchALUopALUsrcRegWriteIn structionMemoryPC0R1Rdata132R21RegisterFileW1WdataALU32zeroResult32AddrRdata20212DataData0321Memory3Wdata{15~0}sign32 extend2ALUcontrol6{5~0}ALU工作原理图BA321zeroALU3232Result* 两级控制:通过系统控制器(Control)3ALUoperFunc6ALUcontrol2ALUop 和运算器控制器(ALU Control)产生 ALU的控制信号:ALUoper* ALU控制信号对照表:ALUop Func(来自R型指令的func字段)操作 ALUop1 ALUop2 F5 0 0 1 1 1 1 1 0 1 × × × × × × × × × × × × F4 × × × × × × × F3 × × 0 0 0 0 1 F2 × × 0 0 1 1 0 F1 × × 0 1 0 0 1 F0 × × 0 0 0 1 0 010:ADD 110:SUB 010:ADD 110:SUB 000:AND 001: OR 111:SLT 5.单周期数据通路的构建1)构件:PC、指令存储器、寄存器文件RF和数据存储器; 2)取指令的过程:PC→IM: A/RD3)取源操作数的过程:IM:RD→RF:A1/RD1。

西南交大 实验六 CPU寄存器组设计

实验六CPU寄存器组设计西南交大计算机组成原理实验(代码)实验要求:用VDHL语言设计CPU寄存器组,其包括4个8位通用寄存器(R0-R3)和一个8位专用寄存器PC,R0-R3&PC操作方式见下表格,之后要将PC和R0-R3(其中一个)输出并用4个数码管显示。

R0-R3:寄存器控制信号操作RA1 RA0 Wr RdR0 0 0 0 1 写入1 0 读出R1 0 1 0 1 写入1 0 读出R2 1 0 0 1 写入1 0 读出R3 1 1 0 1 写入1 0 读出PC:Clk’event and clk=’0’Reset=0 Reset=1PC<=0 M=0 PC<=d(15 downto 8)M=1 PC<=PC+1M=2 PC<=PC-1实验原理:8位通用寄存器R0-R3和8位PC的值是由16位D输入决定的,PC取D的高8位,R0-R3取第8位实验代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity e6 isport(clk,wt,rd,reset:in std_logic;RA,M:in std_logic_vector(1 downto 0);D: in std_logic_vector(15 downto 0);sel:buffer std_logic_vector(2 downto 0);led7:out std_logic_vector(7 downto 0));end;architecture one of e6 issignal R0,R1,R2,R3,PC,temp:std_logic_vector(7 downto 0);signal data:std_logic_vector(3 downto 0);signal sel_temp:std_logic_vector(2 downto 0);beginprocess(clk,reset,M)beginif clk'event and clk='0' thenif reset='0' then PC<="00000000";else case M iswhen "00"=>PC<=D(15 downto 8);when "01"=>PC<=PC+1;when "10"=>PC<=PC-1;when others=>NULL;end case;end if; end if;end process;process(RA,wt,rd)begincase RA iswhen"00"=>if wt='0'and rd='1' then R0<=D(7 downto 0);else if wt='1' and rd='0' then temp<=R0;end if; end if;when"01"=>if wt='0'and rd='1' then R1<=D(7 downto 0);else if wt='1' and rd='0' then temp<=R1;end if; end if;when"10"=>if wt='0'and rd='1' then R2<=D(7 downto 0);else if wt='1' and rd='0' then temp<=R2;end if; end if;when"11"=>if wt='0'and rd='1' then R3<=D(7 downto 0);else if wt='1' and rd='0' then temp<=R3;end if; end if;end case;end process;process(clk)beginif clk'event and clk='1' thensel_temp<=sel_temp+1;if sel_temp>="011" then sel_temp<="000";end if;sel<=sel_temp;case sel_temp iswhen "000"=>data<=temp(7 downto 4);when "001"=>data<=temp(3 downto 0);when "010"=>data<=PC(7 downto 4);when "011"=>data<=PC(3 downto 0);when others=>NULL;end case;end if;end process;process(data)begincase data isWHEN "0000"=> led7<="00111111";--0WHEN "0001"=> led7<="00000110";--1WHEN "0010"=> led7<="01011011";--2WHEN "0011"=> led7<="01001111";--3WHEN "0100"=> led7<="01100110";--4WHEN "0101"=> led7<="01101101";--5WHEN "0110"=> led7<="01111101";--6WHEN "0111"=> led7<="00000111";--7WHEN "1000"=> led7<="01111111";--8WHEN "1001"=> led7<="01101111";--9WHEN "1010"=> led7<="01110111";--10WHEN "1011"=> led7<="01111100";--11WHEN "1100"=> led7<="00111001";--12WHEN "1101"=> led7<="01011110";--13WHEN "1110"=> led7<="01111001";--14WHEN "1111"=> led7<="01110001";--15WHEN OTHERS =>NULL;end case;end process;end;引脚锁定:D0-D3------------k1k2k3k4 D4-D7-------s1s2s3s4D8-D11------------k7k8k9k10 D12-D15-------s7s8s9s10Clk-------a14 RA0-Ra1----------k5k6 M0-M1--------k11k12Wr------s5 rd------s6 reset------s12sel0-sel2和led0-led7(a-dp)参照8位动态显示管实验结果:当D=F8F7时,R0/R1/R2/R3=F7,PC=F8,注意:当要更改输入D值,要先将数值写入寄存器,再读出,否则数码管将不会显示新的数值。

西南交通大学计算机组成原理课程设计报告材料

《计算机组成实验 C》课程设计适用专业:电子信息类专业专业:软件工程班级:软件一班学号:姓名:某某某指导教师:陈红梅实验学期:2014-2015 第 1 学期西南交通大学信息科学与技术学院目录简化计算机系统的设计 (2)一、实验目的 (2)二.、实验内容 (2)三.、预习要求 (2)四、实验报告 (2)1. BLOCK图 (3)2. 程序设计(纸质的版本我用手抄) (4)3. 仿真波形图 (11)4、仿真中遇到的问题: (14)五、实验感想 (15)简化计算机系统的设计一、实验目的通过学习简单的指令系统及其各指令的操作流程,用VHDL 语言实现简单的处理器模块,并通过调用存储器模块,将处理器模块和存储器模块连接形成简化的计算机系统。

二.、实验内容1. 用VHDL语言实现简单的处理器模块。

2. 调用存储器模块设计64×8的存储器模块。

3. 将简单的处理器模块和存储器模块连接形成简单的计算机系统。

4. 将指令序列存入存储器,然后分析指令执行流程。

三.、预习要求1、学习简单指令集。

2、学习各指令的操作流程。

四、实验报告1. BLOCK图2. 程序设计(纸质的版本我用手抄)CPU的设计:LIBRARY ieee;USE ieee.std_logic_1164.ALL;PACKAGE mypack ISCONSTANT idle : std_logic_vector(3 DOWNTO 0) :="0000";CONSTANT load : std_logic_vector(3 DOWNTO 0) :="0001";CONSTANT move : std_logic_vector(3 DOWNTO 0) :="0010";CONSTANT addx : std_logic_vector(3 DOWNTO 0) :="0011";CONSTANT subp : std_logic_vector(3 DOWNTO 0) :="0100";CONSTANT andp : std_logic_vector(3 DOWNTO 0) :="0101";CONSTANT orp : std_logic_vector(3 DOWNTO 0) :="0110";CONSTANT xorp : std_logic_vector(3 DOWNTO 0) :="0111";CONSTANT shrp : std_logic_vector(3 DOWNTO 0) :="1000";CONSTANT shlp : std_logic_vector(3 DOWNTO 0) :="1001";CONSTANT swap : std_logic_vector(3 DOWNTO 0) :="1010";CONSTANT jmp : std_logic_vector(3 DOWNTO 0) :="1011";CONSTANT jz : std_logic_vector(3 DOWNTO 0) :="1100";CONSTANT read : std_logic_vector(3 DOWNTO 0) :="1101";CONSTANT write : std_logic_vector(3 DOWNTO 0) :="1110";CONSTANT stop : std_logic_vector(3 DOWNTO 0) :="1111";END mypack;LIBRARY ieee;USE ieee.std_logic_1164.ALL;USE ieee.std_logic_unsigned.ALL;USE WORK.mypack.ALL;------------------------cpu实体声明--------------------------------- ENTITY cpu ISPORT(reset : IN std_logic; --清零信号低有效clock : IN std_logic; --时钟信号Write_Read: OUT std_logic; --读写信号,'1'为写 M_address: OUT std_logic_vector(11 DOWNTO 0); --地址线M_data_in: IN std_logic_vector(7 DOWNTO 0); --数据输入线M_data_out: OUT std_logic_vector(7 DOWNTO 0); --数据输出线 overflow: OUT std_logic); --溢出标志END cpu;------------------------cpuRTL级行为描述-------------------------------- ARCHITECTURE RTL of cpu ISSIGNAL IR: std_logic_vector(15 DOWNTO 0); --指令寄存器 SIGNAL MDR: std_logic_vector(7 DOWNTO 0); --数据寄存器 SIGNAL MAR: std_logic_vector(11 DOWNTO 0); --地址寄存器 SIGNAL status: integer RANGE 0 TO 6; --状态寄存器BEGINstatus_change: PROCESS(reset, clock, status )BEGINIF reset = '0' THEN status <= 0 ;ELSIF clock'EVENT AND clock = '0' THENCASE status ISWHEN 0 =>status <= 1;WHEN 1 =>IF IR(15 DOWNTO 12) = Stop THENstatus <= 1;ELSEstatus <= 2;END IF;WHEN 2 =>CASE IR(15 DOWNTO 12) ISWHEN Read|Write|Jmp|Jz|Swap =>status <= 3;WHEN OTHERS =>status <= 0;END CASE;WHEN 3 =>IF IR(15 DOWNTO 12)= Swap THENstatus <= 0;ELSEstatus <= 4;END IF;WHEN 4 =>status <= 5;WHEN 5 =>CASE IR(15 DOWNTO 12) ISWHEN Read|Write =>status <= 6;WHEN OTHERS =>status <= 0;END CASE;WHEN OTHERS =>status <= 0;END CASE;ELSENULL;END IF;END PROCESS status_change;seq: PROCESS(reset,clock)VARIABLE PC:std_logic_vector(11 DOWNTO 0); --程序计数器 VARIABLE R0,R1,R2,R3: std_logic_vector(7 DOWNTO 0); --通用寄存器VARIABLE A: std_logic_vector(7 DOWNTO 0); --临时寄存器VARIABLE temp: std_logic_vector(8 DOWNTO 0); --临时变量BEGINIF(reset='0') THEN -- 清零IR <= (OTHERS=>'0');PC := (OTHERS=>'0');R0 := (OTHERS=>'0');R1 := (OTHERS=>'0');R2 := (OTHERS=>'0');R3 := (OTHERS=>'0');A := (OTHERS=>'0');MAR <= (OTHERS=>'0');MDR <= (OTHERS=>'0');ELSIF(clock'event AND clock='1') THENoverflow <= '0';CASE status ISWHEN 0=> --状态0IR <= M_data_in & "00000000"; --取指令PC := PC+1; --程序计数器加1WHEN 1=> --状态1IF (IR(15 DOWNTO 12) /= stop) THENMAR <= PC;END IF;CASE IR(15 DOWNTO 12) ISWHEN load =>R0:= "0000" & IR(11 DOWNTO 8);WHEN shlp|shrp =>CASE IR(11 DOWNTO 10) IS -- Rx to AWHEN "00"=> A:= R0;WHEN "01"=> A:= R1;WHEN "10"=> A:= R2;WHEN OTHERS => A:= R3;END CASE;WHEN Move|addx|subp|andp|orp|xorp|Swap=> CASE IR(9 DOWNTO 8) IS -- Ry to AWHEN "00"=> A:=R0;WHEN "01"=> A:=R1;WHEN "10"=> A:=R2;WHEN OTHERS=> A:=R3;END CASE;WHEN OTHERS => NULL;END CASE;WHEN 2=> --状态2CASE IR(15 DOWNTO 12) ISWHEN addx => -- Rx:= Rx + A;CASE IR(11 DOWNTO 10) ISWHEN "00"=>temp := (R0(7) & R0(7 DOWNTO 0)) + (A(7) & A(7 DOWNTO 0));R0:=temp(7 DOWNTO 0);overflow <= temp(8) XOR temp(7);WHEN "01"=>temp :=(R1(7) & R1(7 DOWNTO 0)) + (A(7) & A(7 DOWNTO 0));R1:=temp(7 DOWNTO 0);overflow <= temp(8) XOR temp(7);WHEN "10"=>temp :=(R2(7) & R2(7 DOWNTO 0)) + (A(7) & A(7 DOWNTO 0));R2:=temp(7 DOWNTO 0);overflow <= temp(8) XOR temp(7);WHEN OTHERS=>temp :=(R3(7) & R3(7 DOWNTO 0)) + (A(7) & A(7 DOWNTO 0));R3:=temp(7 DOWNTO 0);overflow <= temp(8) XOR temp(7);END CASE;WHEN subp => -- Rx:= Rx - A;CASE IR(11 DOWNTO 10) ISWHEN "00"=>temp :=(R0(7) & R0(7 DOWNTO 0)) + NOT(A(7) & A(7 DOWNTO 0)) + 1;R0:=temp(7 DOWNTO 0);overflow <= temp(8) XOR temp(7);WHEN "01"=>temp :=(R1(7) & R1(7 DOWNTO 0)) + NOT(A(7) & A(7 DOWNTO 0)) + 1;R1:=temp(7 DOWNTO 0);overflow <= temp(8) XOR temp(7);WHEN "10"=>temp :=(R2(7) & R2(7 DOWNTO 0)) + NOT(A(7) & A(7 DOWNTO 0)) + 1;R2:=temp(7 DOWNTO 0);overflow <= temp(8) xor temp(7);WHEN OTHERS=>temp :=(R3(7) & R3(7 DOWNTO 0)) + NOT(A(7) & A(7 DOWNTO 0)) + 1;R3:=temp(7 DOWNTO 0);overflow <= temp(8) XOR temp(7);END CASE;WHEN move =>CASE IR(11 DOWNTO 10) ISWHEN "00"=> R0:= A;WHEN "01"=> R1:= A;WHEN "10"=> R2:= A;WHEN OTHERS=> R3:= A;END CASE;WHEN shrp =>CASE IR(11 DOWNTO 10) ISWHEN "00"=> R0:= '0' & A( 7 DOWNTO 1 );WHEN "01"=> R1:= '0' & A( 7 DOWNTO 1 );WHEN "10"=> R2:= '0' & A( 7 DOWNTO 1 );WHEN OTHERS=> R3:= '0' & A( 7 DOWNTO 1 );END CASE;WHEN shlp =>CASE IR(11 DOWNTO 10) ISWHEN "00"=> R0:= A( 6 DOWNTO 0 ) & '0';WHEN "01"=> R1:= A( 6 DOWNTO 0 ) & '0';WHEN "10"=> R2:= A( 6 DOWNTO 0 ) & '0';WHEN OTHERS=> R3:= A( 6 DOWNTO 0 ) & '0';END CASE;WHEN andp => --Rx:= Rx AND A; CASE IR(11 DOWNTO 10) ISWHEN "00"=> R0:=R0 AND A;WHEN "01"=> R1:=R1 AND A;WHEN "10"=> R2:=R2 AND A;WHEN OTHERS=> R3:=R3 AND A;END CASE;WHEN orp => --Rx:= Rx OR A;CASE IR(11 DOWNTO 10) ISWHEN "00"=> R0:=R0 OR A;WHEN "01"=> R1:=R1 OR A;WHEN "10"=> R2:=R2 OR A;WHEN OTHERS=> R3:=R3 OR A;END CASE;WHEN xorp => --Rx:= Rx XOR A; CASE IR(11 DOWNTO 10) ISWHEN "00"=> R0:=R0 XOR A;WHEN "01"=> R1:=R1 XOR A;WHEN "10"=> R2:=R2 XOR A;WHEN OTHERS=> R3:=R3 XOR A;END CASE;WHEN Swap => --Swap: Rx to Ry; CASE IR(11 DOWNTO 8) ISWHEN "0100"=> R0:=R1;WHEN "1000"=> R0:=R2;WHEN "1100"=> R0:=R3;WHEN "0001"=> R1:=R0;WHEN "1001"=> R1:=R2;WHEN "1101"=> R1:=R3;WHEN "0010"=> R2:=R0;WHEN "0110"=> R2:=R1;WHEN "1110"=> R2:=R3;WHEN "0111"=> R3:=R1;WHEN "1011"=> R3:=R2;WHEN "0011"=> R3:=R0;WHEN OTHERS=> NULL;END CASE;WHEN OTHERS => NULL;END CASE;WHEN 3=> --状态3CASE IR(15 DOWNTO 12) ISWHEN Swap=> -- Swap: A to RxCASE IR(11 DOWNTO 10) ISWHEN "00"=> R0:=A;WHEN "01"=> R1:=A;WHEN "10"=> R2:=A;WHEN OTHERS=> R3:=A;END CASE;WHEN jmp|Jz|Read|Write =>IR(7 DOWNTO 0)<= M_data_in; -- 取双字节指令的后半部分 PC := PC+1;WHEN OTHERS => NULL;END CASE;WHEN 4=> --状态4CASE IR(15 DOWNTO 12) ISWHEN jmp => -- 无条件转移指令PC := IR(11 DOWNTO 0);MAR <= IR(11 DOWNTO 0);WHEN Jz => -- 条件转移指令IF(R0="00000000") thenPC := IR(11 DOWNTO 0);MAR <= IR(11 DOWNTO 0);elseMAR <= PC;END IF;WHEN Read =>MAR <= IR(11 DOWNTO 0);WHEN Write =>MAR <= IR(11 DOWNTO 0);MDR <= R0;WHEN OTHERS => NULL;END CASE;WHEN 5 => --状态5MAR <= PC;WHEN 6 => --状态6CASE IR(15 DOWNTO 12) ISWHEN Read => R0 := M_data_in;WHEN OTHERS=> NULL;END CASE;END CASE;END IF;END process seq;comb: PROCESS (reset, status)BEGINIF (reset = '1' AND status = 5 AND IR(15 DOWNTO 12)= Write ) THEN Write_Read <= '1';ELSEWrite_Read <= '0';END IF;END PROCESS comb;M_address <= MAR;M_data_out <= MDR;END RTL;3. 仿真波形图3.1总体的仿真波形图1、我们可以看到CPU有6种工作模式,并且在不同的工作模式下实现了不同的功能。

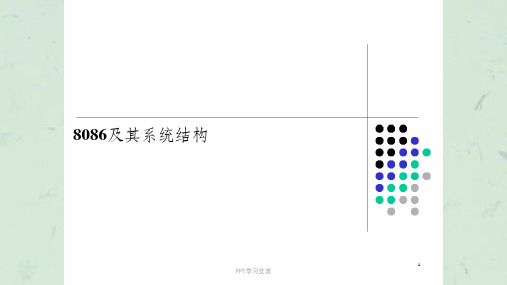

西南交大,微机原理,教师第2章课件

PPT学习交流

9

9

地址发生器

组成:地址加法器、指令指针IP和段寄存器。 设立地址加法器的目的:8086CPU地址总线有20 位,而内部地址寄存器都是16位,需要加法器形成 20位地址。 工作原理:段寄存器内容×16+偏移地址(IP或指 令中的操作数地址给出)。

器的状态

PPT学习交流

2

2

第一节:8086微处理器内部结构

PPT学习交流

3

3

指令和程序

机器指令

操作码 + 操作数

若干条指令构成程序

PPT学习交流

4

4

指令解释方式

微处理器解释一条指令的完整步骤可以归纳为如下两 个阶段:

取指:从内存中取出指令,明确指令规定的功能; 执行:分析指令要求实现的功能,读取所需要的操作 数,执行指令规定的操作,并保存执行结果。

SI

DI

AX 累加器 BX 基址寄存器 CX 计数寄存器 DX 数据寄存器

堆栈指针 基址指针 源变址寄存器 目的变址寄存器

通用寄存器

CS

代码段寄存器

DS ES

数据段寄存器 附加段寄存器

段寄存器

SS

堆栈段寄存器

IP F

指令指针 标志寄存器

专用寄存器

13

PPT学习交流

13

通用寄存器

(1 )数据寄存器: 用于存放8 位或16 位的二进制操作 数,这些操作数可以是参加操作的原始数据、运算得到 的中间结果,也可以是操作数的地址。大多数算术和逻 辑运算指令都可以使用这些寄存器。

PPT学习交流

10

10

计算机组成原理指令部件模块实验报告

五、实验总结

通过实验七和八明白了计算机运行过程的皮毛,用户给出一条指令,计算机转换为自己的语言, 并让程序计数器加 1 好执行下一条指令,这是宏观的,用户下的这条指令又分为一些微指令,由 微程序控制单元继续执行,指令有很多,这就要求计算机选择执行或不执行,执行哪一条,如何 执行,出错了怎么处理等等,关于计算机我们要学习的还很多,我们得先弄明白现有的计算机是 怎么工作的,才能更好的去维护和应用计算机,技术更高时我们要创造更先进的计算机。

指令部件模块实验的原理就是先给程序计数器 PC 一个值,进行下一条指令时观察 PC 值的变化, 实验八和实验七微程序控制单元的区别在于实验七是微观的,实验八是宏观上的,打个比方就是 实验八的重点是是我发出叫你跑的指令后我的状态,实验七的重点是我发出跑的指令后你要进行 的行为。 如图 7-8-1 所示, 2 片 74LS163 作为 8 位 PC 程序计数器的 8 位输入/输出公用端用 8 芯扁平线与 BUS 总线接口相连接。2 片 74LS163 组成了 PC 程序计数器,它有 LDPC、LOAD 信号,LDPC 是程序计数器 的端,LOAD 是装入数据,脉冲 T3 来控制 PC 指针的装载和加 1 操作。在“L”状态下,由 8 位置数 开关装入起始地址,当 LOAD=1、LDPC=1 时,按【单步】命令键,在 T3 上升沿把数据开关的内容装 入 PC。当 CBA=001、由表 7-1-1 知是 PC 送总线,LOAD=0、LDPC=1、LDAR=1 时,按【单步】命令键,

微地址灯 (001001) P(1)=1

注:【单步】键的功能是启动时序电路产生 T1~T4 四拍单周期脉冲 结果分析: 先由数据开关给 PC 置数为 00000000, 其它都关闭, 只令 SW-B=1, 表示其他部件送总线, 令 LOAD LOPC 都为 1 时,由图 7-8-1 是给 PC 中装入数据开关置的数,地址总线单元显示 00H,数已装入,这是 PC 值的写入; 关闭 SW-B, LOAD LOPC 都为 0, 令 CBA=001 是 PC 送总线, 此时数据总线显示 00000000, 这是 PC 值的读出; 在保持 PC 值读出的开关状态下,置 LDAR=1、LDPC=1,按【单步】命令键,在 T3 节拍把当前数据 总线的内容(即 PC)打入地址锁存器,地址总线单元的显示器显示 00H,在 T3 节拍的上升沿 PC 计数器加 1,PC 单元的显示器显示 01H;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验8 指令存储器与取指令部件的设计

西南交大计算机组成原理实验(代码)

实验要求:建立256*16的指令存储器ROM,将它关联到元件IPM-Rom,有PC 值决定存储器地址,PC有清零,置数,自动加一,自动减一功能,并将指令输出到数码管显示。

实验原理:建立内存文件,256代表内存地址是8位,16代表内存数据是16位实验代码:

PC:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity PC is

port(clk,reset,load,add:in std_logic;

inn:in std_logic_vector(7 downto 0);

output:buffer std_logic_vector(7 downto 0));

end;

architecture one of PC is

begin

process(clk)

begin

--wt<=load&add;

if clk'event and clk='1' then

if reset='1' then output<="00000000";

else if load='1' then output<=inn;

else if add='1' then output<=output+1;

else output<=output-1;

end if;

end if;

end if;

end if;

end process;

end;

FRQ:用于分频

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity FRQ is

port(clk_in:in std_logic;

clk_out:out std_logic);

end;

architecture one of FRQ is

signal temp:std_logic_vector(2 downto 0);

begin

process(clk_in)

begin

if clk_in'event and clk_in='1' then

temp<=temp+1;

clk_out<=temp(2);

end if;

end process;

end;

IR:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity IR is

port(clk1,clk2,aadd:in std_logic;

input:in std_logic_vector(15 downto 0);

sel:buffer std_logic_vector(2 downto 0);

outadd:out std_logic;

led7:out std_logic_vector(7 downto 0));

end;

architecture one of IR is

signal sel_temp:std_logic_vector(2 downto 0);

signal data:std_logic_vector(3 downto 0);

begin

process(clk1,clk2)

begin

if clk1'event and clk1='1' then

if aadd='1' then outadd<='1';

else outadd<='0'; end if;

end if;

if clk2'event and clk2='1' then

sel_temp<=sel_temp+1;

if sel_temp>="011" then sel_temp<="000"; end if;

sel<=sel_temp;

case sel_temp is

when"000"=>data<=input(15 downto 12);

when"001"=>data<=input(11 downto 8);

when"010"=>data<=input(7 downto 4);

when"011"=>data<=input(3 downto 0);

when others=>null;

end case;

end if;

case data is

WHEN "0000"=> led7<="00111111";--0

WHEN "0001"=> led7<="00000110";--1

WHEN "0010"=> led7<="01011011";--2

WHEN "0011"=> led7<="01001111";--3

WHEN "0100"=> led7<="01100110";--4

WHEN "0101"=> led7<="01101101";--5

WHEN "0110"=> led7<="01111101";--6

WHEN "0111"=> led7<="00000111";--7

WHEN "1000"=> led7<="01111111";--8

WHEN "1001"=> led7<="01101111";--9

WHEN "1010"=> led7<="01110111";--10

WHEN "1011"=> led7<="01111100";--11

WHEN "1100"=> led7<="00111001";--12

WHEN "1101"=> led7<="01011110";--13

WHEN "1110"=> led7<="01111001";--14

WHEN "1111"=> led7<="01110001";--15

WHEN OTHERS =>NULL;

end case;

end process;

end;

原理图:

内存文件:

引脚锁定:。