实验五_存储器设计

试验五存储器连接6116的使用

实验五存储器连接(6116的使用)【实验名称】存储器连接(6116的使用)。

【实验目的】掌握存储器译码及读写的方法。

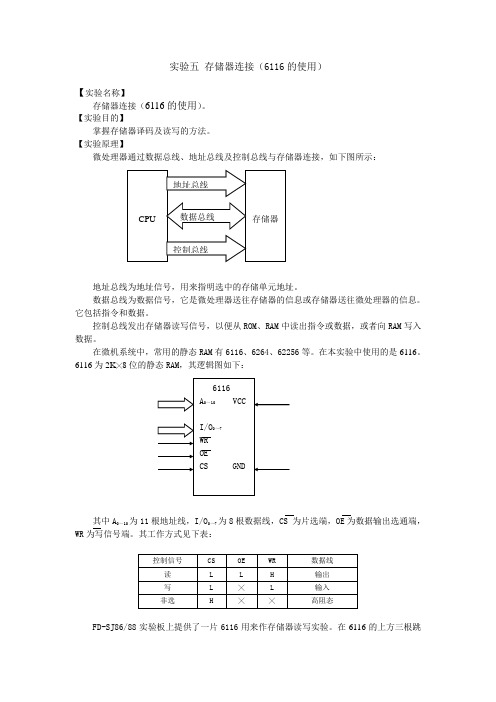

【实验原理】微处理器通过数据总线、地址总线及控制总线与存储器连接,如下图所示:地址总线为地址信号,用来指明选中的存储单元地址。

数据总线为数据信号,它是微处理器送往存储器的信息或存储器送往微处理器的信息。

它包括指令和数据。

控制总线发出存储器读写信号,以便从ROM、RAM中读出指令或数据,或者向RAM写入数据。

在微机系统中,常用的静态RAM有6116、6264、62256等。

在本实验中使用的是6116。

6116为2K╳8位的静态RAM,其逻辑图如下:其中A0~10为11根地址线,I/O0~7为8根数据线,CS 为片选端,OE为数据输出选通端,WR为写信号端。

其工作方式见下表:FD-SJ86/88实验板上提供了一片6116用来作存储器读写实验。

在6116的上方三根跳线J57、J58、J59分别用来设置6116的片选端、读信号、写信号的连接状态。

当以短路块分别将J57、J58、J59上面两根针短路时,则6116片选端连接由U39产生的译码信号,其译码范围为0A0000H~0A07FFH,因6116为2K存储器,所以地址0A0000H~0A07FFH和0A0800H~0A0FFFH重叠。

6116的读写信号则分别接到系统总线上的存储器读写信号。

其数据通过74LS245(U38)接到系统的数据总线上。

【实验内容】在FD-SJ86/88实验板上的6116芯片内写入一些数据,然后读出显示在屏幕上以验证正确与否。

【实验连线】① 6264的地址线J8(A0~A10)接总线上的地址线A0~A10。

② J57、J58、J59的下面的两个脚以短路块连接。

【实验程序】DATA SEGMENTMESSAGE DB 'PLEASE ENTER A KEY TO SHOW THE CONTENTS',0DH,0AH,'$'DATA ENDSSTACK SEGMENT STACKSTA DW 50 DUP(?)TOP EQU LENGTH STASTACK ENDSCODE SEGMENTASSUME CS:CODE,DS:DATA,SS:STACK,ES:DATASTART: MOV AX,DATAMOV DS,AXMOV AX,STACKMOV SS,AXMOV SP,TOPMOV AX,0A000HMOV ES,AXMOV BX,0000HMOV CX,26MOV DL,40HWRITE: INC DLMOV ES:[BX],DLINC BXCMP DL,5AHJNZ SS1MOV DL,40HSS1: LOOP WRITEMOV DX,OFFSET MESSAGEMOV AH,9INT 21HMOV AH,01HINT 21HMOV AX,0A000HMOV ES,AXMOV BX,0000HMOV CX,26READ: MOV DL,ES:[BX]MOV AH,02HINT 21HINC BXLOOP READMOV AH,4CHINT 21HCODE ENDSEND START【思考题】将字符‘0’~‘9’写入存储器,再将其读出,应如何修改程序?。

计算机组成原理实验_存储器部件教学实验

实验题目存储器部件教学实验一、实验目的:1. 熟悉ROM芯片和RAM芯片在功能和使用方法等方面的相同和差异之处。

学习用编程器设备向EEPROM芯片内写入一批数据的过程和方法。

2. 理解并熟悉通过字、位扩展技术实现扩展存储器系统容量的方案。

3. 了解静态存储器系统使用的各种控制信号之间正常的时序关系。

4. 了解如何通过读、写存储顺的指令实现对58C65 ROM芯片的读、写操作。

加深理解存储器部件在计算机整机系统中的作用。

二、实验设备与器材:TEC-XP+教学实验系统和仿真终端软件PCEC。

三、实验说明和原理:1、内存储器原理内存储器是计算机中存放正在运行中的程序和相关数据的部件。

在教学计算机存储器部件设计中,出于简化和容易实现的目的,选用静态存储器芯片实现内存储器的存储体,包括唯读存储区和随读写存储区两部分,ROM存储区选用4片长度8位、容易8KB的58C65芯片实现,RAM存储区选用2片长度8位、容量2KB的6116芯片实现,每2个8位的芯片合成一组用于组成16位长度的内存字,6个芯片被分成3组,其地址空间分配关系是:0-1777h用于第一组ROM,固化监控程序,2000-2777h用于RAM,保存用户程序和用户数据,其高端的一些单元作监控程序的数据区,第二组ROM的地址范围可以由用户选择,主要用于完成扩展内存容量的教学实验。

地址总线的低13位送到ROM芯片的地址线引脚,用于选择芯片内的一个存储字。

用于实现存储字的高位字节的3个芯片的数据线引脚、实现低位字节的3个芯片的数据线引脚分别连接在一起接到数据总线的高、低位字节,是实现存储器数据读写的信息通路。

数据总线要通过一个双向三态门电路与CPU一侧的内部总线IB 相连接,已完成存储器、接口电路和CPU之间的数据通讯。

2、扩展教学机的存储空间四、实验内容:1) 要完成存储器容量扩展的教学实验,需为扩展存储器选择一个地址,并注意读写和OE等控制信号的正确状态。

《计算机组成原理》实验

实验一、运算实验算术逻辑一、实验目的1、掌握简单运算器的数据传送通路2、验证运算功能发生器(74LS181)的组合功能二、实验设备CCT-IV计算机组成原理教学实验系统一台,排线若干。

三、实验原理实验中的运算器由两片74LS181构成。

运算器的输出经过一个三态门74LS245和数据总线相连,运算器的两个数据输入端,分别由二个锁存器74LS273锁存,锁存器的输入端和数据总线相连,数据输入输出都通过总线完成;数据显示灯(“BUS UNIT”)与数据总线相连,用来显示数据总线内容。

实验中的数据输入由数据开关(“INPUT DEVICE”)给出,并经过三态门74LS245和数据总线相连,数据输出可以经总线输出至七段数码管(“OUTPUT DEVICE”)显示S3S2S1S0MLDDR1 T4 LDDR2SW-B图1-2运算器数据通路图1-2中T4为脉冲信号,其它均为电平信号。

在实验中,只需将“W/R UNIT”的T4接至“STATE UNIT”的微动开关KK2的输出端,按动微动开关,即可获得实验所需的单脉冲,而S3、S2、S1、S0、Cn、M、LDDR、ALU-B、SW-B各电平控制信号用“SWITCH UNIT”中的二进制数据开关来模拟,其中Cn、ALU-B、SW-B为低电平有效,LDDR1,LDDR2为高电平有效进位控制运算的实验,是在前面实验的基础上增加进位控制部分(如1-3图所示),其中181的进位进入一个74锁存器,其写入是由T4的AR信号控制,T4是脉冲信号,实验时将T4连至“STATE UNIT”的微动开关KK2上。

AR是电平控制信号,可用于实现带进位控制实验,而T4脉冲是将本次运算的进位结果锁存到进位锁存器中。

四、实验内容1、按图1-1实验接线图连接线路,仔细查线无误后,接通电源。

2、用二进制数码开关分别向DR1和DR2寄存器臵数01100101,10100111。

①打开数据输入三态门SW-B=0 关闭运算器输出三态门ALU-B=1②向寄存器DR1传送数据,数据开关臵01100101,LDDR1=1,LDDR2=0,按下KK2,产生T4信号③向寄存器DR2传送数据,数据开关臵10100111,LDDR1=0,LDDR2=1,按下KK2,产生T4信号④关闭数据输入三态门SW-B=1,打开运算器输出三态门ALU-B=0⑤当臵S3、S2、S1、S0、M为11111时,总线指示灯DR1中的数,而臵成10101时总线指示DR2中的数。

杭电计组实验5-存储器设计实验

5’b000007 32’b0000000732’b0000000732'h0055_752332'h0055_7523

(2)答:这些单元的数据已经被改写了。读出数据与写入数据一致。

RAM_B uut (

.clka(clka),

.wea(wea),

.addra(addra),

.dina(dina),

.douta(douta)

);

initial begin

// Initialize Inputs

clka = 0;

wea = 0;

addra = 0;

dina = 0;

// Wait 100 ns for global reset to finish

NET "Clk" LOC = C9;

NET "LED[4]" LOC = M11;

NET "LED[3]" LOC = V15;

NET "LED[2]" LOC = U15;

NET "LED[1]" LOC = V16;

NET "LED[0]" LOC = U16;

NET "Mem_Addr[7]" LOC = U8;

output reg [7:0]LED;

wire [31:0]M_R_Data;//存在存储器里的32位读出数据

reg [31:0]M_W_Data;//寄存在暂存器的32位写入数据

RAM_B test_ram (

存储器读写实验

实验三 8255A 并 行 口 实 验

一、实验目的 1、掌握8255A和微机接口方法。 2、掌握8255A的工作方式和编程原理。 二、实验原理 1、 如实验原理图,PC口8位接8个开关K1~ K8,PB口8位接8个发 光二极管,从PC口读入8位开关量送PB口显示。拨动K1~ K8,PB口 上接的8个发光二极管L1~ L8对应显示K1~ K8的状态。

实验七 A/D转换实验

一、实验目的 1、 加深理解逐次逼近法模数转换器的特征和工作原理。 2、掌握ADC0809的接口方法以及A/D输入程序的设计和调试方法。 二、实验原理 1、本实验采用 ADC0809 做 A/D 转换实验。ADC0809 是一种8路模拟输入 、8位数字输出的逐次逼近法A/D器件,转换时间约100us,转换精度为 ±1/512,适用于多路数据采集系统。ADC0809片内有三态输出的数据锁 存器,故可以与8088微机总线直接接口。 图中ADC0809的CLK信号接CLK=2.385MHZ,基准电压Vref(+)接Vcc。一 般在实际应用系统中应该接精确+5V,以提高转换精度,ADC0809片选 信号0809CS和/IOW、/IOR经逻辑组合后,去控制ADC0809的ALE、 START、ENABLE信号。ADC0809的转换结束信号EOC未接, 如果以中 断方式实现数据采集,需将EOC信号线接至中断控制器8259A的中断源 输入通道。本实验以延时方式等待A/D转换结束,ADC0809的通道号选 择线ADD-A、ADD-B、ADD-C 接系统数据线的低3位,因此 ADC0809的8个通道值地址分别为00H、01H、02H、03H、04H、05H 、 06H、07H。

存贮器读写实验

Hale Waihona Puke 8088系统硬件安装

• 1、接交流电源线。 • 2、将RS-232通信电缆线的9 芯 D 型插座一头插入实验

系统的9 芯 D 型插座J2上,另一头接入主机 COM1~ COM4 的任一插座上。 选择 COM1、COM2、COM3 或 COM4 的原则是:该通信口必须能正常工作, 且 与 通信电缆提供的插头匹配。

RAM(2000H~23FFH)写数据55AAH 3.修改程序,用循环指令将2000H~23FFH的内容传送到

3000H~33FFH中 4.提交实验报告

DVCC-8086JHN实验系统整体原理框图

以Inte18088CPU 为核心部件,并 以最小方式工作。

由8284芯片给 CPU提供时钟

和复位信号

通过总线收发器和地址锁存 器对系统中的数据信息和地

址信息进行缓冲或锁存

通过总线插座将信号引出, 为各实验提供必要的信号

27512EPROM 里面放的是系

DVCC-8086JHN 通用微机原理及接口实验系统

DVCC-8086JHN 性能特点

• 1、用8088CPU 为主 CPU,并以最小工作方式构成系统 。 • 2、 系统以二片 62256 静态 RAM 构成系统的 64K 基本内存, 地

址范围为 00000H~0FFFFH。 另配一片 32K EPROM 存放系统程 序和实验程序。 • 3、自带键盘显示器,能单机独立运行,为实验程序的调试带 来方 便。 • 4、备有通用外围电路,包括逻辑电平开关电路、发光二极管显示 电路、 时钟电路、单脉冲 发生电路等。 • 5、 提供各种微机常用 I/O 接口芯片:包括定时/计数器接口芯片 (8253A), 并行接口芯片 (8255A),A/D 转换芯片(0809),D/A 转换 芯片( 0832) , 中断控制器接口芯片(8259A),键盘显 示接口芯片 (8279A),串行通信接口芯片(8251A)等。 • 6、配备中文 WINDOWS 9x/2000/xp界面调试软件及实验演示软件 。 可以单步、断点、连续等方式调试运行各实验程序 。

储存器实验报告

储存器实验报告储存器实验报告一、引言储存器是计算机中重要的组成部分,它用于存储和读取数据。

在计算机科学领域,储存器的设计和性能对计算机的运行速度和效率有着重要的影响。

本实验旨在通过设计和实现一个简单的储存器,来深入了解储存器的工作原理和性能指标。

二、实验目的1. 了解储存器的基本概念和分类;2. 掌握储存器的存储原理和读写操作;3. 分析和评估储存器的性能指标。

三、实验过程1. 储存器的分类储存器按照存储介质的不同可以分为随机存储器(RAM)和只读存储器(ROM)。

RAM是一种易失性存储器,它可以随机读写数据。

ROM则是一种非易失性存储器,主要用于存储固定的程序和数据。

2. 储存器的存储原理储存器的存储原理是通过电子元件的状态来表示数据的存储状态。

在RAM中,每个存储单元由一个电容和一个晶体管组成。

当电容充电时表示存储单元存储的是1,当电容放电时表示存储单元存储的是0。

在ROM中,存储单元由一组可编程的开关组成,每个开关的状态决定了存储单元存储的数据。

3. 储存器的读写操作储存器的读操作是通过将地址信号传递给储存器来选择要读取的存储单元,然后将存储单元的数据输出。

储存器的写操作是通过将地址信号传递给储存器来选择要写入的存储单元,然后将要写入的数据输入。

四、实验结果在实验中,我们设计并实现了一个8位的RAM储存器。

通过对储存器进行读写操作,我们成功地将数据存储到储存器中,并成功地从储存器中读取数据。

实验结果表明,储存器的读写操作是可靠和有效的。

五、实验分析1. 储存器的性能指标储存器的性能指标包括存储容量、存取时间和存储器的可靠性。

存储容量是指储存器可以存储的数据量,通常以位或字节为单位。

存取时间是指从发出读写指令到数据可以被读取或写入的时间间隔。

存储器的可靠性是指储存器的故障率和故障恢复能力。

2. 储存器的应用储存器广泛应用于计算机、手机、平板电脑等电子设备中。

在计算机中,储存器用于存储程序和数据,是计算机的核心组件之一。

寄存器实验实验报告

寄存器实验实验报告一. 引言寄存器是计算机中重要的数据存储器件之一,用于存储和传输数据。

通过对寄存器进行实验,我们可以更好地理解寄存器的工作原理和应用。

本实验旨在通过设计和测试不同类型的寄存器,深入掌握寄存器的各种功能和操作。

二. 实验设计本实验设计了两个寄存器的实验,分别为移位寄存器和计数器寄存器。

1. 移位寄存器实验移位寄存器是一种特殊的串行寄存器,它能够实现对数据位的移位操作。

本实验设计了一个4位的移位寄存器,分别使用D触发器和JK触发器实现。

实验步骤如下:1) 首先,根据设计要求将4个D或JK触发器连接成移位寄存器电路。

2) 确定输入和输出端口,将输入数据连接到移位寄存器的输入端口。

3) 设计测试用例,输入测试数据并观察输出结果。

4) 分析实验结果,比较不同触发器类型的移位寄存器的性能差异。

2. 计数器寄存器实验计数器寄存器是一种能够实现计数功能的寄存器。

本实验设计了一个二进制计数器,使用T触发器实现。

实验步骤如下:1) 根据设计要求将多个T触发器连接成二进制计数器电路。

2) 设计测试用例,输入计数开始值,并观察输出结果。

3) 测试计数的溢出和循环功能,观察计数器的行为。

4) 分析实验结果,比较不同计数器位数的性能差异。

三. 实验结果与分析在实验过程中,我们完成了移位寄存器和计数器寄存器的设计和测试。

通过观察实验结果,可以得出以下结论:1. 移位寄存器实验中,无论是使用D触发器还是JK触发器,移位寄存器都能够正确地实现数据位的移位操作。

而使用JK触发器的移位寄存器在性能上更加优越,能够实现更复杂的数据操作。

2. 计数器寄存器实验中,二进制计数器能够准确地实现计数功能。

通过设计不同位数的计数器,我们发现位数越多,计数范围越大。

综上所述,寄存器是计算机中重要的存储器件,通过实验我们深入了解了寄存器的工作原理和应用。

移位寄存器和计数器寄存器都具有广泛的应用领域,在数字电路设计和计算机系统中起到了重要作用。

51单片机实验-实验五 存储器扩展实验

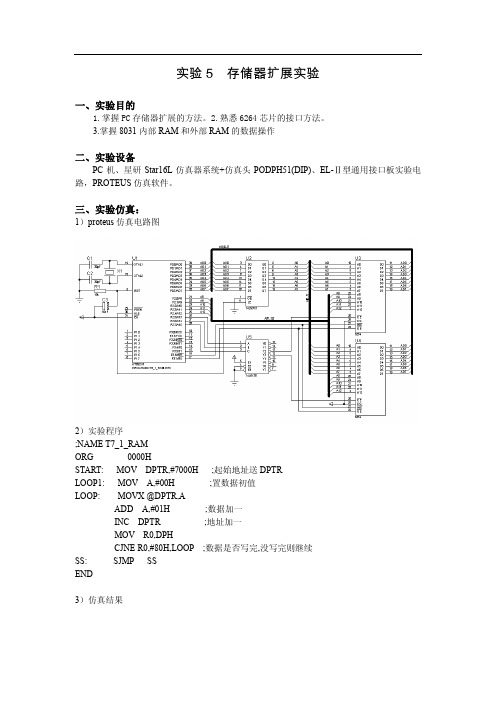

实验5 存储器扩展实验一、实验目的1.掌握PC存储器扩展的方法。

2.熟悉6264芯片的接口方法。

3.掌握8031内部RAM和外部RAM的数据操作二、实验设备PC机、星研Star16L仿真器系统+仿真头PODPH51(DIP)、EL-Ⅱ型通用接口板实验电路,PROTEUS仿真软件。

三、实验仿真:1)proteus仿真电路图2)实验程序;NAME T7_1_RAMORG 0000HSTART: MOV DPTR,#7000H ;起始地址送DPTRLOOP1: MOV A,#00H ;置数据初值LOOP: MOVX @DPTR,AADD A,#01H ;数据加一INC DPTR ;地址加一MOV R0,DPHCJNE R0,#80H,LOOP ;数据是否写完,没写完则继续SS: SJMP SSEND3)仿真结果运行上面的程序,由于设定起始地址为7000,而P2.0~P2.4分别作为地址线A8~A12,P2.5~P2.7分别接74ls138的ABC三个口,且38译码器的Y2接6264-U3的片选口CE,与接6264-U4的片选口CE,所以此时CBA为011,则选择的存储器为U4,将00~FF这组数据分别送到U4的以7000H为起始地址的单元中,并循环放置(即proteus仿真结果中的1000H 地址);若将程序中的起始地址改为5000H,检验是否写完数据的数值#80H改为#60H,则此时CBA为010,此时选择的是U3存储器,结果与选择U4时一样。

证明这些地址都可用,如果不可用,则在写入数据时所有地址单元中的数值保持为FF。

四、实验台操作1)接线实验台已将内部线路接好,可用地址范围为4000~7FFFH2)实验结果实验结果基本与仿真结果一致。

片上存储器实验——SRAM 读写实验

实验五片上存储器实验——SRAM 读写实验实验目的:1. 熟悉SEED-DEC2812 的实验环境;2. 解SRAM 存储空间的分配。

实验内容:1. DSP 的初始化;2. DARAM 上写数据;3. 检查并读取SRAM 上的数据。

实验背景知识:TMS320F2812 片内包括5 段SARAM,M0、M1、L0、L1 和H0 段。

所有基于C28x 内核的数字信号处理器都包含两个单周期快速访问的存储器,M0和M1。

每个空间的长度都是1K 字,其中M0 映射到0x000000~0x0003F 空间,M1 映射到0x000400~0x0007F 空间。

在复位状态下,堆栈指针指向M1 模块的起始位置。

MO 和M1 既可以执行程序也可以存放数据变量。

其中,M0 和M1 段大小都为1K×16位的SARAM,当复位后,堆栈指针指向M1 段的开头。

M0 和M1 段都可以映射到程序区和数据区。

L0、L1 和H0 段大小总和为16K×16 位的SARAM,分为 3 块(4K+4K+8K),分别是L0(4K),L1(4K),H0(8K)。

每块可以单独使用,都可以映射到程序区和数据区。

SRAM 实验,包含文件:1. sram.c:这是实验的主程序,包含了系统初始化,SRAM 读写程序等。

2. DSP28_GlobalVariableDefs.c:定义各模块的全局变量。

3. DSP28_SysCtrl.c:系统初始化函数。

4. DSP28_DefaultIsr.c:系统中断向量表初始化5. 2812.cmd: 声明了系统的存储器配置与程序各段的连接关系。

6. 2812.gel:系统初始化程序流程图1. 将DSP 仿真器与计算机连接好;2. 将DSP 仿真器的JTAG 插头与SEED-DEC2812 单元的J1 相连接;3. 打开SEED-DTK2812 的电源。

观察SEED-DEC-MBoard 单元的+5V,+3.3V,+15V,-15V 的电源指示灯以及SEED_DEC2812 的电源指示灯D2 是否均亮;若有不亮的,请断开电源,检查电源。

微机原理:串操作存储器访问实验

实验五:串操作存储器访问实验实验环境PC机+Win 2003+emu8086 学号姓名182054424 王锐一.实验项目要求基本要求:1.实现存储器串操作访问2.编程实现安全的串拷贝功能扩展要求:1.源串与目的串有重叠的处理方法源串在低地址,目的串在高地址的移动,从尾部开始移动思考题:1.如何提高操作速度二.理论分析或算法分析(含实验项目要求的分析、数学或逻辑推导等)1.将s2复制到s1的位置2.从s1复制到s2+4的位置具体步骤:1.计数器计数16个字符2.把源赋给源地址寄存器3.把第一个地址赋值给目的寄存器4.调用移动子程序三.实现方法(含实现思路、程序流程图、实验电路图和源程序列表等)1.第一次移动:SI>DI,从前往后进行串操作即可2.第二次移动SI<DI,要改变移动的方向,从后往前3.源代码如下;首先,将s2复制到s1的位置;从s1复制到s2+4的位置;主程序mov CX, 16 ;计数器 16个字符mov SI, strs ;把源赋给源地址寄存器mov DI, std1 ;把第一个地址赋值给目的寄存器call memmove ;调用内存移动mov CX, 16mov SI, std1mov DI, std2call memmovejmp $s1 db 4 dup(0) ;空四个字节位置s2 db "0123456789ABCDEF" ;源字符串s3 db 10 dup(0) ;空十个字节位置;位置定义strs equ offset s2std1 equ offset s1std2 equ offset s2+4memmove proc nearcmp SI, DI ;比较je jendcld ;方向标志清零,默认从前往后ja j1 ;从前往后std ;方向改变add SI, CXadd DI, CXdec SIdec DIj1: rep movsb ;串操作jend:retmemmove endp四.实验结果分析(含执行结果验证、输出显示信息、图形、调试过程中所遇的问题及处理方法等,如果有引用的参考文献,安排在本节最后列出)第一次移动结束截图如下第二次移动结束截图如下思考题若CX>=2,将movesb变为movesw若CX是奇数,最后一个字节额外处理。

存储器扩展实验报告

一、实验目的1. 了解存储器的结构及其与CPU的连接方式。

2. 掌握存储器的位扩展、字扩展和字位扩展方法。

3. 通过实际操作,加深对存储器扩展原理的理解,提高动手实践能力。

二、实验原理存储器扩展是计算机硬件设计中常见的技术,目的是为了满足系统对存储容量的需求。

存储器扩展主要分为位扩展、字扩展和字位扩展三种方式。

1. 位扩展:当存储芯片的数据位小于CPU对数据位的要求时,可以通过位扩展来解决。

位扩展是将多个存储芯片的数据总线并联,形成一个更高位宽的数据总线,与CPU的数据总线相连。

2. 字扩展:当存储芯片的存储容量不能满足CPU对存储容量的要求时,可以通过字扩展来解决。

字扩展是将多个存储芯片的数据总线、读写控制线并联,形成一个更大容量的存储器,与CPU的数据总线、读写控制线相连。

3. 字位扩展:字位扩展是位扩展和字扩展的结合,既能扩展存储容量,又能扩展数据位宽。

三、实验设备1. 实验箱2. 逻辑分析仪3. 逻辑门电路4. 实验指导书四、实验步骤1. 搭建存储器扩展电路(1)根据实验要求,选择合适的存储芯片,如SRAM、ROM等。

(2)根据存储芯片的规格,确定存储器的容量、数据位宽和地址线位数。

(3)根据存储器的容量和位宽,计算所需的存储芯片数量。

(4)搭建存储器扩展电路,包括存储芯片、地址译码器、数据线、读写控制线等。

2. 仿真实验(1)使用逻辑分析仪观察存储器扩展电路的信号波形。

(2)通过实验指导书提供的测试程序,对存储器进行读写操作。

(3)观察逻辑分析仪的信号波形,分析存储器扩展电路的工作情况。

3. 分析实验结果(1)根据实验结果,验证存储器扩展电路是否满足实验要求。

(2)分析存储器扩展电路的优缺点,提出改进措施。

五、实验结果与分析1. 实验结果通过实验,搭建了存储器扩展电路,实现了存储器的位扩展、字扩展和字位扩展。

逻辑分析仪的信号波形显示,存储器扩展电路工作正常,满足实验要求。

2. 实验分析(1)位扩展:通过位扩展,实现了存储器数据位宽的增加,满足了CPU对数据位宽的要求。

双端口存储器实验步骤

双端口存储器实验步骤一、实验目的双端口存储器是一种非常重要的存储器类型,本实验旨在通过实际操作了解双端口存储器的工作原理和应用。

二、实验原理双端口存储器是指具有两个独立的数据输入/输出端口的存储器。

其中一个端口可以用于读取和写入数据,而另一个端口只能用于读取数据。

双端口存储器通常用于需要高速并发访问的应用中,例如视频处理、音频处理等。

三、实验设备1. FPGA开发板2. Quartus II软件3. 双端口RAM芯片四、实验步骤1. 设计电路图首先,需要使用Quartus II软件设计电路图。

在电路图中添加一个双端口RAM模块,并将其连接到FPGA开发板上。

确保电路图正确无误,并生成可编程文件。

2. 编写Verilog代码接下来,需要编写Verilog代码来控制RAM模块的读写操作。

代码需要包括以下内容:- 地址信号:用于指定要访问的内存地址。

- 数据信号:用于传输要写入或读取的数据。

- 读/写信号:用于指定当前操作是读还是写。

- 时钟信号:用于同步各个模块之间的操作。

3. 烧录可编程文件将生成的可编程文件烧录到FPGA开发板上,确保烧录成功。

4. 进行测试使用示波器等测试工具,对RAM模块进行读写测试。

确保数据能够正常读取和写入,并且能够在不同端口之间进行并发访问。

五、实验注意事项1. 在设计电路图和编写代码时,需要仔细阅读芯片的数据手册,并按照要求正确配置各个信号。

2. 在进行测试时,需要注意时钟信号的频率和稳定性,以确保数据传输的准确性。

3. 如果出现问题,应该及时检查电路图、代码和硬件连接,并进行排查。

实验五 扩展存储器读写实验

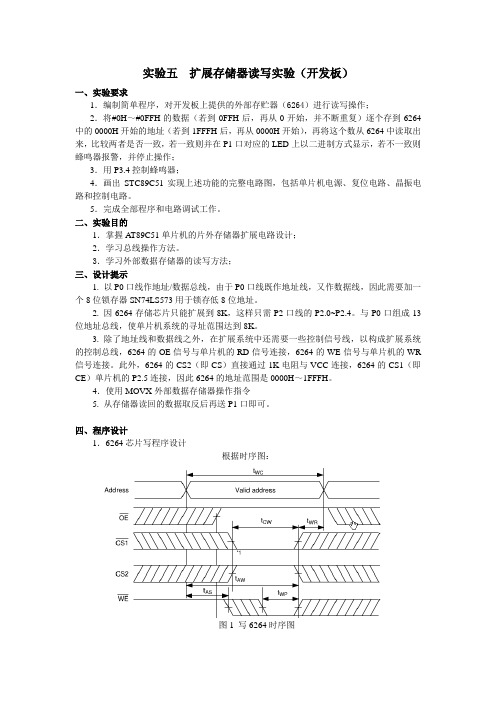

实验五扩展存储器读写实验(开发板)一、实验要求1.编制简单程序,对开发板上提供的外部存贮器(6264)进行读写操作;2.将#0H~#0FFH的数据(若到0FFH后,再从0开始,并不断重复)逐个存到6264中的0000H开始的地址(若到1FFFH后,再从0000H开始),再将这个数从6264中读取出来,比较两者是否一致,若一致则并在P1口对应的LED上以二进制方式显示,若不一致则蜂鸣器报警,并停止操作;3.用P3.4控制蜂鸣器;4.画出STC89C51实现上述功能的完整电路图,包括单片机电源、复位电路、晶振电路和控制电路。

5.完成全部程序和电路调试工作。

二、实验目的1.掌握A T89C51单片机的片外存储器扩展电路设计;2.学习总线操作方法。

3.学习外部数据存储器的读写方法;三、设计提示1. 以P0口线作地址/数据总线,由于P0口线既作地址线,又作数据线,因此需要加一个8位锁存器SN74LS573用于锁存低8位地址。

2. 因6264存储芯片只能扩展到8K,这样只需P2口线的P2.0~P2.4。

与P0口组成13位地址总线,使单片机系统的寻址范围达到8K。

3. 除了地址线和数据线之外,在扩展系统中还需要一些控制信号线,以构成扩展系统的控制总线,6264的OE信号与单片机的RD信号连接,6264的WE信号与单片机的WR 信号连接。

此外,6264的CS2(即CS)直接通过1K电阻与VCC连接,6264的CS1(即CE)单片机的P2.5连接,因此6264的地址范围是0000H~1FFFH。

4.使用MOVX外部数据存储器操作指令5. 从存储器读回的数据取反后再送P1口即可。

四、程序设计1.6264芯片写程序设计根据时序图:图1 写6264时序图2.6264芯片读程序设计根据时序图:图2 读6264时序图3.参考流程框图如下图5 流程图五、主要元件。

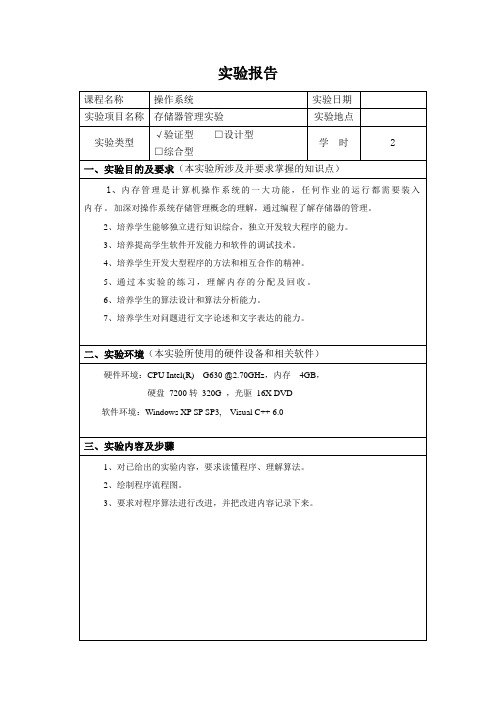

存储器管理实验实验报告

软件环境:Windows XP SP SP3, Visual C++ 6.0

三、实验内容及步骤

1、对已给出的实验内容,要求读懂程序、理解算法。

2、绘制程序流程图。

3、要求对程序算法进行改进,并把改进内容记录下来。

四、实验结果(本实验源程序清单及运行结果或实验结论、实验设计图)

五、实验总结(对本实验结果进行分析,学生软件开发能力和软件的调试技术。

4、培养学生开发大型程序的方法和相互合作的精神。

5、通过本实验的练习,理解内存的分配及回收。

6、培养学生的算法设计和算法分析能力。

7、培养学生对问题进行文字论述和文字表达的能力。

二、实验环境(本实验所使用的硬件设备和相关软件)

硬件环境:CPU Intel(R) G630 @2.70GHz,内存4GB,

实验报告

课程名称

操作系统

实验日期

实验项目名称

存储器管理实验

实验地点

实验类型

√验证型 □设计型

□综合型

学 时

2

一、实验目的及要求(本实验所涉及并要求掌握的知识点)

1、内存管理是计算机操作系统的一大功能,任何作业的运行都需要装入内存。加深对操作系统存储管理概念的理解,通过编程了解存储器的管理。

2、培养学生能够独立进行知识综合,独立开发较大程序的能力。

王楠-计组实验五Cache控制器设计实验

074-王楠-计组实验五C a c h e控制器设计实验(共4页)-本页仅作为预览文档封面,使用时请删除本页-延安大学计算机学院实验报告专用纸学号姓名王楠班级计科18课程名称计算机组成原理实验项目名称Cache控制器设计实验任课教师指导教师实验组别第组同组者教师评语及成绩:实验成绩:教师签字:(请按照实验报告的有关要求书写,一般必须包括:1、实验目的;2、实验内容;3、实验步骤与方法;4、实验数据与程序清单;5、出现的问题及解决方法;6、实验结果、结果分析与体会等内容。

)【1】实验目的(1)掌握Cache控制器的原理及其设计方法。

(2)熟悉CPLD应用设计及EDA软件的使用。

【2】实验原理1、采用直接映像方式的cache控制器图1直接映像方式2、采用CPU首先访问Cache,若在Cache中找不到目标地址,则从MEM单元中读入到Cache。

图2 Cache系统框图3、按区号、块号、块内地址访问目标地址,系统默认存储每个块的首地址,若同时访问同一块中的其他地址,将出现新访问的地址覆盖与之在同一块的另一块号。

【3】实验步骤(1)使用Quartus II 软件编辑实现相应的逻辑并进行编译,直到编译通过,Cache 控制器在EPM1270芯片中对应的引脚如图2-2-5所示,框外文字表示IO号,框内文字表示该引脚的含义(本实验例程见‘安装路径\Cpld \CacheCtrl\’工程)(2)关闭实验系统电源,按图2-2-6连接实验电路,并检查无误,图中将用户需要连接的信号用圆圈标明(3)打开实验系统电源,将生成的POF文件下载到EMP1270中去,CPLD单元介绍见实验。

(4)将时序与操作台单元的开关KK3置为‘运行’档,CLR信号由CON单元的CLR模拟给出,按动CON单元的CLR按钮,清空区表。

(5)预先往主存写入数据:联机软件提供了机器程序下载功能,以代替手动读写主存,机器程序以指定的格式写入到以TXT为后缀的文件中,机器指令的格式如下:如$P 1F 11,表示机器指令的地址为1FH,指令值为11H,本次实验只初始化00-0FH共16个单元,初始数据如下,程序中分号‘;'为注释符,分号后面的内容在下载时将被忽略掉。

计算机组成原理实验五存储器读写实验

计算机组成原理实验五存储器读写实验实验五存储器读写实验⼀、实验⽬的1.掌握存储器的⼯作特性。

2.熟悉静态存储器的操作过程,验证存储器的读写⽅法。

⼆、实验原理1.静态存储器芯⽚的6116的逻辑功能2.存储器实验单元电路3.存储器实验电路三、实验过程1.连线1)连接实验⼀(输⼊、输出实验)的全部连线。

2)按逻辑原理图连接M-W、 M-R 两根信号低电平有效信号线。

3)连接A7-A0 8根地址线。

4)连接B-AR正脉冲有效信号2.顺序写⼊存储器单元实验操作过程1)把有B-AR控制开关全部拨到0,把有其他开关全部拨到1,使全部信号都处于⽆效状态。

2)在输⼊数据开关拨⼀个实验数据,如“00000001”,即16进制的01H。

把IO-R控制开关拨下,把地址数据送到总线。

3)拨动⼀下B-AR开关,即实现“1-0-1”,产⽣⼀个正脉冲,把地址数据送地址寄存器保存。

4)在输⼊数据开关拨⼀个实验数据,如“10000000”,即16进制的80H。

把IO-R控制开关拨下,把实验数据送到总线。

5)拨动M—W控制开关,即实现“1—0—1”,产⽣⼀个负脉冲,把实验数据存⼊存储器的01H号单元。

6)按表2-11所⽰的地址数据和实验数据,重复上⾯(1)、(2)、(3)、(4)4个步骤,顺序在存储器单元中存放不同的实验数据。

表2-11 推荐的典型实验数3.顺序读出存储器单元实验操作过程(1)在输⼊数据开关上拨⼀个地址(如00000001,即16进制数01H),拨下IO —R开关把地址数据送⼈总线。

(2)拨动⼀下B—AR开关,即实现“0—1—0”,产⽣⼀个正脉冲,把地址数据送地址寄存器(AR)保存。

(3)把IO—R开关拨上,切断输⼊开关与总线的联系。

(4)拨下M—R控制开关,把实验数据从存储器的01H号单元赌场送总线,验证实验数据是否与表2-11中的内容相符合。

(5)拨动IO—R开关,即实现“1—0—1”,产⽣⼀个负脉冲,把从存储器读出的实验数据从总线送输出显⽰电路L7—L0。

存储器设计课程设计

存储器设计课程设计一、课程目标知识目标:1. 学生能够理解存储器的基本概念,掌握存储器的层次结构及其工作原理。

2. 学生能够描述不同类型的存储器(如RAM、ROM、硬盘等)的特点及应用场景。

3. 学生能够掌握存储器的设计方法,包括存储器单元、地址译码器和数据总线的连接方式。

技能目标:1. 学生能够运用所学知识,设计简单的存储器电路,并分析其性能。

2. 学生能够使用相关软件工具进行存储器的设计和仿真,提高实践操作能力。

3. 学生能够通过团队合作,解决存储器设计过程中遇到的问题,培养沟通与协作能力。

情感态度价值观目标:1. 学生能够认识到存储器在计算机系统中的重要作用,增强对硬件知识的兴趣和求知欲。

2. 学生在学习过程中,培养勇于尝试、善于思考、积极探索的良好学习习惯。

3. 学生能够认识到科技发展对生活的影响,激发创新意识,树立社会责任感。

分析课程性质、学生特点和教学要求:1. 课程性质:本课程为计算机硬件原理与应用的实践课程,要求学生具备一定的电子电路基础知识。

2. 学生特点:学生处于高年级,已具备一定的专业知识,具有较强的自学能力和动手实践能力。

3. 教学要求:注重理论与实践相结合,以学生为主体,引导他们主动探究、合作学习,提高解决问题的能力。

二、教学内容1. 存储器概述:介绍存储器的基本概念、作用、分类及其在计算机系统中的地位。

- 教材章节:第3章“存储器系统”- 内容列举:存储器的层次结构、各类存储器的特点及性能指标。

2. 存储器工作原理:讲解RAM、ROM、硬盘等存储器的工作原理及性能差异。

- 教材章节:第3章“存储器系统”- 内容列举:静态存储器、动态存储器、只读存储器、闪存、硬盘等的工作原理及性能。

3. 存储器设计方法:阐述存储器单元、地址译码器和数据总线的连接方式,以及设计存储器的基本步骤。

- 教材章节:第4章“存储器设计”- 内容列举:存储器单元设计、地址译码器设计、数据总线设计、存储器容量扩展。

黄天实验五虚拟存储器管理实验报告

实验五虚拟存储器管理学号 1415251011 姓名黄天班级 14集成1班华侨大学电子工程系设计目的1、理解虚拟存储器概念。

2、掌握分页式存储管理地址转换和缺页中断。

设计内容与基本要求1、模拟分页式存储管理中硬件的地址转换和产生缺页中断。

2、用先进先出页面调度算法处理缺页中断。

设计报告内容1、分页式存储管理和先进先出页面调度算法原理。

1).分页式存储管理原理在存储器管理中,连续分配方式会形成许多“碎片”,虽然可通过“紧凑”方法将许多碎片拼接成可用的大块空间,但须为之付出很大开销。

如果允许将一个进程直接分散地装入到许多不相邻的分区中,则无须再进行“紧凑”。

基于这一思想而产生了离散分配方式。

如果离散分配的基本单位是页,则称为分页存储管理方式。

在分页存储管理方式中,如果不具备页面对换功能,则称为基本分页存储管理方式,或称为纯分页存储管理方式,它不具有支持实现虚拟存储器的功能,它要求把每个作业全部装入内存后方能运行。

请求式分页系统是建立在基本分页基础上的,为了能支持虚拟存储器功能,而增加了请求调页功能和页面置换功能。

2).先进先出页面调度算法原理优先淘汰最早进入内存的页面,亦即在内存中驻留时间最久的页面。

该算法实现简单,只需把调入内存的页面根据先后次序链接成队列,设置一个指针总指向最早的页面。

但该算法与进程实际运行时的规律不适应,因为在进程中,有的页面经常被访问。

2、程序流程图LAB5_HT_14152510113、程序及注释。

#include<cstdio>#include<cstring>#define SizeOfPage 100 //定义页面#define SizeOfBlock 128#define M 4struct info//页表信息结构体{bool flag; //页标志,1表示该页已在主存,0表示该页不在主存long block;//块号4、运行结果以及结论。

头歌存储器实验报告

一、实验目的1. 理解存储器的基本概念和原理;2. 掌握存储器的设计与实现方法;3. 熟悉头歌存储器实验平台的操作和功能;4. 提高动手实践能力和创新意识。

二、实验背景随着计算机技术的发展,存储器在计算机系统中的地位越来越重要。

存储器主要负责数据的存储和读取,其性能直接影响到计算机系统的运行速度和稳定性。

头歌存储器实验平台是一款基于Logisim仿真软件的存储器实验平台,通过该平台可以学习和实践存储器的设计与实现。

三、实验原理1. 存储器的基本概念:存储器是计算机系统中用于存储数据和指令的设备,按照存储方式可分为随机存储器(RAM)和只读存储器(ROM)。

RAM具有读写速度快、容量可扩展等特点,适用于计算机系统中的数据缓存;ROM具有存储容量有限、数据只能读出不能写入等特点,适用于存储系统固件、启动程序等。

2. 存储器的工作原理:存储器通过地址译码器将地址空间划分为若干个存储单元,每个存储单元具有唯一的地址。

当CPU向存储器发送地址信号时,地址译码器根据地址信号选择对应的存储单元,然后通过数据总线进行数据的读写操作。

3. 存储器的设计与实现:存储器的设计主要包括存储单元的设计、地址译码器的设计、数据总线的设计等。

存储单元通常采用静态随机存储器(SRAM)或动态随机存储器(DRAM)技术;地址译码器采用译码器或查找表(LUT)实现;数据总线采用三态门实现。

四、实验内容1. 存储器模块的设计与实现:根据实验要求,设计一个具有256个存储单元的RAM模块,每个存储单元容量为8位。

采用SRAM技术实现存储单元,地址译码器采用译码器实现,数据总线采用三态门实现。

2. 存储器模块的测试:使用Logisim仿真软件对设计的存储器模块进行测试,验证存储器模块的功能是否正常。

3. 存储器模块的扩展:根据实验要求,扩展存储器模块的容量为1024个存储单元,每个存储单元容量为8位。

在原有基础上进行扩展,确保存储器模块的功能和性能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

计算机组成原理实验五《存储器设计》实验报告姓名:吴速碘黄紫微学号:******** ********班级:计算机二班日期2015、5、25实验五存储器设计一、实验目的1、掌握RAM和ROM的Verilog语言描述方法;2、学习用宏模块的方法定制RAM和ROM。

二、实验任务1、设计并实现一个128*16 的单端口的RAM;2、设计并实现一个128*16的ROM;3、设计并实现一个双端口的128*16的RAM4、设计并实现一个16*32的FIFO。

5、设计并实现正弦信号发生器,见“正弦信号发生器实验指南”。

三、实验步骤1 编写Verilog代码(见附页)2功能仿真进行分析与综合,排除语法上的错误建立波形仿真文件,输入激励生成功能仿真网表进行功能仿真,观察输出结果3选择器件DE2_70开发板的使用者请选择EP2C70F896C64绑定管脚5 下载验证DE2_70开发板的下载:使用USB-Blaster进行下载四、实验内容五、实验思考题1、分析存储器采用三态输出的原因是什么?存储器的输出端是连接在数据总线上的。

数据总线相当于一条车流频繁的大马路,必须在绿灯条件下,车辆才能进入这条大马路,否则要撞车发生交通事故。

同理,存储器中的数据是不能随意传送到数据总线上的。

例如,若数据总线上的数据是“1”(高电平5V),存储器中的数据是“0”(低电平0V),两种数据若碰到一起就会发生短路而损坏单片机。

因此,存储器输出端口不仅能呈现“l”和“0”两种状态,还应具有第三种状态“高阻"态。

呈“高阻"态时,输出端口相当于断开,对数据总线不起作用,此时数据总线可被其他器件占用。

当其他器件呈“高阻”态时,存储器在片选允许和输出允许的条件下,才能将自己的数据输出到数据总线上。

2、单端口和双端口的区别是什么?单端口ram是ram的读写只有一个端口,同时只能读或者只能写。

双端口ram是ram读端口和写端口分开,一个端口能读,另一个端口可以同时写。

3、什么情况下考虑采用双端口存储器?(1)为了使CPU不致因为等待存储器读写操作的完成而无事可做,可以采取一些加速CPU和存储器之间有效传输的特殊措施:●采用更高速的主存储器,或加长存储器的字长;●采用并行操作的双端口存储器;●在CPU和主存储器之间插入一个高速缓冲存储器(Cache),以缩短读出时间;●在每个存储器周期中存取几个字.(采用交叉存储器)(2)双端口存储器是指同一个存储器具有两组相互独立的读写控制线路,由于进行并行的独立操作,是一种高速工作的存储器。

(3)●当两个端口的地址不相同时,在两个端口上进行读写操作,一定不会发生冲突。

当任一端口被选中驱动时,就可对整个存储器进行存取,每一个端口都有自己的片选控制和输出驱动控制。

●当两个端口同时存取存储器同一存储单元时,便发生读写冲突。

为解决此问题,特设置了BUSY标志。

由片上的判断逻辑决定对哪个端口优先进行读写操作,而暂时关闭另一个被延迟的端口。

●总之,当两个端口均为开放状态(BUSY为高电平)且存取地址相同时,发生读写冲突.此时判断逻辑可以使地址匹配或片使能匹配下降至5ns,并决定对哪个端口进行存取.4、FIFO的工作特点是什么?为什么常用于实现程序中的子程序调用、递归等?特点:FIFO存储器是系统的缓冲环节,如果没有FIFO存储器,整个系统就不可能正常工作,它主要有几方面的功能:1)对连续的数据流进行缓存,防止在进机和存储操作时丢失数据;2)数据集中起来进行进机和存储,可避免频繁的总线操作,减轻CPU的负担;3)允许系统进行DMA操作,提高数据的传输速度。

这是至关重要的一点,如果不采用DMA操作,数据传输将达不到传输要求,而且大大增加CPU的负担,无法同时完成数据的存储工作。

因此,选择合适的存储芯片对于提高系统性能很重要,在以往的设计中经常采用的是“乒乓型”存储方式,这种方式就是采用两片存储器,数据首先进入其中一片,当数据满时再让数据进入第二片存储器,同时通过逻辑控制,将第一片存储器中的数据取走,以此类推,两片轮流对数据进行缓存。

这种方式有着较明显的缺点,首先是控制复杂,要有专门的逻辑来维护这种轮流机制;其次,数据流的流向要不断变化,限制了数据流的速率,还容易产生干扰。

从数据传输上说,缓存芯片容量越大,对后续时序要求就越低,可减少总线操作的频次;但从数据存储上说,就意味着需要开辟更大的内存空间来进行进行缓冲,会增加计算机的内存开销,而且容量越大,成本也越高。

因此,在综合考虑系统性能和成本的基础上,选择满足系统需要的芯片即可。

在FIFO存储器而不是地址总线上附加了表示内部缓冲器状态(Buffer Full,缓冲器已满;Buffer Empty,缓冲器为空)的状态引脚,连接于FIFO的双方利用该状态进行操作的控制。

另外,还设计了在接通电源及复位(Reset)或由于操作中的某些异常等原因而重新初始化(无数据状态)FIFO的复位引脚,这可以说是FIFO存储器的特点。

Verilog代码《sinwaveV》module sinwaveV#(parameter DATA_WIDTH=8, parameter ADDR_WIDTH=6)(input clk,output reg [(DATA_WIDTH-1):0] q);reg [(ADDR_WIDTH-1):0] Q1;wire newclk;reg [4:0] clk_cnt;assign newclk = clk_cnt[4];always @(posedge CLK)beginclk_cnt <= clk_cnt+1;endalways @(posedge newclk)beginQ1<=Q1+1;endlpm_rom0 lpm_rom0_inst ( .address ( Q1), .clock ( CLK ), .q ( DOUT ) ); endmodule《test1》// synopsys translate_off`timescale 1 ps / 1 ps// synopsys translate_onmodule test1 (address,clock,data,wren,q);input [6:0] address;input clock;input [15:0] data;input wren;output [15:0] q;`ifndef ALTERA_RESERVED_QIS// synopsys translate_off`endiftri1 clock;`ifndef ALTERA_RESERVED_QIS// synopsys translate_on`endifwire [15:0] sub_wire0;wire [15:0] q = sub_wire0[15:0];altsyncram altsyncram_component (.address_a (address),.clock0 (clock),.data_a (data),.wren_a (wren),.q_a (sub_wire0),.aclr0 (1'b0),.aclr1 (1'b0),.address_b (1'b1),.addressstall_a (1'b0),.addressstall_b (1'b0),.byteena_a (1'b1),.byteena_b (1'b1),.clock1 (1'b1),.clocken0 (1'b1),.clocken1 (1'b1),.clocken2 (1'b1),.clocken3 (1'b1),.data_b (1'b1),.eccstatus (),.q_b (),.rden_a (1'b1),.rden_b (1'b1),.wren_b (1'b0));defparamaltsyncram_component.clock_enable_input_a = "BYPASS",altsyncram_component.clock_enable_output_a = "BYPASS",altsyncram_component.intended_device_family = "Cyclone IV GX",altsyncram_component.lpm_hint = "ENABLE_RUNTIME_MOD=NO",altsyncram_component.lpm_type = "altsyncram",altsyncram_component.numwords_a = 128,altsyncram_component.operation_mode = "SINGLE_PORT",altsyncram_component.outdata_aclr_a = "NONE",altsyncram_component.outdata_reg_a = "CLOCK0",altsyncram_component.power_up_uninitialized = "FALSE",altsyncram_component.read_during_write_mode_port_a = "NEW_DATA_NO_NBE_READ",altsyncram_component.widthad_a = 7,altsyncram_component.width_a = 16,altsyncram_component.width_byteena_a = 1;endmodule《test2》// synopsys translate_off`timescale 1 ps / 1 ps// synopsys translate_onmodule test2 (address,clock,q);input [6:0] address;input clock;output [15:0] q;`ifndef ALTERA_RESERVED_QIS// synopsys translate_off`endiftri1 clock;`ifndef ALTERA_RESERVED_QIS// synopsys translate_on`endifwire [15:0] sub_wire0;wire [15:0] q = sub_wire0[15:0];altsyncram altsyncram_component (.address_a (address),.clock0 (clock),.q_a (sub_wire0),.aclr0 (1'b0),.aclr1 (1'b0),.address_b (1'b1),.addressstall_a (1'b0),.addressstall_b (1'b0),.byteena_a (1'b1),.byteena_b (1'b1),.clock1 (1'b1),.clocken0 (1'b1),.clocken1 (1'b1),.clocken2 (1'b1),.clocken3 (1'b1),.data_a ({16{1'b1}}),.data_b (1'b1),.eccstatus (),.q_b (),.rden_a (1'b1),.rden_b (1'b1),.wren_a (1'b0),.wren_b (1'b0));defparamaltsyncram_component.address_aclr_a = "NONE",altsyncram_component.clock_enable_input_a = "BYPASS",altsyncram_component.clock_enable_output_a = "BYPASS",altsyncram_component.init_file = "vv_CPU.mif",altsyncram_component.intended_device_family = "Cyclone IV GX",altsyncram_component.lpm_hint = "ENABLE_RUNTIME_MOD=NO",altsyncram_component.lpm_type = "altsyncram",altsyncram_component.numwords_a = 128,altsyncram_component.operation_mode = "ROM",altsyncram_component.outdata_aclr_a = "NONE",altsyncram_component.outdata_reg_a = "CLOCK0",altsyncram_component.widthad_a = 7,altsyncram_component.width_a = 16,altsyncram_component.width_byteena_a = 1;endmodule《test3》// synopsys translate_off`timescale 1 ps / 1 ps// synopsys translate_onmodule test3 (clock,data,rdaddress,wraddress,wren,q);input clock;input [15:0] data;input [6:0] rdaddress;input [6:0] wraddress;input wren;output [15:0] q;`ifndef ALTERA_RESERVED_QIS// synopsys translate_off`endiftri1 clock;tri0 wren;`ifndef ALTERA_RESERVED_QIS// synopsys translate_on`endifwire [15:0] sub_wire0;wire [15:0] q = sub_wire0[15:0];altsyncram altsyncram_component (.address_a (wraddress),.clock0 (clock),.data_a (data),.wren_a (wren),.address_b (rdaddress),.q_b (sub_wire0),.aclr0 (1'b0),.aclr1 (1'b0),.addressstall_a (1'b0),.addressstall_b (1'b0),.byteena_a (1'b1),.byteena_b (1'b1),.clock1 (1'b1),.clocken0 (1'b1),.clocken1 (1'b1),.clocken2 (1'b1),.clocken3 (1'b1),.data_b ({16{1'b1}}),.eccstatus (),.q_a (),.rden_a (1'b1),.rden_b (1'b1),.wren_b (1'b0));defparamaltsyncram_component.address_aclr_b = "NONE",altsyncram_component.address_reg_b = "CLOCK0",altsyncram_component.clock_enable_input_a = "BYPASS",altsyncram_component.clock_enable_input_b = "BYPASS",altsyncram_component.clock_enable_output_b = "BYPASS",altsyncram_component.intended_device_family = "Cyclone IV GX",altsyncram_component.lpm_type = "altsyncram",altsyncram_component.numwords_a = 128,altsyncram_component.numwords_b = 128,altsyncram_component.operation_mode = "DUAL_PORT",altsyncram_component.outdata_aclr_b = "NONE",altsyncram_component.outdata_reg_b = "CLOCK0",altsyncram_component.power_up_uninitialized = "FALSE",altsyncram_component.read_during_write_mode_mixed_ports = "DONT_CARE",altsyncram_component.widthad_a = 7,altsyncram_component.widthad_b = 7,altsyncram_component.width_a = 16,altsyncram_component.width_b = 16,altsyncram_component.width_byteena_a = 1;endmodule《test4》// synopsys translate_off`timescale 1 ps / 1 ps// synopsys translate_onmodule test4 (clock,data,rdreq,wrreq,empty,full,q,usedw);input clock;input [15:0] data;input rdreq;input wrreq;output empty;output full;output [15:0] q;output [4:0] usedw;wire [4:0] sub_wire0;wire sub_wire1;wire sub_wire2;wire [15:0] sub_wire3;wire [4:0] usedw = sub_wire0[4:0];wire empty = sub_wire1;wire full = sub_wire2;wire [15:0] q = sub_wire3[15:0];scfifo scfifo_component (.clock (clock),.data (data),.rdreq (rdreq),.wrreq (wrreq),.usedw (sub_wire0),.empty (sub_wire1),.full (sub_wire2),.q (sub_wire3),.aclr (),.almost_empty (),.almost_full (),.sclr ());defparamscfifo_component.add_ram_output_register = "OFF",scfifo_component.intended_device_family = "Cyclone IV GX",scfifo_component.lpm_numwords = 32,scfifo_component.lpm_showahead = "OFF",scfifo_component.lpm_type = "scfifo",scfifo_component.lpm_width = 16,scfifo_component.lpm_widthu = 5,scfifo_component.overflow_checking = "ON",scfifo_component.underflow_checking = "ON",scfifo_e_eab = "ON";endmodule。