同步计数器的设计实验报告文档

VHDL实验报告JK触发器、同步计数器

Verilog HDL实验报告Verilog 实验报告题目:JK触发器、同步计数器系部名称:通信工程专业名称:通信工程班级:班内序号:学生姓名:时间:2010.11.28一、实验内容:用JK触发器构成同步计数器:设计一个同步计数器,其逻辑图和JK触发器的逻辑图所示。

清零信号clear低电平有效,输入数据在时钟信号clock的上升沿被锁存,触发器在clock的下降沿输出,当count_enable信号为低电平时停止计数。

写出同步计数器的verilog描述和激励模块,在激励模块中使用clear和count_enable对计数器进行测试,并显示输出计数Q[3:0]。

二、实验原理图:JK触发器构成同步计数器源代码://主模块module synchronous_counter(clear,clock,count_enable,Q);input clear,clock,count_enable;output [3:0] Q;wire qbar1,qbar2,qbar3,qbar0;wire a,b,c;assign a = Q[0] & count_enable;assign b = a & Q[1];assign c = b & Q[2];JK_flip_flop myJK(count_enable,count_enable,clock,clear,Q[0],qbar0);JK_flip_flop myJK1(a,a,clock,clear,Q[1],qbar1);JK_flip_flop myJK2(b,b,clock,clear,Q[2],qbar2);JK_flip_flop myJK3(c,c,clock,clear,Q[3],qbar3);endmodule//调用的JK触发器模块module JK_flip_flop(j,k,clock,clear,q,qbar);input j,k,clock,clear;output q,qbar;wire a,b,y,ybar,c,cbar,d,q,qbar;assign a = ~ (((qbar & j)& clock) & clear);assign b = ~ ((clock & k) & q);assign y = ~ (a & ybar);assign ybar = ~ ((y & clear) & b);assign c = ~(y & cbar);assign cbar = ~ clock;assign d = ~ (cbar & ybar);assign q = ~ (c & qbar);assign qbar = ~ ((q & clear) & d);endmodule测试文件源代码:module count_test;reg count_enable=1,clock=0,clear=0;wire [3:0]Q;synchronous_counter myCount(clear,clock,count_enable,Q);initial #10 clear=1;always@(negedge clock)begin$monitor($time," clear=%b,count_enable=%b,Q=%b%b%b%b\n",clear,count_enable,Q[3],Q[2],Q[1],Q[0]);endalways clock = #5 ~clock;always count_enable= #170 ~count_enable; endmodule实验结果:波形图:三、实验心得:这次实验比上一次顺利多了,可能是因为有了前一次的铺垫,我对软件的熟悉度有了一定的提高。

计数器设计实验报告

计数器设计实验报告《计数器设计实验报告》一、实验的开始:充满好奇与期待“哇,计数器设计实验听起来就超酷的!”我兴奋地对同桌说。

就像要去探索一个神秘的宝藏,我心里充满了好奇。

那天,阳光透过窗户洒在实验桌上,好像也在为我们的实验加油助威。

老师把实验器材一一摆出来的时候,我眼睛都放光了,感觉像是打开了一个装满魔法道具的盒子。

比如那些五颜六色的导线,就像彩虹的碎片落在桌上。

同桌也很激动,他搓着手说:“这肯定很有趣,就像搭积木一样。

”这让我更加迫不及待地想要开始了。

这时候,我就想啊,生活中的很多事情不就像这个实验吗?充满未知,只要我们带着好奇和期待去探索,就会有不一样的收获。

二、遇到困难:有点沮丧但不放弃“哎呀,这怎么弄啊?”我皱着眉头嘟囔着。

按照图纸接线的时候,我老是接错,计数器就是不工作。

旁边的小组已经有进展了,我心里那叫一个着急啊,就像热锅上的蚂蚁。

我对小组成员说:“我感觉我像个迷路的小蚂蚁,完全找不到方向了。

”这时组长拍了拍我的肩膀说:“别灰心,我们再仔细看看。

”他的话就像一阵小风吹散了我心头的乌云。

就像爬山的时候突然遇到陡峭的路段,虽然难走,但只要有人鼓励,就有勇气继续。

于是我们重新检查线路,一个一个接口地核对,每检查一个接口,都像是在黑暗中摸索着寻找那把能打开成功之门的钥匙。

三、小组合作:团结的力量真伟大“我发现问题了!”小组里的一个同学大喊一声。

就像黑暗中突然出现了一道亮光。

原来是有个小零件的连接松动了。

我们都围了过去,你一言我一语地讨论起来。

“看,就是这里,差点就被我们忽略了。

”另一个同学说道。

我笑着说:“还好我们是一个小组,人多力量大啊。

”这就像一群小蜜蜂一起建造蜂巢,每个小蜜蜂都有自己的任务,缺了谁都不行。

大家齐心协力把零件重新接好,计数器开始有反应了,那一瞬间,我们都欢呼起来,那种喜悦就像在一场比赛中获得了冠军一样。

我深深感受到,在困难面前,大家团结在一起,就没有克服不了的难关,就像很多根小木棍绑在一起,就变得很结实。

实验四、 计数器的设计 电子版实验报告

实验四:计数器的设计实验室:信息楼247 实验台号: 4 日期:专业班级:机械1205 姓名:陈朝浪学号: 20122947一、实验目的1. 通过实验了解二进制加法计数器的工作原理。

2. 掌握任意进制计数器的设计方法。

二、实验内容(一)用D触发器设计4位异步二进制加法计数器由D触发器组成计数器。

触发器具有0和1两种状态,因此用一个触发器就可以表示1位二进制数。

如果把n个触发器串起来,就可以表示N位二进制数。

(用两个74LS74设计实现)(二)利用74LS161设计实现任意进制的计数器设计要求:学生以实验台号的个位数作为所设计的任意进制计数器。

先熟悉用1位74LS161设计十进制计数器的方法。

①利用置位端实现十进制计数器。

②利用复位端实现十进制计数器。

提示:设计任意计数器可利用芯片74LS161和与非门设计,74LS00为2输入与非门,74LS30为8输入与非门。

74LS161为4位二进制加法计数器,其引脚图及功能表如下。

三、实验原理图1.由4个D触发器改成的4位异步二进制加法计数器2.由74LS161构成的十进制计数器四、实验结果及数据处理1.4位异步二进制加法计数器实验数据记录表2. 画出你所设计的任意进制计数器的线路图,并说明设计思路。

设计思路:四进制为四个输出Q3Q2Q1Q0=0000,0001,0010,0011循环,第一个无效状态为0100 1,置位法设计四进制计数器:当检测到输入为0011时,先输出显示3,然后再将D置于低电位,计数器输出Q3Q2Q1Q0复位。

2,复位法设计四进制计数器:当检测到第一个无效状态0100时,通过与非门的反馈计数器的Cr首先置于低电平使计数器复位为0000。

五、思考题1. 由D触发器和JK触发器组成的计数器的区别?答:D触发器是cp上升沿触发,JK触发器是下降沿触发。

2. 74LS161是同步还是异步,加法还是减法计数器?答:同步。

加法计数器。

3. 设计十进制计数器时将如何去掉后6个计数状态的?答:加一个与非门形成负反馈。

同步计数器(3)

同步计数器的设计与实现一.实验内容利用FPGA 设计一个3位,十进制同步计数器范围000~999,三键控制(使能、复位、加计数、减计数)具体功能如下:实现计数功能,域值范围为000~999,并在数码管上显示两个触点开关实现“使能”、“复位”这两个功能,一个拨码开关控制加、减计数功能系统上电复位后,按下1键“复位”将计数器清零,使用拨码开关选择加计数,然后按住2键“使能”,使得计数器开始计数,数码管显示的数字每次加1。

松开2键,计数器保持现有计数。

切换拨码开关到减计数功能,再次按住2键,使得计数器相相反的方向计数。

二.实验原理整个计数器的结构如图所示去抖电路EN RST计数器分频_计数器分频_数码管显示UPDOWNCLKCLK数码管控制器D I S P _D I G I T S数码管FPGA而核心模块计数器的结构如下所示CLK EN UPDOWNOFBCD_OUT CLK EN UPDOWNOFBCD_OUT CLKEN UPDOWNOFBCD_OUT单个的计数器就是一个状态机,有0-9一共10种状态。

去抖电路原理如下:常用软件方法去抖,即检测出键闭合后执行一个延时程序,产生一段时间的延时(实验工具上为100ms~200ms),让前沿抖动消失后再一次检测键的状态,如果仍保持闭合状态电平,则确认为真正有键按下。

FPGA 的数码管电路如下所示;因此必须设计动态扫描来实现输出3位数的目的。

分频电路使用状态机来设计,4分频的状态机的状态转移图如下所示这样每次从s0状态出发回到s0状态输出时钟就经历了一个周期。

三.实验过程分频:library IEEE;use IEEE.STD_LOGIC_1164.ALL;entity FreDiv_4P isPort ( RST : in STD_LOGIC;CLK_I : in STD_LOGIC;CLK_O : out STD_LOGIC);end FreDiv_4P;architecture Behavioral of FreDiv_4P istype state_type is (s0,s1,s2,s3);signal state : state_type;beginprocess(RST,CLK_I)beginif (RST='0') then state <= s0; CLK_O <= '0';elsif (CLK_I='1' and CLK_I'event) thencase state iswhen s0 =>state <= s1;CLK_O <= '0';when s1 =>state <= s2;when s2 =>state <= s3;CLK_O <= '1';when s3 =>state <= s0;when others =>state <= s0;end case;end if;end process;end Behavioral;单个的计数器:画出卡诺图并化简就可以得到每一位的组合逻辑,源代码如下:library IEEE;use IEEE.STD_LOGIC_1164.ALL;entity counter_ddd isPort ( en : in STD_LOGIC;updown : in STD_LOGIC;rst : in STD_LOGIC;clk : in STD_LOGIC;overf : out STD_LOGIC;cout : out STD_LOGIC_VECTOR (3 downto 0)); --ABCD 3--0end counter_ddd;architecture Behavioral of counter_ddd is--component dff-- Port ( clk : in STD_LOGIC;-- d : in STD_LOGIC;-- q : out STD_LOGIC);--end component;signal c_buf : STD_LOGIC_VECTOR(3 downto 0);signal c_overf : STD_LOGIC;begincomb:process(clk,en,rst)beginif rst='0' thenc_buf <= "0000";--cout<="0000";elsif clk'event and clk='1' and en='0' thenc_buf(3)<=(updown and c_buf(3) and (not c_buf(2)) and (not c_buf(1)) and (not c_buf(0)))or (updown and (not c_buf(3)) and c_buf(2) and c_buf(1) and c_buf(0))or ((not updown) and (not c_buf(3)) and (not c_buf(2)) and (not c_buf(1))and (not c_buf(0)))or ((not updown) and c_buf(3) and (not c_buf(2)) and (not c_buf(1)) and c_buf(0));c_buf(2)<=((not updown) and (not c_buf(3)) and c_buf(2) and c_buf(0))or ((not updown) and (not c_buf(3)) and c_buf(2) and c_buf(1) and (not c_buf(0)))or ((not updown) and c_buf(3) and (not c_buf(2)) and (not c_buf(1)) and (not c_buf(0)))or (updown and (not c_buf(3)) and c_buf(2) and (not c_buf(1)))or (updown and (not c_buf(3)) and (not c_buf(2)) and c_buf(1) and c_buf(0))or (updown and (not c_buf(3)) and c_buf(2) and c_buf(1) and (not c_buf(0)));c_buf(1)<=(updown and (not c_buf(3)) and (not c_buf(1)) and c_buf(0))or (updown and (not c_buf(3)) and c_buf(1) and (not c_buf(0)))or ((not updown) and (not c_buf(3)) and c_buf(1) and c_buf(0))or ((not updown) and(not c_buf(3)) and c_buf(2) and (not c_buf(1)) and (not c_buf(0)))or ((not updown) and c_buf(3) and (not c_buf(2)) and (not c_buf(1)) and (not c_buf(0)));c_buf(0)<=((not c_buf(3)) and (not c_buf(0)))or (c_buf(3) and (not c_buf(2)) and (not c_buf(1)) and (not c_buf(0)));c_overf <= ((not c_buf(3)) and (not c_buf(2)) and (not c_buf(1)) and (not c_buf(0)) and (not updown))or (c_buf(3) and (not c_buf(2)) and (not c_buf(1)) and c_buf(0) and updown);-- cout <= c_buf;end if;end process;overf <= c_overf;cout <= c_buf;end Behavioral;去抖电路:signal cnt_debounce : integer range 0 to 10000000 := 0;signal cnt_sw : integer range 0 to 10000000:= 0;signal max_sw max_debounce : integer ;--定义延时;signal sw_debounced : std_logic; --- 去抖后的按键输出process(clk,rst_n) --- 使用原始的时钟beginif(rst_n = '0') thensw_debounced <= '0';cnt_debounce <= 0;cnt_sw <= 0;elsif clk'event and clk = '1' thenif sw = '0' then --- 按键低电平有效if cnt_debounce = max_debounce thencnt_debounce <= 0;sw_debounced <= '1'; --- 确认按键发生elsecnt_debounce <= cnt_debounce + 1;end if;end if;if sw_debounced = '1' then --- 检测按键是否松开if cnt_sw = max_sw thencnt_sw <= 0;sw_debounced <= '0'; --- 确认按键松开elsecnt_sw <= cnt_sw + 1;end if;sw_debounced <= cnt_sw;end if;end if;end process;动态扫描源代码:library IEEE;use IEEE.STD_LOGIC_1164.ALL;entity decoder3_7 isPort ( in1 : in STD_LOGIC_VECTOR (3 downto 0); --百位in2 : in STD_LOGIC_VECTOR (3 downto 0); --十位in3 : in STD_LOGIC_VECTOR (3 downto 0); --个位clk : in STD_LOGIC;dis_com : out STD_LOGIC_VECTOR (7 downto 0);dout : out STD_LOGIC_VECTOR (7 downto 0)); end decoder3_7;architecture Behavioral of decoder3_7 issignal counter : integer range 0 to 2;signal in_buf : STD_LOGIC_VECTOR(3 downto 0);signal dis_com_buf : STD_LOGIC_VECTOR (7 downto 0);beginprocess(clk,dis_com_buf)beginif clk'event and clk='1' thenif counter = 2 thencounter <= 0;elsecounter <= counter+1;end if;case counter iswhen 0 => dis_com_buf <= "11111110";in_buf <= in3;when 1 => dis_com_buf <= "11111101";in_buf <= in1;when 2 => dis_com_buf <= "11111011";in_buf <= in2;end case;case in_buf iswhen "0000" => dout<="00000011";when "0001" => dout<="10011111";when "0010" => dout<="00100101";when "0011" => dout<="00001101";when "0100" => dout<="10011001";when "0101" => dout<="01001001";when "0110" => dout<="01000001";when "0111" => dout<="00011111";when "1000" => dout<="00000001";when "1001" => dout<="00001001";when others => dout<="00000000";end case;end if;dis_com <= dis_com_buf;end process;end Behavioral;再在顶层模块里把这些器件按原理图连接起来就行了.源程序如下:library IEEE;use IEEE.STD_LOGIC_1164.ALL;entity syn_counter isPort ( en : in STD_LOGIC;updown : in STD_LOGIC;rst : in STD_LOGIC;clk : in STD_LOGIC;dis_com : out STD_LOGIC_VECTOR (7 downto 0);cout : out STD_LOGIC_VECTOR (7 downto 0)); end syn_counter;architecture Behavioral of syn_counter iscomponent decoder3_7Port ( in1 : in STD_LOGIC_VECTOR (3 downto 0); --百位in2 : in STD_LOGIC_VECTOR (3 downto 0); --十位in3 : in STD_LOGIC_VECTOR (3 downto 0); --个位clk : in STD_LOGIC;dis_com : out STD_LOGIC_VECTOR (7 downto 0);dout : out STD_LOGIC_VECTOR (7 downto 0));end component;component counter_dddPort ( en : in STD_LOGIC;updown : in STD_LOGIC;rst : in STD_LOGIC;clk : in STD_LOGIC;overf : out STD_LOGIC;cout : out STD_LOGIC_VECTOR (3 downto 0)); --ABCD 3--0 end component;component divclkPort ( clk : in STD_LOGIC;rst : in STD_LOGIC;out_buff : out STD_LOGIC);end component;component divPort ( RST : in STD_LOGIC;CLK_I : in STD_LOGIC;CLK_O : out STD_LOGIC);end component;component div2Port ( RST : in STD_LOGIC;CLK_I : in STD_LOGIC;CLK_O : out STD_LOGIC);end component;--component div2_counter-- Port ( clk : in STD_LOGIC;-- rst : in STD_LOGIC;-- out_buff : out STD_LOGIC);--end component;--component key_noshake-- Port ( sw : in STD_LOGIC;-- clk : in STD_LOGIC;-- rst_n : in STD_LOGIC;-- sw_out : out STD_LOGIC);--end component;signal out_clk,out_clk2 : STD_LOGIC;signal cout1 : STD_LOGIC_VECTOR (3 downto 0);signal cout2 : STD_LOGIC_VECTOR (3 downto 0);signal cout3 : STD_LOGIC_VECTOR (3 downto 0);signal overf1: STD_LOGIC;signal overf2,overf3 : STD_LOGIC;begin--u0:key_noshake port map(rst,clk,rst,rst1);--u1:key_noshake port map(en,clk,rst1,en1);u2:div port map(rst,clk,out_clk);--u3;div-counter(clk,rst,out_clk2);u3:div2 port map(rst,clk,out_clk2);u4:counter_ddd port map(en,updown,rst,out_clk,overf1,cout1);--个位计数u5:counter_ddd port map(en,updown,rst,overf1,overf2,cout2); --十位计数u6:counter_ddd port map(en,updown,rst,overf2,overf3,cout3); --百位计数u7:decoder3_7 port map(cout3,cout1,cout2,out_clk2,dis_com,cout);end Behavioral;Testbench代码如下:ENTITY SYNTB ISEND SYNTB;ARCHITECTURE behavior OF SYNTB IS-- Component Declaration for the Unit Under Test (UUT)COMPONENT syn_counterPORT(en : IN std_logic;updown : IN std_logic;rst : IN std_logic;clk : IN std_logic;dis_com : OUT std_logic_vector(7 downto 0);cout : OUT std_logic_vector(7 downto 0));END COMPONENT;--Inputssignal en : std_logic := '0';signal updown : std_logic := '0';signal rst : std_logic := '0';signal clk : std_logic := '0';--Outputssignal dis_com : std_logic_vector(7 downto 0);signal cout : std_logic_vector(7 downto 0);-- Clock period definitionsconstant clk_period : time := 20 ns; BEGIN-- Instantiate the Unit Under Test (UUT) uut: syn_counter PORT MAP (en => en,updown => updown,rst => rst,clk => clk,dis_com => dis_com,cout => cout);-- Clock process definitionsclk_process :processbeginclk <= '0';wait for clk_period/2;clk <= '1';wait for clk_period/2;end process;-- Stimulus processstim_proc: processbeginrst<='1';wait for 100 ns;en<='1';updown<='1';rst<='0';wait for 2000 ms;end process;END;四.实验结果与分析五.实验总结通过这次同步计数器的实验,让我明白了计数器的状态机的设计方法,也明白了计数器之间如何相互连接起来,知道了去抖电路的工作原理与设计方法。

同步计数器实验报告

同步计数器实验报告集成计数器实验报告实验三集成计数器一、实验目的1、掌握集成计数器构成N进制的计数器的连接方法。

二、预习要求1.熟悉芯片各引脚排列。

2.理解构成模长M进制计数器的原理。

3.实验前设计好实验所用电路,画出实验用的接线图。

三、实验内容1、设计一模长M = 60进制的计数电路。

1)用同步连接反馈预置法实现。

2)用同步连接反馈清零法实现。

2、按设计图连接电路。

CP接频率为1Hz的方波脉冲,各计数器的输出Q3Q2Q1Q0接七段BCD显示译码器CD4511的DCBA输入端,CD4511的输出接七段数码显示器。

3、.接通实验箱电源,观察七段数码显示器计数状态的变化过程,并记录该状态循环。

四、实验器材数字逻辑实验箱,74LS160,74LS00,74LS20。

五、实验报告要求1、60进制计数器的电路设计图、连线图和计数器的测试结果。

4、测试过程中出现的问题及解决办法。

六、实验用元件介绍1.集成计数器74LS160本实验所用集成芯片为异步清零同步预置四位8421码10进制加法计数器74LS161,集成芯片的各功能端如图所示,其功能见附表。

V QQQQ74LS160功能表RDET EP CP D D DD QQ Q Q 0××××××××0 0 0 010××↑D C B A D C B A 110 ××××××保持11×0×××××保持111 1↑××××计数10 1 2 374LS160为异步清零计数器,即RD端输入低电平,不受CP控制,输出端立即全部为“0”,功能表第一行。

74LS160具有同步预置功能,在RD端无效时,LD端输入低电平,在时钟共同作用下,CP 上跳后计数器状态等于预置输入DCBA,即所谓“同步”预置功能(第二行)。

计数器设计实验报告

实验报告实验:计数器设计班级:12传感网姓名:**学号:**********一、实验目的1.熟悉硬件描述语言软件的使用。

2.数序计数器的工作原理和逻辑功能。

3.掌握计数器的设计方法。

二、实验原理计数器是数字系统中使用最多的时序逻辑电路,其应用范围非常广泛。

计数器不仅能用于时钟脉冲技术,而且还用于定时、分频、产生节拍脉冲和脉冲序列以及进行数字运算等。

三、实验内容1.设计一个具有仅为输出信号的十进制加法计数器,要求有异步清零功能及同步使能控制端。

(1)代码library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt10 isport (clk,rst,en,load:in std_logic;data:in std_logic_vector(3 downto 0);dout:out std_logic_vector(3 downto 0);cout:out std_logic);end cnt10;architecture behav of cnt10 isbeginprocess(clk,rst,en,load)variable q:std_logic_vector(3 downto 0);beginif rst='0' then q:=(others=>'0');elsif clk'event and clk='1' thenif en='1' thenif (load='0') then q:=data; elseif q<9 then q:=q+1;else q:=(others=>'0');end if;end if;end if;end if;if q="1001" then cout<='1';else cout<='0';end if;dout<=q;end process;end behav;(2)编译完成(3)波形(4)网表RTL传输层映射2.设计一个具有进位输出信号的六进制加法计数器,要求具有异步清零功能及同步使能控制端。

黄红涛实验报告同步计数器

黄红涛实验报告同步计数器学生实验报告实验课名称:硬件描述语言实验项目名称:同步计数器专业名称:电子科学与技术班学级:电子科学与技术一班号:学生姓名:黄红涛教师姓名:程鸿亮________年_11___月__13__日组别_____________________同组同学_ 刘增辉实验日期:年 11 月 13 日实验室名称______ 成绩____ 一、实验名称:同步计数器二、实验目的与要求:实验目的:设计一个同步二十四进制计数器,理解触发器同步计数工作机制,掌握同步触发控制的描述方法以及异步清零的描述方法实验要求:通过编程,实现一个同步二十四进制计数器,要求有1个异步清零端、1个时钟脉冲输入、驱动7段数码管显示的个位和十位信号端,具体接口说明如下图所示:计数时钟脉冲输入;:异步清零信号,高电平有效,此时输出显示为“00”[60]:十位数的7段数码管显示输出; [60]:个位数的7段数码管显示输出;首先在上进行功能和时序仿真,之后通过器件及其端口配置下载程序到开发平台中在硬件实现中,要求:1 用实验平台的按键实现清零():采用模式2的输入方式,要求用键1实现清零2 用实验平台的数码管实现计数输出的显示:要求使用数码管8显示十位、数码管7显示个位3 用实验平台的发光阵列的8显示进位信号,要求当数码管输出“23”时,进位输出有效4 计数器的时钟信号采用实验平台的0时钟资源:可以通过跳线选择不同的时钟频率,0的时钟范围是~20此频率不能选择的太高,一般应选择16Hz以下,同学们可以调节此跳线观察计数效果三、实验内容:实验步骤:1 打开软件,建立一个新的工程:2 建立文件:3 建立矢量波形文件4 进行功能仿真5 进行时序仿真6 器件的下载四、实验条件:1 操作系统2 开发系统3 杭州康芯硬件开发平台五、实验原理:1.程序流程图:开始_:=_ 10_:=_/10<=__7(_)<=__7(_)结束开始='1'?NYN' ='1'?YN_=23?Y_<=0;co<='0';_<=_+1;co<='0';_<=0;co<='1';结束2硬件设置与调试原理:1)采用模式2的输入方式,用验平台的按键实现清零(),用8作为进位输出指示灯,用数码管8显示十位、数码管7显示个位,当异步清零端为高电平‘1’时,无论当前计数器的输出为多少,即可改变输出结果为“00”,数码管8,数码管7分别显示输出的十位和个位,计数结果直接可以通过数码管的显示数据读出来,当计数到达“23”时,此上面为高电平,正常发光2)计数器的输出信号随时钟信号的变化具有规律性,他们的变化遵循以下规律:C00 1 2 3 4 5 6 7 8 9 0 10 0 0 0 0 0 0 0 0 0 0 0C02 3 4 5 6 7 8 9 0 1 2 30 0 0 0 0 0 0 0 0 0 0 13)计数器的时钟信号采用实验平台的0时钟资源:可以通过跳线选择不同的时钟频率,0的时钟范围是~20此频率不能选择的太高,一般应选择16Hz以下开发平台的适配板上有20时钟资源,通过适配板上的跳线可以选择采用适配板的固定20频率信号或者I/O板上的0时钟资源(此两类时钟在管脚映射表中都称为0,当然对于此实验计数时钟频率不能太高,所以必须通过跳线选择较低的频率)0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 11 0 1 10 1 1 0 1 1 0 1 1 0 1 1 0 1 1 0 1 1 0 1 1 0 1 1 0 1 2 0 1 2 0 12 0 1 2六、源代码: ;__; 24(: _;: __(6 0) co: _);;24_: 0 23;__7(: 0 10) __ _:__(6 0);0=>_:=""; 1=>_:=""; 2=>_:=""; 3=>_:=""; 4=>_:=""; 5=>_:=""; 6=>_:=""; 7=>_:=""; 8=>_:=""; 9=>_:=""; =>_:=""; ;_;__7;:()(='1')_<=0; co<='0';(' ='1')(_=23) _<=0;co<='1';_<=_+1; co<='0';; ;;:(_)_t_t:;_t:=_ 10; _t:=_/10;<=__7(_t); <=__7(_t);; ;七、实验结果与分析:创建波形文件,进行功能仿真:进行时序仿真:实验结果照片正常计数状态,数码管8和数码管7进行输出显示,此时计数到4 清零信号有效,输出为“00”输出为“23”时,进位显示8被点亮八、讨论和回答问题及体会:1、信号与变量值带入有区别在变量的赋值语句中,该语句一旦执行,其值会立即被赋予变量,在执行下一条语句时,该变量的值就为上一句新赋的值而对于信号代入语句,该语句即使被执行也不会立即代入,下一条语句执行时,仍使用原来的信号值故在程序中计数时,要使用变量,否则会报错2、在程序的编写过程中,我们应该首先分析各个端口的优先级顺序,这一点就可以利用语句首先进行判断这一点是用语言进行设计数字逻辑电路的共同点,是我们学习过程中必须掌握的内容3、实验中,需要对每一个端口指定器件的引脚,在引脚指定过程中需要参照开发系统所给的I/O端口映射表,通过开发平台上每个I/O器件附近的I/O编号,在映射表中找到相应的引脚名,填入相应的对话框这一应该特别小心,也是实验最后成败的最为关键的一步4、在实验中所遇到的还有一个问题就是模式的选择,在此实验中,应该选择模式2注意频率资源的选择,选择的频率,但此频率不能选择的太高,一般应选择16Hz以下注意适配板上跳线,若跳线置右,则连接I/O板上的0,跳线置左,则选择适配板上的20时钟这些都是实验中的小问题,在实验中只有养成严谨科学的态度和作风,认真注意各个实验细节,才能保证实验的最后成功。

同步计数器设计

2.选择触发器类型,求驱动方程和输出方程。 2.选择触发器类型,求驱动方程和输出方程。 选择触发器类型 触发器类型: 触发器类型:D 个数: 个数:2

4

2.选择触发器类型,求驱动方程和输出方程。 2.选择触发器类型,求驱动方程和输出方程。 选择触发器类型 状态转换表 输入 X 0 0 0 1 1 1 1 现态 Q1n Q0n 0 0 0 1 1 0 0 0 0 1 1 0 1 1

D0 = Q1 Q 0 + Q 0 X

6

Z 2 = Q1Q1 Q 0 + Q 0 X

D1 = Q1Q0 + Q1 Q0 X

Z 1 = Q1 Q 0 X

Z 2 = Q1Q0 X

7

设计举例

全状态转换表 4. 画全状态图 次 态 驱动信号 输出 输入 现态 X/Z1Z2 X Q1n Q0n Q1n+1Q0n+1 D1 D0 Z1 Z2 0 1 0 0 0 0 0 0 1 0 1 1 0 1 0 0 0 0 ☓/00 1 0 0 0 0 0 1 0 0 00 01 1 0 0 0 1 0 1 0 0 0/10 ☓/00 1 0 1 1 0 1 0 0 0 1/01 0/00 1 1 0 1 1 1 1 0 0 11 10 1 1 1 0 0 0 0 0 1 1/00 0 1 1 0 0 0 0 0 0 电路是一个能自启动且满足带进位输出端、模可变的计数器。 电路是一个能自启动且满足带进位输出端、模可变的计数器。

8

设计举例

仿真波形: 仿真波形:

X 1

0 2 0

X=0,三进制加法计数器 =1,四进制加法计数器 = , X= ,

9

10

Q1 Q0 X 00

0 0 1 0

同步计数器VHDL的设计

EDA技术及应用实验报告

——同步计数器VHDL的设计

班级:XXX

姓名:XXX

学号:XXX

一、实验目的:

学习数控分频器的设计、分析和测试方法。

二、实验原理:

同步计数器的功能就是在时钟脉冲的控制下,构成计数器的各触发器状态同时发生变化的一类计数器。

本实验是一个模为60,具有异步复位、同步置数功能的8421BCD码计数器。

三、实验内容和步骤:

1、打开文本编辑器,完成同步计数器的设计。

2、完成同步计数器的设计输入、进行目标器件选择。

3、引脚锁定。

4、编译。

5、对同步计数器设计进行仿真。

四、实验下载并实测

该同步计数器具有异步复位,同步置数功能。

当load=1时,便把输入信号与指导输出端,然后开始计数,计数到60时,LED灯闪烁,计数器从0开始计数。

74x163同步计数器实验报告

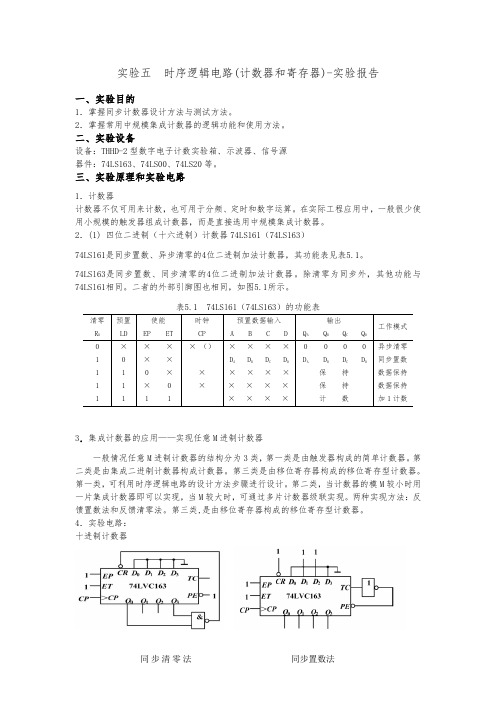

74x163同步计数器实验报告篇一:100进制计数器实验报告南京信息工程大学数字电路实验报告学号:20111305062班级:11电信2班姓名:杨天星一、引言计数器电路是一种随时钟输入CP 的变化,其输出按一定的顺序变化的时序电路,其变化的特点不同可将计数器电路按以下几种进行分类:按照时钟脉冲信号的特点分为同步计数器和异步计数器两大类,其中同步计数中构成计数器的所有触发器在同一个时刻进行翻转,一般来讲其时钟输入端全连在一起;异步计数器即构成计数器的触发器的时钟输入CP没有连在一起,其各触发器不在同一时刻变化。

一般来讲,同步计数器较异步计数器具有更高的速度。

按照计数的数码变化升降分为加法计数器和减法计数器,也有一些计数器既可实现加计数又可实现减计数器,这类计数器为可逆计数器。

按照输出的编码形式可分为:二进制计数器、二—十进制计数器、循环码计数器等。

按计数的模数(或容量)分:十进制计数器、十六进制计数、六十进制计数器等。

二、主要设计要求利用74LS163设计模为100的计数器一、电路设计和分析1、74LS163逻辑功能表2、芯片特性74LS163为二进制四位并行输出的计数器,它有并行装载输入和同步清零输入端。

74LS00为四二输入与非门。

74LS20为四输入与非门。

3、设计思路用两个模为10的计数器构成模为100的计数器。

模为10的计数器实现方法:用一个与非门,两个输入取自QA和QD,输出接清零段CLR。

当第9个脉冲结束时,QA和QD 都为“1”,则与非门输出为“0”,并加到CLR端,因CLR为同步清零端,此时虽已建立清零信号,但并不执行,只有第10个时钟脉冲到来后74LS163才被清零。

4、电路仿真第三章一、实验结果分析1、设计结果该设计可以实现0到99循环计数。

2、遇到的问题一开始设计时,只简单完成了2个10位计数器功能,以至于没有考虑到十位清零问题,做出来的是90进制的计数器。

3、解决方法将十位163芯片的ENT引脚与QA 和QD一起通过与非门接到CLR,这样当计数器到99时就会给一个低电平,使十位清零。

设计计数器的实验报告

设计计数器的实验报告设计计数器的实验报告引言:计数器是数字电路中常见的一个组件,它可以用来记录和显示某个事件的次数或周期。

本实验旨在设计一个简单的二进制计数器,通过实际操作和观察,加深对计数器的原理和实现方式的理解。

一、实验目的本实验的主要目的是掌握计数器的设计原理和实现方法,具体包括以下几点:1. 了解计数器的基本概念和工作原理;2. 学习使用逻辑门和触发器构建计数器电路;3. 实际操作计数器电路并观察其输出结果。

二、实验器材1. 逻辑门集成电路(如与门、或门、非门等);2. 触发器集成电路(如RS触发器、D触发器等);3. 连线、电源、示波器等实验器材。

三、实验步骤1. 确定计数器的位数:根据实际需求,选择计数器的位数。

本实验以4位计数器为例。

2. 确定计数器的计数方式:根据实际需求,选择计数器的计数方式。

本实验以二进制计数方式为例。

3. 设计计数器的逻辑电路:根据所选择的位数和计数方式,设计计数器的逻辑电路。

以4位二进制计数器为例,可以使用4个D触发器构建。

将D触发器的时钟输入端串联,将每个D触发器的输出端连接到下一个D触发器的数据输入端,形成一个环形结构。

4. 连接电路并进行实验:按照设计好的逻辑电路连接实验器材,接入电源后,观察计数器的输出结果。

5. 调试和优化:如果计数器的输出结果不符合预期,可以检查电路连接是否正确,逻辑门和触发器是否工作正常,及时调试和优化。

四、实验结果与分析在本实验中,我们设计了一个4位二进制计数器,并成功实现了计数功能。

通过观察计数器的输出结果,可以发现计数器按照二进制方式进行计数,每次计数加1,当计数达到最大值时,会回到初始值重新开始计数。

通过实验可以得出以下结论:1. 计数器的位数决定了其能够表示的最大计数值,位数越多,最大计数值越大;2. 计数器的计数方式决定了其计数规律,二进制计数方式是最常见和简单的计数方式;3. 计数器的设计需要根据实际需求进行选择和优化,可以根据需要增加位数或者改变计数方式。

实验十二计数器实验

STE-3A 数字电路实验—12实验十二同步计数器和异步计数器一.实验目的1. 进一步掌握异步和同步计数器的工作原理和逻辑功能。

2. 掌握中规模集成计数器逻辑功能的测试方法。

3. 熟悉用中规模集成计数器实现N进制计数器的方法。

二.电路原理简述计数器是具有计数功能的时序逻辑电路,是数字系统中的基本数字部件,它的功能是用触发器统计脉冲的个数。

它的应用十分广泛,不仅用来计数、还可以用于分频、定时。

按输入计数时钟脉冲方式的不同,可分为异步计数器和同步计数器;按计数值的加减不同,可分为加法计数器和减法计数器(也包括加减法功能同时具备的可逆计数器;按数制的不同,可分为二进制计数器,十进制计数器(即二-十进制计数器),N进制计数器。

三.实验设备名称数量型号1.适配器1只SD1282.2JK触发器2只SD1193.4与门1只SD1034.LED显示器1只SD1125.四位计数器1只SD1056.电源1只5V7.实验板1块5孔8.电子导线若干四.实验内容与步骤1. 异步二进制计数器由四只JK触发器组成四位异步二进制加法计数器(见图12-1)。

计数时钟脉冲不是同时加到所有触发器的cp输入端,应翻转的触发器并不同时翻转的计数器称为异步计数器。

JK 触发器作计数触发器使用时,只要将J、K接高电平1即可。

根据JK触发器的状态表,J=K =1时,每当一个计数时钟脉冲结束时,触发器就翻转一次,实现了计数触发。

低位触发器翻转两次即计两数就产生一个进位脉冲,因此,高位触发器的CP端应接低位的Q端。

该计数器的工作波形图如图12-2所示。

图12-1图12-2表12-1按图12-3连接线路,用手控方式按表4发计数时钟脉冲,观察A、B、C、D四个输出端的变化,并将实验结果记入表12-1中。

图12-32. 同步二进制计数器由四只JK触发器再加二只与门就可组成四位同步二进制加法计数器(见图12-4),计数时钟脉冲同时加到所有触发器的时钟输入端,使应翻转的触发器同时翻转的计数器称为同步计数器。

进制同步计数器设计

实验名称:100进制同步计数器设计专业班级:姓名:学号:实验日期:一、实验目的:1、掌握计数器的原理及设计方法;2、设计一个0~100的计数器;3、利用实验二的七段数码管电路进行显示;二、实验要求:1、用VHDL 语言进行描写;2、有计数显示输出;3、有清零端和计数使能端;三、实验结果:1. VHDL程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;PACKAGE my_pkg ISComponent nd2 -- 或门PORT (a,b: IN STD_LOGIC;c: OUT STD_LOGIC);END Component;Component led_decoderPORT (din:in std_logic_vector(3 downto 0 ); --四位二进制码输入seg:out std_logic_vector(6 downto 0) ); --输出LED七段码END Component;Component CNT60 --2位BCD码60进制计数器PORT( CR:IN STD_LOGIC;EN:IN STD_LOGIC;CLK:IN STD_LOGIC;OUTLOW:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);OUTHIGH:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0) );END Component;Component CNT100 --带使能和清零信号的100进制计数器PORT(CLK:IN STD_LOGIC;EN:IN STD_LOGIC;CLR:IN STD_LOGIC;OUTLOW:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);OUTHIGH:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0) ); END Component;Component freq_div --50MHZ时钟分频出1HzPORT(clkinput : IN STD_LOGIC;output : OUT STD_LOGIC);END Component;Component jtd --交通灯控制器PORT(CLKIN:IN STD_LOGIC; --50MHZR1,G1,R2,G2,R3,G3,R4,G4:OUT STD_LOGIC; --红绿灯信号输出GAO,DI:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0) --倒计时输出);END Component;END my_pkg;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE work.my_pkg.ALL; --打开程序包ENTITY Demo3 ISPORT (CRl:IN STD_LOGIC;ENl:IN STD_LOGIC;CLKIN: IN STD_LOGIC;LEDLOW,LEDHIGH: OUT STD_LOGIC_VECTOR(6 downto 0));END Demo3;ARCHITECTURE behv OF Demo3 ISSIGNAL CLKTEMP: STD_LOGIC; --定义中转信号SIGNAL LEDLOWTEMP,LEDHIGHTEMP:STD_LOGIC_VECTOR(3 downto 0);BEGINu1:freq_div PORT MAP(CLKIN,CLKTEMP); --位置关联方式u2:CNT60 PORTMAP(CR=>CRl,EN=>ENl,CLK=>CLKTEMP,OUTLOW=>LEDLOWTEMP,OUTHIGH=>LEDHIGHTE MP); --名字关联方式u3:led_decoder PORT MAP(LEDLOWTEMP,LEDLOW); --低位数码管输出u4:led_decoder PORT MAP(LEDHIGHTEMP,LEDHIGH); --高位数码管输出END behv;LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY freq_div ISPORT(clkinput : IN STD_LOGIC;output : OUT STD_LOGIC);END freq_div;ARCHITECTURE rt OF freq_div ISSIGNAL count_signal : INTEGER RANGE 0 TO 25000000;signal mid1 : STD_LOGIC ;BEGINPROCESS (clkinput)BEGINIF (clkinput'EVENT AND clkinput = '1') THENif count_signal=24999999 then --50MHz division to 1Hzcount_signal <= 0;mid1<= not mid1;elsecount_signal <= count_signal + 1;end if;output <= mid1;end if;END PROCESS;end rt;--文件名:decoder.vhdlibrary IEEE;use IEEE.STD_LOGIC_1164.ALL;entity led_decoder isPort (din:in std_logic_vector(3 downto 0 ); --四位二进制码输入seg:out std_logic_vector(6 downto 0) ); --输出LED七段码end led_decoder;architecture Behavioral of led_decoder isbeginprocess(din)begincase din iswhen "0000" =>seg<="1000000";--0when "0001" => seg<="1111001";--1when "0010" => seg<="0100100";--2when "0011" => seg<="0110000";--3when "0100" => seg<="0011001";--4when "0101" => seg<="0010010";--5when "0110" => seg<="0000010";--6when "0111" => seg<="1011000";--7when "1000" => seg<="0000000";--8when "1001" => seg<="0010000";--9when others => seg<="0000110";--Eend case;end process;end Behavioral;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT60 ISPORT(CR:IN STD_LOGIC;EN:IN STD_LOGIC;CLK:IN STD_LOGIC;OUTLOW:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);OUTHIGH:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0) );END CNT60;ARCHITECTURE behav OF CNT60 ISBEGINPROCESS(CLK,CR,EN)BEGINif CR='1' thenOUTHIGH<="0000";OUTLOW<="0000";elsif EN ='1'thenIF CLK'EVENT AND CLK='1' THENIF OUTHIGH="1001" AND OUTLOW="1001" THENOUTHIGH<="0000";OUTLOW<="0000";ELSIF OUTLOW="1001" THENOUTHIGH<=OUTHIGH+1;OUTLOW<="0000";ELSE OUTLOW<=OUTLOW+1;END IF;END IF;END IF;END PROCESS;END behav;2.仿真结果以及说明①. 分频器仿真结果:经过多次仿真,发现按照实验要求分频出1HZ的频率是无法仿真出需要的结果的,因为时钟脉冲太多,QuartusII显示不了。

实验五--时序逻辑电路实验报告

实验五时序逻辑电路(计数器和寄存器)-实验报告一、实验目的1.掌握同步计数器设计方法与测试方法。

2.掌握常用中规模集成计数器的逻辑功能和使用方法。

二、实验设备设备:THHD-2型数字电子计数实验箱、示波器、信号源器件:74LS163、74LS00、74LS20等。

三、实验原理和实验电路1.计数器计数器不仅可用来计数,也可用于分频、定时和数字运算。

在实际工程应用中,一般很少使用小规模的触发器组成计数器,而是直接选用中规模集成计数器。

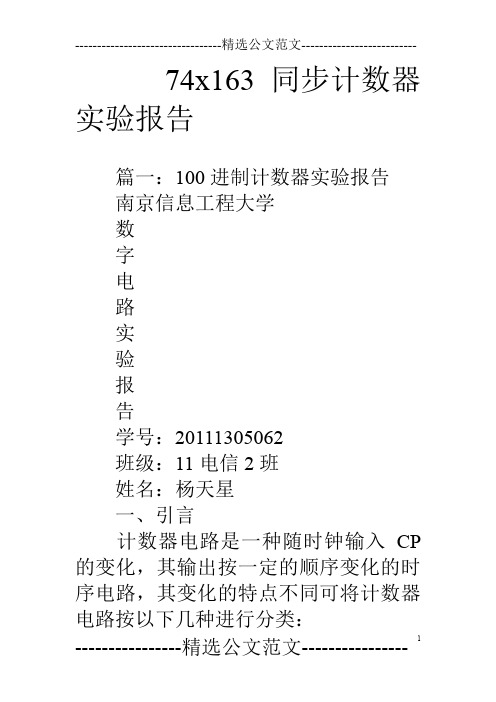

2.(1) 四位二进制(十六进制)计数器74LS161(74LS163)74LSl61是同步置数、异步清零的4位二进制加法计数器,其功能表见表5.1。

74LSl63是同步置数、同步清零的4位二进制加法计数器。

除清零为同步外,其他功能与74LSl61相同。

二者的外部引脚图也相同,如图5.1所示。

表5.1 74LSl61(74LS163)的功能表清零预置使能时钟预置数据输入输出工作模式R D LD EP ET CP A B C D Q A Q B Q C Q D0 ××××()××××0 0 0 0 异步清零1 0 ××D A D B D C D D D A D B D C D D同步置数1 1 0 ××××××保持数据保持1 1 ×0 ×××××保持数据保持1 1 1 1 ××××计数加1计数3.集成计数器的应用——实现任意M进制计数器一般情况任意M进制计数器的结构分为3类,第一类是由触发器构成的简单计数器。

第二类是由集成二进制计数器构成计数器。

第三类是由移位寄存器构成的移位寄存型计数器。

第一类,可利用时序逻辑电路的设计方法步骤进行设计。

数电实验7——计数器. 报告docx

深圳大学实验报告课程名称:数字电子技术实验项目名称:计数器学院:光电工程学院专业:光源与照明指导教师:**报告人:黄学号:2016 班级:实验时间:2018年12月19日实验报告提交时间:教务处制三、实验原理:计数器器件是应用较广的器件之一,它有很多型号,各自完成不同的功能,可根据不同的需要选用。

本实验选用74LS162做实验器件。

74LS162引脚图见图1。

74LS162是十进制BCD同步计数器。

Clock是时钟输入端,上升沿触发计数触发器翻转。

允许端P和T都为高电平时允许计数,允许端T为低时禁止Carry产生。

同步预置端Load加低电平时,在下一个时钟的上升沿将计数器置为预置数据端的值。

清除端Clear为同步清除,低电平有效,在下一个时钟的上升沿将计数器复位为0。

74LS162的进位位Carry在计数值等于9时,进位位Carry为高,脉宽是1个时钟周期,可用于级联。

四、实验内容与步骤:(一)实验内容:1、用1片74LS162和1片74LS00采用复位法构一个模7计数器。

用单脉冲做计数时钟,观测计数状态,并记录。

用连续脉冲做计数时钟,观测并记录Q D,Q C,Q B,Q A的波形。

2、用1片74LS162和1片74LS00采用置位法构一个模7计数器。

用单脉冲做计数时钟,观测并记录Q D,Q C,Q B,Q A的波形。

3、用2片74LS162和1片74LS00构成一个模60计数器。

2片74LS162的Q D,Q C,Q B,Q A分别接两个译码显示的D,B,C,A端。

用单脉冲做计数时钟,观测数码管数字的变化,检验设计和接线是否正确。

(二)实验接线及测试结果:1、复位法构成的模7计数器接线图及测试结果(1)复位法构成的模7计数器接线图图9.1 复位法7进制计数器接线图1 图9.2 复位法7进制计数器接线图2 图中,AK1是按单脉冲按钮,LED0,LED1,LED2和LED3是逻辑状态指示灯,100kHz 是连续脉冲源。

进制同步计数器设计报告

浙江万里学院实验报告实验名称: 100进制同步计数器设计专业班级:电子103姓名:徐强学号: 2018014092 实验日期:2018.5.10一、实验目的:1、掌握计数器的原理及设计方法;2、设计一个0~100的计数器;3、利用实验二的七段数码管电路进行显示;二、实验要求:1、用VHDL 语言进行描写;2、有计数显示输出;3、有清零端和计数使能端;三、实验结果:1. VHDL程序LIBRARY IEEE。

USE IEEE.STD_LOGIC_1164.ALL。

PACKAGE my_pkg ISComponent nd2 -- 或门PORT (a,b: IN STD_LOGIC。

c: OUT STD_LOGIC>。

END Component。

Component led_decoderPORT (din:in std_logic_vector(3 downto 0 >。

--四位二进制码输入 seg:out std_logic_vector(6 downto 0> >。

--输出LED七段码END Component。

Component CNT60 --2位BCD码60进制计数器PORT( CR:IN STD_LOGIC。

EN:IN STD_LOGIC。

CLK:IN STD_LOGIC。

OUTLOW:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0>。

OUTHIGH:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0> >。

END Component。

Component CNT100 --带使能和清零信号的100进制计数器PORT(CLK:IN STD_LOGIC。

EN:IN STD_LOGIC。

CLR:IN STD_LOGIC。

OUTLOW:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0>。

十二进制同步计数器的设计

同步计数器的设计

《数字电路与逻辑设计》

11/28

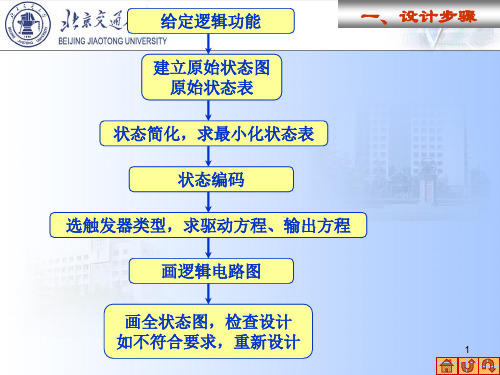

1.确定电路所需的触发器数目。 2.列出计数器的状态转换图。 3.根据状态转换图画出状态转换表。 4.根据状态转换表,写出J-K触发器的状态方程和驱动方程。 5.检查自启动性。 6 .画出逻辑图。

同步计数器的设计

《数字电路与逻辑设计》

12/28

2

0

1

2

3

功能脚设置

接开关,设置为1

“ 1”

“ 1”

2

0

3

1

Vcc 14 13 12 11 10 9

8

Vcc 14 13 12 11 10 9 8

74LS00

74LS08

1 2 3 4 5 6 7地 4 5 6 7地

1

2

3

同步计数器的设计

《数字电路与逻辑设计》

22/28

接输出

1 0

2

0

3

1

Vcc 14 13 12 11 10 9

实验四

同步计数器的设计

信息科学系

邱泽敏 254434193@

实验目的 1. 熟悉J-K触发器的逻辑功能。

2. 掌握J-K触发器构成同步计数器。

同步计数器的设计

《数字电路与逻辑设计》

2/28

实验内容

1 .用 JK 触发器和门电路设计一个特殊 12 进制计数 器,要求使用权的排列为8421的非BCD码,即允许 使用1010及以后各码,其十进制数的状态转移图为:

4

同步计数器的设计

《数字电路与逻辑设计》

6/28

1.确定电路所需的触发器数目。 2.列出计数器的状态转换图。 3.根据状态转换图画出状态转换表。 4.根据状态转换表,写出J-K触发器的状态方程和驱动方程。 5.检查自启动性。 6 .画出逻辑图。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2020同步计数器的设计实验报告文档Contract Template同步计数器的设计实验报告文档前言语料:温馨提醒,报告一般是指适用于下级向上级机关汇报工作,反映情况,答复上级机关的询问。

按性质的不同,报告可划分为:综合报告和专题报告;按行文的直接目的不同,可将报告划分为:呈报性报告和呈转性报告。

体会指的是接触一件事、一篇文章、或者其他什么东西之后,对你接触的事物产生的一些内心的想法和自己的理解本文内容如下:【下载该文档后使用Word打开】同步计数器的设计实验报告篇一:实验六同步计数器的设计实验报告实验六同步计数器的设计学号:姓名:一、实验目的和要求1.熟悉JK触发器的逻辑功能。

2.掌握用JK触发器设计同步计数器。

二、实验仪器及器件三、实验预习1、复习时序逻辑电路设计方法。

⑴逻辑抽象,得出电路的状态转换图或状态转换表①分析给定的逻辑问题,确定输入变量、输出变量以及电路的状态数。

通常都是取原因(或条件)作为输入逻辑变量,取结果作输出逻辑变量。

②定义输入、输出逻辑状态和每个电路状态的含意,并将电路状态顺序编号。

③按照题意列出电路的状态转换表或画出电路的状态转换图。

通过以上步骤将给定的逻辑问题抽象成时序逻辑函数。

⑵状态化简①等价状态:在相同的输入下有相同的输出,并且转换到同一次态的两个状态。

②合并等价状态,使电路的状态数最少。

⑶状态分配①确定触发器的数目n。

因为n个触发器共有2n种状态组合,所以为获得时序电路所需的M个状态,必须取2n1<M2n②给每个电路状态规定对应的触发器状态组合。

⑷选定触发器类型,求出电路的状态方程、驱动方程和输出方程①根据器件的供应情况与系统中触发器种类尽量少的原则谨慎选择使用的触发器类型。

②根据状态转换图(或状态转换表)和选定的状态编码、触发器的类型,即可写出电路的状态方程、驱动方程和输出方程。

⑸根据得到的方程式画出逻辑图⑹检查设计的电路能否自启动①电路开始工作时通过预置数将电路设置成有效状态的一种。

②通过修改逻辑设计加以解决。

⑺设计步骤简图图3设计步骤简图2、按实验内容设计逻辑电路画出逻辑图。

设计思路详情见第六部分。

电路图如下:四、实验原理1.计数器的工作原理递增计数器----每来一个CP,触发器的组成状态按二进制代码规律增加。

递减计数器-----按二进制代码规律减少。

双向计数器-----可增可减,由控制端来决定。

2.集成J-K触发器74LS73⑴符号:图1J-K触发器符号⑵功能:表1J-K触发器功能表⑶状态转换图:图2J-K触发器状态转换图⑷特性方程:Qn1JQnKQn⑸注意事项:①在J-K触发器中,凡是要求接“1”的,一定要接高电平(例如5V),否则会出现错误的翻转。

③触发器的两个输出负载不能过分悬殊,否则会出现误翻。

④J-K触发器的清零输入端在工作时一定要接高电平或连接到实验箱的清零端子。

3.时序电路的设计步骤内容见实验预习。

五、实验内容1.用J-K触发器和门电路设计一个特殊的12进制计数器,其十进制的状态转换图为:图412进制计数器状态转换图六、实验设计及数据与处理⑴设计在12进制同步计数器中,输出的状态只由前一周期的状态决定,而与外来输入无关,因此目标电路为Moore型。

而数字电路只有0和1两种状态,因此目标电路要表达12种状态需要用4个变量Q1、Q2、Q3、Q4的16种组合中的12种。

现定义十进制数01~12的对应二进制数为输出状态,可得目标电路的状态转换表如下:表212进制同步计数器状态状态转换表本实验选择J-K触发器,根据状态转换表以及J-K触发器特性方程:Qn1JQnKQn得到目标电路方程如下:nnn输出方程:Y0nQ0n、Y1nQ1n、Y2nQ2、Y3Q3驱动方程:Q0一个CP发生一次变化,因此J0K01。

Q1每当Q0为1时,发生变化,因此nJ1K1Q0。

Q2在Q1Q0都为1以及12(即1100的时候)发生变化,因此J2=K2=Q1nQ0n+Q3nQ2nQ3在Q2Q1Q0都为1的时候,以及12的时候发生变化,因此J3=K3=Q0nQ1nQ2n+Q3nQ2n。

状态方程:Q0n1J0Q0nK0Q0nQ1n1J1Q1nK1Q1n篇二:计数器实验报告实验4计数器及其应用一、实验目的1、学习用集成触发器构成计数器的方法2、掌握中规模集成计数器的使用及功能测试方法二、实验原理计数器是一个用以实现计数功能的时序部件,它不仅可用来计脉冲数,还常用作数字系统的定时、分频和执行数字运算以及其它特定的逻辑功能。

计数器种类很多。

按构成计数器中的各触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器。

根据计数制的不同,分为二进制计数器,十进制计数器和任意进制计数器。

根据计数的增减趋势,又分为加法、减法和可逆计数器。

还有可预置数和可编程序功能计数器等等。

目前,无论是TTL还是CMOS集成电路,都有品种较齐全的中规模集成计数器。

使用者只要借助于器件手册提供的功能表和工作波形图以及引出端的排列,就能正确地运用这些器件。

1、中规模十进制计数器CC40192是同步十进制可逆计数器,具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如图5-9-1所示。

图5-9-1CC40192引脚排列及逻辑符号图中LD―置数端CPU―加计数端CPD―减计数端CO―非同步进位输出端BO―非同步借位输出端D0、D1、D2、D3―计数器输入端Q0、Q1、Q2、Q3―数据输出端CR―清除端CC40192的功能如表5-9-1,说明如下:表5-9-1当清除端CR为高电平“1”时,计数器直接清零;CR置低电平则执行其它功能。

当CR为低电平,置数端LD也为低电平时,数据直接从置数端D0、D1、D2、D3置入计数器。

当CR为低电平,LD为高电平时,执行计数功能。

执行加计数时,减计数端CPD接高电平,计数脉冲由CPU输入;在计数脉冲上升沿进行8421码十进制加法计数。

执行减计数时,加计数端CPU接高电平,计数脉冲由减计数端CPD输入,表5-9-2为8421码十进制加、减计数器的状态转换表。

加法计数表5-9-减计数2、计数器的级联使用一个十进制计数器只能表示0~9十个数,为了扩大计数器范围,常用多个十进制计数器级联使用。

同步计数器往往设有进位(或借位)输出端,故可选用其进位(或借位)输出信号驱动下一级计数器。

图5-9-2是由CC40192利用进位输出CO控制高一位的CPU 端构成的加数级联图。

图5-9-2CC40192级联电路3、实现任意进制计数(1)用复位法获得任意进制计数器假定已有N进制计数器,而需要得到一个M进制计数器时,只要M<N,用复位法使计数器计数到M时置“0”,即获得M进制计数器。

如图5-9-4所示为一个由CC40192十进制计数器接成的6进制计数器。

(2)利用预置功能获M进制计数器图5-9-5为用三个CC40192组成的421进制计数器。

外加的由与非门构成的锁存器可以克服器件计数速度的离散性,保证在反馈置“0”信号作用下计数器可靠置“0”。

图5-9-3六进制计数器图5-9-4是一个特殊12进制的计数器电路方案。

在数字钟里,对时位的计数序列是1、2、11,12、1、是12进制的,且无0数。

如图所示,当计数到13时,通过与非门产生一个复位信号,使CC40192(2)〔时十位〕直接置成0000,而CC40192(1),即时的个位直接置成0001,从而实现了5-5-1-12计数。

图5-9-4特殊12进制计数器三、实验设备与器件1、+5V直流电源2、双踪示波器3、连续脉冲源4、单次脉冲源5、逻辑电平开关6、逻辑电平显示器7、译码显示器8、CC40192×3CC4011(74LS00)CC4012(74LS20)四、实验内容1、测试CC40192同步十进制可逆计数器的逻辑功能计数脉冲由单次脉冲源提供,清除端CR、置数端LD、数据输入端D3、D2、D1、D0分别接逻辑开关,输出端Q3、Q2、Q1、Q0接实验设备的一个译码显示输入相应插口A、B、C、D;CO和BO接逻辑电平显示插口。

按表5-9-1逐项测试并判断该集成块的功能是否正常。

(1)清除令CR=1,其它输入为任意态,这时Q3Q2Q1Q0=0000,译码数字显示为0。

清除功能完成后,置CR=0(2)置数CR=0,CPU,CPD任意,数据输入端输入任意一组二进制数,令LD=0,观察计数译码显示输出,予置功能是否完成,此后置LD=1。

(3)加计数CR=0,LD=CPD=1,CPU接单次脉冲源。

清零后送入10个单次脉冲,观察译码数字显示是否按8421码十进制状态转换表进行;输出状态变化是否发生在CPU的上升沿。

(4)减计数CR=0,LD=CPU=1,CPD接单次脉冲源。

参照3)进行实验。

由内容可做实验得,计数端接单次脉冲源,清除端CR、置数端LD、数据输入端D3D2D1D0分别接逻辑开关,Q3Q2Q1Q0接实验设备的一个译码显示输入相应端口ABCD,CO、BO接逻辑电平显示插口,按表5-9-1测试,其结果与表5-9-1相一致。

2、图5-9-2所示,用两片CC40192组成两位十进制减法计数器,输入1Hz连续计数脉冲,进行由00―99递减计数,记录之。

由内容可做实验得,按图5-9-2连接电缆,其中(1)片CPCR1=0LD1=1D接连续脉冲源,两片Q3CPU1=1,BO1接2片CPD2CR2=0LD2=1CPU2=1BO2为借位端。

译码显示器,显示器数值由00开始递减。

3、将两位十进制减法计数器改为两位十进制加法计数器,实现由99―00累加计数,记录之。

由内容可做实验得,接图5-9-2电路,显示器由00开始递增4、设计一个数字钟移位60进制计数器并进行实验。

由内容可做实验得,将实验3中(2)片接法改为图5-9-3,即得到特殊12进制计数器5、按图5-9-4进行实验,记录之。

由内容可做实验得,按图5-9-4连接电路,得到特殊12进制计数器。

六、实验心得在整个设计的过程中,关键在于时序电路的连接及电路的细节设计上,连接时要特别注意分清各个管脚,要分析原理以及可行的原因,是整个电路可稳定工作。

从中我感觉到每个实验都是要反复实践,其过程可能相当繁琐,但总会有所收获的。

Q0分别接篇三:计数器设计实验报告实验报告实验:班级:姓名:学号:一、实验目的1.熟悉硬件描述语言软件的使用。

2.数序计数器的工作原理和逻辑功能。

3.掌握计数器的设计方法。

二、实验原理计数器是数字系统中使用最多的时序逻辑电路,其应用范围非常广泛。

计数器不仅能用于时钟脉冲技术,而且还用于定时、分频、产生节拍脉冲和脉冲序列以及进行数字运算等。

三、实验内容1.设计一个具有仅为输出信号的十进制加法计数器,要求有异步清零功能及同步使能控制端。

(1)代码libraryieee;useieee.std_logic_1164.all;useieee.std_logic_unsigned.all ;entitycnt10isport(clk,rst,en,load:instd_logic;data:instd_logic_vector( 3downto0);dout:outstd_logic_vector(3downto0);cout:outstd_ logic);endcnt10;architecturebehavofcnt10isbeginprocess(clk,rst,en,load)variableq:std_logic_vector(3downto0);beginifrst='0'thenq:=(others=>'0');elsifclk'eventandclk='1'the nifen='1'thenif(load='0')thenq:=data;elseifq<9then=""q:="(others=">'0' );endif;endif;endif;endif;ifq="1001"thencout<='1';elsecout<='0';endif;dout<=q;endprocess;endbehav;(2)编译完成(3)波形(4)网表RTL传输层映射2.设计一个具有进位输出信号的六进制加法计数器,要求具有异步清零功能及同步使能控制端。