一个简单的VHDL程序

第三章 VHDL程序设计1

五、VHDL与其它硬件描述语言的比较

行为级 VHDL: 具有较强的系统级抽象描述能力,适 合行为级和 RTL级的描述。设计者可不必 了解电路细节,所作工作较少,效率高。 但对综合器的要求高,不易控制底层电路 的生成。IEEE标准,支持广泛。 RTL: Register Translate Level

其中,端口模式: in: 输入型,此端口为只读型。 out: 输出型,只能在实体内部对其赋值。 inout:输入输出型,既可读也可赋值。 buffer: 缓冲型,与 out 相似,但可读。

21

out 和 buffer 的区别:

inout 和 buffer 的区别: Inout:是一个双向引脚,它在out引脚上加入一个 22 三态输出和输入缓冲器构成的

configuration 配置名 of 实体名 is

for

选配结构体名

end for ;

end 配置名;

32

例:一个与非门不同实现方式的配置如下:

library ieee; use ieee.std_logic_1164.all; configuration first of nand is for art1; entity nand is end for; port(a: in std_logic; end first; b: in std_logic; c: out std_logic); --configuration second of nand is end entity nand; -for art2 architecture art1 of nand is -end for; begin --end second; c<=not (a and b); end architecture art1; architecture art2 of nand is begin c<=‘1’ when (a=‘0’) and (b=‘0’) else ‘1’ when (a=‘0’) and (b=‘1’) else ‘1’ when (a=‘1’) and (b=‘0’) else ‘0’ when (a=‘1’) and (b=‘1’) else ‘0’; 33 end architecture art2;

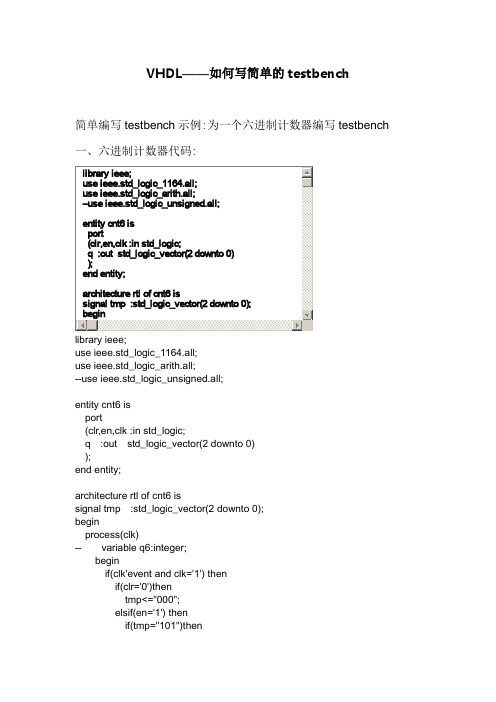

VHDL——如何写简单的testbench

use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;--use ieee.std_logic_unsigned.all;entity cnt6 isport(clr,en,clk :in std_logic;q :out std_logic_vector(2 downto 0) );end entity;architecture rtl of cnt6 issignal tmp :std_logic_vector(2 downto 0); beginprocess(clk)-- variable q6:integer;beginif(clk'event and clk='1') thenif(clr='0')thentmp<="000";elsif(en='1') thenif(tmp="101")thentmp<="000";elsetmp<=unsigned(tmp)+'1';end if;end if;end if;q<=tmp;-- qa<=q(0);-- qb<=q(1);-- qc<=q(2);end process;end rtl;二、六进制计数器testbench的代码signal en :std_logic:='0';signal clk :std_logic:='0';signal q :std_logic_vector(2 downto 0);constant clk_period :time :=20 ns;begininstant:cnt6 port map(clk=>clk,en=>en,clr=>clr,q=>q);clk_gen:processbeginwait for clk_period/2;clk<='1';wait for clk_period/2;clk<='0';end process;clr_gen:processbeginclr<='0';wait for 30 ns;clr<='1';wait;end process;en_gen:processbeginen<='0';wait for 50ns;en<='1';wait;end process;end rtl;--测试平台文件(testbench)的基本结构library ieee;use ieee.std_logic_1164.all;entity test_bench is --测试平台文件的空实体(不需要端口定义) end test_bench;architecture tb_behavior of test_bench iscomponent entity_under_test --被测试元件的声明port(list-of-ports-theri-types-and-modes);end component;begininstantiation:entity_under_test port map(port-associations);process() --产生时钟信号……end process;process() --产生激励源……end process;end tb_behavior;------------------------------------------------------------------- --简单计数程序源码library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_unsigned.all;entity sim_counter isport(clk :in std_logic;reset :in std_logic;count :out std_logic_vector(3 downto 0));end entity;architecture behavioral of sim_counter issignal temp :std_logic_vector(3 downto 0);beginprocess(clk,reset)beginif reset='1' thentemp<="0000";elsif clk'event and clk='1' thentemp<=temp+1;end if;end process;count<=temp;end behavioral;------------------------------------------------------------------- --简单计数程序,测试文件代码(testbench)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.numeric_std.all;entity counter_tb_vhd is --测试平台实体end counter_tb_vhd;architecture behavior of counter_tb_vhd is--被测试元件(DUT)的声明component sim_counterport(clk :in std_logic;reset :in std_logic;count :out std_logic_vector(3 downto 0));end component;--输入信号signal clk:std_logic:='0';signal reset :std_logic:='0';--输出信号signal count :std_logic_vector(3 downto 0);constant clk_period :time :=20 ns; --时钟周期的定义begindut:sim_counter port map(clk=>clk,reset=>reset,counter=>counter);clk_gen:processbeginclk='1';wait for clk_period/2;clk='0';wait for clk_period/2;end process;tb:process --激励信号beginwait for 20 ns;reset<='1';wait for 20 ns;reset<='0';wait for 200 ns;wait; --will wait forever;end process;end;--激励信号的产生方式--1.以一定的离散时间间隔产生激励信号的波形--2.基于实体的状态产生激励信号,也就是说基于实体的输出响应产生激励信号--两种常用的复位信号--1.周期性的激励信号,如时钟--2.时序变化的激励型号,如复位--eg.产生不对称时钟信号w_clk<='0' after period/4 when w_clk='1' else'1' after 3*period/4 when w_clk='0' else'0';--eg.产生堆成时钟信号,process语句clk_gen1:processconstan clk_period := 40 ns;beginclk='1';wait for clk_period/2;clk='0';wait for clk_period/2;end process;四、如果自己不想写这些testbench的这些固定格式,可以在quartus 里自动生成testbench文件的模板,然后往里面写信号就行了步骤:processing->start->start test bench template write这里需要注意的是要在仿真选项里选择一个仿真工具,然后才会生成testbench自动生成的testbench模板格式如下:-- Copyright (C) 1991-2008 Altera Corporation-- Your use of Altera Corporation's design tools, logic functions-- and other software and tools, and its AMPP partner logic-- functions, and any output files from any of the foregoing-- (including device programming or simulation files), and any-- associated documentation or information are expressly subject-- to the terms and conditions of the Altera Program License-- Subscription Agreement, Altera MegaCore Function License-- Agreement, or other applicable license agreement, including,-- without limitation, that your use is for the sole purpose of-- programming logic devices manufactured by Altera and sold by-- Altera or its authorized distributors. Please refer to the-- applicable agreement for further details.-- ***************************************************************************-- This file contains a Vhdl test bench template that is freely editable to-- suit user's needs .Comments are provided in each section to help the user -- fill out necessary details.-- ***************************************************************************-- Generated on "03/13/2011 20:05:04"-- Vhdl Test Bench template for design : cnt6---- Simulation tool : ModelSim (VHDL)--LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY cnt6_vhd_tst ISEND cnt6_vhd_tst;ARCHITECTURE cnt6_arch OF cnt6_vhd_tst IS-- constants-- signalsSIGNAL clk : STD_LOGIC;SIGNAL clr : STD_LOGIC;SIGNAL en : STD_LOGIC;SIGNAL q : STD_LOGIC_VECTOR(2 DOWNTO 0);COMPONENT cnt6PORT (clk : IN STD_LOGIC;clr : IN STD_LOGIC;en : IN STD_LOGIC;q : OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END COMPONENT;BEGINi1 : cnt6PORT MAP (-- list connections between master ports and signalsclk => clk,clr => clr,en => en,q => q);init : PROCESS-- variable declarationsBEGIN-- code that executes only onceWAIT;END PROCESS init;always : PROCESS-- optional sensitivity list-- ( )-- variable declarationsBEGIN-- code executes for every event on sensitivity list WAIT;END PROCESS always;END cnt6_arch;。

VHDL语言教程

VHDL语言教程VHDL是一种硬件描述语言,用于描述数字电路和系统,并进行硬件的设计和仿真。

它被广泛应用于数字电路设计、嵌入式系统开发和可编程逻辑控制器等领域。

本教程将介绍VHDL语言的基本概念和语法,帮助您了解和学习这门强大的硬件描述语言。

一、VHDL概述VHDL是Very High Speed Integrated Circuit Hardware Description Language的缩写,意为高速集成电路硬件描述语言。

它是一种硬件描述语言,用于描述数字电路和系统。

与传统的电路设计方法相比,使用VHDL可以更加方便、高效地进行电路设计和测试。

1.VHDL的起源和发展VHDL最早由美国国防部为了解决数字电路设计复杂、效率低下的问题而研发。

后来,VHDL成为了一种IEEE标准(IEEE1076)并被广泛应用于数字电路设计和仿真。

2.VHDL的优点VHDL具有以下几个优点:-高级抽象:VHDL提供了一种高级描述电路的方法,使得设计者能够更加方便地表达复杂的电路结构和行为。

-可重用性:VHDL支持模块化设计,使得设计者可以将电路的不同部分进行抽象和封装,提高了电路的可重用性。

-高效仿真:VHDL可以进行高效的电路仿真和测试,有助于验证电路设计的正确性和可靠性。

-灵活性:VHDL可以应用于各种不同类型和规模的电路设计,从小规模的数字逻辑电路到大规模的系统级设计。

二、VHDL语法和基本概念1.VHDL的结构VHDL程序由程序单元(unit)组成,程序单元是VHDL描述的最小单元。

程序单元包括实体(entity)、结构(architecture)、过程(process)和包(package)等。

2. 实体(entity)实体是VHDL描述电路模块的一个部分,包括输入输出端口、信号声明和实体标识符等。

3. 结构(architecture)结构描述了实体的具体电路结构和行为,包括组件声明、信号赋值和行为描述等。

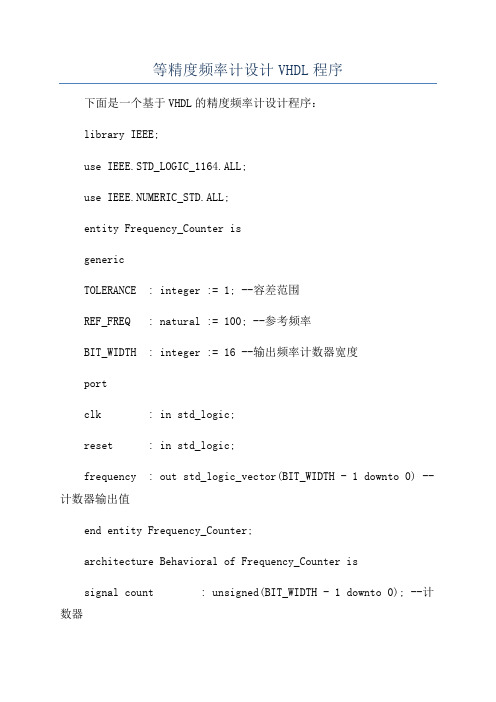

等精度频率计设计VHDL程序

等精度频率计设计VHDL程序下面是一个基于VHDL的精度频率计设计程序:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.NUMERIC_STD.ALL;entity Frequency_Counter isgenericTOLERANCE : integer := 1; --容差范围REF_FREQ : natural := 100; --参考频率BIT_WIDTH : integer := 16 --输出频率计数器宽度portclk : in std_logic;reset : in std_logic;frequency : out std_logic_vector(BIT_WIDTH - 1 downto 0) --计数器输出值end entity Frequency_Counter;architecture Behavioral of Frequency_Counter issignal count : unsigned(BIT_WIDTH - 1 downto 0); --计数器signal count_enable : std_logic; --计数使能信号signal ref_counter : unsigned(ceil(log2(real(REF_FREQ * CLK_FREQ) / TOLERANCE)) - 1 downto 0); --参考计数器beginprocess(clk, reset)beginif reset = '1' thencount <= (others => '0'); --复位为0count_enable <= '0';ref_counter <= (others => '0');elsif rising_edge(clk) thencount <= count + 1; --计数信号递增end if;if ref_counter = REF_FREQ - 1 thenelseref_counter <= ref_counter + 1; --参考计数器递增end if;end if;end process;process(clk, reset)beginif reset = '1' thencount_enable <= '0';elsif rising_edge(clk) thencount_enable <= '1'; --参考频率达到后启用计数信号elsecount_enable <= '0';end if;end if;end process;frequency <= std_logic_vector(count);end architecture Behavioral;在此设计中,我们定义了一个Frequency_Counter实体,它有几个泛型参数,包括CLK_FREQ(输入时钟频率),TOLERANCE(容差范围),REF_FREQ(参考频率)和BIT_WIDTH(输出频率计数器的宽度)。

vhdl语言100例程序

vhdl语言100例程序以下是100个关于VHDL语言的程序示例:1. 用VHDL编写一个计数器模块2. 用VHDL编写一个SR-Latch模块3. 用VHDL编写一个JK-Flip Flop模块4. 用VHDL编写一个D-Flip Flop模块5. 用VHDL编写一个T-Flip Flop模块6. 用VHDL编写一个复位计数器模块7. 用VHDL编写一个移位寄存器模块8. 用VHDL编写一个状态机模块9. 用VHDL编写一个MUX模块10. 用VHDL编写一个DeMUX模块11. 用VHDL编写一个加法器模块12. 用VHDL编写一个减法器模块13. 用VHDL编写一个乘法器模块14. 用VHDL编写一个除法器模块15. 用VHDL编写一个比较器模块16. 用VHDL编写一个位逻辑模块17. 用VHDL编写一个字逻辑模块18. 用VHDL编写一个数据选择器模块19. 用VHDL编写一个FIFO队列模块20. 用VHDL编写一个LIFO栈模块21. 用VHDL编写一个流水线模块22. 用VHDL编写一个中断控制器模块23. 用VHDL编写一个时钟分频器模块24. 用VHDL编写一个IO控制器模块25. 用VHDL编写一个SPI通信控制器模块26. 用VHDL编写一个I2C通信控制器模块27. 用VHDL编写一个UART通信控制器模块28. 用VHDL编写一个哈希函数模块29. 用VHDL编写一个随机数产生器模块30. 用VHDL编写一个CRC校验器模块31. 用VHDL编写一个AES加密算法模块32. 用VHDL编写一个DES加密算法模块33. 用VHDL编写一个SHA加密算法模块34. 用VHDL编写一个MD5加密算法模块35. 用VHDL编写一个RSA加密算法模块36. 用VHDL编写一个卷积滤波器模块37. 用VHDL编写一个峰值检测器模块38. 用VHDL编写一个平滑滤波器模块39. 用VHDL编写一个中值滤波器模块40. 用VHDL编写一个微处理器模块41. 用VHDL编写一个信号发生器模块42. 用VHDL编写一个信号采集器模块43. 用VHDL编写一个频率计算器模块44. 用VHDL编写一个相位计算器模块45. 用VHDL编写一个时序分析器模块46. 用VHDL编写一个正弦波产生器模块47. 用VHDL编写一个余弦波产生器模块48. 用VHDL编写一个数字滤波器模块49. 用VHDL编写一个数字信号处理器模块50. 用VHDL编写一个数字识别模块51. 用VHDL编写一个自动售货机模块52. 用VHDL编写一个二进制加法器模块53. 用VHDL编写一个二进制减法器模块54. 用VHDL编写一个二进制乘法器模块55. 用VHDL编写一个二进制除法器模块56. 用VHDL编写一个自然对数模块57. 用VHDL编写一个指数函数模块58. 用VHDL编写一个三角函数模块59. 用VHDL编写一个高斯滤波器模块60. 用VHDL编写一个激光传感器模块61. 用VHDL编写一个超声波传感器模块62. 用VHDL编写一个光电传感器模块63. 用VHDL编写一个温度传感器模块64. 用VHDL编写一个气压传感器模块65. 用VHDL编写一个陀螺仪模块67. 用VHDL编写一个电流传感器模块68. 用VHDL编写一个电容传感器模块69. 用VHDL编写一个磁场传感器模块70. 用VHDL编写一个通信电缆模块71. 用VHDL编写一个电源控制器模块72. 用VHDL编写一个电机控制器模块73. 用VHDL编写一个汽车控制器模块74. 用VHDL编写一个飞机控制器模块75. 用VHDL编写一个摄像头模块76. 用VHDL编写一个音频控制器模块77. 用VHDL编写一个扬声器控制器模块78. 用VHDL编写一个拨号器模块79. 用VHDL编写一个振动控制器模块80. 用VHDL编写一个压力控制器模块81. 用VHDL编写一个过滤器模块82. 用VHDL编写一个微波发射模块84. 用VHDL编写一个智能电表模块85. 用VHDL编写一个闹钟模块86. 用VHDL编写一个计时器模块87. 用VHDL编写一个时间戳模块88. 用VHDL编写一个脉冲宽度模块89. 用VHDL编写一个电路仿真模块90. 用VHDL编写一个电路控制模块91. 用VHDL编写一个电路测试模块92. 用VHDL编写一个电路优化模块93. 用VHDL编写一个电路布局模块94. 用VHDL编写一个电路验证模块95. 用VHDL编写一个数字信号发生器模块96. 用VHDL编写一个数字信号反演器模块97. 用VHDL编写一个数字信号滤波器模块98. 用VHDL编写一个数字信号加速器模块99. 用VHDL编写一个数字信号降噪器模块100. 用VHDL编写一个数字信号解调器模块VHDL语言是一种硬件描述语言,它用于描述数字电路和系统。

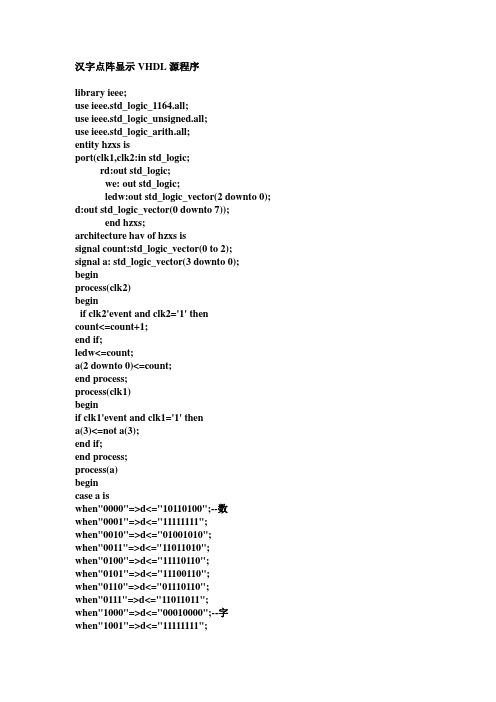

汉字点阵显示VHDL源程序

汉字点阵显示VHDL源程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity hzxs isport(clk1,clk2:in std_logic;rd:out std_logic;we: out std_logic;ledw:out std_logic_vector(2 downto 0); d:out std_logic_vector(0 downto 7));end hzxs;architecture hav of hzxs issignal count:std_logic_vector(0 to 2);signal a: std_logic_vector(3 downto 0);beginprocess(clk2)beginif clk2'event and clk2='1' thencount<=count+1;end if;ledw<=count;a(2 downto 0)<=count;end process;process(clk1)beginif clk1'event and clk1='1' thena(3)<=not a(3);end if;end process;process(a)begincase a iswhen"0000"=>d<="10110100";--数when"0001"=>d<="11111111"; when"0010"=>d<="01001010"; when"0011"=>d<="11011010"; when"0100"=>d<="11110110"; when"0101"=>d<="11100110"; when"0110"=>d<="01110110"; when"0111"=>d<="11011011"; when"1000"=>d<="00010000";--字when"1001"=>d<="11111111";when"1010"=>d<="11111101"; when"1011"=>d<="00001100"; when"1100"=>d<="11111111"; when"1101"=>d<="00010000"; when"1110"=>d<="00010000"; when"1111"=>d<="00001100";when others=>d<="00000000";end case;end process;rd<='1';we<='0';end hav;数字抢答器VHDL源程序1)抢答器QDQlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity qdq isport(clr:in std_logic;a,b,c,d:in std_logic;an,bn,cn,dn:out std_logic);end qdq;architecture hav of qdq issignal ss:std_logic_vector(0 to 3);beginss<=a&b&c&d;process(clr,a,b,c,d)beginif clr='1' thencase ss iswhen "1000"=>an<='1';bn<='0';cn<='0';dn<='0'; when "0100"=>an<='0';bn<='1';cn<='0';dn<='0'; when "0010"=>an<='0';bn<='0';cn<='1';dn<='0'; when "0001"=>an<='0';bn<='0';cn<='0';dn<='1'; when others=>an<='0';bn<='0';cn<='0';dn<='0'; end case;elsif clr='0' thenan<='0';bn<='0';cn<='0';dn<='0';end if;end process;end hav;2)计分器JFQlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity jfq isport(en1:in std_logic;clk3:in std_logic;bs:out std_logic_vector(3 downto 0);ss:out std_logic_vector(3 downto 0);gs:out std_logic_vector(3 downto 0);add:in std_logic;dec:in std_logic);end jfq;architecture hav of jfq isbeginprocess(clk3,en1,add,dec)variable ssw:std_logic_vector(3 downto 0); variable bsw:std_logic_vector(3 downto 0); beginbsw:="0001";if clk3='1' and clk3'event thenif en1='1' thenif add='1' thenif ssw="1001" thenbsw:=bsw+1;ssw:="0000";elsessw:=ssw+1;end if;elsif dec='1' thenif ssw="1111" thenbsw:=bsw-1;ssw:="1001";elsessw:=ssw-1;end if;end if;end if;end if;ss<=ssw;bs<=bsw;gs<="0000";end process;end hav;3) 选择器XZQlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity xzq isport( a1,b1:in std_logic;abw:in std_logic_vector(0 to 3);asw:in std_logic_vector(0 to 3);agw:in std_logic_vector(0 to 3);bbw:in std_logic_vector(0 to 3);bsw:in std_logic_vector(0 to 3);bgw:in std_logic_vector(0 to 3);obw:out std_logic_vector(0 to 3);osw:out std_logic_vector(0 to 3);ogw:out std_logic_vector(0 to 3)); end xzq;architecture hav of xzq isbeginprocess(a1,b1)beginif a1='1' and b1='0' thenobw<=abw;osw<=asw;ogw<=agw;elsif a1='0' and b1='1' thenobw<=bbw;osw<=bsw;ogw<=bgw;end if;end process;end hav;4)译码器YMQlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity ymq isport( clk2:in std_logic;bw:in std_logic_vector(3 downto 0);sw:in std_logic_vector(3 downto 0);gw:in std_logic_vector(3 downto 0);y:out std_logic_vector(7 downto 0);ledw:out std_logic_vector(2 downto 0)); end ymq;architecture hav of ymq issignal knum:std_logic_vector(3 downto 0); signal count:std_logic_vector(2 downto 0); beginprocess(clk2)beginif clk2'event and clk2='1' thenif count<2 thencount<=count+1;elsecount<="000";end if;end if;end process;ledw<=count;knum<=gw when count=0 elsesw when count=1 elsebw when count=2 ;y<="00111111" when knum="0000" else "00000110" when knum="0001" else"01011011" when knum="0010" else"01001111" when knum="0011" else"01100110" when knum="0100" else"01101101" when knum="0101" else"01111101" when knum="0110" else"00000111" when knum="0111" else"01111111" when knum="1000" else"01101111" when knum="1001" else"00000000" ;end hav;。

vhdl 程序的基本结构 vhdl程序一般由5个部分组成

块语句

块标号:BLOCK[保护表达式] [类属子句;] [端口子句;] [块说明部分;] BEGIN <块语句部分;> END BLOCK 块标号;

类属子句用于参数的定义;端口子句用于信号的定义; 块说明部分对该块要用到的信号、常数、元件和子程序 等进行说明;块语句部分对该块的功能进行描述,块语 句部分的语句是并行执行的,和书写顺序无关。

IEEE: IEEE认可的标准库 std_logic_1164:定义了 std_logic, std_logic_vector, std_ulogic, std_ulogic_vector 等数据类型

VHDL 程序的基本结构

VHDL程序一般由5个部分组成: Library(库) Package(程序包)

CONFIGURATION small_count OF counter IS FOR count_255 END FOR; END small_count; CONFIGURATION big_count OF counter IS FOR count_64K END FOR; END big_count;

Library(程序库) Package(程序包)

Entity(实体) Architecture(构造体) Configuration(配置)

库和程序包

库 :存放已编译过的实体、构造体、 程序包和配置 程序包:由一组对外可见的信号、常量、 数据类型、子程序、属性等组成 的程序集合

库和程序包的使用

子程序调用语句 过程名(参数表);

子程序调用语句若位于 “构造体” 或 “块语句” 中,它就是并发语句; 若位于 “进程语句” 或 另一个“子 程序”中,它就是顺序语句;

1用VHDL设计的一位二进制全加器的示例程序

1用VHDL设计的一位二进制全加器的示例程序VHDL(Very High-Speed Integrated Circuit Hardware Description Language)是一种硬件编程语言,它使用结构化的方法来描述数字系统中的电路。

在设计一位二进制全加器之前,我们需要了解一下什么是二进制全加器。

二进制全加器是一种逻辑电路,用于将两个二进制位以及一个进位输入相加,并生成一个和输出以及一个进位输出。

以下是一个使用VHDL编写的一位二进制全加器的示例程序:```vhdl-- Entity声明entity full_adder isportA, B, Cin : in std_logic; -- 输入端口,分别对应两个二进制位和进位Sum, Cout : out std_logic -- 输出端口,分别对应和和进位end full_adder;-- Architecture实现architecture behavior of full_adder isbeginprocess(A, B, Cin)variable temp_sum : std_logic;begintemp_sum := (A xor B) xor Cin; -- 计算和值Sum <= temp_sum; -- 输出和值Cout <= (A and B) or (Cin and (A xor B)); -- 计算进位end process;end behavior;```该程序定义了一个名为`full_adder`的实体,它有3个输入端口(A,B和Cin)和2个输出端口(Sum和Cout)。

`std_logic`是VHDL中的一种数据类型,用于表示逻辑电平。

在架构部分,程序使用一个过程来计算和值(temp_sum)和进位(Cout)。

和值的计算通过使用异或(`xor`)操作符来实现,进位的计算则使用与(`and`)和或(`or`)逻辑操作符的组合来实现。

用VHDL语言编写的数字钟程序

永州职业技术学院课程设计课程名称:EDA技术实用教程题目:基于FPGA的数字钟设计系、专业:电子技术系应用电子年级、班级:07级电子大专学生姓名:**指导老师:***时间:2008年12月目录一、系统设计………………………………………………………..1.1设计要求……………………………………………………1.1.1任务………………………………………………..1.1.2要求……………………………………………….1.1.3题目分析…………………………………………二.方案论证与比较…………………………………2.1方案一…………………………………………2.2 方案二…………………………………………2.3 方案三…………………………………………三、设计思路……………………………………………………3.1硬件模块………………………………………………3.2软件模块………………………………………………….四、调试情况………………………………………………….五、系统调试…………………………………………………六、心得体会……………………………………………………... 附:参考文献……………………………………………………..用VHDL语言编写的数字钟程序摘要:本设计要求一个12进制或24进制的具有时、分、秒计时功能的数字钟,并要求能进行时、分、秒调整,每逢时有报时功能。

数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。

本设计基于FPGA芯片的数字钟的设计,通过多功能数字钟的设计思路,详细叙述了整个系统的硬件、软件实现过程,实现了时间的显示和修改功能、报时功能等,并尽可能的减少误差,使得系统可以达到实际数字钟的允许误差范围内。

关键词:FBGA、数码管、按键一、系统设计1.1 设计要求1.1.1 任务设计并制作一个数字钟,通过设计,掌握电子设计的一般思路,学习电子设计的一般方法。

(VHDL)8位二进制乘法电路程序

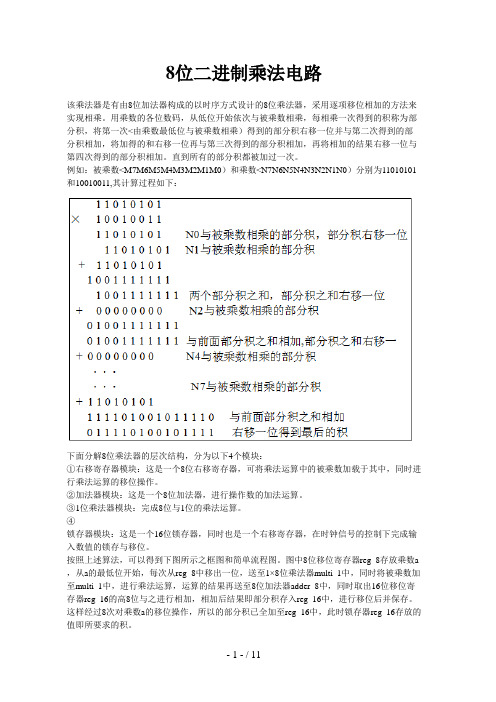

8位二进制乘法电路该乘法器是有由8位加法器构成的以时序方式设计的8位乘法器,采用逐项移位相加的方法来实现相乘。

用乘数的各位数码,从低位开始依次与被乘数相乘,每相乘一次得到的积称为部分积,将第一次<由乘数最低位与被乘数相乘)得到的部分积右移一位并与第二次得到的部分积相加,将加得的和右移一位再与第三次得到的部分积相加,再将相加的结果右移一位与第四次得到的部分积相加。

直到所有的部分积都被加过一次。

例如:被乘数<M7M6M5M4M3M2M1M0)和乘数<N7N6N5N4N3N2N1N0)分别为11010101和10010011,其计算过程如下:下面分解8位乘法器的层次结构,分为以下4个模块:①右移寄存器模块:这是一个8位右移寄存器,可将乘法运算中的被乘数加载于其中,同时进行乘法运算的移位操作。

②加法器模块:这是一个8位加法器,进行操作数的加法运算。

③1位乘法器模块:完成8位与1位的乘法运算。

④锁存器模块:这是一个16位锁存器,同时也是一个右移寄存器,在时钟信号的控制下完成输入数值的锁存与移位。

按照上述算法,可以得到下图所示之框图和简单流程图。

图中8位移位寄存器reg_8存放乘数a ,从a的最低位开始,每次从reg_8中移出一位,送至1×8位乘法器multi_1中,同时将被乘数加至multi_1中,进行乘法运算,运算的结果再送至8位加法器adder_8中,同时取出16位移位寄存器reg_16的高8位与之进行相加,相加后结果即部分积存入reg_16中,进行移位后并保存。

这样经过8次对乘数a的移位操作,所以的部分积已全加至reg_16中,此时锁存器reg_16存放的值即所要求的积。

<A)电路框图<B)简单流程图8位移位寄存器是在时钟<r8_clk'event and r8_clk='1')信号作用下,当r8_load='1'时,将8位乘数加载进入;而当r8_load='0'时,对数据进行移位操作,同时定义一个信号reg8用来装载新数据及移位后的操作数,完成这些操作后,寄存器的最低位reg8(0>传送给r8_out输出。

VHDL语法简单总结

VHDL语法(yǔfǎ)简单总结VHDL语法简单(jiǎndān)总结VHDL语法(yǔfǎ)简单总结一个(yī ɡè)VHDL程序代码包含实体(shítǐ)(entity)、结构(jiégòu)体(architecture)、配置(pèizhì)(configuration)、程序包(package)、库(library)等。

一、数据类型1.用户自定义数据类型使用关键字TYPE,例如:TYPE my_integer IS RANGE -32 TO 32;–用户自定义的整数类型的子集TYPE student_grade IS RANGE 0 TO 100;–用户自定义的自然数类型的子集TYPE state IS (idle, forward, backward, stop);–枚举数据类型,常用于有限状态机的状态定义一般来说,枚举类型的数据自动按顺序依次编码。

2.子类型在原有已定义数据类型(lèixíng)上加一些约束条件,可以定义(dìngyì)该数据类型的子类型。

VHDL不允许不同类型的数据直接进行操作运算,而某个数据类型的子类型则可以和原有类型数据直接进行操作运算。

子类型定义使用(shǐyòng)SUBTYPE关键字。

3.数组(ARRAY)ARRAY是将相同数据类型的数据集合在一起(yīqǐ)形成的一种新的数据类型。

TYPE type_name IS ARRAY (specification) OF data_type;–定义新的数组类型(lèixíng)语法结构SIGNAL signal_name: type_name [:=initial_value];–使用新的数组类型对SIGNAL,CONSTANT, VARIABLE进行声明例如:TYPE delay_lines IS ARRAY (L-2 DOWNTO 0) OF SIGNED (W_IN-1 DOWNTO 0);–滤波器输入延迟链类型定义TYPE coeffs IS ARRAY (L-1 DOWNTO 0) OF SIGNED (W_COEF-1 DOWNTO 0);–滤波器系数(xìshù)类型定义SIGNAL delay_regs: delay_lines; –信号延迟(yánchí)寄存器声明CONSTANT coef: coeffs := ( ); –常量(chángliàng)系数声明并赋初值4.端口数组在定义电路的输入/输出端口时,有时需把端口定义为矢量阵列,而在ENTITY中不允许使用TYPE进行类型定义,所以(suǒyǐ)必须在包集(PACKAGE)中根据端口的具体信号特征建立用户自定义的数据类型,该数据类型可以供包括ENTITY在内的整个设计使用。

VHDL语言程序及其详细注释

end generate; 循环描述结束 end;结构体结束

8位多路选择器

entity Mux8 is 定义实体,实体名为 generic (TPD : TIME :=1ns); 类属参数说明 port (A, B : in BIT_VECTOR(7 downto 0);端口说明,输入输出及其类型 sel : in BIT := ‘0’; Y : out BIT_VECTOR (7 downto 0));

port (x,y,cin: in BIT; cout,sum: out BIT); end component;结束声明,COMPONENT,END COMPONENT之间是元件引脚的定义 signal c: BIT_VECTOR(7downto 0);定义信号

结构体说明部分

Begin

结构体开始 for generate是为了同一类关系的循环描述,是一种简化写法

end;实体说明结束 architecture Behave of DFFClr is实体的结构体名称及其所属关系 signal Qi : BIT;定义信号 begin QB <= not Qi ; Q <= Qi 结构体开始 信号赋值 process (CLR, CLK) begin 定义进程并且开始进程

end;实体说明结束 architecture Behave of Mux8 is 实体的结构体名称及其所属关系 begin结构体开始

Y <=A after TDP when sel = ‘1’ else B after TDP; 延时 赋值 end;实体说明结束

VHDL编写IIC程序

如题所示,本文是使用VHDL语言编写的IIC 总线的24C02的读写例程,程序加了中文注释便于想我一样的初学者理解,写使用的写一个字节,读使用的随机读,具体参考24c02的手册library IEEE;use IEEE.std_logic_1164.all;use ;use ;entity iic_com isport(clk: in STD_LOGIC;rst_n: in STD_LOGIC;sw1_en: in STD_LOGIC; --读使能sw2_en: in STD_LOGIC; --写使能scl: out STD_LOGIC;sda: inout STD_LOGIC;dis_data: out STD_LOGIC_VECTOR (7 downto 0));end entity iic_com;architecture iic_communication of iic_com issignal sw_state: STD_LOGIC;signal cnt_delay: STD_LOGIC_VECTOR (8 downto 0);signal scl_pos: STD_LOGIC;signal scl_hig: STD_LOGIC;signal scl_neg: STD_LOGIC;signal scl_low: STD_LOGIC;signal db_r: STD_LOGIC_VECTOR (7 downto 0);signal read_data: STD_LOGIC_VECTOR (7 downto 0);signal sda_r: STD_LOGIC;signal sda_in: STD_LOGIC;signal sda_link: STD_LOGIC;signal num: STD_LOGIC_VECTOR (3 downto 0);constant DEVICE_READ: STD_LOGIC_VECTOR (7 downto 0) := "10100001";--器件地址读constant DEVICE_WRITE: STD_LOGIC_VECTOR (7 downto 0) := "10100000";--器件地址写constant WRITE_DATA: STD_LOGIC_VECTOR (7 downto 0) := "11000011"; --写入的数据constant BYTE_ADDR: STD_LOGIC_VECTOR (7 downto 0) := "00000011";--写入的地址type state is (IDLE,START1,ADD1,ACK1,ADD2,ACK2,START2,ADD3,ACK3,DATA,ACK4,STOP1,STOP2);signal cstate: state;signal temp_sw1,temp_sw2:Std_LOGIC;begin----------------------process(clk,rst_n)beginif (rst_n = '0') thensw_state <= '0';elsif (clk'event AND clk = '1') thenif(sw1_en = '1') thensw_state <= '0';elsif (sw2_en = '1') thensw_state <= '1';end if;end if;end process;----------------------process(clk,rst_n)beginif (rst_n = '0') thencnt_delay <= '0' & x"00";elsif (clk'event AND clk = '1') thenif(cnt_delay = 10#499#) then --相当于500分频,得到100K时钟cnt_delay <= '0' & x"00";elsecnt_delay <= cnt_delay+'1';end if;end if;end process;scl_pos <= '1' when (cnt_delay = 10#499#) else'0'; --IIC时钟上升沿scl_hig <= '1' when (cnt_delay = 10#124#) else'0'; --IIC时钟高电平scl_neg <= '1' when (cnt_delay = 10#249#) else'0'; --IIC时钟下降沿scl_low <= '1' when (cnt_delay = 10#374#) else'0'; --IIC时钟低电平process(clk,rst_n)beginif (rst_n = '0') thenscl <= '0';elsif (clk'event AND clk = '1') thenif(scl_pos = '1') thenscl <= '1';elsif(scl_neg = '1') thenscl <= '0';end if;end if;end process;----------------------process(clk,rst_n)beginif (rst_n = '0') thencstate <= IDLE;sda_r <= '1';sda_link <= '0';num <= x"0";read_data <= x"00";elsif (clk'event AND clk = '1') thencase cstate iswhen IDLE =>sda_link <= '1';sda_r <= '1';if (sw1_en/=temp_sw1)or(sw2_en/=temp_sw2) then --当sw1_en 和sw2_en 变化一次,只读或写一次,防止屡次读写temp_sw1<=sw1_en;temp_sw2<=sw2_en;if ((sw1_en = '1') OR (sw2_en = '1')) thendb_r <= DEVICE_WRITE;cstate <= START1;elsecstate <= IDLE;end if;elsecstate <= IDLE;end if;when START1 =>if (scl_hig = '1') then --起始位sda_link <= '1';--数据线由sda_r控制sda_r <= '0';cstate <= ADD1;num <= x"0";elsecstate <= START1;end if;when ADD1 => --器件地址&'0'if (scl_low = '1') thenif (num = x"8") thennum <= x"0";sda_r <= '1';sda_link <= '0';--数据线设为高阻态,允许输入cstate <= ACK1;elsecstate <= ADD1;num <= num+'1';case num iswhen x"0" => sda_r <= db_r(7);when x"1" => sda_r <= db_r(6);when x"2" => sda_r <= db_r(5);when x"3" => sda_r <= db_r(4);when x"4" => sda_r <= db_r(3);when x"5" => sda_r <= db_r(2);when x"6" => sda_r <= db_r(1);when x"7" => sda_r <= db_r(0);when others => NULL;end case;end if;elsecstate <= ADD1;end if;when ACK1 => --应答if (scl_neg = '1') thencstate <= ADD2;db_r <= BYTE_ADDR;elsecstate <= ACK1;end if;when ADD2 => --要写入数据或读取数据的地址if (scl_low = '1') thenif (num = x"8") thennum <= x"0";sda_r <= '1';sda_link <= '0';--数据线设为高阻态,允许输入cstate <= ACK2;elsesda_link <= '1';--数据线由sda_r控制num <= num+'1';cstate <= ADD2;case num iswhen x"0" => sda_r <= db_r(7);when x"1" => sda_r <= db_r(6);when x"2" => sda_r <= db_r(5);when x"3" => sda_r <= db_r(4);when x"4" => sda_r <= db_r(3);when x"5" => sda_r <= db_r(2);when x"7" => sda_r <= db_r(0);when others => NULL;end case;end if;elsecstate <= ADD2;end if;when ACK2 => --应答if (scl_neg = '1') thenif (sw_state = '0') then --如果写入数据cstate <= DATA;db_r <= WRITE_DATA;elsif (sw_state = '1') then --如果读取数据db_r <= DEVICE_READ;cstate <= START2;end if;elsecstate <= ACK2;end if;when START2 => --起始位if (scl_low = '1') thensda_link <= '1';sda_r <= '1';cstate <= START2;elsif (scl_hig = '1') thensda_r <= '0';cstate <= ADD3;elsecstate <= START2;end if;when ADD3 => --器件地址&'1' if (scl_low ='1') thenif (num = x"8") thennum <= x"0";sda_r <= '1';sda_link <= '0';cstate <= ACK3;l11<='0';elsenum <= num+'1';cstate <= ADD3;case num iswhen x"0" => sda_r <= db_r(7);when x"2" => sda_r <= db_r(5);when x"3" => sda_r <= db_r(4);when x"4" => sda_r <= db_r(3);when x"5" => sda_r <= db_r(2);when x"6" => sda_r <= db_r(1);when x"7" => sda_r <= db_r(0);when others => NULL;end case;end if;elsecstate <= ADD3;end if;when ACK3 => --应答if (scl_neg = '1') thencstate <= DATA;sda_link <= '0';elsecstate <= ACK3;end if;when DATA =>if (sw_state = '1') then --如果是读数据if (num <= x"7") thencstate <= DATA;if (scl_hig = '1') thennum <= num+'1';case num iswhen x"0" => read_data(7) <= sda_in;when x"1" => read_data(6) <= sda_in;when x"2" => read_data(5) <= sda_in;when x"3" => read_data(4) <= sda_in;when x"4" => read_data(3) <= sda_in;when x"5" => read_data(2) <= sda_in;when x"6" => read_data(1) <= sda_in;when x"7" => read_data(0) <= sda_in;when others => NULL;end case;end if;elsif ((scl_low = '1') AND (num = x"8")) thennum <= x"0";cstate <= ACK4;elsecstate <= DATA;end if;elsif (sw_state = '0') then --如果是写数据sda_link <= '1';if (num <= x"7") thencstate <= DATA;if (scl_low = '1') thensda_link <= '1';num <= num+'1';case num iswhen x"0" => sda_r <= db_r(7);when x"1" => sda_r <= db_r(6);when x"2" => sda_r <= db_r(5);when x"3" => sda_r <= db_r(4);when x"4" => sda_r <= db_r(3);when x"5" => sda_r <= db_r(2);when x"6" => sda_r <= db_r(1);when x"7" => sda_r <= db_r(0);when others => NULL;end case;end if;elsif ((scl_Low = '1') AND (num = x"8")) thennum <= x"0";sda_r <= '1';sda_link <= '0';cstate <= ACK4;elsecstate <= DATA;end if;end if;when ACK4 => --应答if (scl_neg = '1') thencstate <= STOP1;elsecstate <= ACK4;end if;when STOP1 => --停止位if(scl_low = '1') thensda_link <= '1';sda_r <= '0';cstate <= STOP1;elsif (scl_hig = '1') thensda_r <= '1';cstate <= STOP2;elsecstate <= STOP1;end if;when STOP2 =>if (scl_low = '1') thensda_r <= '1';elsecstate <= IDLE;end if;when others => cstate <= IDLE;end case;end if;end process;process (sda, sda_link)beginif(sda_link = '1') thensda <= sda_r;elsesda <= 'Z';end if;end process;sda_in <= sda;--sda_in <= 'z';--sda <= sda_r when (sda_link = '1') else-- "z";dis_data <= read_data;end architecture iic_communication;。

乐曲硬件演奏电路的VHDL设计报告+程序

一、设计题目:乐曲硬件演奏电路的VHDL设计二、设计目标:了解一般乐曲演奏电路设计设计方法,学习VHDL语言,熟悉EDA设计软件QuartusII和MAX+plusⅡ,加强独立完成电子设计的能力。

(1)能够播放“梁祝”乐曲。

(2)能够通过LED显示音阶。

(3)(选作)具有“播放/停止”功能,并在此基础上实现“按键演奏”的电子琴功能。

主芯片型号为FLEX10K10LC84-4三、实验电路的工作原理:(演奏电路逻辑图)组成乐曲的每个音符的发音频率值及其持续的时间是乐曲能够连续演奏所需的两个基本要素,设计演奏电路的关键就是获得这两个要素所对应的数值以及通过纯硬件的手段来利用这些数值实现所希望乐曲的演奏效果。

演奏电路逻辑图有三部分:音乐节拍和音调发生器、简谱码对应的分频预置数查表电路、数控分频与演奏发生器。

演奏电路逻辑图:四、设计内容:1.完成程序的编辑工作。

2.将音乐数据制作成LMP_ROM文件.3.将程序加载到MAX+plusⅡ中进行编译、仿真,并保存仿真结果。

4.到实验室进行下载验证。

引脚进行锁定,然后下载到实验芯片中观察实验结果。

五、仿真结果:1.音乐节拍和音调发生器(NoteTabs.VHD)notetabs模块中设置了一个8位二进制计数器(计数最大值138),作为音符数据ROM的地址发生器。

这个计数器的计数频率选为4Hz,即每一个计数值的停留时间为0.25秒,恰为当全音符设为1秒时,四四拍的4分音符持续时间。

随着notetabs模块中的计数器按4Hz的时钟速率作为加法计数时,即随地址值递增时,音符数据ROM中的音符数据将从ROM中通过ToneIndex[3..0]端口输向ToneTaba模块,“梁祝”乐曲就开始连续自然的演奏起来了。

Notetabs模块仿真图:2.简谱码对应的分频预置数查表电路(T oneTaba.VHD)音符的持续时间需根据乐曲的速度及每个音符的节拍数来确定,tonetaba模块的功能首先是为speakera提供决定所发音符的预置数,而此数在speakera输入口停留的时间即为此音符的节拍值。

《VHDL语言及应用》Quartus II 软件使用与 VHDL 基础程序设计实验

《VHDL语言及应用》Quartus II 软件使用与 VHDL 基础程序设计实验一、实验目的:(1)掌握 Quartus II 开发软件的基本使用,包括新建工程,代码编写与添加,工程编译与综合,建立波形仿真等步骤;(2)通过与门电路(AndGate)功能的编写,掌握 VHDL 程序的基本设计结构。

二、实验设备及软件:电脑,Quartus II 软件四、实验过程1.新建工程打开软件,File--New--New Quartus II Projec然后点击OK, 新建工程的第一个界面直接点击 Next, 界面第一行要在FPGA工程文件夹路径后再加上单独工程的名字,界面第二,第三行分别与工程目录名设定相同,因此都写AndGate。

选择实验需要的器件型号。

2.新建与添加代码文件对.vhd文件先进行编辑,编辑之后才可进行保存,点击左上方保存按钮,将代码文件保存至工程目录中,文件名为 AndGate。

第1行,第2行:库、程序包的调用说明。

第4行:ENTITY实体名IS。

第6行,第7行:输入的端口类型,输出的端口类型。

第12行:将信号赋值给对应的输出端口。

3.工程编译编译完成,通过下方的 Message窗口可以确认编译是否成功,如有错误,从Message信息提示判断代码何处出现错误,在编译完成后,点击左侧编译窗口中的RTL Viewer 可以查看代码综合生成的电路,此时编译窗口中还有一布EDA Netlist Writer没有自动完成,如果要进行功能波形仿真,则此时要再双击EDA Netlist Writer完成。

4.波形仿真点击左上角的 File—New--Vector Waveform File点击OK,出现波形文件界面后,点击左上方保存按钮,将其保存至工程目录中,默认命名与工程名相同,都为AndGate。

在波形文件界面左侧的Name拦中右键,选择Insert-->Insert Node or Bus,在弹出的界面中,点击Node Finder。

VHDL程序实例

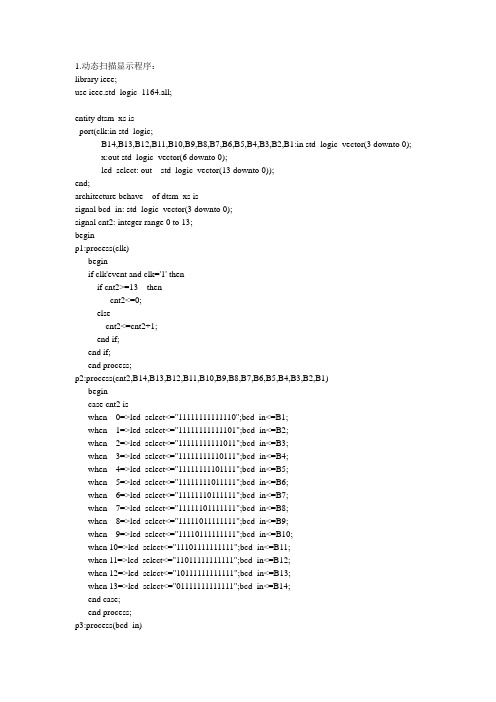

1.动态扫描显示程序:library ieee;use ieee.std_logic_1164.all;entity dtsm_xs isport(clk:in std_logic;B14,B13,B12,B11,B10,B9,B8,B7,B6,B5,B4,B3,B2,B1:in std_logic_vector(3 downto 0);x:out std_logic_vector(6 downto 0);led_select: out std_logic_vector(13 downto 0));end;architecture behave of dtsm_xs issignal bcd_in: std_logic_vector(3 downto 0);signal cnt2: integer range 0 to 13;beginp1:process(clk)beginif clk'event and clk='1' thenif cnt2>=13 thencnt2<=0;elsecnt2<=cnt2+1;end if;end if;end process;p2:process(cnt2,B14,B13,B12,B11,B10,B9,B8,B7,B6,B5,B4,B3,B2,B1)begincase cnt2 iswhen 0=>led_select<="11111111111110";bcd_in<=B1;when 1=>led_select<="11111111111101";bcd_in<=B2;when 2=>led_select<="11111111111011";bcd_in<=B3;when 3=>led_select<="11111111110111";bcd_in<=B4;when 4=>led_select<="11111111101111";bcd_in<=B5;when 5=>led_select<="11111111011111";bcd_in<=B6;when 6=>led_select<="11111110111111";bcd_in<=B7;when 7=>led_select<="11111101111111";bcd_in<=B8;when 8=>led_select<="11111011111111";bcd_in<=B9;when 9=>led_select<="11110111111111";bcd_in<=B10;when 10=>led_select<="11101111111111";bcd_in<=B11;when 11=>led_select<="11011111111111";bcd_in<=B12;when 12=>led_select<="10111111111111";bcd_in<=B13;when 13=>led_select<="01111111111111";bcd_in<=B14;end case;end process;p3:process(bcd_in)begincase bcd_in iswhen "0000"=>x<="1111110";when "0001"=>x<="0110000";when "0010"=>x<="1101101";when "0011"=>x<="1111001";when "0100"=>x<="0110011";when "0101"=>x<="1011011";when "0110"=>x<="1011111";when "0111"=>x<="1110000";when "1000"=>x<="1111111";when "1001"=>x<="1111011";when others=>x<="0000000";end case;end process;end;2.分频器设计程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;entity divider_1m isport(clk: in std_logic;clk_1Hz: out std_logic;clk_500Hz:buffer std_logic); end divider_1m;architecture rtl of divider_1m is signal cnt1:integer range 0 to 1999; signal cnt2:integer range 0 to 499; beginp1:process(clk)beginif clk'event and clk='1' thenif cnt1=cnt1'high thencnt1<=0;elsecnt1<=cnt1+1;end if;end if;end process;p2:process(clk,cnt1)beginif clk'event and clk='1' thenif cnt1>=999 thenclk_500Hz<='1';elseclk_500Hz<='0';end if;end if;end process;p3:process(clk_500Hz)beginif clk_500Hz'event and clk_500Hz='1' thenif cnt2=cnt2'high thencnt2<=0;elsecnt2<=cnt2+1;end if;end if;end process;p4:process(clk_500Hz,cnt2)beginif clk_500Hz'event and clk_500Hz='1' thenif cnt2>=249 thenclk_1Hz<='1';elseclk_1Hz<='0';end if;end if;end process;end rtl;3. 8位移位寄存器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY REG8 ISPORT(LOAD,CLR,DIRE,EN,CLK:IN STD_LOGIC;DATA :IN STD_LOGIC_VECTOR(7 DOWNTO 0);DOUT :BUFFER STD_LOGIC_VECTOR(7 DOWNTO 0)); END REG8;ARCHITECTURE A OF REG8 ISBEGINPROCESS(LOAD,CLR,DIRE,EN,CLK)V ARIABLE X:STD_LOGIC;BEGINIF LOAD='1' THEN DOUT<=DATA;ELSIF CLR='1' THEN DOUT<="00000000";ELSIF EN='1' THEN DOUT<=DOUT;ELSIF CLK'EVENT AND CLK='1' THENIF DIRE='1'THENX:=DOUT(7);DOUT(7 DOWNTO 1)<=DOUT(6 DOWNTO 0);DOUT(0)<=X;ELSEX:=DOUT(0);DOUT(6 DOWNTO 0)<=DOUT(7 DOWNTO 1);DOUT(7)<=X;END IF;END IF;END IF;END PROCESS;END A;4.BCD计数器设计(任意进制)LIBRARY ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;ENTITY cnt365 ISPORT(clk,reset:IN STD_LOGIC;daout:out std_logic_vector (9 downto 0));END;ARCHITECTURE fun OF cnt365 ISSIGNAL count: STD_LOGIC_VECTOR(9 downto 0); BEGINdaout <= count;p1:process(clk,reset)beginif (reset='1') thencount <= "0000000000";elsif (clk'event and clk='1') thenif count(9 downto 0)="1101100100"thencount(9 downto 0)<="0000000000";elsif count(7 downto 0)="10011001" thencount<=count + "01100111";elsif count(3 downto 0)="1001" thencount<=count + "0111";elsecount <= count + 1;end if;end if;end process p1;END fun;5.基于状态机的计数器设计library ieee;use ieee.std_logic_1164.all;entity statemachine_counter isport(clr,clk: in std_logic;q:out std_logic_vector(2 downto 0)); end;architecture a of statemachine_counter is type state_type is (s0,s1,s2,s3,s4,s5,s6); signal present_state,next_state: state_type;beginp1:process(clk,clr)beginif clr='1' thenpresent_state<=s0;elsif clk'event and clk='1' thenpresent_state<=next_state;end if;end process p1;p2:process(clk,present_state)begincase present_state iswhen s0=>next_state<=s1;when s1=>next_state<=s2;when s2=>next_state<=s3;when s3=>next_state<=s4;when s4=>next_state<=s5;when s5=>next_state<=s6;when s6=>next_state<=s0;end case;end process p2;p3:process(clr,present_state)beginif clr='1' thenq<="000";elsecase present_state iswhen s0=>q<="000";when s1=>q<="001";when s2=>q<="010";when s3=>q<="011";when s4=>q<="100";when s5=>q<="101";when s6=>q<="110";end case;end if;end process p3;end a;LED灯控制--设计一个循环彩灯控制器,该控制器控制红,绿,黄三个发光二极管循环发亮--要求红发光管亮2秒,绿亮3秒,黄亮1秒。

VHDL串口程序

rx_int: in std_logic --接收数据中断信号,接收数据期间时钟为高电平,传送给串口发送

bps_start:out std_logic; --接收到数据后,波特率时钟启动置位

rx_data: out std_logic_vector(7 downto 0); --接收数据寄存器,保存直至下一个数据来到

rx_int: out std_logic --接收数据中断信号,接收数据期间时钟为高电平,传送给串口发送

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity uart_rx is

port(clk : in std_logic; --系统时钟

rst_n=>rst_n, --复位信号

rs232_tx=>rs232_tx, --RS232发送数据信号

clk_bps=>clk_bps_2, --此时clk_bps的高电平为发送数据的采样点

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity uart is

port(clk : in std_logic; --系统时钟

rst_n: in std_logic; --复位信号

clk_bps=>clk_bps_2,

bps_start=>bps_start_2

);

VHDL仿真步骤

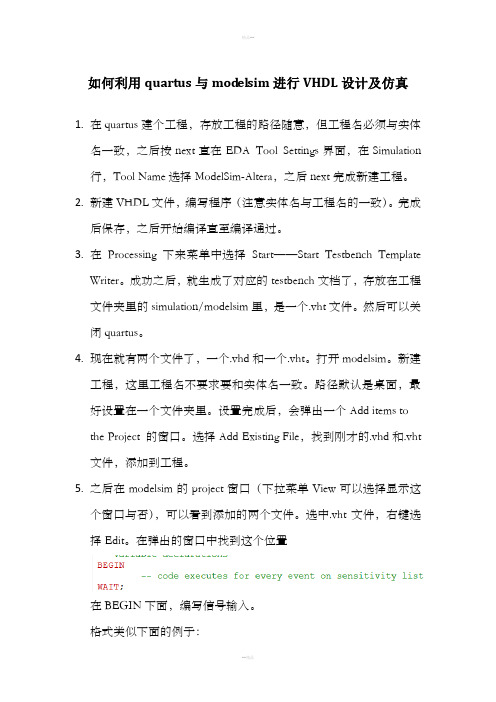

如何利用quartus与mod elsim进行VHDL设计及仿真1.在quartus建个工程,存放工程的路径随意,但工程名必须与实体名一致,之后按next直在EDA Tool Settings界面,在Simulation 行,Tool Name选择ModelSim-Altera,之后next完成新建工程。

2.新建VHDL文件,编写程序(注意实体名与工程名的一致)。

完成后保存,之后开始编译直至编译通过。

3.在Processing下来菜单中选择Start——Start Testbench TemplateWriter。

成功之后,就生成了对应的testbench文档了,存放在工程文件夹里的simulation/modelsim里,是一个.vht文件。

然后可以关闭quartus。

4.现在就有两个文件了,一个.vhd和一个.vht。

打开modelsim。

新建工程,这里工程名不要求要和实体名一致。

路径默认是桌面,最好设置在一个文件夹里。

设置完成后,会弹出一个Add items to the Project 的窗口。

选择Add Existing File,找到刚才的.vhd和.vht 文件,添加到工程。

5.之后在modelsim的project窗口(下拉菜单View可以选择显示这个窗口与否),可以看到添加的两个文件。

选中.vht文件,右键选择Edit。

在弹出的窗口中找到这个位置在BEGIN下面,编写信号输入。

格式类似下面的例子:input <="00000001" after 1us,"00000010" after 2us,"00000100" after 3us,"00001000" after 4us,"00010000" after 5us,"00100000" after 6us,"01000000" after 7us,"10000000" after 8us;好了之后保存。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(2)关系运算符 对具有相同数据类型的运算对象进行比较运算 ,运算结果的数据 类型为布尔类型

等于(=)、不等于(/=)、大于、小于、大于等于(>=)、小于等于(<=);

(3)算术运算符

加、减、乘(*)、除(/)、MOD(取模)、REM(取余)、ABS(绝对值)、乘方 (**)

与变量不同的是,信号的赋值要经过延时后才能成为当前值。 信号的作用:在进程间传递信息,完成进程间通信;二是在结构设计中用来连 接元件,实现元件间的通信。 例:library ieee; Use ieee.std_logic_1164.all; Entity zuhe is Port(a,b,c,d:in std_logic;

(7)标准逻辑矢量(std_logic_vector)数据类型

是std_logic数据类型的组合。

注意:VHDL语言是一种强类型语言,对数据类型要求非常严格,不同数据类型的 数据不能进行直接运算或代入赋值;即使类型相同,长度不同也不能代入。可以用 类型转换函数来实现类型转换。

4、运算操作符

(1)逻辑运算符 对具有相同数据类型的运算对象进行逻辑运算

PORT(i0,i1 : IN STD_LOGIC; q: OUT STD_LOGIC );

END ENTITY or21; ARCHITECTURE one OF or21 IS

BEGIN

q<=i0 OR i1; END ARCHITECTURE one;

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY inv21 IS

标准库里主要包括std_logic_1164、numeric_bit和numberic_std.

2 实体 实体有点类似原理图中的一个器件符号,用来描述该器件的输入输出 端口特征,但不涉及器件的具体逻辑功能和内部电路结构 格式:entity 实体名 is

【generic(类属表)】 【port (端口说明;】 end 实体名;

Type fsmst is(s0,s1,s2,s3);

Signal present_state,next_state:fsmst;

综合器在编码过程中自动将枚举元素转换成位矢量,位矢量的长度取决于枚举元素 的数量。如上述语句4个枚举元素,位矢量的长度为2,每个枚举元素默认的编码: s0=“00”;s1=“01”;s2=“10”;s3=“11”

G:out std_logic); End zuhe; Architechure one of zuhe is Signal e,f : std_logic; Begin E<=a or b; F<=not(c or d); G<=e and f; end;

3、数据类型 常用的数据类型 (1)整形(integer)数据类型 正整数、负整数和零。范围-214783647~214783647(231-1) (2)布尔(boolean)数据类型 取值”ture”或”false” (3)位(bit)数据类型 取值’1’或’0‘;要用单引号 (4)位矢量(bit_vector) 位矢量数据类型是基于位数据类型的数组 例:signal dd:bit_vector(7 downto 0) 信号dd被定义位一个8位宽的矢量,最左位为dd(7),最右位为dd(0) (5)枚举类型 用文字符号来表示一组实际的二进制类型,在状态机设计中,通常将二进制数表 示的状态用文字符号代替

只描述电路的功能或称为行为,即电路输入与输出间的转换的行为,而不包含实现 这些功能的硬件结构信息。称为行为描述。

举例:采用行为描述方式的2选1多路选择器

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY mux21 IS

PORT( a,b : IN STD_LOGIC; s : IN STD_LOGIC; y : OUT STD_LOGIC );

ENTITY mux21 IS PORT( a,b : IN STD_LOGIC; s : IN STD_LOGIC; y : OUT STD_LOGIC );

END ENTITY mux21; ARCHITECTURE dataflow OF mux21 IS BEGIN y<=(a AND (NOT s)) OR (b AND s); END ARCHITECTURE dataflow;

END ENTITY mux21; ARCHITECTURE behav OF mux21 IS

BEGIN PROCESS(a,b,s) BEGIN IF s='0' THEN y<=a; ELSE y<=b; END IF; END PROCESS;

END ARCHITECTURE behav;

(2)结构体描述方法 从实体的硬件结构方面描述,包含元件的说明。元件之间的互连说明。采用 的基本语句是元件例化语句或生成语句。这要求设计者具有较好的硬件基础 例:用VHDL语言的结构描述法描述2选1数据选择器 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY and21 IS

3 结构体 用来描述前面定义的实体内部结构和逻辑功能。结构体必须和实体相联系,一个 实体可以有多个结构体。他的运行是并行的。 格式: Architecture 结构体名 of 实体名 is [说明语句] Begin [功能描述语句] End 结构体名;

VHDL结构体的三种描述方法

(1)行为描述方法

PORT(i0,i1 : IN STD_LOGIC; q: OUT STD_LOGIC );

END ENTITY and21; ARCHITECTURE one OF and21 IS

BEGIN q<=i0 AND i1; END ARCHITECTURE one;

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY or21 IS

VHDL程序结构和要素

VHDL程序基本结构 VHDL语言的结构体描述方法 VHDL语言要素 VHDL基本描述语句

一个简单的VHDL程序

Library ieee; Use ieee.std_logic_1164.all;

Entity mux21 is Port(A,B,S:in std_logic; Z:out std_logic); End mus21;

VHDL的语言的要素

VHDL的语言要素,作为硬件描述语言的基本元素,主要有标识符、数据对 象、数据类型和运算操作符等 1、标识符 VHDL标识符的命名规则 (1)有效字符是26个英文字母(不区分大小写)、10个数字符号0-9、下 划线(不能用到开头) (2)每个标识符用英文字母开头,字符串中不能有空格。 2、数据对象 凡是可以赋予一个值的客体叫对象,包括常量、信号与变量 (1)常量 在设计中不会变的值。主要是为了程序更容易阅读和修改。它 必须在程序包、实体、构造体或进程的说明区域加以说明。一般要赋予初 始值,且只能被赋值一次。 常量定义的一般表达式:constant 常量名:数据类型:=表达式; 例:constant width:integer:=8;

(4)移位运算符

逻辑左移(SLL)、逻辑右移(SRL)、算术左移(SLA)、算术右移(SRA)、逻 辑循环左移(ROL)、逻辑循环右移(ROR)

(5)并置运算符“&”

用于位的连接,将几个位用并置运算符连接起来,可以构成一个具有4位长度的位矢 量

使用运算符时注意: (1)操作符之间的优先级 (2)运算重载 如两信号数据类型不同,不能将一个信号的值赋给另一个信号。数据类型 的转换必须要用运算重载。一般用ieee 1164中的标准重载函数实现。 Library ieee; Use ieee_std_logic_1164.all; Use ieee_std_logic_arith.all Use ieee_std_logic_unsigned.all Use ieee_std_logic_signed.all 程序包里有转换函数

Architecture one of mux21 is Begin Z<=A when S=‘0’ 的基本结构

VHDL的设计描述包括库(library)、实体(entity)和结构体architecture)

1、库 库已经存储和放置了可被其他VHDL程序调用的数据定义。器 件说明、程序包等资源。库的种类很多,常见的库有IEEE标准库、 work库。

temp:=x“5c”; 逐位赋值:

temp(6):=‘1’; 多位赋值:

temp(6 downto 3):=“1011”; (3)信号 是描述硬件系统的基本数据对象,与硬件中的”连线“相对应,一般而 言,信号是全局变量,使用范围是实体、结构体和程序包。 信号的定义: Signal 信号名:数据类型:=初始值; 信号可以多次赋值,赋值表达式: 目标信号名<=表达式;这种方式允许产生延时

PORT(i0 : IN STD_LOGIC; q: OUT STD_LOGIC );

END ENTITY inv21; ARCHITECTURE one OF inv21 IS BEGIN

q<= (NOT i0); END ARCHITECTURE one;

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY mux21 IS

(6)标准逻辑位(std_logic)数据类型

Std_logic数据类型是ieee 1164中定义的一种工业标准的逻辑类型,它包含9种取值, 分别为:

在程序中使用std_logic数据类型前,必须在程序中申明库和程序包说明语句: