SP3767HN 低功耗立体声收音机电路

基于单片机和TEA5767HN的FM收音机系统的设计

在当前数字信息技术和网络技术高速发展的PC时代。

嵌入式技术越来越同人们的生活紧密相关。

其中掌上嵌入式电子产品更是给人们的生活带来了很大方便和很多快乐。

尽管生活方式不断发生变化,但无线电仍然很流行。

因此,本文针对TEA5767HN数字收音机芯片的控制机理,阐述了通过该芯片和C51单片机来将FM数字收音机嵌入智能电子产品的设计方法。

1 系统整体设计思路本立体声FM数字收音机的设计目标是通过单片机AT89S52来控制FM接收芯片TEA5767HN,从而实现可自动搜索并存储10多个电台节目(也可手动搜索并存储电台节目)。

所收听电台的频率和台号及时钟可在显示模块中的LCD上显示,音量则可通过音量加、减按键自主控制,并能存储关机时设定的数据以及闹钟功能。

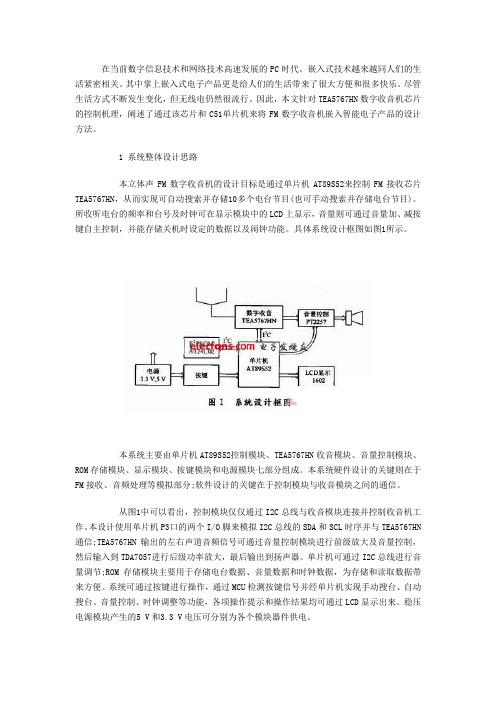

具体系统设计框图如图1所示。

本系统主要由单片机AT89S52控制模块、TEA5767HN收音模块、音量控制模块、ROM存储模块、显示模块、按键模块和电源模块七部分组成。

本系统硬件设计的关键则在于FM接收、音频处理等模拟部分;软件设计的关键在于控制模块与收音模块之间的通信。

从图1中可以看出,控制模块仅仅通过I2C总线与收音模块连接并控制收音机工作。

本设计使用单片机P3口的两个I/O脚来模拟I2C总线的SDA和SCL时序并与TEA5767HN 通信;TEA5767HN输出的左右声道音频信号可通过音量控制模块进行前级放大及音量控制,然后输入到TDA7057进行后级功率放大,最后输出到扬声器。

单片机可通过I2C总线进行音量调节;ROM存储模块主要用于存储电台数据、音量数据和时钟数据,为存储和读取数据带来方便。

系统可通过按键进行操作,通过MCU检测按键信号并经单片机实现手动搜台、自动搜台、音量控制、时钟调整等功能,各项操作提示和操作结果均可通过LCD显示出来。

稳压电源模块产生的5 V和3.3 V电压可分别为各个模块器件供电。

2 硬件系统电路设计由于本系统硬件设计的关键在于FM接收、音频处理等模拟电路部分,其余电路均为常规电路,因而其硬件系统的设计着重分析收音模块、音量控制模块这两部分电路。

七管分立收音机原理图及安装过程说明.

七管分立收音机原理及安装过程说明一、实验目的:通过对一只正规产品收音机的安装、焊接、调试、了解电子产品的装配全过程,训练动手能力,掌握元器件的识别,简易测试,及整机调试工艺。

二、要求:1、对照原理图讲述整机工作原理;2、对照原理图看懂装配接线图;3、了解图上符号,并与实物对照;4、根据技术指标测试各元器件的主要参数;5、认真细致地安装焊接,排除安装焊接过程中出现的故障。

三、产品简介该机为七管中波调幅袖珍式半导体收音机,采用全硅管标准二级中放电路,用二只二极管正向压降稳压电路,稳定从变频、中频到低放的工作电压,不会因为电池电压降低而影响接收灵敏度,使收音机仍能正常工作,本机体积小巧,外观精致,便于携带。

1、技术指标:频率范围:525~1605KHz中频频率:465KHz灵敏度:≤ 2mV/m S/N 20dB扬声器:Ф57mm 8Ω输出功率:50mW电源:3V (2节 5号电池2、调幅工作原理(1工作方框图(2工作原理当调幅信号感应到 B1及 C1组成的天线调谐回路,选出我们所需的电信号 f1进入 V1(9018H 三极管基极;本振信号调谐在高出 f1频率一个中频的 f2(f1+465KHz 例:f1=700KHz 则 f2=700+465KHz=1165KHz进入 V1发射极,由 V1三极管进行变频,通过 B3选取出 465KHz 中频信号经 V2和 V3二级中频放大 , 进入 V4检波管 , 检出音频信号经 V5(9014低频放大和由 V6、 V7组成功率放大器进行功率放大,推动扬声器发声。

图中 D1、 D2 (IN4148组成 1.3V ±0.1V 稳压,固定变频,一中放、二中放、低放的基极电压,稳定各级工作电流,以保持灵敏度。

由 V4(9018三极管 PN 结用作检波。

R1、 R4、 R6、 R10分别为 V1、 V2、 V3、V5的工作点调整电阻, R11为 V6、 V7功放级的工作点调整电阻, R8为中放的AGC 电阻, B3、 B4、 B5为中周(内置谐振电容 ,既是放大器的交流负载又是中频选频器,该机的灵敏度,选择性等指标靠中频放大器保证。

集成电路调频收音机diy——简单、灵敏度高、选择性好

集成电路调频收音机diy——简单、灵敏度高、选择性好•我们知道调频收音机(FM)有着非常好的性能:抗干扰能力强、音质优美,调频广播现在也非常丰富,如何制作一台性能优良的调频收音机是广大电子爱好者梦寐以求的事情,而分立元件的调频收音机需要的元件多、调试复杂,集成电路的调频收音机,制作相对简单一些,稍微有点电子知识的人就可以完成。

今天给大家介绍一个性能非常好、调试十分简单、元件数较少的调频集成电路收音机,它是DTA7000调频集成电路,该集成电路的简单之处在于它仅仅有一个LC选頻电路,而其它的集成电路还有一个本振LC电路,需要对二者进行统调,没有搞好这一关,其它都是白做。

•电路图如下:由两部分组成:集成电路部分、功放部分,当如果嫌麻烦,后面的功放部分可以省去,直接接高阻耳机或小功率扬声器(低阻也可以,不过声音较低)。

•TDA7000FM集成电路组成:射频输入级、混频器、本振、中频限幅器、中频滤波器、放大器、相位解调器、静音检测、锁频环系统和电源控制振荡器。

该集成电路具有一个FLL(锁频环)系统以70kHz的中频,由有源RC滤波器获得选择,内部结构图如下,这个我们了解以下就行,没有必要细究。

TDA7000结构图•所有元件均很容易配齐,外接天线使用普通的拉杆天线即可,可变电容为20p有机薄膜电容,电感为5-6T的0.5-0.7mm漆包线在圆珠笔上绕制即可,如果频率不合适,适当调节电感精密程度,或者利用电感表进行测量,确定接受频率。

A、B端为输出端,可以直接接高阻耳机,也可以外接任何功放电路,本实验用的是TDA2822集成电路,喇叭为3W,声音很洪亮。

•该电路非常简单,制作容易,成功率100%,且效果非常好,特别是在城市里,随便接一根导线做天线就能清晰的收听广播,很适合于初学者制作。

TDA7000调频收音机外接元件电路图功放电路图•也可以采用以下电路图,使用变容二极管改变频率,有兴趣的朋友可以试一下。

使用变容二极管的调频收音机。

收音机电路分析与调试ppt课件

收音机的输入回路和本振回路

三点统调的作用 整机灵敏度的均匀性和选择性等达到最好的程度,要使收音机 的本振在整个频段内总是高于电台信号465 kHz是较困难的,为 此,可使本地振荡回路在高端(1400 kHz)、中间(1000 kHz) 和低端(600 kHz)三点处的频率比电台频率高465 kHz,这样本 振在其它点的频率即算基本调准。

为了规范事业单位聘用关系,建立和 完善适 应社会 主义市 场经济 体制的 事业单 位工作 人员聘 用制度 ,保障 用人单 位和职 工的合 法权益

5)低放和功放电路

低放电路主要由 V5、B6组成,进行信 号的电压放大。

功放电路将前置电 路送来的音频信号进 行功率放大,推动扬 声器发出声音。

为了规范事业单位聘用关系,建立和 完善适 应社会 主义市 场经济 体制的 事业单 位工作 人员聘 用制度 ,保障 用人单 位和职 工的合 法权益

为了规范事业单位聘用关系,建立和 完善适 应社会 主义市 场经济 体制的 事业单 位工作 人员聘 用制度 ,保障 用人单 位和职 工的合 法权益

3)统调(三点跟踪)

磁性天线

微调电容

调接收低频率端:双连全旋进,高频信号发生器输出载频 525KHz;移动磁性天线线圈在磁棒上的位置,同时用mV表监 测输出音频电压大小,将输出的音频电压调至最大。 调接收高频率端:双连全旋出,高频信号发生器输出载频 1605KHz,用无感锣刀调与天线连相并联的微调电容,同时用 mV表监测输出音频电压大小,将输出的音频电压调至最大。

一、1)收SD音-1机05电收路音分机析直(流以通S路D-105为例)

为了规范事业单位聘用关系,建立和 完善适 应社会 主义市 场经济 体制的 事业单 位工作 人员聘 用制度 ,保障 用人单 位和职 工的合 法权益

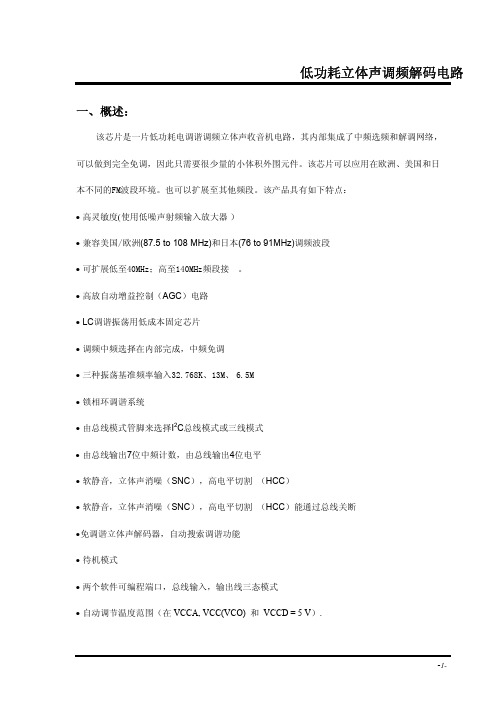

低功耗立体声调频解码电路

静电击穿电压

Ves

对于除数据脚外的所有管脚

对于数据脚

注意: 1. 机器模式(R = 0 Ω, C = 200 pF). 2. 人工模式 (R = 1.5 kΩ, C = 100 pF).

条件

note1 note2 note1 note2

最小值

−0.3

−0.3

−0.3

−0.3

−55

−40 −200 −2000 −150 −2000

-2-

三、电路结构框图:

VCCA

FM antenna 100pF L1

47nF LIMDEC2

29

47nF LIMDEC1 28

47nF TIFC 27

33nF Vref 26

MPXO 25

33nF TMUTE 24

VAFR 23

VAFL 22

R1

Igain 32

4.7 22nF

AGND 33

22uF

30 11

56 19

80 26

µA µA

待机模式; VCCD = 5 V

50

78

105

µA

bus enable line HIGH bus enable line LOW

20

33

45

µA

-5-

低功耗立体声调频解码电路

(2)直流工作点

符号

参数

直流工作点 VCPOUT

无负载

VXTAL1

VXTAL2

VPHASEFIL VPILFIL VVAFL VVAFR VTMUTE VMPXO VVref VTIFC

760

1

1.2

10.5 10.7

6 6.2 940

数字式调频立体声收音机电路原理图如何

数字式调频立体声收音机电路原理图如何数字式调频立体声收音机电路原理图如何?答:数字式调频立体声收音机电路原理图如图6.22所示。

由图6.22可知数字式调频立体声收音TMP75AIDGKR机电路主要由飞利浦TEA5767 (或其兼容产品)收音模块、TDA2822音频放大电路和单片机掌握电路构成。

首先调频信号经由天线接收送到TEA5767第10脚,第7脚和第8 脚为左右声道输出,送往音频放大电路进行功率放大以推动扬声器。

单片机接受按键的掌握信息并通过I2C总线对TEA5767实现掌握,完成选台的功能,然后将频率实时显示在数码管上。

制作数字式调频立体声收音机需要选用哪些元器件?答:制作数字式调频立体声收音机需要选用4块集成电路, 其中∣C.选用STC89C51型单片机,IC,选用飞利浦TEA5767 型收音集成电路,IC,选用TDA2822型音频功率放大集成电路,IC。

选用7805型三端稳压集成电路。

vτ, ~vT,、VT,选用SC9012 型三极管,VT。

选用SC9014型三极管。

VD1、VD,、VDo 选用IN4148 型二极管,VD2〜VD5 选用1N4007型整流二极管,VD。

、VDo〜VD.,选用LED发光二极管。

晶体振荡器选用频率为11.0592MHz品振,其他元器件无特别要求,按图6.22所示型号选用。

制作数字式调频立体声收音机所用的元器件实物如图6.23所示。

数字式调频立体声收音机电路原理图如何?答:数字式调频立体声收音机电路原理图如图6.22所示。

由图6.22可知数字式调频立体声收音TMP75AIDGKR机电路主要由飞利浦TEA5767 (或其兼容产品)收音模块、TDA2822音频放大电路和单片机掌握电路构成。

首先调频信号经由天线接收送到TEA5767第10脚,第7脚和第8 脚为左右声道输出,送往音频放大电路进行功率放大以推动扬声器。

单片机接受按键的掌握信息并通过I2C总线对TEA5767实现掌握,完成选台的功能,然后将频率实时显示在数码管上。

TEA5767收音机设计

摘要随着我国经济的高速发展,微电子技术、无线电通信技术和自动控制技术也得到了迅速发展,锁相环和频率合成技术已经进入一个崭新的时代,其应用越来越广。

而收音机作为现代的娱乐工具,与人们的生活紧密相关,随着人们对其要求的提高,收音机得到了快速发展,传统的电容、电感调台收音机已经向数字化收音机发展。

本文在已有的收音机模块的基础上,采用A T89S52微控制器对收音机进行控制,由 1602液晶模块作显示,用TEA5767的高灵敏度,低电压和低功耗的全集成的优点作收音模块芯片,通过合理设计,制作了一款完善的数字调谐收音机,并增加了传统收音机所不具备的功能,使之达到了较为理想的效果。

关键词:微控制器, TEA5767,收音机ABSTRACTWith the development of the economy, microelectronic technology, radio communication technology and the automatic theory are developed rapidly, the compound frequency technology has been in a new state. It's application is becoming more and more widely. But the radio as an important pastime tools , it also has developed quickly with the improving requirement of the people .It's radio technology has developed from tradition capacitance or inductance to digital .The article is based on the now-being general radio module, using A T89S52 microcontroller to control the radio, by 1602 for liquid crystal display modules, with TEA5767 the high sensitivity, low voltage and low power consumption of all the advantages of integrated chips for the radio module. the reliability is improved and the feeling of comfort is better through the reasonable design, so the function of radio is more powerful compared with tradition one .Keywords: Microcontroller, TEA5767,Radio目录摘要 (I)ABSTRACT (II)第1章引言 (1)1.1背景 (1)1.2研究内容 (1)第2章芯片介绍 (2)2.1TEA5767收音芯片概述 (2)2.1.1 TEA5767的特点 (2)2.1.2 管脚说明 (3)2.1.3 I2C总线说明 (3)2.1.4 数据传输 (4)2.21602液晶模块介绍 (6)2.2.1技术参数 (7)2.2.2 接口信号说明 (7)2.2.3制器接口时序说明(HD4478及兼容芯片) (7)2.2.4 控制器接口时序说明 (10)2.3FM62429芯片介绍 (11)2.4AT89S52片机模块介绍 (12)第3章硬件电路设计 (16)3.1系统组成 (16)3.2收音模块 (17)3.3音量控制模块 (17)3.4LCD1602模块 (18)3.5按键模块 (18)3.6AT89S52微控制模块 (19)第4章软件设计部分 (21)4.1主程序流程图 (21)4.2按键控制 (22)4.3收音机控制 (22)4.4LCD显示控制 (23)第5章结束语 (24)致谢 (25)参考文献 (26)附录源代码 (27)第1章引言1.1背景收音机诞生到现在已有80年的历史了,在此期间经历了60年代从电子管到晶体管的革命,80年代从晶体管到集成电路的革命,目前正面临着数字化革命。

收音机的工作原理

收音机的工作原理标题:收音机的工作原理引言概述:收音机是一种常见的电子设备,它能够接收无线电信号并将其转化为声音。

本文将详细介绍收音机的工作原理,包括信号接收、解调、放大和音频输出等四个部分。

一、信号接收1.1 天线:收音机的天线用于接收无线电信号,它能够将无线电波转化为电信号。

1.2 调谐电路:收音机中的调谐电路能够选择特定频率的无线电信号,并将其传递给后续的解调电路。

1.3 预放电:预放电电路能够将接收到的微弱信号进行放大,以便后续的处理。

二、解调2.1 检波器:收音机中的检波器用于将调谐电路传递过来的高频信号转化为低频信号。

2.2 二极管:检波器通常使用二极管来实现,它能够将无线电信号的正弦波转化为直流信号。

2.3 滤波器:滤波器用于去除检波器输出的直流分量,以便后续的放大和音频输出。

三、放大3.1 中频放大:收音机中的中频放大器能够放大检波器输出的低频信号,以便进一步处理。

3.2 变压器:中频放大器通常使用变压器来实现信号的放大。

3.3 高频放大:高频放大器用于放大调谐电路传递过来的高频信号,以增强信号强度。

四、音频输出4.1 音频放大:音频放大器用于放大中频放大器输出的低频信号,使其能够驱动扬声器。

4.2 扬声器:扬声器将放大后的信号转化为声音,并将其传递给用户。

4.3 音量调节:收音机通常配备音量调节器,用户可以通过调节音量控制电路来改变声音的大小。

通过以上四个部分的工作,收音机能够将无线电信号转化为声音信号,并通过扬声器输出给用户。

收音机的工作原理涉及到信号接收、解调、放大和音频输出等多个环节,每个环节都起着关键的作用。

深入了解收音机的工作原理有助于我们更好地理解和使用这一常见的电子设备。

和初学者谈谈电子管收音机电源电路

和初学者谈谈电子管收音机电源电路本帖最后由白居不易于 2017-5-9 10:13 编辑电子管工作时要耗电,因此任何电子管收音机都离不开电源。

比如束射功放管6P1,电子管手册给出灯丝电压6.3V,灯丝电流0.45A,屏极电压250V,第2栅(帘栅)极电压250V,第1栅电压(栅极偏压)-12.5V(有的电子管给出阴极电阻值)。

电子管收音机的电源电路包括灯丝电压'、屏极、帘栅极等需要的直流高压以及信号栅极的偏压三部分:一、灯丝电源,也叫甲电,A电。

除极少数冷阴极电子管不需要灯丝电源,直热式管灯丝通电后发射电子,旁热式管灯丝加热氧化物阴极。

常用的电子管灯丝分两类,一类是电压相同,电流各异,如直热管1A2、1K2、1B2等灯丝电压1.2V,2P2(灯丝电压串接2.4V,并联1.2V)。

6N2、6P1、6Z4、6N8P、6P6P等表示灯丝电压为6.3V;12AX7、12AT7、12AU7,灯丝电压串接12.6V,并联6.3V。

另一类为电流相同,电压各异,如12SA7GT、12SK7GT、12SQ7GT、35L6GT、50L6GT、35Z5GT等电流均为0.15A,适用于交直流两用串丝机电路。

国外有的复合管灯丝电压117V,可直接用于110V交直流电源。

此外欧洲管H(0.15A)、P(0.3A)、U(0.1A)、X(0.6A)等打头的电子管均为串丝机使用电子管,其性能与E(灯丝电压6.3V)打头后缀相同的电子管一样。

一些老式电子管和军用代号电子管的灯丝电压需要查阅手册,还有一种0打头的冷阴极整流管,不需要热丝。

1、直流收音机灯丝电源采用电池供电:过去有一种大型甲电,电压1.5V,用于收音机灯丝和老式电话机,国产直热管灯丝电压1.2V,在电池电压降低后仍然保持较高灵敏度,比美式灯丝电压1.4V直热管经济耐用,为业余制作的首选。

后来有一种热电偶发电器,点燃煤油灯加热后产生电能供给直流收音机使用,但是成本较高,没有普及。

收音机工作原理、电路图、安装、焊接图片详解

零

电阻 共13只

R1 100k 棕黑黄 R2 2k 红黑红 R3 100Ω 棕 黑 棕 R4 20k 红黑橙 R5 150Ω 棕 绿 棕

21

中频放大级

中频放大级是指变频输出至振幅检波器之 间的电路,其作用是放大中频信号,它是收音 机的“心脏”。收音机的灵敏度、选择性及音质 都有直接影响。中频放大器应具有增益高、稳 定性好、选择性优良、通频带较宽的特点。

灵敏度:收音机接收弱信号的能力。 单位:mV/m 该数值越小灵敏度越高。

22

检波级

2

2. 无线电发射与接收的基本原理 (1)无线电发射的基本原理 我们已经知道利用天线可以把无线电波向空中发射出去,但是天 线长度必须和电磁波长相对应,才能有效地发射。而且只有频率相当 高的电磁场才具有辐射能力,因此利用频率较高的无线电波才能传送 信号。我们把无线波发射机中产生的高频振荡作为“载波”,将音频 信号加到“载波”上,这个过程叫做调制。经过调制以后的高频振荡 叫做已调信号。 利用传输线可把已调信号送到发射天线,变成无线电波,发射到 空间去。经过调制以后可以使广播信号有效的发射,而且不同的发射 机可以采用不同的“载波”频率,使彼此互不干扰。 一台广播发射机应该包括四个部分:一是声音的变换与放大,这 一部分的频率较低,叫做低频部分;二是高频振荡的产生、放大、调 制和高频功率放大,统称高频部分;三是天线与传输线;四是直流电 源部分。 话筒和音频放大器的作用,是把声音变换成调制器所需的一定强度 的音频电信号。高频振荡器的作用是产生高频正弦振荡,即载波,它 的频率叫做载频。

B

14

变变变 变频振荡

(1)输入回路。 从天线接收进来的高频信号首先进入输入调谐回路。输入回路的任务是: 1. 通过天线收集电磁波,使之变为高频电流;2.选择信号。在众多的信号 中,只有载波频率与输入调谐回路相同的信号才能进入收音机。 (2)变频和本机振荡级。 从输入回路送来的调幅信号和本机振荡器产生的等幅信号一起送到变 频级,经过变频级产生一个新的频率,这一新的频率恰好是输入信号频率 和本振信号频率的差值,称为差频。例如,输入信号的频率是535kHz,本 振频率是1000kHz ,那么它们的差频就是1000 kHz - 535 kHz = 465kHz;当输入信号是1605kHz时,本机振荡频率也跟着升高,变成 2070kHz。也就是说,在超外差式收音机中,本机振荡的频率始终要比输 入信号的频率高一个465kHz。这个在变频过程中新产生的差频比原来输入 信号的频率要低,比音频却要高得多,因此我们把它叫做中频。不论原来 输入信号的频率是多少,经过变频以后都变成一个固定的中频,然后再送 到中频放大器继续放大,这是超外差式收音机的一个重要特点。 以上三种频率之间的关系可以用下式表达: 本机振荡频率-输入信号频率=中频

第五讲 高频电路设计举例

引脚 1 2

功能 GND L-OUT R-OUT MPX ANT

引脚 6 7 8 9 10

功能 DATA CLK BUS MODE W/R VCC

2 TEA 5767

9

3

8

4 7

4

5 6

5

B-102BC应用模块与单片机采用I2C通 信的典型接口电路

VCC

+

47uF C1 224 GND LOUT C2 224

PLL7~PLL0:预置或搜索电台的频率数值的低8位。 写模式字节3格式

B7 (MSB) SUD B0 (LSB) SWP1

B6

SSL1

B5

SSL0

B4

HLSI

B3

MS

B2

ML

B1

MR

SUD:搜索方向设置。1向上搜索,0向下搜索。 SSL1,SSL0:设定搜索停止电平 SSL SSL 搜索停止电平

HLSI:设置高低本振。1为高本振,本振频率高 出电台一个中频(225kHz)。0为低本振,本振 频率低于接收电台一个中频。 MS:单声道和立体声设置。1单声道,0立体声。 ML:左声道静音设置。1静音,0非静音。 MR:右声道静音设置。1静音,0非静音。 SWP1:软件可编程输出口1设置。1时SWPOR1为 高,0时SWPOR1为低。 1 0 0 1 1 0 0 1 0 1 不搜索 低 电 平 , ADC 输 出值为5 中 电 平 , ADC 输 出值为7 高 电 平 , ADC 输 出值为10

(1)写控制寄存器 当向TEA5767HN写控制字时,按地址和写第1~5字节顺序进行。先写一个字节的 最高位,在时钟下降沿写入的数据有效。 写模式字节1格式

B7 (MSB) MUTE B6 SM B5 PLL13 B4 PLL12 B3 PLL11 B2 PLL10 B1 PLL9 B0 (LSB) PLL8

七管调幅收音机工作原理

七管调幅收音机工作原理七管调幅收音机工作原理框图七管调幅收音机电路图本机电路图如图所示。

由B1及C1-A组成的天线调谐回路感应出广播电台的调幅信号,选出我们所需要的电台信号F1基极。

本真新号调谐在高出F1一个中频F2进入V1发射极,由V1三极管进行变频,在V1集电极回路通过B3选取F2与F1的差频信号。

中频信号经V2和V3二级中频放大,进入V4检波管,检出音频信号经V5低频放大由V6,V7组成变压器耦合功率放大器进行功率放大,推动扬声器发声。

图中D1,D2组成1.3V+-0.1V稳压,提出变频,一中放,二中放,低放的基极电压,稳定各级工作电流,保证整机灵敏度。

V4发射-基极结用做检波。

R1、R4、R6、R10分别做为V1、V2、V3、V5的工作点调整电阻,R11为V6、V7功放级的工作点调整电阻,R8为中方的AGC电阻,B3、B4、B5为中周,既是放大器的交流负载又是中频选频器,该机的灵敏度、选择性等指标靠中频放大器保证。

B6、B7为音频变压器,起交流负载及阻抗匹配的作用。

1.输入调谐电路.输入调谐电路由双连可变电容器的C A和T1的初级线圈L ab组成,是一并联谐振电路,T1是磁性天线线圈,从天线接收进来的高频信号,通过输入调谐电路的谐振选出需要的电台信号,电台信号频率是f=1/2πL ab C A,当改变C A时,就能收到不同频率的电台信号。

2.变频电路本机振荡和混频合起来称为变频电路。

3.中频放大电路4.检波和自动增益控制电路中频信号经一级中频放大器充分放大后由T4耦合到检波管VT3,VT3既起放大作用,又是检波管,VT3构成的三极管检波电路5.前置低放电路检波滤波后的音频信号由电位器RP送到前置低放管VT4,经过低放可将音频信号电压放大几十到几百倍6.功率放大器(OTL电路)。

SP3767高性能低功耗电调谐FM接收及处理集成电路

HV F 4 装 技术 在 国内属 首创 。 Q N 0封

3 应用范 围和 市场 前景 、

S36 P 7 7主要 应用 于 MP 3的 F M接 收模 块 。MP 3随身听 已成 为 近几 年来 发展 最快 的 电子 产 品 , I C市 据 D

场 调研 报 告 , 全球 MP 3市 场正 蓬 勃发 展 , 将 以 2%的年增 长 速度 在 2 0 年 达 到 4 0亿 欧元 的市 场 规模 , 并 0 08 7

维普资讯

年平 均 每月 可达 3 0万颗 电路 ,P 7 7 N可 以应 用在 欧洲 、美 国和 日本 不 同 的 F 波 段 环境 ,主要 应用 在 0 S36H M P / 4领域 。市 场前 景非 常好 。 M3MP

无 锡硅 动 力微 电子 股 份 有 限公 司坐 落 于无 锡 国家 高新 技术 产 业 开发 区珠 江 路 5 号 ,占地 面积 2 1 0亩 , 建 筑 面积 50 00平方 米 , 有 员工 19人 , 现 4 是一 家 以集成 电路设 计 、 试 、 测 销售 为 主营 的高科 技 民营企业 。 公 司前 身无 锡 硅动 力微 电子 有 限公 司成 立 于 2 0 03年 6月 ,07年 2月引 进 战略 投 资者 , 成 股份 制改 20 完 造 。凭 借 国家集 成 电路 设计 基 地之 一 的无 锡 地 区强 大 的半 导体产 业 链 支撑 , 以及公 司核 心 团 队成 员 具 有 的 大规 模集 成 电路研 发 、 生产 及经 营 的多年 实 践经 验 和技术 积 累, 司 自成 立 以来 实现 了大 幅度跨 越 式发 展 。 公 目前公 司 是无 锡集 成 电路设 计 产 业 化基 地 的 骨干 企业 ,03年 1 被 省科 技 厅 认 定 为江 苏 省高 新技 20 2月 术 企业 ,0 5年 6月通 过 IO 0 1的质 量 体 系认 证 ,05年 1 被 国家 信 息产 业 部 认 定 为集 成 电路 设 计 20 S 90 20 2月 企业 ,0 6年度 被 评为无 锡 市 十大集 成 电路设 计企 业称 号 ,并获得 了 2 0 —0 6年 度 中 国半 导体 产 品 和技 20 05 20 术创 新 奖 。公 司充 分 发挥 功率 集 成 、 数模 混合 的技术 优 势 , 以市 场 为 导 向 , 发拥 有 自主知 识产 权 的 优质 产 开 品, 以最优 的性 能价 格 比来满 足市 场 的需求 。开发 产 品涉及 电源管 理 、 响 、 信 、 音 通 马达控 制 、 车 电子 、 汽 电量

(整理)SP3767HN低功耗立体声收音机电路.

第九章、SP3767HN 低功耗立体声收音机电路一、概述:SP3767HN 是一片低功耗电调谐调频立体声收音机电路,其内部集成了中频选频和解调网络,可以做到完全免调,因此只需要很少量的小体积外围元件。

SP3767HN 可以应用在欧洲、美国和日本不同的FM 波段环境。

二、管脚说明:32.768KHzor四、极限参数:最大绝对额定值:(IEC 60134)七、典型应用:(1)应用线路图or应用图元件清单八、封装外形:HVQFN40:带散热片的塑料扁平封装;无引线;40 管脚;体积6*6*0.9mm九:附件(1): I 2C-总线说明I 2C 总线是通过二根线(串行数据线和串行时钟线)来连接器件之间通信的总线,并根据地址识别每个器件。

启动总线后的第一个字节的高七位是从器件的寻址IC 的地址为C0:1100000 。

I 2C 总线的逻辑结构:收发机。

最低位未使用。

最大低电平和最小高电平分别限定在0.2VCCD 和0.45VCCD。

总线模式(BUSMODE)引脚必须接地时工作在I2C-总线模式注:总线工作在最大时钟频率为400KHz,不能连接IC到一个正工作在高时钟的总线上。

(2):数据传输数据顺序:地址,字节1,字节2,字节3,字节4,字节5(数据传送必须按顺序)。

地址最低位为“0”,表示写操作到SP3767。

每个字节的第七位被认为是最高位,并作为字节的第一位传送。

在时钟的下降沿,数据变为有效信号。

在每一字节后面的停止信号可以缩短传送时间。

在整个传输完成之前发送一个停止条件:保留的字节将包含以前的信息。

如果一个字没有传送完,新的字节将被使用,但新的调谐周期不会开始。

通过standby位设置,芯片可以工作在省电的待机模式;总线仍然激活。

屏蔽总线界面可以减小待机电流。

如果总线界面被屏蔽则程序没有待机模式,芯片维持正常工作,但已经脱离总线。

软口1能够被用作调谐指示器输出,在搜台没有完成的时候,软口1输出低电平。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第九章、SP3767HN 低功耗立体声收音机电路

一、概述:

SP3767HN 是一片低功耗电调谐调频立体声收音机电路,其内部集成了中频选频和解调网络,可以做到完全免调,因此只需要很少量的小体积外围元件。

SP3767HN 可以使用在欧洲、美国和日本不同的FM 波段环境。

二、管脚说明:

32.768KHzor

四、极限参数:

最大绝对额定值:(IEC 60134)

七、典型使用:(1)使用线路图or

使用图元件清单

八、封装外形:

HVQFN40:带散热片的塑料扁平封装;无引线;40 管脚;体积6*6*0.9mm

九:附件

(1): I 2

C-总线说明I 2

C 总线是通过二根线(串行数据线和串行时钟线)来连接器件之间通信的总线,并根据地址识别每个器件。

启动总线后的第一个字节的高七位是从器件的寻址地址。

IC 的地址为C0:1100000 。

I 2

C 总线的逻辑结构:收发机。

最低位未使用。

最大低电平和最小高电平分别限定在0.2VCCD 和0.45VCCD。

总线模式(BUSMODE)引脚必须接地时工作在I2C-总线模式注:总线工作在最大时钟频率为400KHz,不能连接IC到一个正工作在高时钟的总线上。

(2):数据传输数据顺序:地址,字节1,字节2,字节3,字节4,字节5(数据传送必须按顺序)。

地址最低位为“0”,表示写操作到SP3767。

每个字节的第七位被认为是最高位,并作为字节的第一位传送。

在时钟的下降沿,数据变为有效信号。

在每一字节后面的停止信号可以缩短传送时间。

在整个传输完成之前发送一个停止条件:保留的字节将包含以前的信息。

如果一个字没有传送完,新的字节将被使用,但新的调谐周期不会开始。

通过standby位设置,芯片可以工作在省电的待机模式;总线仍然激活。

屏蔽总线界面

可以减小待机电流。

如果总线界面被屏蔽则程序没有待机模式,芯片维持正常工作,但已经脱离总线。

软口1能够被用作调谐指示器输出,在搜台没有完成的时候,软口1输出低电平。

当搜到预先设置的台或搜索完成或界定波段达到时,软口1输出高电平。

当第五字节最大有效位设置为逻辑1时,锁相环的参考频率改变。

调谐系统能够工作在XTAL2引脚接6.5MHz晶振。

(3):上电复位在上电复位时,静音位置“1”,其他所有位置“0”。

为了初始化集成块所有位必须重新

设定。

(4): I 2

C-总线协议

表1:写模式S(1)

地址(写) A(2)

数据位

A(2)

P(3)

注意:1:S 为启动条件。

2:A 为应答信号。

3:P 为停止条件。

表2:读模式

S(1)

地址(读)

A(2)

数据位1

注意:1:S 为启动条件。

2:A 为应答信号。

表3:IC 地址位

注:1:读或者写模式

a) 0 对SP3767 写操作。

b) 1 对SP3767 读操作。

(5): 3-线说明3-线控制:写/读,时钟和数据线;工作在最大时钟频率为1MHz。

提示:通过standby位设置,芯片可以工作在省电的待机模式。

在待机模式下芯片必须设置在写模式。

在待机期间,当芯片设置为读模式时,芯片会保持数据。

屏蔽总线界面可以减小待机电流。

如果总线界面被屏蔽则程序没有待机模式,芯片维持正常工作,但已经脱离时钟和数据线。

(6):数据传输

数据顺序:地址,字节1,字节2,字节3,字节4,字节5(数据传送必须按顺序)。

在写/读控制的上升沿可以写数据到芯片。

在时钟的上升沿之前,数据必须为有效信号。

当时钟为低时可改变数据信号,在时钟的上升沿时数据被写入芯片。

在以开始二字节或每个字节之后,如果有新的开始信号,数据传输被停止。

在写/读控制的下降沿可以从芯片读数据。

当时钟为低时,写/读控制改变。

在写/读控制的下降沿数据端出现第一个字节的最大有效位。

在时钟下降沿移存数据,在上升沿读数据。

要实现两个连续的读或写操作,写/读必须固定在最少一个时钟周期。

当一个搜索调谐请求被发送时,芯片将自动开始搜索,搜索方向和搜索停止电平可以设置。

当搜到一个强度等于或大于停止电平时,调谐系统停止且准备好标志

位为高。

在搜索期间,当一个制式已经符合时,调谐系统停止且制式标志位为高。

在这种情况下准备好标志位也为高。

软口1能够被用作调谐指示器输出,在搜台没有完成的时候,软口1输出低电平。

当搜到预先设置的台或搜索完成或界定波段达到时,软口1输出高电平。

当第五字节最大有效位设置为逻辑1时,锁相环的参考频率改变。

调谐系统能够工作在XTAL2引脚接6.5MHz晶振。

(7):上电复位在上电复位时,静音位置“1”,其他所有位任意设置。

为了初始化集成块所有位必须重新设

定。

(8):写数据

表4:写模式

数据字节1

数据字节2

数据字节3

数据字节4

数据字节5

表5 数据字节1 的格式

表6 数据字节1 的各个位描述

表7 数据字节2 的格式

表8 数据字节2 的各个位描述

位号

符号

描述

7 到0

PLL[7:0]

设定用于搜索和预设的可编程频率合成器。

表9 数据字节3 的格式

表10 数据字节3 的各个位描述

表11:搜索停止标准设定

表12:数据字节4 的格式

表13:数据字节4 的各个位描述

表14:数据字节5 的格式

表15:数据字节5 的各个位描述

(9):读数据

表16:读模式

数据字节1

数据字节2

数据字节3

数据字节4

数据字节5

表17:数据字节1 的格式

表18:数据字节1 的各个位描述

表19:数据字节2 的格式

表20:数据字节2 的各个位描述

位号

符号

描述

7 到0

PLL[7:0]

设定用于搜索和预设后的可编程频率合成器设定结果。

表21:数据字节3 的格式

表22:数据字节3 的各个位描述

表23:数据字节4 的格式

表24:数据字节4 的各个位描述

表25:数据字节5 的格式

表26:数据字节5 的各个位描述

位号

符号

描述

7 到0

预留为扩展用,由内部置0。

(10):总线传输时间表27:数字电平和传输时间

符号参数条件最小值最大值单位数字输入

VIH 输入高电平 0.45VCCD −V VIL 输入低电平−0.2VCCD V 数字输出

Isink(L) 低电平吸收电流 500 −µA VOL 低电平输出电压IOL = 500 µA −450 mV 传输时间

I2C总线−400 kHz fclk

时钟输入频率

3-线− 1 MHz tHIGH 时钟高电平时间I2C总线 1 −µs

3-线300 −ns tLOW 时钟低电平时间I2C总线 1 −µs

3-线300 −ns tW(write) 写操作脉冲宽度 3-线 1 −µs tW(read) 读操作脉冲宽度 3-线 1 −µs tsu(clk) 时钟建立时间 3-线300 −ns

读操作数据输出控制时

th(out)

3-线10 −ns 间

td(out) 读操作输出延迟时间3-线−100 ns tsu(write) 写操作建立时间 3-线100 −ns th(write) 写操作控制时间 3-线100 −ns。