Verilog逻辑设计实例系列一解析

Verilog 语言教程(逻辑及语法部分)

a b #2 c d #3

a

b #2 c

#3

d

#4

e

总延迟=Max{2,3}+4=7

时钟周期必须 > 7ns

总延迟= {Max{2,3}+4+1}=8

时钟周期必须 > 4ns

总处理数据的吞吐量增加

e

#1

#4

#1

22

为什么要设计有限状态机?

如果能严格以时钟跳变沿为前提,按排好时时序, 来操作逻辑系统中每一个开关Si,则系统中数据 的流动和处理会按同一时钟节拍有序地进行,可 以控制冒险和竞争现象对逻辑运算的破坏,时延 问题就能有效地加以解决。

寄存器间数据流动的控制开关

开关S1

组合逻辑

开关S2

dddd qqqq

dddd qqqq

组合逻辑

dddd qqqq

clock

2021/7/13

寄存器1

寄存器2

寄存器3

17

开关逻辑应用举例

寄存器间数据流动的控制开关

开关S1

dq clock

寄存器A

开关S2

2021/7/13

开关S3

dq

寄存器B

开关S4

开关S5

- 时序逻辑: 由多个触发器和多个组合逻辑块组成的网

络。常用的有:计数器、复杂的数据流动控制逻辑、运算 控制逻辑、指令分析和操作控制逻辑。同步时序逻辑的设 计是设计复杂的数字逻辑系统的核心。

- 存储器和寄存器:用于暂时存储数据信息。

2021/7/13

4

组合逻辑举例之一

一个八位数据通路控制器

`define ON 1 ‘b 1 `define OFF 1 ‘b 0 wire ControlSwitch; wire [7:0] out, in; assign out = (ControlSwith== `ON) ? in : 8 ‘h00

verilog组合逻辑写法

verilog组合逻辑写法Verilog是一种硬件描述语言(HDL),用于设计数字电路。

在Verilog 中,组合逻辑是指基于输入值瞬间计算输出的逻辑。

本文将详细介绍Verilog中常用的组合逻辑写法和技巧,帮助读者更好地理解和运用该语言。

一、Verilog中的基本逻辑门Verilog中有几种基本逻辑门,包括AND门、OR门、NOT门和XOR门。

这些门可以通过逻辑表达式来表示,例如:- AND门:使用符号“&”表示,例如A & B表示A与B的逻辑与操作。

- OR门:使用符号“|”表示,例如A | B表示A与B的逻辑或操作。

- NOT门:使用符号“~”表示,例如~A表示A的逻辑非操作。

- XOR门:使用符号“^”表示,例如A ^ B表示A与B的逻辑异或操作。

二、组合逻辑的例子下面给出一些常见的组合逻辑例子,以便读者更好地理解Verilog 中的写法。

1. 4位全加器:```verilogmodule Full_Adder(input a, input b, input carry_in,output sum, output carry_out);wire xor1, xor2, and1, and2;xor xor1_inst(.a(a), .b(b), .o(xor1));xor xor2_inst(.a(xor1), .b(carry_in), .o(sum)); and and1_inst(.a(a), .b(b), .o(and1));and and2_inst(.a(xor1), .b(carry_in), .o(and2)); or or_inst(.a(and1), .b(and2), .o(carry_out)); endmodule```2. 2:1多路选择器:```verilogmodule Mux2_1(input a, input b, input select,output out);wire not_select;not not_inst(.a(select), .o(not_select));and and1_inst(.a(a), .b(not_select), .o(out1));and and2_inst(.a(b), .b(select), .o(out2));or or_inst(.a(out1), .b(out2), .o(out));endmodule```以上示例仅为演示Verilog中的组合逻辑写法,并不包括完整的模块连接等细节。

verilog 组合逻辑例子

verilog 组合逻辑例子(原创版)目录1.引言2.Verilog 组合逻辑概述3.Verilog 组合逻辑设计方法4.补码转换和七段译码逻辑设计示例5.条件选择和多路开关逻辑设计6.寄存器和组合逻辑电路的优化7.总结正文1.引言Verilog 是一种硬件描述语言,广泛应用于数字电路和系统级设计领域。

在 Verilog 中,逻辑电路可以分为组合逻辑和时序逻辑两类。

组合逻辑电路是指在任何时刻,输出信号仅依赖于当前输入信号的电路。

本文将介绍如何使用 Verilog 描述组合逻辑电路,并通过实际例子来说明组合逻辑的设计方法。

2.Verilog 组合逻辑概述在 Verilog 中,组合逻辑电路主要使用 assign 语句进行描述。

assign 语句可以对一个或多个 net(线网)进行连续赋值,等价于门级描述。

此外,case 语句也可以用于组合逻辑电路的设计,可以实现多路选择等功能。

3.Verilog 组合逻辑设计方法在设计组合逻辑电路时,可以采用以下方法:(1)使用真值表:真值表是一种表格,用于表示输入信号和输出信号之间的对应关系。

通过真值表,可以找到组合逻辑电路的逻辑表达式。

(2)使用逻辑表达式:逻辑表达式是一种用逻辑运算符(如与、或、非等)描述电路功能的数学表达式。

通过逻辑表达式,可以进一步用Verilog 描述组合逻辑电路。

(3)使用逻辑门电路图:逻辑门电路图是一种用逻辑门(如与门、或门、非门等)表示电路功能的图形化表示方法。

通过逻辑门电路图,可以直观地描述组合逻辑电路。

4.补码转换和七段译码逻辑设计示例补码转换和七段译码器是组合逻辑电路的典型应用。

补码转换是将二进制数转换为补码表示的电路,七段译码器是将二进制数转换为七段显示器可显示的编码。

例如,对于一个 4 位二进制数,其补码表示为:ABC~D。

其中,A、B、C、D 分别表示 4 位二进制数的最高位、次高位、次次高位和最低位。

通过 Verilog 代码,可以实现补码转换和七段译码功能。

verilog 类 实例

verilog 类实例Verilog类是一种硬件描述语言,用于描述和设计数字电路。

它是一种基于事件驱动的语言,主要用于描述电子系统中的逻辑电路和时序电路。

本文将介绍Verilog类的基本概念和用法,以及如何使用Verilog类来实现数字电路设计。

我们来了解一下Verilog类的基本结构。

Verilog类由模块(module)、端口(port)、信号(signal)和过程块(always block)组成。

模块是Verilog类的最基本单位,用于封装和组织电路的功能。

端口是模块与外部环境之间的接口,用于输入和输出数据。

信号是数字电路中的数据流,用于表示电路内部的状态和数据。

过程块是Verilog类中的关键部分,用于描述电路的行为和逻辑。

在Verilog类中,我们可以使用各种语句和运算符来实现电路的功能。

例如,我们可以使用赋值语句(assign)来给信号赋值,使用条件语句(if-else)来实现逻辑判断,使用循环语句(for、while)来实现重复操作。

此外,Verilog类还支持多种逻辑运算符和算术运算符,如与(and)、或(or)、非(not)、加(add)、减(subtract)等。

Verilog类的一个重要应用是设计和实现各种数字逻辑电路,例如加法器、乘法器、寄存器、计数器等。

下面以一个简单的全加器为例来说明Verilog类的使用。

全加器是一种常用的组合逻辑电路,用于实现两个二进制数的相加操作。

它由两个半加器和一个或门组成。

每个半加器用于计算两个输入位的和(Sum)和进位(Carry),而或门用于将两个半加器的进位相加得到最终的进位。

以下是一个使用Verilog类实现的全加器的代码示例:```module FullAdder(input A, input B, input Cin, output Sum, output Cout);wire S1, C1, C2;HalfAdder HA1(.A(A), .B(B), .Sum(S1), .Carry(C1));HalfAdder HA2(.A(S1), .B(Cin), .Sum(Sum), .Carry(C2));or Gate(.A(C1), .B(C2), .Y(Cout));endmodulemodule HalfAdder(input A, input B, output Sum, output Carry);assign {Carry, Sum} = A + B;endmodule```在上述代码中,FullAdder模块是一个顶层模块,它实例化了两个HalfAdder模块和一个或门。

verilog 组合逻辑例子

verilog 组合逻辑例子Verilog组合逻辑例子Verilog是一种硬件描述语言,常用于数字逻辑综合和编写硬件模块。

组合逻辑是Verilog中的一种基本类型,用于描述没有存储功能,只有输入和输出之间逻辑关系的电路。

以下是一些Verilog组合逻辑例子及其详细讲解。

1. 逻辑门AND门module and_gate(input a,input b,output y);assign y = a && b;endmodule在这个例子中,我们定义了一个AND门的模块。

它有两个输入a 和b,一个输出y。

通过assign语句,我们将输出y赋值为输入a和b 的逻辑与结果。

OR门module or_gate(input a,input b,output y);assign y = a || b;endmodule这是一个OR门的例子。

和AND门类似,我们通过assign语句将输出y赋值为输入a和b的逻辑或结果。

2. 多路选择器module mux(input a,input b,input c,input d,input [1:0] sel,output y);assign y = (sel == 2'b00) ? a :(sel == 2'b01) ? b :(sel == 2'b10) ? c :d;endmodule这个例子演示了一个4路多路选择器。

它有4个输入a、b、c和d,一个2位选择信号sel,一个输出y。

根据选择信号的不同值,输出y将根据如下规则选择不同的输入信号:00选择a,01选择b,10选择c,11选择d。

3. 比较器module comparator(input [3:0] a,input [3:0] b,output eq,output gt,output lt);assign eq = (a == b);assign gt = (a > b);assign lt = (a < b);endmodule上面的例子展示了一个比较器。

verilog hdl应用程序设计实例精讲

verilog hdl应用程序设计实例精讲网上现在有很多关于verilog hdl应用程序设计的资料,但是并没有一个很系统和全面的教程来帮助初学者快速入门。

本文就verilog hdl应用程序设计实例进行了精讲,从基本概念到应用实例一步一步地回答了初学者的问题,帮助大家理解verilog hdl的设计和应用。

一、verilog hdl的基本概念Verilog HDL是一种硬件描述语言,用于描述数字系统,包括逻辑电路、集成电路等等。

它既可以进行仿真验证,也可以直接生成硬件电路。

简单来说,verilog hdl就是一种用来描述数字系统的语言。

1.1 模块与实例化在verilog hdl中,模块是最基本的设计单元,每个模块包含一个或多个端口和内部逻辑电路。

模块可以包含其他模块,这被称为实例化。

实例化可以理解为创建一个模块的实例,并根据实例进行连接。

1.2 端口和内部信号模块的端口是与其他模块或外部电路连接的接口,可以是输入、输出或双向。

内部信号是模块内部产生和使用的信号,只在模块内部可见。

1.3 组合逻辑与时序逻辑组合逻辑是指只有输入信号改变时才会改变输出信号的逻辑电路,而时序逻辑是指输出信号的改变还受到时钟信号的控制。

在verilog hdl中,可以使用逻辑门、逻辑运算符和条件语句来实现组合逻辑和时序逻辑。

二、verilog hdl应用程序设计实例接下来,我们通过一些实例来展示verilog hdl的应用程序设计。

2.1 4位全加器我们首先来实现一个4位全加器。

全加器是用来实现两个二进制数的加法的电路,它能够实现两个输入和一个进位的相加操作,输出结果和进位。

在verilog hdl 中,可以使用逻辑运算符和条件语句来实现全加器。

2.2 4位加法器我们可以使用四个全加器来实现一个4位加法器。

加法器是用来实现两个二进制数的加法的电路,它能够实现多位的相加操作,输出结果和进位。

2.3 4位计数器计数器是一种能够实现计数功能的电路,它能够根据时钟信号进行计数,并在达到一定数值时输出特定信号。

verilog 组合逻辑例子

verilog 组合逻辑例子(原创实用版)目录1.引言2.Verilog 组合逻辑简介3.Verilog 组合逻辑设计举例4.总结正文1.引言Verilog 是一种硬件描述语言,主要用于数字系统硬件的描述和仿真。

在 Verilog 中,组合逻辑电路是一种重要的逻辑电路类型,它可以根据输入信号的当前状态来产生稳定的输出信号。

本文将介绍 Verilog 组合逻辑的相关知识,并通过一些例子来说明如何使用 Verilog 描述组合逻辑电路。

2.Verilog 组合逻辑简介组合逻辑电路是一种数字逻辑电路,其输出信号仅仅取决于输入信号的当前状态,与过去的输入信号无关。

组合逻辑电路具有两个特点:(1)由逻辑门电路组成,不含有任何的记忆元件;(2)电路是单向传输的,电路中不存在任何反馈回路。

在 Verilog 中,可以使用 assign 语句来描述组合逻辑电路。

assign 语句用于对线网进行赋值,等价于门级描述,但从更高的抽象层次对电路进行描述。

3.Verilog 组合逻辑设计举例以下是一个使用 Verilog 描述的组合逻辑电路例子,用于实现一个负数的补码转换功能:```verilogmodule compconv(a, acomp);input [7:0] a;output [7:0] acomp;wire [6:0] b;wire [7:0] y;assign b = ~a[6:0]; // 计算负数的反码assign y[6:0] = b[6:0]; // 计算负数的补码assign y[7] = a[7]; // 保留最高位为 1,表示负数assign acomp = y; // 输出补码endmodule```在这个例子中,我们首先计算输入信号 a 的反码,然后计算其补码,并将结果输出。

这个过程中,我们使用了 Verilog 的 assign 语句来描述组合逻辑电路。

4.总结通过以上例子,我们可以看到如何使用 Verilog 描述组合逻辑电路。

《Verilog设计实例》PPT课件

精选PPT

6

task sort2; inout [t:0] x, y; reg [t:0] tmp; if( x > y ) begin tmp = x; x = y; y = tmp; end endtask endmodule

精选PPT

7

[例4]. 比较器的设计实例(利用赋 值语句设计组合逻辑) module compare(equal,a,b); parameter size=1; output equal; input [size-1:0] a, b; assign equal =(a==b)? 1 : 0; endmodule

assign outvec= h? 4'b0111 : g? 4'b0110 : f? 4'b0101:

e? 4'b0100 : d? 4'b0011 :c? 4'b0010 : b? 4'b0001:

a? 4'b0000 : 4'b1000; assign none_on = outvec[3];

精选PPT

18

[例9]. 输出驱动器设计实例 三态输出驱动器设计方案之一: module trist1( out, in, enable); output out; input in, enable; assign out = enable? in: 'bz; endmodule

精选PPT

19

三态输出驱动器设计方案之二: module trist2( out, in, enable ); output out; input in, enable;

begin

if(clk)

q=data;

Verilog代码设计案例分析

Verilog代码设计案例分析

Verilog以其灵活性而得到大部分FPGA设计者的喜爱,然而有些时候,这些灵活性也带来一些小问题,因此我们要记住,电脑永远没人我们聪明,我们一定要提前知道代码会被综合成什幺样子。

下面举一个有趣的例子。

假如定义如下变量:

reg [4:0] wp;

reg [4:0] rp;

.

.

Always @(posedge rx_ll_clock)

Begin

if (rp == wp + 2)

full

else

full

..

end

从上面的代码可以看出,综合器应该综合一个触发器,一个加法器和一个比较器。

这里的触发器和加法器不多说了,问题就出在的比较器上。

按照我们的想法是当rp=0,wp=30时,full应该在时钟沿变为为1。

在项目设计时,FuncTIon仿真时就出现了问题,最终发现综合器的综合结果和我们预期的不一致,如下图所示.

很明显,综合的比较器位宽是[5:0]而不是我们期望的[4:0]。

最终我们将红色部分修改如下:

if (rp == wp + 2)改为if (rp == wp + 5h02)

最终的综合结果变为我们所期望的结果:。

verilog优化逻辑的例子

verilog优化逻辑的例子Verilog是一种硬件描述语言,用于描述数字电路的行为和结构。

在设计数字电路时,优化逻辑是非常重要的,可以使电路具有更高的性能和更低的功耗。

下面列举了10个使用Verilog优化逻辑的例子。

1. 优化逻辑运算:在设计数字电路时,经常需要使用逻辑运算符,如与、或、非等。

通过合理地使用逻辑运算符,可以减少电路中门的数量,从而提高电路的性能和速度。

2. 优化布尔表达式:布尔表达式是用于描述逻辑电路的重要工具。

通过简化布尔表达式,可以减少电路中的逻辑门数量,从而提高电路的效率。

3. 优化时序逻辑:时序逻辑是一种特殊的逻辑电路,它的输出取决于输入信号的顺序和时序。

通过合理地设计时序逻辑,可以减少电路中的延迟,提高电路的速度和性能。

4. 优化组合逻辑:组合逻辑是一种不带时钟的逻辑电路,它的输出仅取决于当前的输入信号。

通过合理地设计组合逻辑,可以减少电路中的延迟和功耗,提高电路的性能。

5. 优化多输入逻辑:多输入逻辑是一种具有多个输入信号的逻辑电路。

通过优化多输入逻辑,可以减少电路中的逻辑门数量,提高电路的速度和功耗。

6. 优化状态机:状态机是一种用于描述电路行为的模型。

通过优化状态机的设计,可以减少电路中的逻辑门数量,提高电路的性能和速度。

7. 优化数据通路:数据通路是用于处理数据的路径,包括寄存器、加法器、乘法器等。

通过优化数据通路的设计,可以减少电路中的延迟和功耗,提高电路的性能。

8. 优化存储器设计:存储器是用于存储数据的电路,包括寄存器、RAM、ROM等。

通过优化存储器的设计,可以减少电路中的延迟和功耗,提高电路的性能。

9. 优化时钟频率:时钟频率是电路运行的速度,通过优化电路的设计,可以提高电路的时钟频率,从而提高电路的性能和速度。

10. 优化功耗:功耗是电路消耗的能量,通过优化电路的设计,可以减少电路中的功耗,提高电路的能效。

通过Verilog优化逻辑的设计,可以提高电路的性能和速度,减少电路的延迟和功耗,从而实现更高效的数字电路设计。

verilog优化逻辑的例子

verilog优化逻辑的例子以Verilog优化逻辑为例,我们将介绍10个优化技巧和实例,以帮助您更好地理解和运用Verilog语言。

1. 使用位运算代替乘法和除法在某些情况下,使用位运算可以替代乘法和除法操作,从而提高运算效率。

例如,将一个数乘以2可以使用左移操作来代替。

2. 使用位宽最小化在设计中,尽量使用最小的位宽来表示信号,以节省资源和提高性能。

例如,如果一个信号的最大值是15,那么可以使用4位来表示,而不是8位。

3. 使用优化的逻辑门在Verilog中,可以使用不同类型的逻辑门来实现相同的功能。

选择合适的逻辑门可以提高设计的性能和效率。

例如,使用与门和或门来实现逻辑与操作比使用与非门和与门的组合更有效率。

4. 使用分层次设计将复杂的逻辑模块划分为较小的子模块,可以提高设计的可读性和可维护性。

通过分层次设计,可以更容易地进行逻辑优化和调试。

5. 使用生成循环生成循环是一种强大的Verilog语言特性,可以用来生成重复的逻辑结构。

通过使用生成循环,可以减少冗余的代码,并提高设计的可维护性。

6. 使用选择语句代替多层if-else语句在某些情况下,使用选择语句(case语句)可以替代多层if-else 语句,从而提高代码的可读性和性能。

选择语句可以更清晰地表达逻辑关系,并且在硬件实现中更高效。

7. 使用寄存器代替连续赋值在Verilog中,连续赋值会导致逻辑的多次计算,从而降低性能。

为了提高性能,可以使用寄存器来保存中间结果,并在需要时进行赋值。

8. 使用常量和参数在设计中,使用常量和参数可以提高代码的可读性和可维护性。

通过将常量和参数定义在模块的顶部,可以方便地修改和调整设计参数。

9. 使用复位和使能信号在复杂的设计中,使用复位和使能信号可以控制模块的行为,从而提高设计的灵活性和可靠性。

通过使用复位信号,可以在系统启动时将模块重置到初始状态。

10. 使用状态机状态机是一种常用的设计模式,可以将复杂的逻辑结构分解为一系列简单的状态。

verilog编程实例

verilog编程实例我们需要明确这个电路的功能和设计要求。

假设我们需要实现一个4位二进制加法器,即输入两个4位的二进制数,输出它们的和。

为了简化问题,我们先考虑只有无符号整数的加法,即只需要实现两个正整数的相加。

接下来,我们可以使用Verilog语言来描述这个电路的结构和行为。

我们首先声明输入端口和输出端口的位宽,即4位。

然后,我们定义一个module,命名为"binary_adder"。

在这个module中,我们定义了两个4位的输入信号a和b,以及一个4位的输出信号sum。

同时,我们还定义了一个内部信号carry,用于记录进位信息。

在module的主体部分,我们使用assign语句来实现信号之间的逻辑关系。

具体地,我们可以通过逐位相加的方式,将输入信号a和b的每一位与进位carry相加,并将结果存储在输出信号sum的对应位上。

同时,我们还需要更新进位carry的值,以确保加法运算的正确性。

为了实现这个逻辑,我们可以使用Verilog中的加法运算符"+"和逻辑与运算符"&"。

通过对输入信号的每一位进行逐位运算,我们可以得到输出信号sum的每一位的值。

同时,我们还需要根据输入信号和进位carry的值,计算出新的进位carry的值。

在实际的Verilog编程中,我们需要注意信号的声明和赋值的顺序。

一般而言,我们需要先声明信号,然后再通过assign语句对信号进行赋值。

这样可以确保信号的值能够正确传递和计算。

完成Verilog代码的编写后,我们需要使用相应的仿真工具来验证电路的功能。

常用的仿真工具有ModelSim和Xilinx ISE等。

通过仿真工具,我们可以为输入信号a和b设置不同的值,并观察输出信号sum的变化。

通过比较输出信号sum和预期的结果,我们可以验证电路的正确性。

除了验证电路的正确性外,我们还可以通过综合工具将Verilog代码转换成对应的门级电路。

verilog时序逻辑和组合逻辑

verilog时序逻辑和组合逻辑

摘要:

1.组合逻辑简介

2.时序逻辑简介

3.组合逻辑与时序逻辑的区别

4.实例分析

5.总结

正文:

【1】组合逻辑简介

组合逻辑是数字电路设计中的基础部分,它主要研究如何使用布尔代数和逻辑门来实现数字逻辑电路。

组合逻辑电路的特点是,其输出仅依赖于当前时刻的输入,而与之前的输入状态无关。

简而言之,组合逻辑电路不需要考虑时间因素,只需关注输入与输出之间的关系。

【2】时序逻辑简介

时序逻辑是数字电路设计的另一个重要分支,它主要研究如何在电路中处理带有时间约束的逻辑问题。

时序逻辑电路的输出不仅依赖于当前时刻的输入,还与之前时刻的输入状态有关。

这使得时序逻辑电路的设计相比组合逻辑电路更为复杂。

【3】组合逻辑与时序逻辑的区别

组合逻辑和时序逻辑的主要区别在于对时间因素的处理。

组合逻辑不考虑输入信号的历史状态,而时序逻辑关注输入信号的历史状态对电路输出的影

响。

此外,组合逻辑电路的设计相对简单,而时序逻辑电路的设计则更为复杂。

【4】实例分析

以一个简单的触发器为例,触发器的输入信号为A、B,输出信号为Q。

在没有考虑时序约束的情况下,可以使用组合逻辑实现触发器。

但当需要满足一定的时间约束(如设置潜伏期和建立时间)时,组合逻辑无法满足要求,必须采用时序逻辑设计。

【5】总结

总之,组合逻辑和时序逻辑在数字电路设计中具有不同的应用场景。

组合逻辑适用于简单数字电路设计,关注输入与输出之间的关系;而时序逻辑适用于复杂数字电路设计,需要考虑时间约束。

VerilogHDL程序设计实例详解

6.2 SPI Master Controller设 计

6.2.3 串行接口层模块设计 4

6 SPI Master Controller实例

6.3.1 spi_top Testbench总体构架

1

6.3.2 模拟Wishbone master模块

及仿真波形

03

3.4.2 shift_divider Te s t b e n c h 设 计

3.4 移位除法器shift_divider 设计实例

04 4 编码器/译码器实例

4 编码器/译码器实例

4.1 二进制编码器bin_enc设计实 例

4.3 密勒译码器miller_de设计实例

4.2 曼彻斯特编译码器manch_ed 设计实例

03

3.3.3 booth_mult Te s t b e n c h 执 行 结果及仿真波形

3.3 布尔乘法器booth_mult 设计实例

3 乘法器/除法器实例

3.4.1 移位除法器 shift_divider设计

01

02

3.4.3 shift_divider Te s t b e nc h 执 行 结 果

02 2 加法器/计数器实例

2 加法器/计数器实例

2.1 1bit半加法器adder 设计实例

2.3 同步4bit全加法器 adder4设计实例

2.5 8bit BCD码计数器 count60设计实例

2.2 1bit全加法器 full_add设计实例

2.4 4bit计数器count4设 计实例

2 加法器/计数器实例

02

4.3.2 检测模块

signal_detect设计

03

4.3.3 signal_detect

verilog逻辑运算

verilog逻辑运算Verilog逻辑运算是数字电路设计中至关重要的一部分,它涵盖了许多基本的逻辑门和运算符,用于实现各种数字电路功能。

Verilog作为硬件描述语言,被广泛应用于FPGA和ASIC设计中。

在这篇文档中,我们将深入探讨Verilog逻辑运算的基本概念、常见逻辑门和运算符的使用,以及一些实际应用的例子。

## 1. Verilog逻辑运算基础Verilog逻辑运算基于数字电路的基本原理,其中包括逻辑门和布尔代数。

逻辑门是数字电路的基本构建块,而布尔代数则提供了描述逻辑运算的数学工具。

### 1.1 逻辑门逻辑门包括AND门、OR门、NOT门等,它们通过组合不同的输入信号产生输出信号。

在Verilog中,我们可以使用模块来表示逻辑门,例如:```verilogmodule AND_gate(output, input1, input2);output = input1 & input2;endmodule```这个例子中,`AND_gate` 模块接受两个输入 `input1` 和`input2`,并输出它们的逻辑与结果。

### 1.2 布尔代数Verilog中的逻辑运算也涉及到布尔代数,它使用逻辑运算符(如AND、OR、NOT)来描述和操作逻辑变量。

例如:```verilogassign result = (A & B) | (~C);```这个例子中,`result` 的值是A和B的逻辑与,再与C的逻辑非的结果。

## 2. 常见逻辑运算符Verilog提供了丰富的逻辑运算符,用于实现各种复杂的逻辑功能。

### 2.1 位运算符Verilog中的位运算符用于对数据的各个位进行操作,包括AND、OR、XOR等。

```verilogassign result = A & B; // 位与运算assign result = A | B; // 位或运算assign result = A ^ B; // 位异或运算```### 2.2 逻辑运算符逻辑运算符用于对整个逻辑值进行操作,包括AND、OR、NOT等。

verilog门电路组合简单设计例化

Verilog门电路组合简单设计例化一、引言在数字电路设计中,Verilog语言被广泛应用于门电路组合的设计和仿真。

门电路组合的设计是数字电路领域中的基础知识之一,对于理解数字电路的原理和应用至关重要。

本文将围绕Verilog门电路组合的简单设计例化展开讨论,从基础概念开始,逐步深入,帮助读者全面、深刻地理解这一主题。

二、Verilog语言简介Verilog是一种硬件描述语言(HDL),主要用于描述数字逻辑电路。

它类似于一种程序设计语言,但其目的是用于描述电子系统,而不是软件程序。

Verilog具有丰富的语法结构,可以描述从简单的门电路到复杂的集成电路的各个层次。

三、门电路组合简介门电路是数字电路领域的基础组成部分,它由与门、或门、非门等基本逻辑门构成。

组合电路是一种数字电路,它的输出完全取决于当前输入状态,与电路的历史状态无关。

门电路组合设计就是通过组合这些基本的逻辑门,构建出完成特定逻辑功能的电路。

四、Verilog门电路组合的设计流程1. 确定功能需求:首先需要明确要设计的门电路要实现什么功能,比如加法器、减法器、比较器等。

2. 逻辑设计:根据功能需求,进行逻辑设计,确定需要用到的基本逻辑门,以及它们之间的连接关系。

3. Verilog编写:利用Verilog语言描述逻辑设计,包括模块的定义、端口的声明、逻辑功能的描述等。

4. 仿真验证:通过仿真工具对Verilog代码进行仿真验证,确保设计符合预期的功能需求。

5. 综合与布局:进行逻辑综合和布局布线,将逻辑设计映射到实际的物理电路中。

6. 下载与测试:将设计好的Verilog门电路下载到目标芯片中进行测试,验证设计的正确性和稳定性。

五、深入理解Verilog门电路组合设计在Verilog门电路组合的设计过程中,需要注意以下几个重要的方面。

1. 模块化设计:在实际设计时,应该将功能模块化,保持清晰的模块划分,利用模块化的设计思想,可以提高设计的可维护性和可重用性。

verilog优化逻辑的例子

verilog优化逻辑的例子Verilog是一种硬件描述语言,用于描述数字逻辑电路。

在设计和实现数字逻辑电路时,优化逻辑是至关重要的。

通过优化逻辑可以提高电路的性能、减少功耗、降低成本等。

下面列举了10个以Verilog优化逻辑的例子。

1. 使用位移操作代替乘法运算:在一些情况下,乘法运算需要大量的硬件资源,可以使用位移操作来代替乘法运算,从而减少硬件资源的使用。

2. 使用并行操作代替串行操作:在一些情况下,串行操作需要较长的延迟时间,可以使用并行操作来代替串行操作,从而减少延迟时间。

3. 优化状态机:对于复杂的状态机,可以通过精简状态转移图或者使用更高效的状态编码方式来优化状态机的逻辑。

4. 使用查找表代替复杂的逻辑判断:对于一些复杂的逻辑判断,可以使用查找表来代替,从而简化逻辑电路。

5. 使用流水线技术:对于一些需要处理大量数据的电路,可以使用流水线技术将处理过程划分为多个阶段,从而提高电路的吞吐量。

6. 使用FIFO缓冲区:在一些需要缓存数据的电路中,使用FIFO缓冲区可以有效地管理数据的输入和输出,提高电路的处理能力。

7. 使用复用器和选择器:在一些需要多路复用和选择的电路中,使用复用器和选择器可以减少硬件资源的使用,简化电路的逻辑。

8. 使用加法器代替减法器:在一些需要进行减法运算的电路中,可以通过转换运算表达式,使用加法器来代替减法器,从而减少硬件资源的使用。

9. 使用编码器和解码器:在一些需要进行编码和解码的电路中,使用编码器和解码器可以简化逻辑电路,降低硬件资源的使用。

10. 使用异步时序逻辑:在一些需要处理异步信号的电路中,使用异步时序逻辑可以提高电路的响应速度和稳定性。

通过以上的优化技术,可以有效地提高数字逻辑电路的性能和效率。

在实际应用中,根据具体的设计需求和资源限制,选择适合的优化技术进行逻辑优化,可以使电路更加高效、可靠和经济。

Verilog逻辑设计实例系列.ppt

简化的状态机的例子(续)

实际上,这个状态机就是你自己。你可能处于下 列三个状态之一:睡眠中,醒了但还在床上,或起床。 你接受两个输入:唤你醒来的闹钟和当天是否是工作日, 后者决定你对闹钟的反映态度。在这个例子中,唯一的 输出就是关掉闹钟。(这里假设你不弄坏闹钟;如果弄 坏闹钟,这个例子就需要一个“弄坏闹钟”的输出)

历史视角:有限状态机和微处理器

微处理器有三个主要部分:寄存器,算术逻 辑单元和控制单元。控制单元输入将被执行的指 令和其他的信息,如标志寄存器的值。控制单元 输出控制信号以便加载和修改寄存器的内容,执 行算术逻辑功能,存取存储器和输入/输出设备。 它按照适当的顺序输出这些信号,以便微处理器 正确读取,译码和执行每条指令。

收费站控制器(续)

收费站有两个输出灯和一个输出警铃。当车 开进收费站,红灯(R)亮,直到司机投入至少 35分为止,此时红灯灭并且绿(G)灯亮。当 汽车离开收费站的时候,绿灯灭,红灯又亮。如 果汽车没有交足费用就离开收费站,则红的一直 亮并且警铃响。直到另一辆车进入收费站时,警 铃才关闭。

该系统需要几个状态来对应已经列出的条件。 另外它还要几个额外的状态来跟踪已投入了多少 钱。下面列表描述有限状态机的状态以及它们的 输出。

收费站控制器状态

状态

SNOCAR S0 S5 S10 S15 S20 S25 S30 SPAID SCHEAT

条件 站中无车 站中有车,已付费0分 站中有车,已付费5分 站中有车,已付费10分 站中有车,已付费15分 站中有车,已付费20分 站中有车,已付费25分 站中有车,已付费30分 站中有车,已付费35分 未付满过站费车就离开收费站

微处理器的控制单元本质上是一个有限状态 机。指令和标志值是状态机的输入,控制信号是 状态机的输出。

Verilog逻辑设计实例系列一

or

M3 (c_out,w2,w3);

endmodule

Add_half_0_delay的完整描述如下所示:

module Add_half_0_delay (sum,c_out,a,b);

output input

sum, c_out; a,b;

xor

M1 (sum,a,b);

and

M2 (c_out,a,b);

第三部分 实践篇

设计实例系列(一) Verilog 逻辑设计介绍

1. 半加器的原理图及其Verilog描述

module Add_half_0_delay (sum,c_out,a,b);

input

a,b;

output

c_out,sum;

xor

(sum,a,b);

and

(c_out,a,b);

endmodule

w1,w2,w3;

Add_half_0_delay M1 (w1,w2,a,b);

Add_half_0_delay M2 (sum,w3,c_in,w1);

or

(c_out,w2,w3);

endmodule

模块可以嵌套在其他模块内,但不能以循环 方式嵌套。当一个模块被其他模块引用时,结构 化层次就形成了嵌套和被嵌套的设计结果,这种 层次形成了一种划分,并且表示了引用嵌套和被 嵌套之间的关系。引用模块称为父模块,被引用 的模块称为子模块,即包含子模块的模块是父模 块。

endmodule

Add_rca_16 Add_rca_4 Add_rca_4 Add_rca_4 Add_rca_4

Add_full Add_full

Add_full Add_full

verilog分享 verilog快速掌握之模块例化

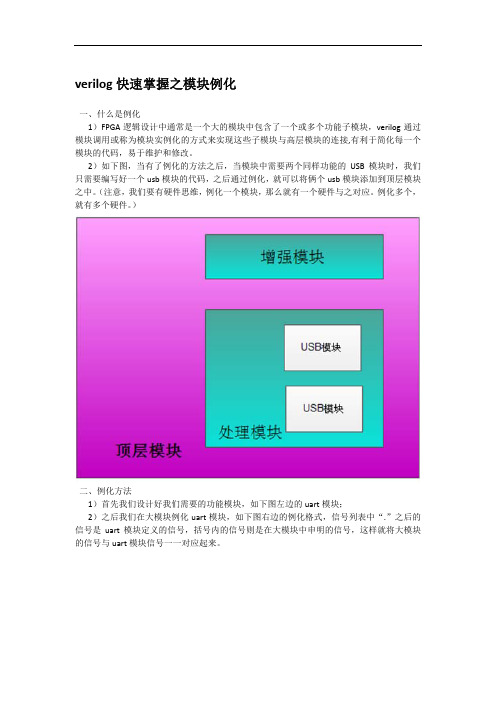

verilog快速掌握之模块例化一、什么是例化1)FPGA逻辑设计中通常是一个大的模块中包含了一个或多个功能子模块,verilog通过模块调用或称为模块实例化的方式来实现这些子模块与高层模块的连接,有利于简化每一个模块的代码,易于维护和修改。

2)如下图,当有了例化的方法之后,当模块中需要两个同样功能的USB模块时,我们只需要编写好一个usb模块的代码,之后通过例化,就可以将俩个usb模块添加到顶层模块之中。

(注意,我们要有硬件思维,例化一个模块,那么就有一个硬件与之对应。

例化多个,就有多个硬件。

)二、例化方法1)首先我们设计好我们需要的功能模块,如下图左边的uart模块;2)之后我们在大模块例化uart模块,如下图右边的例化格式,信号列表中“.”之后的信号是uart模块定义的信号,括号内的信号则是在大模块中申明的信号,这样就将大模块的信号与uart模块信号一一对应起来。

三、参数例化1) 模块例化还有一个好处就是在调用的时候还可以传递/改变参数。

如下图,我们设计了一个uart模块,他的数据位宽只有8位,但是如果我们需要一个16位宽的uart模块,这时候我们可以通过参数例化来减少重新编写模块的工作量。

2)我们定义数据位宽为DATA_W=83)在例化的时候我们可以如下图,在模块名后面加上“#(.DATA_W(16))”,就可以将数据位宽定义为16位。

注意,大家务必掌握参数传递的方法,点拨FPGA课程后面有一部分练习要计时到1秒时间,如果modelsim真的要仿真1秒,跑一个用例就要花费好几分钟或者几个小时,这样的低效率是难以忍受的。

我们仿真时,在测试文件改变1秒的参数值,将它变得很小,这样就能加快仿真迅速。

详细情况,学到相应章节自然会清楚的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1. 半加器的原理图及其Verilog描述

module Add_half_0_delay (sum,c_out,a,b);

input

output xor and endmodule

a,b;

c_out,sum; (sum,a,b); (c_out,a,b);

4.下图所示的二进制全加器电路。 附加了_0_delay的模块表明没有考虑传播延时。

4.1全加器门级电路原理图

4.2全加器Verilog模型

module Add_full_0_delay(sum,c_out,a,b,c_in); input a, b, c_in; output sum, c_out; wire w1,w2,w3; Add_half_0_delay M1 (w1,w2,a,b); Add_half_0_delay M2 (sum,w3,c_in,w1); or (c_out,w2,w3); endmodule

Add_rca_4_的完整描述如下所示:

module Add_rca_4 (sum, c_out, a, b, c_in);

output [3:0] output input [3:0] input wire Add_full M1 Add_full M2 Add_full M3 Add_full M4 endmodule (sum[0], (sum[1], (sum[2], (sum[3], sum; c_out; a,b; c_in ; c_in2, c_in3, c_in4; c_in2, c_in3, c_in4, c_out, a[0], a[1], a[2], a[3], b[0], b[1], b[2], b[3], c_in1); c_in2); c_in3); c_in4);

Add_full

Add_full

Add_full

Add_full

Add_half

half

norf201

invf101

xor

nand

not

xor

nand

not

模块可以嵌套在其他模块内,但不能以循环 方式嵌套。当一个模块被其他模块引用时,结构 化层次就形成了嵌套和被嵌套的设计结果,这种 层次形成了一种划分,并且表示了引用嵌套和被 嵌套之间的关系。引用模块称为父模块,被引用 的模块称为子模块,即包含子模块的模块是父模 块。 如:零延时全加器Add_full_0_delay中 的两个零延时半加器Add_half_0_delay是 Add_full_0_delay的子模块。尽管模块内可 能包含其他的模块和基本门,但基本门中不能再 嵌套其他任何东西。

例1. 一个16位行波进位(ripple-carry)加法器

可由4个4位行波进位加法器级联而成,每个单元所产生 的进位从最低位开始逐次传递至下一级的进位输入端。每 个4位加法器都可视为是全加器的级联。下图说明了一个 零延时16位行波进位加法器Add_rca_16_0_delay的 层次划分和端口信号连接关系,该理想化模型忽略了门的 传播延时。

Add_full的完整描述如下所示:

module Add_full (sum, c_out, a, b, c_in); output input wire Add_full_0_delay Add_full_0_delay or endmodule sum; a,b, c_in; w1,w2,w3; M1 (w1,w2,a,b); M2 (sum,w3,w2,c_in); M3 (c_out,w2,w3);

图 (a)顶层 原理图符号

图 (b)分解为4个4位加法器

图4.7 (c)继续分解为全加器和半加器

Add_rca_16_0_delay的完整描述如下所示:

module Add_rca_16_0_delay (sum, c_out, a, b, c_in);

output [15:0] output input [15:0] input wire Add_rca_4 M1 Add_rca_4 M2 Add_rca_4 M3 Add_rca_4 M4 endmodule sum; c_out; a,b; c_in ; c_in4, c_in8, c_in12,c_out; (sum[3:0], c_in4, a[3:0], b[3:0], c_in); (sum[7:4], c_in8, a[7:4], b[7:4], c_in4); (sum[11:8], c_in12, a[11:8], b[11:8], c_in8); (sum[15:12], c_out, a[15:12], b[15:12],c_in12);

2 三输入与非门及其Verilog原语化举例

… nand(y,a,b,c); …

3.有5输入与非门(AOI)功能 的相互连接起来的基本门原语的声明

wire y1,y2; nor (y_out,y1,y2); and (y1,x_in1,x_in2); nand(y2,x_in3,x_in4,x_in5);

Add_half_0_delay的完整描述如下所示: module Add_half_0_delay (sum,c_out,a,b);

output input

xor and endmodule

sum, c_out; a,b;

M1 (sum,a,b); M2 (c_out,a,b);

Add_rca_16 Add_rca_4 Add_rca_4 Add_rca_4 Add_rca_4