ddr2信号和协议测试分析方案_图文

存储器技术-检验DDR, DDR2 和DDR3 SDRAM命令和协议

应用指南检验DDR, DDR2和DDR3 SDRAM 命令和协议跟上更加复杂、更短设计周期的步伐不只计算机存储器系统一直需要更大、更快、功率更低、物理尺寸更小的存储器,嵌入式系统应用也有类似的要求。

本应用指南介绍了逻辑分析仪在检验DDR, DDR2和DDR3 SDRAM命令和协议中的能力。

检验DDR, DDR2和DDR3 SDRAM 命令和协议应用指南表1. SDRAM 标准引言DRAM的异步操作特性在连接同步处理器时导致了许多设计挑战。

SDRAM (同步DRAM)采用专门设计,以实现DRAM 与计算机系统其余部分同步操作,而不需定义基于序列模式的存储器操作。

SDRAM 的技术演进,如DDR SDRAM,已经迅速提高了存储器的数据速率性能。

DDR, DDR2和DDR3 SDRAM 都通过从存储控制器主机向存储器发送的存储器命令进行控制。

DDR, DDR2和DDR3 SDRAM一直都有这样的需求,就是存储器要容量更大、速度更快、功耗更低以及物理尺寸更小。

这些需求推动着DRAM 技术的进步。

近几年中,主流DRAM 技术有很多主要提升,如SDRAM(同步DRAM),DDR(双数据率)SDRAM,DDR2(双数据率2)SDRAM,DDR3(双数据率3)SDRAM。

DDR(双数据率)SDRAM 通过提升时钟速率、猝发式数据以及在一个时钟内传输两个数据位,提升了内存的数据率性能。

DDR2(双数据率2)SDRAM在DDR的基础有一些进步。

DDR2 SDRAM 时钟速率更高,这样就增加了内存的数据速率。

但在时钟速率增长的情况下,可靠的内存处理对信号完整性的要求更为苛刻。

随着时钟速率增长,电路板上的信号路径变成了传输线,这样正确的布线和信号走线末端端接变得至关重要。

DDR3 SDRAM 是革命性的技术提升,它将SDRAM 速度推到了800Mb/s以上。

DDR3 SDRAM支持六种数据速率和时钟速度。

DDR3-800/1066/1333 SDRAM 在2007年实现,而DDR3-1600在2008年。

DDR、II、IIII 参数及协议和XDR 参数测量

2005

SDR 100 MT/s

2002

2000

设计信号完整性良好带来的好处 “我成了微波设计者!”

保证与不同厂商产品之间的互操作性 改进的设备性能 更多的设计裕量

Page 6

第6页

议程

DDR 存储器技术概述 DDR 探头连接的难点 新型 DDR BGA 探头适配器解决探测难点 DDR 协议验证难点和解决方案 DDR 参数测量难点和解决方案 XDR 参数难点和解决方案 问题和解答

FR4 FR4 FR4

JEDEC DDR 规范中并未提及信号上升/下降时间或者带宽技术指标。 示波器带宽需求是由上升时间决定的,而上升时间是由信号斜率和幅度决定的。使 用技术指标中的信息,可以计算出最快的上升时间。 尽管计算出的最快上升时间看上去对于芯片来说非常出色,但实际性能却非常低。 这是由于实际产品设计和制造中使用的比较便宜的 FR4 材料和连接器造成的。 实际的信号带宽会更低,因为高次谐波被滤掉。

写分离 - 边 沿没有对齐

读分离 - 边 沿是对齐的

InfiniiScan “区域隔离法”可轻松进行读和写分离

第31页

JEDEC DDR3 测试参数列表

技术指标 JESD79-3 DDR3 SDRAM 技术指标 测试参数

Vih(dc), Vil(dc), Vih(ac), Vih(dc) 表 26 – 单端交流和直流输入电平(第 103 页) VIHdiff, VILdiff 表 27 – 差分交流和直流输入电平(第 105 页) Vix 表 28 – 用于差分输入信号的交叉点电压(CK、DQS)(第 105 页) Voh(dc), Vom(dc), Vol(dc), Voh(ac), Vol(ac) 表 31 – 单端交流和直流输出电平(第 109 页) VOHdiff(ac), VOLdiff(ac) 表 32 – 差分输出斜率(第 109 页) SRQse 表 34 – 输出斜率(单端)(第 110 页) SRQdiff 表 36 – 差分输出斜率(第 111 页) 表 37 –用于地址和控制引脚的交流过冲/下冲技术指标(第 113 过冲区域最大峰值幅度、下冲区域最大峰值区域、 页) VDD 以上的最大过冲区域、VSS 以下的最大下冲区 域 表 38 – 用于时钟、数据、选通和模板的交流过冲/下冲技术指标 过冲区域最大峰值幅度、下冲区域最大峰值区域、 (第 114 页) VDDQ 以上的最大过冲区域、VSSQ 以下的最大下 冲区域 tCK(avg), tJIT(per), tJIT(cc), tERR(2per), 表 66 – Speed Bin 定时参数(第 153 页) tERR(3per), tERR(4per), tERR(5per), tERR(nper), tERR(nper2), tCH(avg), tCL(avg), tJIT(duty), tAC, tDQSCK, tDQSQ, tQH, tDQSS, tDSS, tDSH, tHZDQ, tHZDQS, tLZDQ, tLZDQS, tWPRE, tWPST, tRPRE, tRPST, tDQSH, tDQSL, tDS(base), tDH(base), tIS(base), tIH(base)

DDR与DDR-II深刻理解.

DDR 与DDR-IIDDR SDRAMDDR SDRAM全称为Double Data Rate SDRAM,中文名为“双倍数据流SDRAM”。

DDR SDRAM在原有的SDRAM的基础上改进而来。

图1一、DDR 的基本原理以MICRON的MT46V64M16(16 Meg x 16 x 4 Banks)为例,其时序图如下所示:图2 DDR读操作时序图从中可以发现它多了两个信号:CK#与DQS,CK#与正常CK时钟相位相反,形成差分时钟信号。

而数据的传输在CK与CK#的交叉点进行,可见在CK的上升沿与下降沿都有数据被触发,从而实现DDR。

在此,我们可以说通过差分信号达到了DDR的目的,甚至讲CK#帮助了第二个数据的触发,但这只是对表面现象的简单描述,从严格的定义上讲并不能这么说。

之所以能实现DDR,还要从其内部的改进说起。

图3 DDR内部结构图从图中可以看出,其前半部分与SDRAM的结构基本相同,红色框图部分即为比SDRAM多出的部分。

首先不同之处就是内部的Bank control logic规格。

SDRAM中Bank control logic存储单元的容量与芯片位宽相同,但在DDR中Bank control logic存储单元的容量是芯片位宽的一倍。

也因此,真正的行、列地址数量也与同规格SDRAM不一样了。

以本芯片为例,在读取时,Bank control logic在内部时钟信号的触发下一次传送32bit的数据给读取锁存器,再分成2路16bit 数据传给复用器,由后者将它们合并为一路16bit数据流,然后由发送器在DQS的控制下在外部时钟上升沿与下降沿分两次传输16bit的数据给北桥。

这样,如果时钟频率为100MHz,那么在I/O端口处,由于是上下沿触发,那么就是传输频率就是200MHz。

这种内部存储单元容量(也可以称为芯片内部总线位宽)=2×芯片位宽(也可称为芯片I/O 总线位宽)的设计,就是所谓的两位预取(2-bit Prefetch),有的公司则贴切的称之为2-n Prefetch(n代表芯片位宽)。

DDR2内存详解——从原理到测试

DDR2内存详解——从原理到测试作为PC不可缺少的重要核心部件——内存,它伴随着DIY硬件走过了多年历程。

从286时代的30pin SIMM内存、486时代的72pin SIMM 内存,到Pentium时代的EDO DRAM内存、PII时代的SDRAM内存,到P4时代的DDR内存和目前9X5、AM2平台的DDR2内存。

内存从规格、技术、总线带宽等不断更新换代。

不过我们有理由相信,内存的更新换代可谓万变不离其宗,目的在于提高内存的带宽,以满足CPU不断攀升的带宽要求、避免成为高速CPU的运算瓶颈。

随着CPU 性能不断提高,我们对内存性能的要求也逐步升级。

不可否认,紧紧依靠高频率提升带宽的DDR已经力不从心,因此JEDEC 组织提出了DDR2 标准,加上LGA775接口的主板以及最新的965、AM2 940等新平台全面对DDR2内存的支持,所以DDR2内存已经步入了它的春天。

DDR2(Double Data Rate 2) SDRAM是由JEDEC(电子设备工程联合委员会)进行开发的新生代内存技术标准,它与上一代DDR 内存技术标准最大的不同就是,虽然同是采用了在时钟的上升/下降中同时进行数据传输的基本方式,但DDR2内存却拥有两倍于上一代DDR内存预读取能力(即:4bit数据读预取)。

换句话说,DDR2内存每个时钟能够以4倍外部总线的速度读/写数据,并且能够以内部控制总线4倍的速度运行。

此外,由于DDR2标准规定所有DDR2内存均采用FBGA封装形式,而不同于目前广泛应用的TSOP/TSOP-II封装形式,FBGA封装可以提供了更为良好的电气性能与散热性,为DDR2内存的稳定工作与未来频率的发展提供了坚实的基础。

而在DDR参数基础上加入了新的三项参数标准我们首先来温习一下DDR内存参数标准。

(1)CAS(Column Address Strobe) Latency:列地址选通脉冲延迟时间,即DDR-RAM内存接收到一条数据读取指令后要延迟多少个时钟周期才执行该指令。

DDR2设计指导

DDR2设计指导目录1DDR2基本功能描述 (4)1.1DDR2电平 (5)2DDR2 PCB设计 (6)2.1常用拓扑结构 (6)2.1.1DIMM拓扑分析 (6)2.1.2颗粒拓扑分析 (6)2.2走线规则及时序 (7)2.2.1时序 (8)3仿真分析拓扑模板 ..................................................................................... 错误!未定义书签。

图目录图1OCD功能示意 (4)图2ODT可变更参数(EMRS表示内部寄存器) (5)图3电压标准 (5)图4过冲示意图 (5)图52T(左)、1T(右)模式2DIMM各信号流向描述 (6)图6地址拓扑结构 (7)图71驱4地址拓扑 (7)图8DDR2时序关系示意图 (8)1 DDR2基本功能描述DDR2(Double Data Rate 2)SDRAM是由JEDEC进行开发的新生代内存技术标准,它与上一代DDR内存技术标准的区别在于,虽然同是采用了在时钟的上升/下降沿同时进行数据传输的基本方式,但DDR2内存拥有两倍于上一代DDR内存预读取能力(即:4bit数据读预取),DDR2内存每个时钟能够以4倍外部总线的速度读/写数据,并且能够以内部控制总线4倍的速度运行。

DDR2内存采用SSTL_1.8电压标准,相对于DDR标准的SSTL_2.5,降低了不少,因而提供了明显的更小的功耗与更小的发热量,这一点的变化意义重大。

在继承了DDR的优点之外,DDR II新增了OCD、ODT和Post CAS三项功能。

OCD(Off-Chip Driver):也就是所谓的离线驱动调整,DDR II通过OCD可以提高信号的完整性。

DDR II通过调整上拉(pull-up)/下拉(pull-down)的电阻值使两者电压相等。

使用OCD 通过减少DQ-DQS的倾斜来提高信号的完整性;通过控制电压来提高信号品质。

DDR2 SDRAM仿真分析概要

DDR2 SDRAM仿真分析概要发布: 2008-7-05 06:08 | 作者: webmaster | 来源: 本站原创| 查看: 0次DDR2 SDRAM仿真分析概要随着存储器接口的数据速率越来越高,在接收端保证信号完整性和满足时序要求变得更加困难。

尤其是DDR2 SDRAM。

DDR2 SDRAM的数据传输高,延迟和设计容差少,建立时间、保持时间和偏移(Skew)时间都仅有几十皮秒。

本文介绍DDR2 SDRAM设计的简单原理,并讨论如何使用Cadence公司的Allegro工具对DDR2 SDRAM设计进行板级仿真。

DDR SDRAM的出现使传统的同步时钟方式转变成在时钟的上升沿和下降沿同时进行数据采样(图1)。

这种方式能够提供数据的传输速率,但对设计的延迟和时序提出了更严格的要求。

根据Micron公司的资料,数据率为533Mbps的DDR2 SDRAM大约允许585ps左右的板级设计容差。

如果扣除信号完整性和电源完整性的容差后,允许线路延迟的容差仅有30ps左右,因此仅采用数据线等长设计方法已无法符合要求。

图1:DDR SDRAM的源同步方式。

此外,DDR2 SDRAM采用ODT(On-Die Termination)工作模式(图2),即DDR2 SDRAM内部有终端电阻。

ODT 模式在活动状态下启动,在待机状态下关闭,以便降低信号的反射,提高信号质量,降低功耗。

不过,有必要对终端电阻是否适合进行验证。

图2:DDR2 SDRAM的ODT的结构。

DDR设计流程图3为DDR2 SDRAM应用的PCB设计流程,它表明了信号完整性和电源完整性的分析和布局布线之间的关系。

图3:DDR2 SDRAM的PCB设计和仿真流程。

DDR2 SDRAM应用的板级仿真高速电路的板级仿真包括板前仿真和板后仿真两部分。

板前仿真对电路的拓扑结构进行分析,先利用Allegro仿真工具对设计的层叠进行设计来满足阻抗要求,然后对整个电路板的电源噪声问题进行评估,选择合适的去耦电容来稳定电源信号,减少噪声。

DDR原理简介及相关测试ppt课件

Precharge可以对一个Bank进行操作或者对所有的Bank进行同步操作,具体的设定 通过A10,BA0,BA1,BA2来实现

整理ppt

10

Precharge operation

整理ppt

13

ODT—On Die Termination

On Die Termination功能即可以对DQ, DQS/DQS, RDQS/RDQS, and DM的终端 电阻进行开关,可以改善信号完整性。ODT通过EMRS来进行控制

整理ppt

14

Refresh operation

当 CLK的边沿触发到CS, RAS and CAS LOW and WE HIGH,Chip开始进入 Refresh operation,在Refresh之前所有的Bank都必须被预充电,从预充电命令到 Refresh命令执行的时间必须大于tRP。从一个refresh命令到另一个refresh命令的时 间要大于tRFC (Refresh周期),

整理ppt

6

CAS Latency: CAS潜伏期。CAS为列地址选通脉冲,在列地址确定之后就可以 传输数据,但是仍需要经过一段时间才会有数据发出,这段间隔的时间即为CAS 潜伏期,简写为CL。

Additive Latency:简称AL。在RAS命令之后会立即执行CAS命令,CAS命令发出 到被设备执行的时间则成为AL。

整理ppt

23

Setup time and Hold up time SPEC for DDR2

注:tIS(base),tIH(base)的值为当CLK/CLK#的Diff slew rate为2V/ns, adress/CMD 的slew rate为1V/ns的时候的基本值

DDRII测试规范 SOP

DDRII Test SOPRD/EE:Ada_ye2009-04-24一、DDRII 簡介DDR (Dual data Rate SDRAM)SDRAM : 同步动态随机存储器,一般可作以下分类: SDR: Single Data RateDDR: Double Data Rate,2-bit prefetchDDR2: Double Data Rate,4-bit prefetchDDR3: Triple Data Rate,8-bit prefetch在我们现在做的DDR EA test 中,我们一般测试的是DDR2和DDR3,其中主要是对笔记本内存条的Clock、Command、Data做信号验证性测试。

二、DDRII Test Signal 簡介CK .CK# (Clock): CK and CK# are differentiallock inputs. All address and control input signals are sampled on the crossing of the positive edge of CKand negative edge of CK#.CKE (Clock Enable): CKE HIGH activates, andCKE LOW deactivates. CKE must be maintainedHIGH throughout read and write accesses.CS# (Chip Select): All commands are maskedwhen CS is registered HIGH. CS provides forexternal. Rank selection on systems with multipleRanks. CS is considered part of the command code. RAS# : Row Address Strobe.CAS# : Column Address Strobe .WE# : Write Enable operate .BA0 - BA2(Bank Address Inputs):BA0 - BA2define to which bank an Active.A0 - A15 :Provide the address for Activecommands.DQS. DQS# (Data Strobe) :output with read data, input with write data. Edge-aligned with read data, centered in write data.DQ (Data Input/ Output) :Bi-directional data bus.三、DDR Test Plan1. Test conditonsRun 3D Marks:2. Test toolsM/B; DDR:型号、厂商、频率的选择均按照客户要求;Scope,Probe:带宽均在被测信号频率的5倍以上(DELL要求), 3.5倍以上(其他客户要求), 。

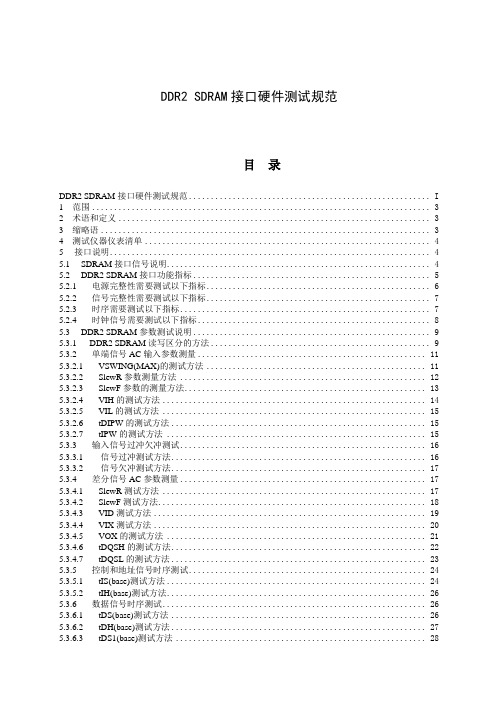

ddr2测试规范

DDR2 SDRAM接口硬件测试规范目录DDR2 SDRAM接口硬件测试规范 (I)1 范围 (3)2 术语和定义 (3)3 缩略语 (3)4 测试仪器仪表清单 (4)5 接口说明 (4)5.1 SDRAM接口信号说明 (4)5.2 DDR2 SDRAM接口功能指标 (5)5.2.1 电源完整性需要测试以下指标 (6)5.2.2 信号完整性需要测试以下指标 (7)5.2.3 时序需要测试以下指标 (7)5.2.4 时钟信号需要测试以下指标 (8)5.3 DDR2 SDRAM参数测试说明 (9)5.3.1 DDR2 SDRAM读写区分的方法 (9)5.3.2 单端信号AC输入参数测量 (11)5.3.2.1 VSWING(MAX)的测试方法 (11)5.3.2.2 SlewR参数测量方法 (12)5.3.2.3 SlewF参数的测量方法 (13)5.3.2.4 VIH的测试方法 (14)5.3.2.5 VIL的测试方法 (15)5.3.2.6 tDIPW的测试方法 (15)5.3.2.7 tIPW的测试方法 (15)5.3.3 输入信号过冲欠冲测试 (16)5.3.3.1 信号过冲测试方法 (16)5.3.3.2 信号欠冲测试方法 (17)5.3.4 差分信号AC参数测量 (17)5.3.4.1 SlewR测试方法 (17)5.3.4.2 SlewF测试方法 (18)5.3.4.3 VID测试方法 (19)5.3.4.4 VIX测试方法 (20)5.3.4.5 VOX的测试方法 (21)5.3.4.6 tDQSH的测试方法 (22)5.3.4.7 tDQSL的测试方法 (23)5.3.5 控制和地址信号时序测试 (24)5.3.5.1 tIS(base)测试方法 (24)5.3.5.2 tIH(base)测试方法 (26)5.3.6 数据信号时序测试 (26)5.3.6.1 tDS(base)测试方法 (26)5.3.6.2 tDH(base)测试方法 (27)5.3.6.3 tDS1(base)测试方法 (28)5.3.6.4 tDH1(base)测试方法 (30)5.3.6.5 tAC的测试方法 (32)5.3.6.6 tDQSCK的测试方法 (33)5.3.6.7 tDQSQ的测试方法 (34)5.3.6.8 tQH的测试方法 (35)5.3.6.9 tDQSS的测试方法 (36)5.3.6.10 tDSS的测试方法 (37)5.3.6.11 tDSH的测试方法 (38)5.3.6.12 tHZ的测试方法 (39)5.3.6.13 tLZ的测试方法 (40)5.3.6.14 tRPRE的测试方法 (42)5.3.6.15 tRPST的测试方法 (43)5.3.6.16 tWPRE的测试方法 (44)5.3.6.17 tWPST的测试方法 (45)5.3.7 时钟信号测试 (46)5.3.7.1 tCK(avg)的测试方法 (46)5.3.7.2 tCH(avg)/ tCL(avg)的测试方法 (47)5.3.7.3 Tj、Dj和Rj的测试方法 (47)5.3.7.4 tJIT(per)的测试方法 (48)5.3.7.5 tJIT(cc)的测试方法 (48)5.3.7.6 tJIT(duty)的测试方法 (49)5.3.7.7 tERR(nper)的测试方法 (49)6 测试内容 (50)6.1 电源完整性测试 (50)6.1.1.1 HS-DDR2 SDRAM-P-001 电源精度测试 (50)6.1.1.2 HS-DDR2 SDRAM-P-002 电源纹波测试 (51)6.1.1.3 HS-DDR2 SDRAM-P-003 电源上电波形测试 (53)6.1.1.4 HS-DDR2 SDRAM-P-003 电源上电时序测试 (53)6.2 信号完整性和时序测试 (54)6.2.1.1 HS-DDR2 SDRAM-S-001控制信号完整性测试 (54)6.2.1.2 HS-DDR2 SDRAM-S-002地址信号完整性测试 (55)6.2.1.3 HS-DDR2 SDRAM-S-003读操作数据信号完整性测试 (56)6.2.1.4 HS-DDR2 SDRAM-S-004写操作数据信号完整性测试 (56)6.3 时序测试 (58)6.3.1.1 HS-DDR2 SDRAM-T-001 读操作数据信号时序测试 (58)6.3.1.2 HS-DDR2 SDRAM-T-002 写操作数据信号时序测试 (59)6.3.1.3 HS-DDR2 SDRAM-T-003 控制信号时序测试 (60)6.3.1.4 HS-DDR2 SDRAM-T-004 地址信号时序测试 (60)6.4 时钟信号测试 (61)6.4.1.1 HS-DDR2 SDRAM-C-001 时钟信号波形测试 (61)6.4.1.2 HS-DDR2 SDRAM-C-002 时钟Jitter测试 (62)6.4.1.3 HS-DDR2 SDRAM-C-003 时钟精度测试 (63)7 引用 (63)1 范围本标准规定了DDR2 SDRAM接口的硬件测试方法和相关测试注意事项,并结合测试示例给以说明。

DDR 参数和协议测量

欢迎来到安捷伦数字测量论坛。

今天我们将讨论如何应对DDR 参数和协议测量的挑战;并讨论当今的一些工具,可以帮助您完成复杂的验证任务。

我们将采用互动对话的方式进行讨论,如果在我陈述过程中您有任何问题或需要进一步阐述,请随时打断我。

现在我们来看一下今天的议程。

首先,我们将迅速回顾DDR 存储器技术。

然后,我们将讨论您如今可能面对的DDR 探测的挑战,和解决这些挑战的新的BGA 探测解决方案。

之后,我们将讨论一些协议和参数测量挑战和解决方案。

最后,我们将讨论XDR 参数挑战和解决方案。

DDR 是一项普及的存储器技术,DDR存储器几乎无处不在。

试着看看周围,您会发现,做报告使用的投影仪里可能就有DDR 存储器,在放映之前它充当数字内容的缓冲器;您的手机也可能在使用DDR 存储器来快速存储和获取信息;甚至您的汽车和冰箱都借助DDR 存储器来存储信息。

本幻灯片中列举了一些使用DDR 设备的例子,在嵌入式设计中都可以发现它的身影,例如,高清晰电视(HDTV)、打印机、电话、投影仪、汽车、基站和许多消费产品;它同样出现在FPGA 设计中,FPGA 通常和DDR 接口结合使用;DDR 还出现在SO-DIMM 和常见DIMM 中,用于计算机内部的快速数据访问。

这是DDR 1、2、3 技术指标的大致比较。

随着DDR 技术的更新换代,其工作电压大幅下降。

由于每个人都知道要降低功耗,因此一些设计实际上采用的是在更低时钟频率上运行(非JEDEC 标准速度)的DDR 3。

下一代DDR 的时钟频率和数据传输率是上一代DDR 的两倍。

DDR 1 采用TSOP(薄型小尺寸)或BGA(球状栅格阵列)封装,DDR 2 和DDR 3 全部采用BGA 封装。

由于BGA封装将所有信号信号放到封装底部,要访问这些信号是一个很大挑战。

需要注意的是,新型DDR 技术无法向后兼容,其物理层和协议层与以往不同。

因此,您必须从性能和成本效益的角度考虑在设计中使用何种DDR 技术。

DDR测试技术介绍与工具分析

DDR测试技术介绍与工具分析DDR 是双倍数据速率的SDRAM 内存,如今大多数计算机系统、服务器产品的主流存储器技术,并且不断向嵌入式系统应用领域渗透。

孰不知,随着iPhone 等大牌智能手机的采纳,DDR 内存俨然成为智能手机转变的方向之一,例如韩国泛泰去年底最新推出的Android 智能手机Vega X 就搭载了512MB 的DDR2 内存。

DDR 技术不断发展,并行总线达到了串行技术的速度,时钟速度达到1GHz。

目前,DDR3 现在已经具备1.6Gb/s 的数据速率,而DDR3-1866 及更高速率版本正在开发中,很快就会出现在市场上。

目前主流的DDR2 也有多种速度、多种容量和多种规格,从DDR-266 的266MT/S、133MHz、2.5V 电压,已经发展到了现在的DDR2-1066 的1066MT/S、533MHz、1.8V 电压。

另外,低能耗DDR(LP-DDR,用于便携式计算机)和显存GDDR 也是DDR 的发展变化版本。

目前主流的DDR 也有多种速度、多种容量和多种规格,从DDR-266 的266MT/S、133MHz、2.5V 电压,已经发展到了现在的DDR3-1600,1.5V 电压。

另外,低能耗DDR(LP-DDR,用于便携式计算机)也是DDR 的发展趋势之一。

技术的升级和应用领域的拓展,都使DDR 存储器的验证和测试更具挑战性。

高数据速率和时钟速度使得时序余量更紧张,导致串扰、阻抗匹配和抖动问题加剧,这需要使用高速测试测量技术和性能更高的测试测量工具,以获得更好的信号捕获能力、测试精度等。

DDR 测试要点和难点鉴于DDR 的stub(短线)拓扑结构和紧张的时序容限,在验证和测试中要求检验多种指标,包括:电气电源和信号电源质量,噪声、毛刺和地弹/地跳;。

最新DDR 信号分析方法

最新DDR 信号分析方法现在示波器上的DDR 物理层信号分析方案,都是针对JEDEC 规范的一致性测试。

在这种方案中,分析软件会按照JEDEC 规范分析DDR 信号的各种参数,并判断测试结果Pass 或者Fail,最终生成一份报告。

但是很多的研发工程师,并不想仅仅获得一个Pass 或者Fail 的结果,而是想对信号做调试分析,但是传统的串行信号分析软件无法分析DDR 信号,为此,力科推出了新的DDR Debugtoolkit。

一,新的DDR 信号分析方法力科DDR Debug toolkit 提供了一种简单易用的DDR 信号调试工具,它快速的对数据做读写分离,形成读写眼图,对眼图进行模板测试和参数测试,对抖动进行分解,定位问题的根源,对比较重要DDR 参数进行测量,像建立时间、保持时间、TDQSCK 等,灵活设置参数,对DDR 信号问题进行调试,可以支持DDR2/DDR3/DDR4/LPDDR2/LPDDR3 等。

二,眼图测量可以同时产生和显示10 个眼图,对5 路DDR 信号进行分析,查看分析眼间的Skew 和时间信息,可以选择DQS 或者Clock 作为时间参考,自定眼图模板,Teledyne Lecroy进行眼图模板测试。

三,测量多个眼图参数: Eye Height Eye Width Eye Crossing Mask Hits Mask Out Eye Amplitude One Level Zero Level四,抖动测试像传统的串行信号分析一样,对DDR 信号的抖动进行测量分析,对抖动进行分解(Tj,Rj,Dj,DCD 等),从TIE Track、TIE Histogram、Bathbub Curve 观察分析抖动,更加深入的了解抖动的分布和源头。

五,DDR 参数测量对比较关键的DDR 参数进行测量,可以同时测量12 个参数,包括Max、Min,Mean 等统计值。

Bursts, transitions, Vref VH(ac), VH(dc), VL(ac), VL(dc) tDS, tDH, tIS, tIH tDQSQ, tDQSCK Slew Rise, Slew Falltips:感谢大家的阅读,本文由我司收集整编。

DDR信号测量方法及信号完整性验证面临的挑战与建议

1. DDR概述如今,存储器件在计算机、汽车与消费电子产品上可谓无所不在。

其中DDR SDRAM(双数据率同步动态随机存取存储器)是最常用的存储器设计技术之一,而随着该技术的发展,其传输速率在日益加快,功耗在日益降低。

传输速度加快使得此类存储器的验证难度呈指数上升。

存储系统要准确工作,其信号完整性必须满足某种最低要求。

因为信号完整性对系统互通性而言非常关键,或者说只有保持信号完整性才能保证不同厂商生产的器件在一起使用时能够很好地结合。

信号完整性问题会引发包括时序冲突、协议背离、时钟抖动以及由其他总线引发的错误等其它问题。

本文介绍了DDR信号的测量方法,DDR信号验证中面临的挑战,并针对其调试方法给出了相关建议。

文中提到的方法适用于DDR、DDR2、 DDR3 和 SDRAM这一类全缓冲的DIMM 系统调试。

为简单起见,这些内存技术在下文中统称为DDR。

.2.测量方法JEDEC规范定义了DRAM的引脚或球必须满足的电气与定时方面的要求。

一些较新的DDR DRAM采用了精细球栅阵列(FBGA)封装,此封装下的焊接球很难接触。

因此,我们建议测量时,探头应尽可能接近DRAM的球状焊点。

通常,我们可以在与焊接球相连的过孔上或与其相连的电阻靠近DRAM一侧的焊盘上测量。

目前最高级的差分有源电压探头能在探头顶端容性负载低于0.22pF的情况下达到高达13GHz的测量带宽。

此类工具对DDR信号(通常为单端信号)的影响非常小,很适合DDR测量,强烈建议大家使用。

由于DDR信号对噪声非常敏感,因此建议在测量此类信号时采用带宽足够大的示波器,以避免示波器的噪声影响测量。

有些示波器具备带宽压缩功能,能调节至恰好适合测量的带宽,以实现最精确和可重复的测量。

图1所示为13 GHz差分有源探头连接到DDR2 DIMM的过孔上的情形。

3.信号验证所面临的挑战同一根数据总线上的DDR数据传输是双向的。

这使DDR信号验证变得非常困难,因为我们首先必须分离数据总线上复杂的数据流才能对其进行信号完整性测量。

基于IBM GPM模型的DDR2接口信号完整性分析

基于IBM GPM模型的DDR2接口信号完整性分析随着ASIC技术和工艺突飞猛进的进展,65/45nm工艺已成为当前设计的主流,高频翻转,冲击求给ASIC后端版图设计,封装及系统设计带来了前所未有的挑战,信号完整性问题,以及往往被忽视的因芯片接口同时开关造成的同步开关噪声(SSN),因为影响到其相临规律器件的稳定和时序变得越来越关键。

在芯片设计阶段,需要对芯片的版图布局、芯片封装以及客户板级信息举行建模和联合,才可以确保系统很好满足囫囵系统性能的要求,提高设计的胜利率。

因此如何在物理设计前提供相对精确的仿真模型成为一个关键问题。

IBM在设计大规模芯片的过程中采纳基于Hspice 语言建立的GPM(Generic Package Model)模型指导设计中的前仿与设计后验证,它不仅包含封装供电网络和信号通路的模型,还包括芯片上的供电网络、IO以及与芯片局部的SRAM、RA等规律电路和片上滤波(DECAP)的布局,另外客户还可以加入实际的负载模型与其衔接组成完整的链路仿真模型。

GPM模型的物理结构框图1所示。

图1 IBM GPM物理结构框图其中,C4是用于衔接芯片与封装的焊球,Package VDD Supply是封装上芯片内核供电网络,Package VDD2 Supply是封装上的IO供电网络,而Package GND Supply是封装上GND网络,On-Chip VDD Bus, On-Chip VDD2 Bus, On-Chip Ground Bus则是芯片上相应供电网络。

对图1所示各个部分建模,可以便利地得到GPM模型的电路结构(2)。

IBM的芯片采纳结构相对固定的电源网络,设计初期可以对于电源网络建模用法一套标准的RLC参数模型,并可以按照实际设计所采纳的布局,对芯片和封装的电源网路RLC参数举行修正。

对于不同的尺寸的芯片与封装设计,通过调整BGA与C4端相应的电源管脚比例可以实现在不转变基本模型结构的状况下,调节接入仿真模型RLC网络的比例近而临近实际设计。

DDR、II、IIII 参数及协议和XDR 参数测量

DDR1 高达 400MT/s 200MHz 155ps (20-80%) 600 (20-80%) 600MHz - 1GHz DDR2 高达 800MT/s 400MHz 100ps (20-80%) 200 (20-80%) DDR3 高达 1.6GT/s 800MHz 60ps (20-80%) 100 (20-80%) 2GHz - 4GHz 4GHz - 8GHz

DDR2 和 DDR3 BGA 探头适配器提供信号访问点。

第14页

主要特性 2: 在 BGA 探头中使用嵌入式电阻器

进行卓越的信号完整性探测

在这里进行探测 在这里进行探测

DRAM DDR2/3 BGA 探头 PCB

嵌入式电阻

嵌入式电阻可以隔离探头负载和活动信号。

嵌入式电阻器可以隔离信号的探头负载效应。

第10页

逻辑分析仪当前探测解决方案的问题

• 使用逻辑分析仪进行协议分析要求与所 有总线信号相连。 • 当前的探测方法没有解决针对单个 DRAM 的探测 • 飞线和中间总线探测方法需要在设计中 留出一定空间和使用连接器

– 不适用于小型主板尤其嵌入式 系统

– 飞线连接单调乏味

第11页

议程

DDR 存储器技术概述 DDR 探测的难点 新型 DDR BGA 探头适配器解决探测难点 DDR 协议验证难点和解决方案 DDR 参数测量难点和解决方案 XDR 参数难点和解决方案 问题和解答

D D R 3 - 1 6 0 0

DDR 技术命名 DDR 技术世代 数据传输率(MT/s) 时钟速率为 ½ 数据传输率 = 800 MHz

DDR DIMM 规范(用于计算机)

P C 3 - 12800

PC 命名中 使用的 DDR DDR 技术世代 存储器带宽 (MB/s) 数据速率(1600) x 8 = 12,800 MB/s

DDR2布线指导

文末有福利

在现代高速数字电路的设计过程中,工 程师总是不可避免的会与DDR或者DDR2打交道。 DDR2的工作频率很高,因此,DDR的Layout也 就成为了一个十分关键的问题,很多时候, DDR2的布线直接影响着信号完整性。下面本 文针对DDR2的Layout 问题进行讨论。

1、DDR2的信号及分组

以上数据取自于Zentel的A3R1GE4CFF

1、DDR2的信号及分组

2、印制电路板叠层

2、印制电路板叠层

4层板叠层示意图

Байду номын сангаас

2、印制电路板叠层

3、端接技术

为满足信号完整性要求,信号线往往需要进行端接处理,端 接方式分为以下三种

3、端接技术 SSTL_18电平标准端接示意图

3、端接技术 差分端接示意图

4、布线顺序

5、导线宽度和间距

导线长度要求

5、导线宽度和间距

导线间距要求

赠送桌面

高速数据传输接口DDR2 IF 的特性及测试.

高速数据传输接口DDR2 I/F 的特性及测试

前言

近年来随着视频设备、个人电脑的发展,在这些设备上进行的3d处理,视频交换以及复杂的运算导致数据量急剧增大,为了满足这些数据要在处理器、memory和外围设备之间的高速交换,近年来出现了多种多样的高速接口。

同时,由于数据的高速传输,也给测试带来的新技术上及测试成本上的挑战。

本文将基于advantest的t6500系列测试系统,针对最近出现的高速数据传输接口ddr2 i/f的特性及测试进行简单介绍。

高速memory i/f概要

为了简单说明,表1列出了从1990年至今 pc memory总线,微处理器,memory单元以及高速接口的对应情况。

从表中可以看出传输总线的速度随着从sdr到ddr2的转变而迅速提高。

随着数据量的日益增大,ddr2存储器已成为内存和图形处理芯片的主流应用。

因此,soc芯片中的ddr2 i/f 应用也越来越广泛。

ddr2在memory cell和i/o buffer间集成了4 bit 的pre-fetches传输线,相同频率的ddr1只集成了2 bit,因此ddr2的数据频率可以达到ddr1的2倍(如图2)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DDR2/3信号和协议测试分析方案

-BJLK

目前在计算机主板和各种嵌入式的应用中,DDR3已经逐渐要取代DDR2成为市场的主流。

DDR3相对于DDR2的主要优势再有更高的数据速率和更低的功耗,例如DDR2的数据速率最高到800MT/s,DDR3的最高数据速率可以到

1600MT/s,而在有些嵌入式的应用中还有可能使用更高速率,因此对于设计和测试都提出了更高的要求。

DDR2/3信号测试分析方案

为了进行可靠的探测,对于示波器器和探头的要求也非常高。

对于DDR3的信号,由于JEDEC 没有给出信号上升/下降时间的参数,因此用户只有根据使用芯片的实际最快上升/下降时间来估算需要的示波器带宽,对于DDR3的信号,20 - 80%的上升时间大约在80~120ps左右。

对于传统的高斯频响的示波器,为了保证测量精度,通常需要示波器带宽是被测信号带宽的3~5倍,而对于Agilent 的90000系列示波器,由于其优异的类似砖墙的频响特性,可以保证带内比较好的平坦度,因此可以使用以下公式: Scope bandwidth required = 1.4x maximum signal frequency for 3% accuracy measurements Scope bandwidth required = 1.2x maximum signal frequency for 5% accuracy measurements Scope bandwidth required = 1.0x maximum signal frequency for 10% accuracy measurements 根据这个公式计算出来的示波器带宽通常都在4~8GHz,因此对于DDR3信号的测试,通常推荐的示波器和探头的带宽在8GHz 。

对于DDR2和DDR3信号的测试,除了我们所熟知的双边沿采样以外,最主要的挑战在于2个方面,第一是如何进行读写信号的分离,第二是JEDEC 规定了很多DDR3的参数,如何进行方便可靠的测量。

下面分别进行介绍:

1、读写信号分离

我们知道,要验证信号的质量,有一个很有效的方法就是使用示波器的眼图测量功能,即用时钟做触发对数据信号进行累积,看累积结果的最差情况是否在可以容许的范围内。

但是遗憾的是,想用这种方法直接测量DDR 的信号质量非常困难,因为DDR 信号读写时序是不一样的。

如下图所示:

我们可以看到,写数据(DQ )的跳变位置对应着锁存信号(DQS )的中心,而读数据的跳变位置却对应着锁存信号的边沿,而且总线上还有三态,因此如果直接用DQS 触发对DQ 累积进行眼图测量的话,会得到下图的结果:

我们看到,由于信号的读写和三态都混在一起,因此很难对信号质量进行评估。

要进行信号的评估,第一步是要能把读写信号分离出来。

传统上有几种方法用来进行读写信号的分离,但都存在一定的缺点。

可以用读写Preamble 的宽度不同用脉冲宽度触发,如下图左边,但由于JEDEC 只规定了Write Preamble的宽度的下限,因此不同芯片间Preamble 的宽度可能是不同的,而且如果read/write的Preamble 的宽度一样的话就不能进行分离了。

也可以用读写信号的幅度不同进行分离,如下图中间,但是如果读写信号幅度差别不大也不适用。

还可以根据RAS 、CAS 、CS 、WE 等控制信号来分离读写,如下图右边所示,但这种方法要求通道数多于4个,只有带数字通道的MSO 示波器才能满足要求。

Agilent 最新推出的9000系列示波器可以实现带宽到4GHz 的但是MSO ,所以可以用于DDR2和一部分DDR3的测试,但对于高速的DDR3信号的测量还是需要更高带宽的90000系列示波器。

为了进行可靠的读写分离,Agilent 的Infiniium 系列示波器提供了一种叫InfiniiScan 的功能,可以通过区域(Zone )定义的方式把读写数据可靠分开。

如下图所示:

根据读写数据的建立保持时间的不同,Agilent 独有的InfiniiScan 功能可以通过在屏幕上画出几个信号必须通过的区域的方式方便地分离出读/写数据,并进一步进行眼图的测试。

如下图所示是写信号的眼图。

用同样方法也可以把读信号的眼图分离出来。

除了形成眼图外,我们还可以利用示波器的模板测量功能对眼图进行定量的分析,如下图所示,用户可以根据JEDEC 的要求自行定义一个模板对读/写信号进行模板测试,如

果模

板测试fail ,还可以利用Agilent 示波器提供的模板定位功能定位到引起fail 的波形段。

2、 DDR3参数的测量

由于JESD 79-3规定了很多DDR3的参数,这些参数的测量如果全靠手工来做,非常耗时耗力,很多用户要完成DDR3的手工测试需要好几天的时间。

因此Agilent 提供了全自动的U7231A DDR3一致性测试软件。

以下是测试软件可以完成的测试项目。

这个软件的使用也非常简便,如下图所示,用户只需要顺序选择好测试速率、测试项目并根据提示进行连接,然后运行测试软件即可。

软件运行后,示波器会自动设置时基、垂直增益、触发等参数并进行测量,测量结果会汇总成一个html 格式的测试报告,报告中列出了测试的项目、是否通过、spec 的要求、实测值、margin 等。

如下图所示:

使用自动测试软件的优点如下:自动化的设置向导避免连接和设置错误;快速的测量和优化的算法减少测试时间;可以测试 JEDEC 规定的速率也可以测试用户自定义的数据速率;独有的自动读写分离技术简化了测试操作;能够多次测量并给出一个统计的结果;能够根据信号斜率自动计算建立/保持时间的修正值。

DDR3 的信号速率比较高,要进行可靠的测量,通常推荐的探头连接方式是使用焊接式探头,而焊接的方式通常拆卸不太方便,而 Agient 的探头前端可以很好地解决这个问题,下图是用 Agilent 的 N5425A+N5426A 探头前端做测试的一个例子。

由于一个 N5425A 可以配 10 个 N5426A,它们之间可以灵活连接。

由于 DDR3 的信号线很多,因此可以把很多 N5426A 焊在常测的信号线上,通过更换 N5425A 和不同 N5426A 之间的连接可以遍历很多的信号,减少了经常焊接的麻烦。

在方便使用的同时 N5425A+ N5426A 可以提供 12G 的探测带宽,因此可以配合更高带宽的探头放大器和示波器使用。

还有许多情况是很难在 PCB 板上找到相应的测试焊盘,所以 Agilent 还提供了不同种类的 DDR3 的 BGA 探头,通过对板子做 Re-work 把 BGA 的 Adapter 焊接在 DDR3 memory chip 和 PCB 板中间,并把信号引出。

DDR2/3 协议测试分析方案对于协议测试来说,需要用到的仪器是逻辑分析仪,其基本原理是通过相应的探头把被测信号引到逻辑分析仪,逻辑分析仪里再运行解码软件进行协议验证和分析。

对于 DIMM 接口的 DDR2/3 协议测试,可以选择 N4835A 等 Interposer 探头连接逻辑分析仪,对于嵌入式应用的 DDR2/3 的协议测试,可以选择相应的 BGA 探头。

如果有可能设计时事先在板上留测试点的话,也可以选择 Soft-Touch 的连接方式,即事先把被测信号引到一些按一定规则排列的焊盘上再通过相应探头前面的针脚顶在被测点上。

由于 DDR3 的数据速率高达 1.6GT/s,所以对逻辑分析仪的要求也很好,对于 DDR3 的测试,推荐采用16900 逻辑分析仪主机+16962A 模块的配置方式。

一下是 16962A 模块的主要指标:1/同步采样眼图分析功能(eyeScan,一次可以同时扫描所有通道眼图; 2/EyeScan 等效采样速率:200G/s; 3/最大深存储定时分析速率:8G/s;4/最大状态分析时

钟:2GHz;5/最大触发速率 2G sequency/s。

逻辑分析仪上可以运行相应的 DDR2/3 解码和协议检查工具,以下是 B4622A DDR2/3 解码和协议检查工具提供的自动协议测试功能和最后生成的测试报告。

下图是对总线利用率的统计结果显示。