STM32F407xx芯片手册第1到3章中文翻译

stm32f407数据手册中文

stm32f407数据手册中文STM32F4是由ST(意法半导体)开发的一种高性能微控制器。

其采用了90纳米的NVM工艺和ART(自适应实时存储器加速器,Adaptive Real-Time MemoryAccelerator T,,)o简介:ST(意法半导体)推出了以基于ARM® Cortex™-M4为内核的STM32F4系列高性能微控制器,其采用了90纳米的NVM工艺和ART(自适应实时存储器加速器,Adaptive Real-Time MemoryAccelerator™)oART技术使得程序零等待执行,提升了程序执行的效率,将Cortext-M4的性能发挥到了极致,使得STM32 F4 系列可达到210DMIPS@168MHz o自适应实时加速器能够完全释放Cortex-M4内核的性能;当CPU 工作于所有允许的频率仁168MHz)时,在闪存中运行的程序,可以达到相当于零等待周期的性能。

STM32F4系列微控制器集成了单周期DSP指令和FPU(floating point unit,浮点单元),提升了计算能力,可以进行一些复杂的计算和控制。

STM32 F4系列引脚和软件兼容于当前的STM32 F2系列产品。

优点兼容于STM32F2系列产品,便于ST的用户扩展或升级产品,而保持硬件的兼容能力。

集成了新的DSP和FPU指令,168MHz的高速性能使得数字信号控制器应用和快速的产品开发达到了新的水平。

提升控制算法的执行速度和代码效率。

先进技术和工艺・存储器加速器:自适应实时加速器(ART Accelerator™ )・多重AHB总线矩阵和多通道DMA:支持程序执行和数据传输并行处理,数据传输速率非常快・90nm工艺咼性能・210DMIPS@168MHz・由于采用了ST的ART加速器,程序从FLASH运行相当于0等待更多的存储器・多达1MB FLASH (将来ST计划推出2MB FLASH的STM32F4) ・192Kb SRAM:128KB在总线矩阵上,64KB在专为CPU使用的数据总线上高级外设与STM32F2兼容・USB OTG 高速480Mbit/s・IEEE1588 ,以太网MAC 10/100・PWM高速定时器:168MHz最大频率・加密/哈希硬件处理器:32位随机数发生器(RNG)・带有日历功能的32位RTC:<1 pA的实时时钟,1秒精度更多的提升・低电压:1.8V到3.6V VDD ,在某些封装上,可降低至1.7V ・全双工I2S・ 12 位ADC:0.41us 转换/2.4Msps(7.2Msps 在交替模式)・高速USART ,可达10.5Mbits/s・高速SPI,可达37.5Mbits/s・Camera接口,可达54M字节/s。

STM32固件库使用手册的中文翻译

创作编号:GB8878185555334563BT9125XW创作者:凤呜大王*UM0427用户手册32位基于ARM微控制器STM32F101xx与STM32F103xx固件函数库介绍本手册介绍了32位基于ARM微控制器STM32F101xx与STM32F103xx的固件函数库。

该函数库是一个固件函数包,它由程序、数据结构和宏组成,包括了微控制器所有外设的性能特征。

该函数库还包括每一个外设的驱动描述和应用实例。

通过使用本固件函数库,无需深入掌握细节,用户也可以轻松应用每一个外设。

因此,使用本固态函数库可以大大减少用户的程序编写时间,进而降低开发成本。

每个外设驱动都由一组函数组成,这组函数覆盖了该外设所有功能。

每个器件的开发都由一个通用API (application programming interface 应用编程界面)驱动,API对该驱动程序的结构,函数和参数名称都进行了标准化。

所有的驱动源代码都符合“Strict ANSI-C”标准(项目于范例文件符合扩充ANSI-C标准)。

我们已经把驱动源代码文档化,他们同时兼容MISRA-C 2004标准(根据需要,我们可以提供兼容矩阵)。

由于整个固态函数库按照“Strict ANSI-C”标准编写,它不受不同开发环境的影响。

仅对话启动文件取决于开发环境。

该固态函数库通过校验所有库函数的输入值来实现实时错误检测。

该动态校验提高了软件的鲁棒性。

实时检测适合于用户应用程序的开发和调试。

但这会增加了成本,可以在最终应用程序代码中移去,以优化代码大小和执行速度。

想要了解更多细节,请参阅Section 2.5。

因为该固件库是通用的,并且包括了所有外设的功能,所以应用程序代码的大小和执行速度可能不是最优的。

对大多数应用程序来说,用户可以直接使用之,对于那些在代码大小和执行速度方面有严格要求的应用程序,该固件库驱动程序可以作为如何设置外设的一份参考资料,根据实际需求对其进行调整。

STM32固件库使用手册的中文翻译.

UM0427用户手册32位基于ARM微控制器STM32F101xx与STM32F103xx固件函数库介绍本手册介绍了32位基于ARM微控制器STM32F101xx与STM32F103xx的固件函数库。

该函数库是一个固件函数包,它由程序、数据结构和宏组成,包括了微控制器所有外设的性能特征。

该函数库还包括每一个外设的驱动描述和应用实例。

通过使用本固件函数库,无需深入掌握细节,用户也可以轻松应用每一个外设。

因此,使用本固态函数库可以大大减少用户的程序编写时间,进而降低开发成本。

每个外设驱动都由一组函数组成,这组函数覆盖了该外设所有功能。

每个器件的开发都由一个通用API (application programming interface 应用编程界面)驱动,API对该驱动程序的结构,函数和参数名称都进行了标准化。

所有的驱动源代码都符合“Strict ANSI-C”标准(项目于范例文件符合扩充ANSI-C标准)。

我们已经把驱动源代码文档化,他们同时兼容MISRA-C 2004标准(根据需要,我们可以提供兼容矩阵)。

由于整个固态函数库按照“Strict ANSI-C”标准编写,它不受不同开发环境的影响。

仅对话启动文件取决于开发环境。

该固态函数库通过校验所有库函数的输入值来实现实时错误检测。

该动态校验提高了软件的鲁棒性。

实时检测适合于用户应用程序的开发和调试。

但这会增加了成本,可以在最终应用程序代码中移去,以优化代码大小和执行速度。

想要了解更多细节,请参阅Section 2.5。

因为该固件库是通用的,并且包括了所有外设的功能,所以应用程序代码的大小和执行速度可能不是最优的。

对大多数应用程序来说,用户可以直接使用之,对于那些在代码大小和执行速度方面有严格要求的应用程序,该固件库驱动程序可以作为如何设置外设的一份参考资料,根据实际需求对其进行调整。

此份固件库用户手册的整体架构如下:⏹定义,文档约定和固态函数库规则。

stm32f407数据手册中文

1.参考1. Stm32f4数据手册:stm32f407zgt6.pdf2. Stm32f4中文手册:stm32f4xx中文参考手册.pdf3.开发板示意图:Explorer stm32f4_ Vxx_ SCH.pdf 2.芯片内部资源1.芯片图片2.芯片参数表3.内核(1)32位高性能Arm Cortex-M4处理器(2)时钟:最高168MHz,实际上比频率高一点(3)支持FPU(浮点运算)和DSP指令4. IO端口(1)Stm32f407zgt6:144针114 IO端口(2)大多数IO端口可以承受5V(模拟通道除外)(3)支持调试:SWD和JTAG,SWD只需要2条数据线5.记忆(1)内存容量:1024k闪存,192K SRAM6.时钟,复位和电源管理(1)1.8〜3.6V电源和IO电压(2)上电复位和可编程掉电监控(3)强大的时钟系统-4〜26m外部高速晶体振荡器内部16 MHz高速RC振荡器-内部锁相环(PLL),在PLL频率加倍后,一般系统时钟是外部或内部高速时钟-外部低速32.768k晶体振荡器,主要用作RTC时钟源7.低功耗(1)三种低功耗模式:睡眠,停止和待机(2)RTC和备用寄存器可以由电池供电8.广告(1)3个12位AD [最多24个外部测试通道](2)内部通道可用于内部温度测量(3)内置参考电压9,DA(1)两个12位Da10,DMA(1)16个具有FIFO和突发支持的DMA通道(2)支持的外设:定时器,ADC,DAC,SDIO,I2S,SPI,I2C和USART 11.多达17个计时器(1)10个通用计时器(TIM2和tim5为32位)(2)2个基本计时器(3)2个高级计时器(4)1个系统计时器(5)2个看门狗定时器12.多达17个通讯接口(1)三个I2C接口(2)6个串口(3)3个SPI接口(4)2个CAN2.0(5)2个USB OTG (6)SDIO。

stm32f407数据手册中文

stm32f407数据手册中文STMICROELECTRONICS STM32F407VGT6 微控制器, 32位, 以太网MAC, 照相机接口, ARM 皮质-M4, 168 MHzSTM32F407 cortex-m4的高端芯片,常用于嵌入式产品中,内含DSPμC/OS II(Micro-Controller Operating System Two)是一个可以基于ROM运行的、可裁剪的、抢占式、实时多任务内核,具有高度可移植性,特别适合于微处理器和控制器,适合很多商业操作系统性能相当的实时操作系统(RTOS)。

为了提供最好的移植性能,μC/OS II最大程度上使用ANSI C语言进行开发,并且已经移植到近40多种处理器体系上,涵盖了从8位到64位各种CPU(包括DSP)。

μC/OS II可以简单的视为一个多任务调度器,在这个任务调度器之上完善并添加了和多任务操作系统相关的系统服务,如信号量、邮箱等。

其主要特点有公开源代码,代码结构清晰、明了,注释详尽,组织有条理,可移植性好,可裁剪,可固化。

内核属于抢占式,最多可以管理60个任务。

从1992年开始,由于高度可靠性、鲁棒性和安全性,μC/OS II已经广泛使用在从照相机到航空电子产品的各种应用中。

μC/OS-II实时多任务操作系统内核。

它被广泛应用于微处理器、微控制器和数字信号处理器。

μC/OS-II 的前身是μC/OS,最早出自于1992 年美国嵌入式系统专家Jean brosse 在《嵌入式系统编程》杂志的5 月和6 月刊上刊登的文章连载,并把μC/OS 的源码发布在该杂志的B B S 上。

μC/OS-II可以大致分成核心、任务处理、时间处理、任务同步与通信,CPU的移植等5个部分。

1) 核心部分(OSCore.c) 是操作系统的处理核心,包括操作系统初始化、操作系统运行、中断进出的前导、时钟节拍、任务调度、事件处理等多部分。

能够维持系统基本工作的部分都在这里。

STM32固件库使用手册的中文翻译版

因为该固件库是通用的,并且包括了所有外设的功能,所以应用程序代码的大小和执行速度可能不是最优 的。对大多数应用程序来说,用户可以直接使用之,对于那些在代码大小和执行速度方面有严格要求的应 用程序,该固件库驱动程序可以作为如何设置外设的一份参考资料,根据实际需求对其进行调整。

1.3.1 变量 ................................................................................................................................................ 28 1.3.2 布尔型 ............................................................................................................................................ 28 1.3.3 标志位状态类型 ........................................................................................................................... 29 1.3.4 功能状态类型 .............................................................................................................

STM32F407xx芯片手册第1到3章中文翻译

STM32F407xx芯⽚⼿册第1到3章中⽂翻译1⽂档约定寄存器缩写列表下⾯的缩写⽤于描述寄存器Read/Write(rw)软件可读写Read-Only(r)软件只读Write-only(w)软件只写Read/clear(rc_w1)软件可读,写1清除,写0⽆作⽤Read/clear(rc_w0)软件可读,写0清除,写1⽆作⽤Read/clear by read软件可读,读后⾃动清零,写0⽆作⽤Read/set(rs)软件可读,可置位,写0⽆作⽤Read-only writeTrigger(rt_w)软件可读,写0或1翻转此位Toggle(t)写1翻转,写0⽆作⽤Reserved(Res.)保留位,必须保持复位值2存储器和总线架构2.1系统架构主系统包括32位多层互联AHB总线阵列,连接以下部件:Height masters—Cortex TM-M4F内核I-Bus(指令总线),D-bus(数据总线)和S-bus(系统总线)—DMA1存储器总线—DMA2存储器总线—DMA2外设总线—以太⽹DMA总线—USB OTG HS DMA总线Seven slaves—内置Flash存储器指令总线—内置Flash存储器数据总线—主内置SRAM1(112KB)—辅助内置SRAM2(16KB)—AHB1外设,包括AHB到APB的桥以及APB外设—AHB2外设—FSMC接⼝总线矩阵提供从主设备到从设备的访问,即使在有若⼲⾼速外设同时运⾏的情况下也能并⾏访问并⾼效运转。

这个架构如图1所⽰。

注意:64KB的CCM(内核耦合存储器core coupled memory)数据RAM并不是总线矩阵的⼀部分,它只能通过CPU来访问。

图1系统架构2.1.1S0:指令总线这条总线连接Cortex TM-M4F内核的指令总线到总线矩阵,⽤于内核取指。

总线的Target是存储有代码的存储器(包括内置Flash存储器/SRAM以及通过FSMC外扩的外部存储器)。

stm32f407数据手册中文

stm32f407数据手册中文STMICROELECTRONICS STM32F407VGT6 微控制器, 32位, 以太网MAC, 照相机接口, ARM 皮质-M4, 168 MHzSTM32F407 cortex-m4的高端芯片,常用于嵌入式产品中,内含DSPμC/OS II(Micro-Controller Operating System Two)是一个可以基于ROM运行的、可裁剪的、抢占式、实时多任务内核,具有高度可移植性,特别适合于微处理器和控制器,适合很多商业操作系统性能相当的实时操作系统(RTOS)。

为了提供最好的移植性能,μC/OS II最大程度上使用ANSI C语言进行开发,并且已经移植到近40多种处理器体系上,涵盖了从8位到64位各种CPU(包括DSP)。

μC/OS II可以简单的视为一个多任务调度器,在这个任务调度器之上完善并添加了和多任务操作系统相关的系统服务,如信号量、邮箱等。

其主要特点有公开源代码,代码结构清晰、明了,注释详尽,组织有条理,可移植性好,可裁剪,可固化。

内核属于抢占式,最多可以管理60个任务。

从1992年开始,由于高度可靠性、鲁棒性和安全性,μC/OS II已经广泛使用在从照相机到航空电子产品的各种应用中。

μC/OS-II实时多任务操作系统内核。

它被广泛应用于微处理器、微控制器和数字信号处理器。

μC/OS-II 的前身是μC/OS,最早出自于1992 年美国嵌入式系统专家Jean brosse 在《嵌入式系统编程》杂志的5 月和6 月刊上刊登的文章连载,并把μC/OS 的源码发布在该杂志的B B S 上。

μC/OS-II可以大致分成核心、任务处理、时间处理、任务同步与通信,CPU的移植等5个部分。

1) 核心部分(OSCore.c) 是操作系统的处理核心,包括操作系统初始化、操作系统运行、中断进出的前导、时钟节拍、任务调度、事件处理等多部分。

能够维持系统基本工作的部分都在这里。

stm32f407数据手册中文

STMICROELECTRONICS STM32F407VGT6 微控制器, 32位, 以太网MAC, 照相机接口, ARM 皮质-M4, 168 MHz, 1 MB, 196 KB, 100 引脚, LQFPSTM32F407VGT6基于高性能的ARM Cortex-M4 32位RISC内核, 运行频率高达168MHz. Cortex-M4内核具有一个浮点单元(FPU)单精度, 支持所有ARM单精度数据处理指令和数据类型. 它还执行全套的DSP指令, 并包含一个存储器保护单元, 加强应用的安全性. STM32F407VGT6融合了高速内嵌存储器(闪存存储器高达1Mbyte, 高达192K字节SRAM), 高达4K字节备用SRAM, 以及一个加强范围的输入输出, 外部设备连接至两个APB总线, 三个AHB总线和一个32位多AHB总线矩阵..高达1Mbyte闪存.高达192+4 K字节SRAM, 包括64K字节CCM (核心耦合存储器) 数据RAM.灵活的静态存储器控制器支持紧凑型闪存, SRAM, PSRAM, NOR 和NAND存储器.LCD并行接口, 8080/6800模式.时钟, 复位和电源管理.4MHz至26 MHz晶体振荡器.内部16 MHz工厂调整RC (1%精准度) .32kHz振荡器用于实时时钟, 带校准功能.内部32kHz RC, 带校准.睡眠, 停止和待机模式.VBAT供电实时时钟, 20×32位备用电源.3 ×12位, 2.4MSPS 模数转换器.2 ×12位数模转换器.通用DMA控制器, 支持FIFO和爆破. .多达17个计时器.调试模式.多达140个输入输出端口, 带中断能力.多达136个快速输入输出, 高达84MHz .多达138个5V输入输出.高达15个通讯接口STM32F407VGT6 中文资料规格参数参数列表反馈错误技术参数电源电压(DC)1.80 V (min)时钟频率168 MHzRAM大小200704 B位数32封装参数安装方式Surface Mount引脚数100封装LQFPLQFPActive制造应用视频和目视, 嵌入式设计与开发, Industrial, 多媒体, 便携式器材, Clock & Timing, Embedded Design & Development, Imaging, Video & Vision, Industrial, , 时钟与计时, 传感与仪器, 工业, 医用Compliant含铅标准Lead FreeREACH SVHC标准No SVHC海关信息ECCN代码3A991A2。

stm32f407数据手册中文

本参考手册涵盖了基于ARM® Cortex®-M3内核的单片机STM32F101xx, STM32F102xx, STM32F103xx, STM32F105xx and STM32F107xx产品线,它为用户使用以上单片机提供了完整的存储器和外设信息。

(STM32F101xx, STM32F102xx, STM32F103xx, STM32F105xx and STM32F107xx advanced ARM-based 32-bit MCUs)

计算机图形学,输入的是对虚拟场景的描述,通常为多边形数组,而每个多边形由三个顶点组成,每个顶点包括三维坐标、贴图坐标、RGB 颜色等。

输出的是图像,即二维像素数组。

计算机视觉,输入的是图像或图像序列,通常来自相机、摄像头或视频文件。

输出的是对于图像序列对应的真实世界的理解,比如检测人脸、识别车牌。

图像处理,输入的是图像,输出的也是图像。

Photoshop中对一副图像应用滤镜就是典型的一种图像处理。

常见操作有模糊、灰度化、增强对比度等。

尽管三者所涉及的都是运用计算机来处理对象,但是长期以来却是属于不同技术领域,近些年来,随着多媒体技术、计算机动画以及三维数据场显示技术等的迅速发展,计算机图形学、图像处理和计算机视觉结合日益紧密,并且相互渗透。

例如,三维游戏为了增加表现力会叠加全屏的后期特效,原理就是数字图像处理,只是将计算量放在了显卡端;计算机视觉对需要识别的照片进行预处理也是运用了数字图像处理技术;最明显的是增强现实(AR),用数字图像处理技术进行预处理,用计算机视觉技术进行跟踪物体的识别与姿态获取,用图形学技术进行虚拟三维物体的叠加和显示。

STM32固件库使用手册的中文翻译版

32位基于ARM微控制器STM32F101xx与STM32F103xx固件函数库介绍本手册介绍了32位基于ARM微控制器STM32F101xx与STM32F103xx的固件函数库。

该函数库是一个固件函数包,它由程序、数据结构和宏组成,包括了微控制器所有外设的性能特征。

该函数库还包括每一个外设的驱动描述和应用实例。

通过使用本固件函数库,无需深入掌握细节,用户也可以轻松应用每一个外设。

因此,使用本固态函数库可以大大减少用户的程序编写时间,进而降低开发成本。

每个外设驱动都由一组函数组成,这组函数覆盖了该外设所有功能。

每个器件的开发都由一个通用API (application programming interface 应用编程界面)驱动,API对该驱动程序的结构,函数和参数名称都进行了标准化。

所有的驱动源代码都符合“Strict ANSI-C”标准(项目于范例文件符合扩充ANSI-C标准)。

我们已经把驱动源代码文档化,他们同时兼容MISRA-C 2004标准(根据需要,我们可以提供兼容矩阵)。

由于整个固态函数库按照“Strict ANSI-C”标准编写,它不受不同开发环境的影响。

仅对话启动文件取决于开发环境。

该固态函数库通过校验所有库函数的输入值来实现实时错误检测。

该动态校验提高了软件的鲁棒性。

实时检测适合于用户应用程序的开发和调试。

但这会增加了成本,可以在最终应用程序代码中移去,以优化代码大小和执行速度。

想要了解更多细节,请参阅Section 2.5。

因为该固件库是通用的,并且包括了所有外设的功能,所以应用程序代码的大小和执行速度可能不是最优的。

对大多数应用程序来说,用户可以直接使用之,对于那些在代码大小和执行速度方面有严格要求的应用程序,该固件库驱动程序可以作为如何设置外设的一份参考资料,根据实际需求对其进行调整。

此份固件库用户手册的整体架构如下:定义,文档约定和固态函数库规则。

固态函数库概述(包的内容,库的架构),安装指南,库使用实例。

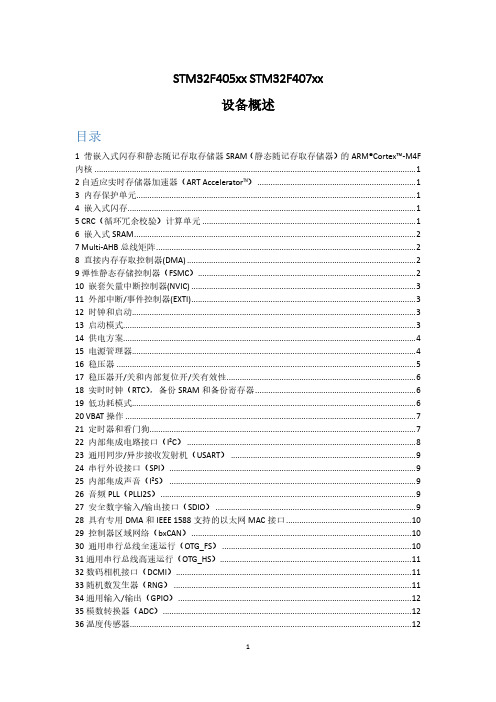

STM32F405xx、STM32F407xx中文资料

设备பைடு நூலகம்述

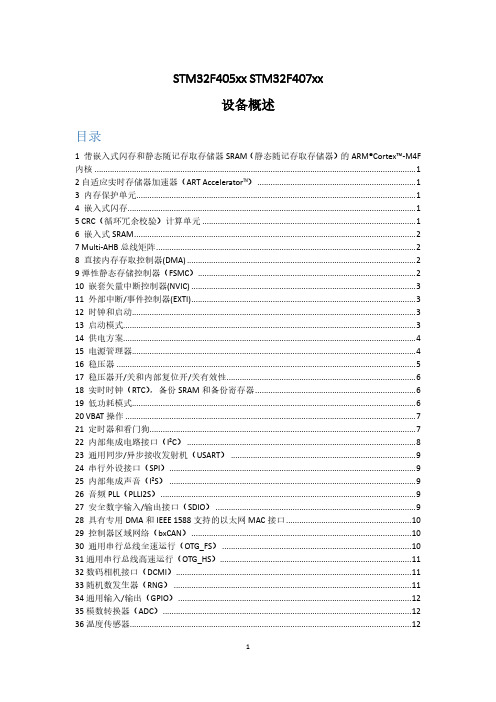

目录

1 带嵌入式闪存和静态随记存取存储器 SRAM(静态随记存取存储器)的 ARM®Cortex™-M4F 内核 ..................................................................................................................................................1 2 自适应实时存储器加速器(ART Accelerator™) ........................................................................1 3 内存保护单元...............................................................................................................................1 4 嵌入式闪存...................................................................................................................................1 5 CRC(循环冗余校验)计算单元 .................................................................................................1 6 嵌入式 SRAM..............................................

单片机STM32外文文献翻译、中英文翻译

外文翻译英文原文:STM32 MicrocontrollerIntroductionRequirements based STM32 family is designed for high-performance, low-cost, low-power embedded applications designed specifically for ARM Cortex-M3 core. According to the performance into two different series: STM32F103 "Enhanced" series and STM32F101 "Basic" series. Enhanced Series clock frequency of 72MHz, the highest performance of similar products product; basic clock frequency of 36MHz, 16-bit product prices get more than 16 products significantly enhance the performance and is 16 product users the best choice. Both series have built-in 32K to 128K of flash memory, the difference is the maximum capacity of the SRAM and peripheral combinations. At 72MHz, executing from Flash, STM32 power consumption 36mA, are 32 products on the market's lowest power, the equivalent of 0.5mA/MHz.STM32F103 Performance Characteristics1)Kernel. ARM32 bit CPU, the maximum operating frequency of 72MHz,1.25DMIPS/MHz. Single-cycle multiply and hardware divide.2)Memory. Integrated on-chip 32-512KB of Flash memory. 6-64KB SRAM memory.3)Clock, reset, and power management. 2.0-3.6V power supply and I / O interface, the drive voltage. POR, PDR and programmable voltage detector. 4-16MHz crystal. Embedded factory tuned 8MHz RC oscillator circuit. 40 kHz internal RC oscillator circuit. CPU clock for the PLL. With calibration for the RTC 32kHz crystal.4)Low power consumption. Three kinds of low-power mode. Sleep, stop, standby mode. For RTC and backup registers supply VBAT.5)Debug mode. Serial debugging and JTAG interface.6)Direct data storage. 12-channel direct data storage controller. Supported peripherals: timers, ADC, DAC, SPI, IIC and USART.7)Up to a maximum of 112 fast I / O ports. Depending on the model, there are 26,37,51,80, and 112 I / O ports, all ports can be mapped to 16 external interruptvectors. In addition to the analog input, all of them can accept the input of 5V or less.8)Up to a maximum of 11 timers. Four 16-bit timers, each with 4 IC / OC / PWM or pulse counter. 2 16 6-channel advanced control timer: up to 6 channels can be used for PWM output. 2 watchdog timer. Systick timer: 24 down counter. Two 16-bit basic timer for driving DAC.9)Up to a maximum of 13 communication interfaces. 2 IIC interface. 5 USART interfaces. 3 SPI interface, two and IIS reuse. CAN interface. USB 2.0 full-speed interface. SDIO interface.System Function1)Integration of embedded Flash and SRAM memory ARM Cortex-M3 core. And 8/16 equipment compared, ARM Cortex-M3 32-bit RISC processor provides a higher code efficiency. STM32F103xx microcontrollers with an embedded ARM core, so it can be compatible with all ARM tools and software.2)Embedded Flash memory and RAM memory. Built up to 512KB embedded Flash, can be used to store programs and data. Up to 64KB of embedded SRAM clock speed of the CPU can read and write.3)Variable static memory. Variable static memory with 4 chip selects, supports four modes: Flash, RAM, PSRAM, NOR and NAND. After three FSMC interrupt lines connected to the OR after the nested vector interrupt controller. No read / write FIFO, except PCCARD, the code is executed from external memory is not supported Boot, the target frequency is equal to SYSCLK / 2, so the time when the system clock is 72MHz, 36MHz conducted in accordance with external access.4)Nested Vectored Interrupt Controller. Can handle 43 maskable interrupt channels, providing 16 interrupt priority levels. Tightly coupled nested vectored interrupt controller to achieve lower latency interrupt handling directly passed to the kernel interrupt vector table entry address, tightly coupled nested vectored interrupt controller kernel interface, allowing early treatment interruption, the latter to be more high-priority interrupt processing, support tail chain, auto-save processor state terrupts automatically restored on interrupt exit, no instructions intervention.5)External interrupt / event controller. External interrupt / event controller consists for 19 to generate interrupt / event requests edge detector lines. Each line can be individually configured to select the trigger event, it can be individually masked. There is a pending interrupt request registers to maintain state. When an external line appear longer than the internal APB2 clock-cycle pulse, the external interrupt / eventcontroller is able to detect. Up to 112 GPIO connected to the 16 external interrupt lines.6)Clocks and startup. At boot time or to the system clock selection, but the reset when the internal 8MHz crystal oscillator is selected as the CPU clock. Can choose a 4-16MHz external clock, and will be monitored to determine the success. During this time, the interrupt controller is disabled and the software management is subsequently disabled. Also, if there is a need, PLL clock interrupt management fully available. Comparator can be used more pre-configuration of the AHB frequency, including high-speed and low-speed APB APB, APB highest frequency of high-speed 72MHz, low-speed APB highest frequency of 36MHz.Architectural AdvantagesIn addition to the new features Enhanced peripheral interfaces, STM32 series also interconnect with other STM32 microcontrollers offer the same standard interface, such sharing of peripherals to enhance the entire product family, application flexibility, so that developers can a plurality of design reuse the same software. New STM32 standard peripherals include 10 timers, two 12-bit ADC, two 12-bit DAC, two I2C interfaces, five USART interfaces and three SPI ports. There are 12 new products peripherals direct data storage channel, there is a CRC calculation unit, like other STM32 microcontrollers, the supports 96 unique identifier.New series also has followed the STM32 microcontroller family of products low voltage and energy saving are two advantages. 2.0V to 3.6V operating voltage range compatible with the mainstream of battery technologies such as lithium batteries and nickel-metal hydride batteries, the package also features a battery operation mode dedicated pin Vbat. 72MHz frequency to execute code from flash consumes only 27mA current. There are four low-power mode, the current consumption can be reduced to two microamps. Quick Start from low power mode to save energy too; starting circuit using STM32 internally generated 8MHz signal, the microcontroller from stop mode when you wake up with less than 6 microseconds.中文翻译:单片机STM321 STM32的介绍STM32系列基于专为要求高性能、低成本、低功耗的嵌入式应用专门设计的ARM Cortex-M3内核。

STM32-参考手册-中文.pdf

STM32-参考⼿册-中⽂.pdf23 串⾏外设接⼝(SPI)⼩容量产品是指闪存存储器容量在16K ⾄32K 字节之间的STM32F101xx、STM32F102xx和STM32F103xx微控制器。

中容量产品是指闪存存储器容量在64K⾄128K字节之间的STM32F101xx、STM32F102xx和STM32F103xx微控制器。

⼤容量产品是指闪存存储器容量在256K⾄512K字节之间的STM32F101xx和STM32F103xx微控制器。

互联型产品是指STM32F105xx和STM32F107xx微控制器。

除⾮特别说明,本章描述的模块适⽤于整个STM32F10xxx微控制器系列。

23.1 SPI简介在⼤容量产品和互联型产品上,SPI接⼝可以配置为⽀持SPI协议或者⽀持I2S⾳频协议。

SPI接⼝默认⼯作在SPI⽅式,可以通过软件把功能从SPI模式切换到I2S模式。

在⼩容量和中容量产品上,不⽀持I2S⾳频协议。

串⾏外设接⼝(SPI)允许芯⽚与外部设备以半/全双⼯、同步、串⾏⽅式通信。

此接⼝可以被配置成主模式,并为外部从设备提供通信时钟(SCK)。

接⼝还能以多主配置⽅式⼯作。

它可⽤于多种⽤途,包括使⽤⼀条双向数据线的双线单⼯同步传输,还可使⽤CRC校验的可靠通信。

I2S也是⼀种3引脚的同步串⾏接⼝通讯协议。

它⽀持四种⾳频标准,包括飞利浦I2S标准,MSB 和LSB对齐标准,以及PCM标准。

它在半双⼯通讯中,可以⼯作在主和从2种模式下。

当它作为主设备时,通过接⼝向外部的从设备提供时钟信号。

警告:由于 SPI3/I2S3 的部分引脚与 JTAG 引脚共享 (SPI3_NSS/I2S3_WS 与 JTDI ,SPI3_SCK/I2S3_CK与JTDO),因此这些引脚不受IO控制器控制,他们(在每次复位后)被默认保留为JTAG⽤途。

如果⽤户想把引脚配置给SPI3/I2S3,必须(在调试时)关闭JTAG并切换⾄SWD接⼝,或者(在标准应⽤时)同时关闭JTAG和SWD接⼝。

stm32f407数据手册中文

1,参考资料1. Stm32f4数据手册:stm32f407zgt6.pdf2. Stm32f4中文手册:stm32f4xx中文参考手册.pdf3.开发板原理图:Explorer stm32f4_ Vxx_ SCH.pdf2,芯片内部资源1.芯片图片2.芯片参数表3.内核(1)32位高性能Arm Cortex-M4处理器(2)时钟:高达168MHz,实际上可以稍微超频一点(3)支持FPU(浮点运算)和DSP指令4. IO端口(1)Stm32f407zgt6:144针114 IO端口(2)大多数IO端口可以承受5V(模拟通道除外)(3)支持调试:SWD和JTAG,SWD只需要2条数据线5.记忆(1)内存容量:1024k闪存,192K SRAM6.时钟,复位和电源管理(1)1.8〜3.6V电源和IO电压(2)上电复位和可编程掉电监控(3)强大的时钟系统-4〜26m外部高速晶体振荡器内部16 MHz高速RC振荡器-内部锁相环(PLL,倍频),PLL倍频后,一般系统时钟是外部或内部高速时钟-外部低速32.768k晶体振荡器,主要用作RTC时钟源7.低功耗(1)三种低功耗模式:睡眠,停止和待机(2)RTC和备用寄存器可以由电池供电8,广告(1)3个12位AD [最多24个外部测试通道](2)内部通道可用于内部温度测量(3)内置参考电压9,DA(1)两个12位Da10,DMA(1)16个具有FIFO和突发支持的DMA通道(2)支持的外设:定时器,ADC,DAC,SDIO,I2S,SPI,I2C和USART 11.多达17个计时器(1)10个通用计时器(TIM2和tim5为32位)(2)2个基本计时器(3)2个高级计时器(4)1个系统计时器(5)2个看门狗定时器12.多达17个通讯接口(1)三个I2C接口(2)6个串口(3)3个SPI接口(4)2个CAN2.0(5)2个USB OTG (6)个SDIO。

STM32F407之USART翻译

●发送方为同步传输提供时钟 ● IRDA SIR 编码器解码器

- 在正常模式下支持 3/16 位的持续时间 ●智能卡模拟功能

- 智能卡接口支持 ISO7816-3 标准里定义的异步 智能卡协议

- 智能卡用到的 0.5 和 1.5 个停止位 单线半双工通信 可配置的使用 DMA 的多缓冲器通信 在 SRAM 里利用集中式 DMA 缓冲接收/发送字节 单独的发送器和接收器使能位 传输检测标志:

发送器 发送器根据 M 位的状态发送 8 位或 9 位的数据字。当发送使能位(TE)被设置时,

发送移位寄存器中的数据在 TX 脚上输出,相应的时钟脉冲在 SCLK 脚上输出。

字符发送 在 USART 发送期间,在 TX 引脚上首先移出数据的最低有效位。在此模式里,

USART_DR 寄存器包含了一个内部总线和发送移位寄存器之间的缓冲器(见图 236)。 每个字符之前都有一个低电平的起始位;之后跟着的停止位,其数目可 配置。 注意:1.在数据传输期间不能复位 TE 位,否则将破坏 TX 脚上的数据,因为波 特率计数器停止计数。正在传输的当前数据将丢失。 2. TE 位被激活后将发送一个空闲帧。

●全双工的,异步通信 ●NRZ 标准的格式(Mark/Space) ●可以在速度和时钟容限之间灵活的配置 16 位或 8 位过采样方法 ● 分数波特率发生器系统

- 通用可编程的发送和接收波特率(参考数据表最 大 APB 频率值。)

●可编程的数据字长度( 8 位或 9 位) ●可配置的停止位 - 支持 1 或 2 个停止位 ●LIN 主发送同步断开符的功能和 LIN 从检测断开符的能力

stm32f407数据手册中文

1.参考1. Stm32f4数据手册:stm32f407zgt6.pdf2. Stm32f4中文手册:stm32f4xx中文参考手册.pdf3.开发板示意图:Explorer stm32f4_ Vxx_ SCH.pdf 2.芯片内部资源1.芯片图片2.芯片参数表3.内核(1)32位高性能Arm Cortex-M4处理器(2)时钟:最高168MHz,实际上比频率高一点(3)支持FPU(浮点运算)和DSP指令4. IO端口(1)Stm32f407zgt6:144针114 IO端口(2)大多数IO端口可以承受5V(模拟通道除外)(3)支持调试:SWD和JTAG,SWD只需要2条数据线5.记忆(1)内存容量:1024k闪存,192K SRAM6.时钟,复位和电源管理(1)1.8〜3.6V电源和IO电压(2)上电复位和可编程掉电监控(3)强大的时钟系统-4〜26m外部高速晶体振荡器内部16 MHz高速RC振荡器-内部锁相环(PLL),在PLL频率加倍后,一般系统时钟是外部或内部高速时钟-外部低速32.768k晶体振荡器,主要用作RTC时钟源7.低功耗(1)三种低功耗模式:睡眠,停止和待机(2)RTC和备用寄存器可以由电池供电8.广告(1)3个12位AD [最多24个外部测试通道](2)内部通道可用于内部温度测量(3)内置参考电压9,DA(1)两个12位Da10,DMA(1)16个具有FIFO和突发支持的DMA通道(2)支持的外设:定时器,ADC,DAC,SDIO,I2S,SPI,I2C和USART 11.多达17个计时器(1)10个通用计时器(TIM2和tim5为32位)(2)2个基本计时器(3)2个高级计时器(4)1个系统计时器(5)2个看门狗定时器12.多达17个通讯接口(1)三个I2C接口(2)6个串口(3)3个SPI接口(4)2个CAN2.0(5)2个USB OTG (6)SDIO。

STM32固件库使用手册的中文翻译

UM0427用户手册之杨若古兰创作32位基于ARM微控制器STM32F101xx与STM32F103xx固件函数库介绍本手册介绍了32位基于ARM微控制器STM32F101xx与STM32F103xx的固件函数库.该函数库是一个固件函数包,它由程序、数据结构和宏构成,包含了微控制器所有外设的功能特征.该函数库还包含每一个外设的驱动描述和利用实例.通过使用本固件函数库,无需深入把握细节,用户也能够轻松利用每一个外设.是以,使用本固态函数库可以大大减少用户的程序编写时间,进而降低开发成本.每个外设驱动都由一组函数构成,这组函数覆盖了该外设所有功能.每个器件的开发都由一个通用API (application programming interface 利用编程界面)驱动,API对该驱动程序的结构,函数和参数名称都进行了尺度化.所有的驱动源代码都符合“Strict ANSIC”尺度(项目于范例文件符合扩充ANSIC尺度).我们曾经把驱动源代码文档化,他们同时兼容MISRAC 尺度(根据须要,我们可以提供兼容矩阵).因为全部固态函数库按照“Strict ANSIC”尺度编写,它不受分歧开发环境的影响.仅对话启动文件取决于开发环境.该固态函数库通过校验所有库函数的输入值来实理想时错误检测.该动态校验提高了软件的鲁棒性.实时检测适合于用户利用程序的开发和调试.但这会添加了成本,可以在终极利用程序代码中移去,以优化代码大小和履行速度.想要了解更多细节,请参阅Section 2.5.因为该固件库是通用的,而且包含了所有外设的功能,所以利用程序代码的大小和履行速度可能不是最优的.对大多数利用程序来说,用户可以直接使用之,对于那些在代码大小和履行速度方面有严酷请求的利用程序,该固件库驱动程序可以作为如何设置外设的一份参考材料,根据实际需求对其进行调整.此份固件库用户手册的全体架构如下:⏹定义,文档商定和固态函数库规则.⏹固态函数库概述(包的内容,库的架构),安装指南,库使用实例.⏹固件库具体描述:设置架构和每个外设的函数.STM32F101xx和STM32F103xx在全部文档中被写作STM32F101x.本用户手册和固态函数库按照以下章节所描述的规范编写.1.1缩写Table 1. 本文档所有缩写定义缩写外设/单元CAN控制器局域网模块DMA直接内存存取控制器EXTI内部间断事件控制器FLASH闪存存储器GPIO通用输入输出I2C内部集成电路IWDG独立看门狗NVIC嵌套间断向量列表控制器PWR电源/功耗控制RCC复位与时钟控制器RTC实时时钟SPI串行外设接口SysTick零碎嘀嗒定时器TIM通用定时器TIM1高级控拟定时器USART通用同步异步接收发射端1.2命名规则固态函数库服从以下命名规则:PPP暗示任一外设缩写,例如:ADC.更多缩写相干信息参阅章节1.1 缩写.零碎、源程叙文件和头文件命名都以“stm32f10x_”作为开头,例如:stm32f10x_conf.h.常量仅被利用于一个文件的,定义于该文件中;被利用于多个文件的,在对应头文件中定义.所有常量都由英文字母大写书写.寄存器作为常量处理.他们的命名都由英文字母大写书写.在大多数情况下,他们采取与缩写规范与本用户手册分歧.外设函数的命名以该外设的缩写加下划线为开头.每个单词的第一个字母都由英文字母大写书写,例如:SPI_SendData.在函数名中,只答应存在一个下划线,用以分隔外设缩写和函数名的其它部分.名为PPP_Init的函数,其功能是根据PPP_InitTypeDef中指定的参数,初始化外设PPP,例如TIM_Init.名为PPP_DeInit的函数,其功能为复位外设PPP的所有寄存器至缺省值,例如TIM_DeInit.名为PPP_StructInit的函数,其功能为通过设置PPP_InitTypeDef 结构中的各种参数来定义外设的功能,例如:USART_StructInit.名为PPP_Cmd的函数,其功能为使能或者失能外设PPP,例如:SPI_Cmd.名为PPP_ITConfig的函数,其功能为使能或者失能来自外设PPP某间断源,例如:RCC_ITConfig.名为PPP_DMAConfig的函数,其功能为使能或者失能外设PPP的DMA接口,例如:TIM1_DMAConfig.用以配置外设功能的函数,老是以字符串“Config”结尾,例如GPIO_PinRemapConfig.名为PPP_GetFlagStatus的函数,其功能为检查外设PPP某标记位被设置与否,例如:I2C_GetFlagStatus.名为PPP_ClearFlag的函数,其功能为清除外设PPP标记位,例如:I2C_ClearFlag.名为PPP_GetITStatus的函数,其功能为判断来自外设PPP的间断发生与否,例如:I2C_GetITStatus.名为PPP_ClearITPendingBit的函数,其功能为清除外设PPP间断待处理标记位,例如:I2C_ClearITPendingBit.1.3编码规则本章节描述了固态函书库的编码规则.固态函数库定义了24个变量类型,他们的类型和大小是固定的.在文件stm32f10x_type.h中我们定义了这些变量:typedef signed long s32;typedef signed short s16;typedef signed char s8;typedef signed long const sc32; /* Read Only */typedef signed short const sc16; /* Read Only */typedef signed char const sc8; /* Read Only */typedef volatile signed long vs32;typedef volatile signed short vs16;typedef volatile signed char vs8;typedef volatile signed long const vsc32; /* Read Only */typedef volatile signed short const vsc16; /* Read Only */typedef volatile signed char const vsc8; /* Read Only */typedef unsigned long u32;typedef unsigned short u16;typedef unsigned char u8;typedef unsigned long const uc32; /* Read Only */typedef unsigned short const uc16; /* Read Only */typedef unsigned char const uc8; /* Read Only */typedef volatile unsigned long vu32;typedef volatile unsigned short vu16;typedef volatile unsigned char vu8;typedef volatile unsigned long const vuc32; /* Read Only */typedef volatile unsigned short const vuc16; /* Read Only */typedef volatile unsigned char const vuc8; /* Read Only */在文件stm32f10x_type.h中,布尔形变量被定义如下:Typedef enum{FALSE = 0,TRUE = !FALSE} bool;1.3.3 标记位形态类型在文件stm32f10x_type.h中,我们定义标记位类型(FlagStatus type)的2个可能值为“设置”与“重置”(SET or RESET).typedef enum{RESET = 0,SET = !RESET} FlagStatus;1.3.4 功能形态类型在文件stm32f10x_type.h中,我们定义功能形态类型(FunctionalState type)的2个可能值为“使能”与“失能”(ENABLE or DISABLE).typedef enum{DISABLE = 0,ENABLE = !DISABLE} FunctionalState;1.3.5 错误形态类型在文件stm32f10x_type.h中,我们错误形态类型类型(ErrorStatus type)的2个可能值为“成功”与“出错”(SUCCESS or ERROR).Typedef enum{ERROR = 0,SUCCESS = !ERROR} ErrorStatus;1.3.6 外设用户可以通过指向各个外设的指针访问各外设的控制寄存器.这些指针所指向的数据结构与各个外设的控制寄存器规划逐个对应.外设控制寄存器结构文件stm32f10x_map.h包含了所有外设控制寄存器的结构,下例为SPI寄存器结构的声明:/* Serial Peripheral Interface */typedef struct{vu16 CR1;u16 RESERVED0;vu16 CR2;u16 RESERVED1;vu16 SR;u16 RESERVED2;vu16 DR;u16 RESERVED3;vu16 CRCPR;u16 RESERVED4;vu16 RXCRCR;u16 RESERVED5;vu16 TXCRCR;u16 RESERVED6;} SPI_TypeDef;寄存器命名遵守上节的寄存器缩写命名规则.RESERVEDi(i为一个整数索引值)暗示被保存区域.外设声明文件stm32f10x_map.h包含了所有外设的声明,下例为SPI外设的声明:#ifndef EXT#DefineEXT extern#endif......#define PERIPH_BASE ((u32)0x40000000)#define APB1PERIPH_BASE PERIPH_BASE#define APB2PERIPH_BASE (PERIPH_BASE + 0x10000)....../* SPI2 Base Address definition*/#define SPI2_BASE (APB1PERIPH_BASE + 0x3800)....../* SPI2 peripheral declaration*/#ifndef DEBUG......#ifdef _SPI2 #define SPI2 ((SPI_TypeDef *) SPI2_BASE)#endif /*_SPI2 */......#else /* DEBUG */…...#ifdef _SPI2EXT SPI_TypeDef *SPI2;#endif /*_SPI2 */…...#endif /* DEBUG */如果用户但愿使用外设SPI,那么必须在文件stm32f10x_conf.h中定义_SPI标签.通过定义标签_SPIn,用户可以访问外设SPIn的寄存器.例如,用户必须在文件stm32f10x_conf.h中定义标签_SPI2,否则是不克不及访问SPI2的寄存器的.在文件stm32f10x_conf.h中,用户可以按照下例定义标签_SPI 和_SPIn.#define _SPI#define _SPI1#define _SPI2每个外设都有若干寄存器专门分配给标记位.我们按照响应的结构定义这些寄存器.标记位的命名,同样遵守上节的外设缩写规范,以‘PPP_FLAG_’开始.对于分歧的外设,标记位都被定义在响应的文件stm32f10x_ppp.h中.用户想要进入除错(DEBUG)模式的话,必须在文件stm32f10x_conf.h中定义标签DEBUG.如许会在SRAM的外设结构部分创建一个指针.是以我们可以简化除错过程,而且通过转储外设获得来获得所有寄存器的形态.在所无情况下,SPI2都是一个指向外设SPI2首地址的指针.变量DEBUG可以仿照下例定义:#define DEBUG 1可以初始化DEBUG模式与文件stm32f10x_lib.c中如下:#ifdef DEBUGvoid debug(void){......#ifdef _SPI2SPI2 = (SPI_TypeDef *) SPI2_BASE;#endif /*_SPI2 */......} #endif /* DEBUG*/Note:1 当用户选择DEBUG模式,宏assert_param被扩展,同时运转时间检查功能也在固态函数库代码中被激活.2 进入DEBUG模式会增大代码的尺寸,降低代码的运转效力.是以,我们强烈建议仅仅在除错的时候使用响应代码,在终极的利用程序中,删除它们.2.固件函数库2.1紧缩包描述STM32F10x固件函数库被紧缩在一个zip文件中.解压该文件会发生一个文件夹:STM32F10xFWLib\FWLib,包含如下所示的子文件夹:Figure 1:固件函数库文件夹结构2.1.1文件夹Examples文件夹Examples,对应每一个STM32外设,都包含一个子文件夹.这些子文件夹包含了整套文件,构成典型的例子,来示范如何使用对应外设.这些文件有:readme.txt:每个例子的简单描述和使用说明.stm32f10x_conf.h:该头文件设置了所有使用到的外设,由分歧的“DEFINE”语句构成.stm32f10x_it.c:该源文件包含了所有的间断处理程序(如果未使用间断,则所有的函数体都为空).stm32f10x.it.h:该头文件包含了所有的间断处理程序的本相.main.c:例程代码.注:所有的例程的使用,都不受分歧软件开发环境的影响.2.1.2文件夹Library文件夹Library包含构成固件函数库核心的所有子文件夹和文件:子文件夹inc包含了固件函数库所需的头文件,用户无需点窜该文件夹:stm32f10x_type.h:所有其他文件使用的通用数据类型和枚举.stm32f10x_map.h:外设存储器映像和寄存器数据结构.stm32f10x_lib.h:主头文件夹,包含了其他头文件.stm32f10x_ppp.h:每个外设对应一个头文件,包含了该外设使用的函数本相,数据结构和枚举.cortexm3_macro.h:文件cortexm3_macro.s对应的头文件.子文件夹src包含了固件函数库所需的源文件,用户无需点窜该文件夹:stm32f10x_ppp.c:每个外设对应一个源文件,包含了该外设使用的函数体.stm32f10x_lib.c:初始化所有外设的指针.注:所有代码都按照Strict ANSIC尺度书写,都不受分歧软件开发环境的影响.2.1.3文件夹Project文件夹Project包含了一个尺度的程序项目模板,包含库文件的编译和所有效户可点窜的文件,可用以建立新的工程.stm32f10x_conf.h:项目配置头文件,默认为设置了所有的外设.stm32f10x_it.c:该源文件包含了所有的间断处理程序(所有的函数体默认为空).stm32f10x_it.h:该头文件包含了所有的间断处理程序的本相.main.c:主函数体文件夹EWARM,RVMDK,RIDE:用于分歧开发环境使用,概况查询各文件夹下的文件readme.txt.2.2固件函数库文件描述Table 2列举和描述了固件函数库使用的所有文件.固件函数库的体系和文件彼此包含的联系暗示在Figure 2中.每一个外设都有一个对应的源文件:stm32f10x_ppp.c和一个对应的头文件:stm32f10x_ppp.h.文件stm32f10x_ppp.c包含了使用外设PPP所需的所有固件函数.提供所有外设一个存储器映像文件stm32f10x_map.h.它包含了所有寄存器的声明,既可以用于Debug模式也能够用于release模式.头文件stm32f10x_lib.h包含了所有外设头文件的头文件.它是独逐个个用户须要包含在本人利用中的文件,起到利用和库之间界面的感化.文件stm32f10x_conf.h是独逐个个须要由用户点窜的文件.它作为利用和库之间的界面,指定了一系列参数.Table 2. 固件函数库文件描述文件名描述参数设置文件,起到利用和库之间界面的感化.用户必须在运转本人的程序前点窜该文件.用户可以利用模板使能或者失能外设.也能够点窜内部晶振的参数.也能够是用该文件在编译前使能Debug或者release模式.主函数体示例.外设间断函数文件.用户可以加入本人的间断程序代码.对于指向同一个间断向量的多个分歧间断请求,可以利用函数通过判断外设的间断标记位来确定精确的间断源.固件函数库提供了这些函数的名称.包含了所有外设的头文件的头文件.它是独逐个个用户须要包含在本人利用中的文件,起到利用和库之间界面的感化.Debug模式初始化文件.它包含多个指针的定义,每个指针指向特定外设的首地址,和在Debug模式被使能时,被调用的函数的定义.该文件包含了存储器映像和所有寄存器物理地址的声明,既可以用于Debug模式也能够用于release模式.所有外设都使用该文件.通用声明文件.包含所有外设驱动使用的通用类型和常数.由C说话编写的外设PPP的驱动源程叙文件.外设PPP的头文件.包含外设PPP函数的定义,和这些函数使用的变量.CortexM3内核特殊指令的指令包装.Figure 2. 固件函数库文件体系结构2.3 外设的初始化和设置本节按步调描述了如何初始化和设置任不测设.这里PPP代表任不测设.1.在主利用文件中,声明一个结构PPP_InitTypeDef,例如:PPP_InitTypeDef PPP_InitStructure;这里PPP_InitStructure是一个位于内存中的工作变量,用来初始化一个或者多个外设PPP.2.为变量PPP_InitStructure的各个结构成员填入答应的值.可以采取以下2种方式:a)按照如下程序设置全部结构体PPP_InitStructure.member1=val1;PPP_InitStructure.member2 = val2;PPP_InitStructure.memberN = valN;/* where N is the number of the structure members */以上步调可以合并在同一行里,用以优化代码大小:PPP_InitTypeDef PPP_InitStructure = { val1, val2,.., valN}b)仅设置结构体中的部分成员:这类情况下,用户该当首先调用函数PPP_SturcInit(..)来初始化变量PPP_InitStructure,然后再点窜其中须要点窜的成员.如许可以包管其他成员的值(多为缺省值)被精确填入.PPP_StructInit(&PPP_InitStructure);PP_InitStructure.memberX = valX;PPP_InitStructure.memberY = valY;/*where X and Y are the members the user wants to configure*/3. 调用函数PPP_Init(..)来初始化外设PPP.4. 在这一步,外设PPP已被初始化.可以调用函数PPP_Cmd(..)来使能之.PPP_Cmd(PPP, ENABLE);可以通过调用一系列函数来使用外设.每个外设都具有各自的功能函数.更多细节参阅Section3 外设固件概述.注:1.在设置一个外设前,必须调用以下一个函数来使能它的时钟:RCC_AHBPeriphClockCmd(RCC_AHBPeriph_PPPx,ENABLE);RCC_APB2PeriphClockCmd(RCC_APB2Periph_PPPx, ENABLE);RCC_APB1PeriphClockCmd(RCC_APB1Periph_PPPx, ENABLE);2. 可以调用函数PPP_Deinit(..)来把外设PPP的所有寄存器复位为缺省值:PPP_DeInit(PPP)3.在外设设置完成当前,继续点窜它的一些参数,可以参照如下步调:PPP_InitStucture.memberX = valX;PPP_InitStructure.memberY = valY; /* where X and Y are the onlymembers that user wants to modify*/PPP_Init(PPP, &PPP_InitStructure);2.4 位段(BitBanding)Cortex™M3存储器映像包含两个位段(bitband)区.这两个位段区将别号存储器区中的每个字映照到位段存储器区的一个位,在别号存储区写入一个字具有对位段区的目标位执行读改写操纵的不异后果.所有STM32F10x外设寄存器都被映照到一个位段(bitband)区.这个特性在各个函数中对单个比特进行置1/置0操纵时被大量使用,用以减小和优化代码尺寸.Section 2.4.1和Section 2.4.2给出了外设固件函数库中如何实现位段访问的描述.2.4.1 映照公式映照公式给出了别号区中的每个字是如何对应位带区的响应位的,公式如下:bit_word_offset = (byte_offset x 32) + (bit_number × 4)bit_word_addr = bit_band_base + bit_word_offset其中:bit_word_offset是目标位在存取器位段区中的地位.bit_word_addr 是别号存储器区中字的地址,它映照到某个目标位.bit_band_base 是别号区的起始地址.byte_offset 是包含目标位的字节在位段里的序号.bit_number 是目标位所在地位(031).2.4.2 利用实例下例揭示了如何把寄存器RCC_CR的PLLON[24]位,映照到别号区:/* Peripheral base address in the bitband region */#define PERIPH_BASE ((u32)0x40000000)/* Peripheral address in the alias region */#define PERIPH_BB_BASE ((u32)0x42000000)/* RCC registers bit address in the alias region */#define RCC_OFFSET (RCC_BASE PERIPH_BASE)/* CR Register *//* Alias word address of PLLON bit */#define CR_OFFSET (RCC_OFFSET + 0x00)#define PLLON_BitNumber 0x18#define CR_PLLON_BB (PERIPH_BB_BASE + (CR_OFFSET * 32 (PLLON_BitNumber * 4))编写一个使能/失能PLL的函数,步调如下:...#define CR_PLLON_Set ((u32)0x01000000)#define CR_PLLON_Reset ((u32)0xFEFFFFFF)...void RCC_PLLCmd(FunctionalState NewState){if (NewState != DISABLE){ /* Enable PLL */RCC>CR |= CR_PLLON_Set;}else{ /* Disable PLL */RCC>CR &= CR_PLLON_Reset;}}Using bitband access this function will be coded as follows:void RCC_PLLCmd(FunctionalState NewState){*(vu32 *) CR_PLLON_BB = (u32)NewState;}2.5 运转时间检测固件函数库通过检查库函书的输入来实现运转时间错误侦测.通过使用宏assert_param来实现运转时间检测.所有请求输入参数的函数都使用这个宏.它可以检查输入参数是否在答应的范围以内.例:函数PWR_ClearFlagstm32f10x_pwr.c:void PWR_ClearFlag(u32 PWR_FLAG){/* Check the parameters */assert_param(IS_PWR_CLEAR_FLAG(PWR_FLAG));PWR>CR |= PWR_FLAG << 2;}stm32f10x_pwr.h:/* PWR Flag */#define PWR_FLAG_WU ((u32)0x00000001)#define PWR_FLAG_SB ((u32)0x00000002)#define PWR_FLAG_PVDO ((u32)0x00000004)#define IS_PWR_CLEAR_FLAG(FLAG) ((FLAG == PWR_FLAG_WU) || (FLAG == PWR_FLAG_SB)如果传给宏assert_param的参数为false,则调用函数assert_failed并返回被错误调用的函数所在的文件名和行数.如果传给宏assert_param的参数为true,则无返回值.宏assert_param编写于文件stm32f10x_conf.h中:/* Exported macro */#ifdef DEBUG/******************************************************************* ************ * * Macro Name : assert_param* Description : The assert_param macro is used for function's parameters check.* It is used only if the library is compiled in DEBUG mode.* Input : expr: If expr is false, it calls assert_failed function.* which reports the name of the source file and the source* line number of the call that failed.* If expr is true, it returns no value.* Return : None******************************************************************* ************/#define assert_param(expr) ((expr) ? (void)0 : assert_failed((u8 *)__FILE__,__LINE__))/* Exported functions */void assert_failed(u8* file, u32 line);#else#define assert_param(expr) ((void)0)#endif /* DEBUG */函数assert_failed编写于文件main.c或者其他用户C文件:#ifdef DEBUG/****************************************************************** * Function name : assert_failed* Description : Reports the name of the source file and the source line number.* where the assert_param error has occurred.* Input : file: pointer to the source file name* line: assert_param error line source number* Output : None* Return : None******************************************************************/ void assert_failed(u8* file, u32 line){/* User can add his own implementation to report the file name and line number, ex: printf("Wrong parameters value: file %s on line %d\r\n", file, line) *//* Infinite loop */while (1){}}#endif注:运转时间检查,即宏assert_param该当只在库在Debug模式下编译时使用.建议在用户利用代码的开发和调试阶段使用运转时间检查,在终极的代码中去掉它们以改进代码尺寸和速度.如果用户仍然但愿在终极的代码中保存这项功能,可以在调用库函数前,从头使用宏assert_param来测试输入参数.3. 外设固件概述本节零碎描述了每一个外设固件函数库.完好地描述所有相干函数并提供如何使用他们的例子.函数的描述按如下格式进行:函数名外设函数的名称输入参数{x}输入参数描述输出参数{x}输出参数描述返回值函数的返回值4. 模拟/数字转换器4.1 ADC寄存器结构4.2 ADC库函数5. 备份寄存器(BKP)5.1 BKP寄存器结构5.2 BKP库函数6控制器局域网(CAN)6.1 CAN寄存器结构6.2 CAN库函数7 DMA控制器(DMA)7.1 DMA寄存器结构7.2 DMA库函数8 内部间断/事件控制器(EXTI)8.1 EXTI寄存器结构8.2 EXTI库函数9 FLASH存储器(FLASH)9.1 FLASH寄存器结构9.2 FLASH库函数10 通用输入/输出(GPIO)GPIO驱动可以用作多个用处,包含管脚设置,单位设置/重置,锁定机制,从端口管脚读入或者向端口管脚写入数据.Section 10.1 GPIO寄存器结构描述了固件函数库所使用的数据结构,Section 10.2 固件库函数介绍了函数库里的所有函数.10.1 GPIO寄存器结构GPIO寄存器结构,GPIO_TypeDef和AFIO_TypeDef,在文件“stm32f10x_map.h”中定义如下:typedef struct{vu32 CRL;vu32 CRH;vu32 IDR;vu32 ODR;vu32 BSRR;vu32 BRR;vu32 LCKR;} GPIO_TypeDefTypedef struct{vu32 EVCR;vu32 MAPR;vu32 EXTICR[4];} AFIO_TypeDef;Table 178.例举了GPIO所有寄存器.Table 178. GPIO寄存器IDR端口输入数据寄存器ODR端口输出数据寄存器BSRR端口位设置/复位寄存器BRR端口位复位寄存器LCKR端口配置锁定寄存器EVCR事件控制寄存器MAPR复用重映照和调试I/O配置寄存器EXTICR内部间断线路015配置寄存器五个GPIO外设声明于文件“stm32f10x_map.h”:...#define PERIPH_BASE ((u32)0x40000000)#define APB1PERIPH_BASE PERIPH_BASE#define APB2PERIPH_BASE (PERIPH_BASE + 0x10000)#define AHBPERIPH_BASE (PERIPH_BASE + 0x20000)...#define AFIO_BASE (APB2PERIPH_BASE + 0x0000)#define GPIOA_BASE (APB2PERIPH_BASE + 0x0800) #define GPIOB_BASE (APB2PERIPH_BASE + 0x0C00) #define GPIOC_BASE (APB2PERIPH_BASE + 0x1000) #define GPIOD_BASE (APB2PERIPH_BASE + 0x1400) #define GPIOE_BASE (APB2PERIPH_BASE + 0x1800) #ifndef DEBUG...#ifdef _AFIO#define AFIO ((AFIO_TypeDef *) AFIO_BASE)#endif /*_AFIO */#ifdef _GPIOA#define GPIOA ((GPIO_TypeDef *) GPIOA_BASE)#endif /*_GPIOA */#ifdef _GPIOB#define GPIOB ((GPIO_TypeDef *) GPIOB_BASE)#endif /*_GPIOB */#ifdef _GPIOC#define GPIOC ((GPIO_TypeDef *) GPIOC_BASE)#endif /*_GPIOC */#ifdef _GPIOD#define GPIOD ((GPIO_TypeDef *) GPIOD_BASE)#endif /*_GPIOD */#ifdef _GPIOE#define GPIOE ((GPIO_TypeDef *) GPIOE_BASE)#endif /*_GPIOE */...#else /* DEBUG */...#ifdef _AFIOEXT AFIO_TypeDef *AFIO;#endif /*_AFIO */#ifdef _GPIOAEXT GPIO_TypeDef *GPIOA;#endif /*_GPIOA */#ifdef _GPIOBEXT GPIO_TypeDef *GPIOB;#endif /*_GPIOB */#ifdef _GPIOCEXT GPIO_TypeDef *GPIOC;#endif /*_GPIOC */#ifdef _GPIODEXT GPIO_TypeDef *GPIOD;#endif /*_GPIOD */#ifdef _GPIOEEXT GPIO_TypeDef *GPIOE;#endif /*_GPIOE */...#endif使用Debug模式时,初始化指针AFIO, GPIOA, GPIOB, GPIOC, GPIOD 和GPIOE 于文件“stm32f10x_lib.c”:#ifdef _GPIOAGPIOA = (GPIO_TypeDef *) GPIOA_BASE;#endif /*_GPIOA */#ifdef _GPIOBGPIOB = (GPIO_TypeDef *) GPIOB_BASE;#endif /*_GPIOB */#ifdef _GPIOCGPIOC = (GPIO_TypeDef *) GPIOC_BASE;#endif /*_GPIOC */#ifdef _GPIODGPIOD = (GPIO_TypeDef *) GPIOD_BASE;#endif /*_GPIOD */#ifdef _GPIOEGPIOE = (GPIO_TypeDef *) GPIOE_BASE;#endif /*_GPIOE */#ifdef _AFIOAFIO = (AFIO_TypeDef *) AFIO_BASE;#endif /*_AFIO */为了访问GPIO寄存器,, _GPIO, _AFIO, _GPIOA, _GPIOB, _GPIOC, _GPIOD和_GPIOE必须在文件“stm32f10x_conf.h”中定义如下:#define _GPIO#define _GPIOA#define _GPIOB#define _GPIOC#define _GPIOD#define _GPIOE#define _AFIO10.2 GPIO库函数Table 179. 例举了GPIO的库函数Table 179. GPIO库函数GPIO_Init根据GPIO_InitStruct中指定的参数初始化外设GPIOx寄存器GPIO_ReadInputData读取指定的GPIO端口输入GPIO_ReadOutputDataBit读取指定端口管脚的输出GPIO_ReadOutputData读取指定的GPIO端口输出GPIO_SetBits设置指定的数据端口位GPIO_ResetBits清除指定的数据端口位GPIO_WriteBit设置或者清除指定的数据端口位GPIO_Write向指定GPIO数据端口写入数据GPIO_PinLockConfig锁定GPIO管脚设置寄存器GPIO_EventOutputConfig选择GPIO管脚用作事件输出GPIO_EventOutputCmd使能或者失能事件输出10.2.1 函数GPIO_DeInitTable 180. 描述了函数GPIO_DeInit函数名GPIO_DeInit输入参数GPIOx:x可所以A,B,C,D或者E,来选择GPIO外设输出参数无返回值无例:/* Resets the GPIOA peripheral registers to their default resetvalues */GPIO_DeInit(GPIOA);10.2.2 函数GPIO_AFIODeInitTable 181. 描述了函数GPIO_AFIODeInitTable 181. 函数GPIO_AFIODeInit函数名GPIO_AFIODeInit输入参数无输出参数无返回值无先决条件无例:/* Resets the Alternate functions registers to their default resetvalues */GPIO_AFIODeInit();10.2.3 函数GPIO_InitTable 182. 描述了函数GPIO_InitTable 182. 函数GPIO_InitGPIO_Init输入参数1GPIOx:x可所以A,B,C,D或者E,来选择GPIO外设输入参数2GPIO_InitStruct:指向结构GPIO_InitTypeDef的指针,包含了外设GPIO的配相信息参阅Section:GPIO_InitTypeDef查阅更多该参数答应取值范围输出参数无返回值无先决条件无被调用函数无GPIO_InitTypeDef structureGPIO_InitTypeDef定义于文件“stm32f10x_gpio.h”:typedef struct{u16 GPIO_Pin;GPIOSpeed_TypeDef GPIO_Speed;GPIOMode_TypeDef GPIO_Mode;} GPIO_InitTypeDefGPIO_Pin该参数选择待设置的GPIO管脚,使用操纵符“|”可以一次选中多个管脚.可以使用下表中的任意组合.Table 183. GPIO_Pin值GPIO_Pin_1选中管脚1GPIO_Pin_2选中管脚2GPIO_Pin_3选中管脚3GPIO_Pin_4选中管脚4GPIO_Pin_5选中管脚5GPIO_Pin_6选中管脚6GPIO_Pin_7选中管脚7GPIO_Pin_8选中管脚8GPIO_Pin_9选中管脚9GPIO_Pin_10选中管脚10GPIO_Pin_11选中管脚11GPIO_Pin_12选中管脚12GPIO_Pin_15选中管脚15GPIO_Pin_All选中全部管脚GPIO_SpeedGPIO_Speed GPIO_Speed用以设置选中管脚的速率.Table 184. 给出了该参数可取的值.Table 184. GPIO_Speed值GPIO_SpeedGPIO_Mode用以设置选中管脚的工作形态.Table 185. 给出了该参数可取的值. Table 185. GPIO_Mode值GPIO_Mode_IPD下拉输入GPIO_Mode_IPU上拉输入GPIO_Mode_Out_OD开漏输出GPIO_Mode_Out_PP推挽输出GPIO_Mode_AF_OD复用开漏输出GPIO_Mode_AF_PP复用推挽输出留意:⏹当某管脚设置为上拉或者下拉输入模式,使用寄存器Px_BSRR和PxBRR ⏹GPIO_Mode答应同时设置GPIO方向(输入/输出)和对应的输入/输出设置,:位[7:4]对应GPIO方向,位[4:0]对应配置.GPIO方向有如下索引GPIO输入模式= 0x00GPIO输出模式= 0x01Table 186. 给出了所有GPIO_Mode的索引和编码Table 186. GPIO_Mode的索引和编码GPIO方向索引模式设置模式代码GPIO Input0x00 GPIO_Mode_AIN 0x00 0x00GPIO_Mode_IN_FLOATING 0x04 0x04GPIO_Mode_IPD 0x08 0x28GPIO_Mode_IPU 0x08 0x48GPIO Output0x01 GPIO_Mode_Out_OD 0x04 0x14GPIO_Mode_Out_PP 0x00 0x10GPIO_Mode_AF_OD 0x0C 0x1CGPIO_Mode_AF_PP 0x08 0x18例:/* Configure all the GPIOA in Input Floating mode */GPIO_InitTypeDef GPIO_InitStructure;GPIO_InitStructure.GPIO_Pin = GPIO_Pin_All;GPIO_InitStructure.GPIO_Speed = GPIO_Speed_10MHz;GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN_FLOATING;GPIO_Init(GPIOA, &GPIO_InitStructure);10.2.4 函数GPIO_StructInitTable 187. 描述了函数GPIO_StructInitTable 187. 函数GPIO_StructInit函数名GPIO_StructInit输入参数GPIO_InitStruct:指向结构GPIO_InitTypeDef的指针,待初始化输出参数无返回值无先决条件无Table 188. 给出了GPIO_InitStruct各个成员的缺省值Table 188. GPIO_InitStruct缺省值成员缺省值例:/* Initialize the GPIO Init Structure parameters */GPIO_InitTypeDef GPIO_InitStructure;GPIO_StructInit(&GPIO_InitStructure);10.2.5 函数GPIO_ReadInputDataBitTable 189. 描述了函数GPIO_ReadInputDataBitTable 189. 函数GPIO_ReadInputDataBit函数名GPIO_ReadInputDataBit输入参数1GPIOx:x可所以A,B,C,D或者E,来选择GPIO外设输入参数2GPIO_Pin:待读取的端口位参阅Section:GPIO_Pin查阅更多该参数答应取值范围先决条件无被调用函数无例:/* Reads the seventh pin of the GPIOB and store it in ReadValue variable */u8 ReadValue;ReadValue = GPIO_ReadInputDataBit(GPIOB, GPIO_Pin_7);10.2.6 函数GPIO_ReadInputDataTable 190. 描述了函数GPIO_ReadInputDataTable 190. 函数GPIO_ReadInputData函数名GPIO_ReadInputData输入参数GPIOx:x可所以A,B,C,D或者E,来选择GPIO外设输出参数无返回值GPIO输入数据端口值先决条件无例:/*Read the GPIOC input data port and store it in ReadValuevariable*/u16 ReadValue;ReadValue = GPIO_ReadInputData(GPIOC);10.2.7 函数GPIO_ReadOutputDataBitTable 191. 描述了GPIO_ReadOutputDataBitTable 191. 函数GPIO_ReadOutputDataBit函数名GPIO_ReadOutputDataBit输入参数1GPIOx:x可所以A,B,C,D或者E,来选择GPIO外设输入参数2GPIO_Pin:待读取的端口位参阅Section:GPIO_Pin查阅更多该参数答应取值范围返回值输出端口管脚值先决条件无被调用函数无例:/* Reads the seventh pin of the GPIOB and store it in ReadValue variable */u8 ReadValue;ReadValue = GPIO_ReadOutputDataBit(GPIOB, GPIO_Pin_7);10.2.8 函数GPIO_ReadOutputDataTable 192. 描述了函数GPIO_ReadOutputDataTable 192. 函数GPIO_ReadOutputData函数名GPIO_ReadOutputData输入参数GPIOx:x可所以A,B,C,D或者E,来选择GPIO外设输出参数无返回值GPIO输出数据端口值先决条件无例:/* Read the GPIOC output data port and store it in ReadValue variable */u16 ReadValue;ReadValue = GPIO_ReadOutputData(GPIOC);10.2.9 函数GPIO_SetBitsTable 193. 描述了GPIO_SetBitsTable 193. 函数GPIO_SetBits函数名GPIO_SetBits输入参数1GPIOx:x可所以A,B,C,D或者E,来选择GPIO外设输入参数2GPIO_Pin:待设置的端口位该参数可以取GPIO_Pin_x(x可所以015)的任意组合参阅Section:GPIO_Pin查阅更多该参数答应取值范围返回值无先决条件无被调用函数无例:/* Set the GPIOA port pin 10 and pin 15 */GPIO_SetBits(GPIOA, GPIO_Pin_10 | GPIO_Pin_15);10.2.10 函数GPIO_ResetBitsTable 194. 描述了GPIO_ResetBitsTable 194. 函数GPIO_ResetBits函数名GPIO_ResetBits输入参数1GPIOx:x可所以A,B,C,D或者E,来选择GPIO外设输入参数2GPIO_Pin:待清除的端口位该参数可以取GPIO_Pin_x(x可所以015)的任意组合参阅Section:GPIO_Pin查阅更多该参数答应取值范围输出参数无返回值无先决条件无被调用函数无例:/* Clears the GPIOA port pin 10 and pin 15 */GPIO_ResetBits(GPIOA, GPIO_Pin_10 | GPIO_Pin_15);10.2.11 函数GPIO_WriteBitTable 195. 描述了GPIO_WriteBitTable 195. 函数GPIO_WriteBit函数名GPIO_WriteBit输入参数1GPIOx:x可所以A,B,C,D或者E,来选择GPIO外设输入参数2GPIO_Pin:待设置或者清除指的端口位该参数可以取GPIO_Pin_x(x可所以015)的任意组合参阅Section:GPIO_Pin查阅更多该参数答应取值范围输入参数3BitVal: 该参数指定了待写入的值该参数必须取枚举BitAction的其中一个值Bit_RESET: 清除数据端口位Bit_SET: 设置数据端口位输出参数无返回值无先决条件无/* Set the GPIOA port pin 15 */GPIO_WriteBit(GPIOA, GPIO_Pin_15, Bit_SET);10.2.12 函数GPIO_WriteTable 196. 描述了GPIO_WriteTable 196. 函数GPIO_Write函数名GPIO_Write输入参数1GPIOx:x可所以A,B,C,D或者E,来选择GPIO外设输入参数2PortVal: 待写入端口数据寄存器的值输出参数无返回值无先决条件无被调用函数无例:/* Write data to GPIOA data port */GPIO_Write(GPIOA, 0x1101);10.2.13 函数GPIO_PinLockConfigTable 197. 描述了GPIO_PinLockConfigTable 197. 函数GPIO_PinLockConfig函数名GPIO_PinLockConfig输入参数2GPIO_Pin:待锁定的端口位该参数可以取GPIO_Pin_x(x可所以015)的任意组合参阅Section:GPIO_Pin查阅更多该参数答应取值范围输出参数无返回值无先决条件无被调用函数无例:/* Lock GPIOA Pin0 and Pin1 */GPIO_PinLockConfig(GPIOA, GPIO_Pin_0 | GPIO_Pin_1);10.2.14 函数GPIO_EventOutputConfigTable 198. 描述了GPIO_EventOutputConfigTable 198. 函数GPIO_EventOutputConfig函数名GPIO_EventOutputConfig输入参数1GPIO_PortSource: 选择用作事件输出的GPIO端口参阅Section:GPIO_PortSource查阅更多该参数答应取值范围输入参数2GPIO_PinSource:事件输出的管脚该参数可以取GPIO_PinSourcex(x可所以015)输出参数无返回值无先决条件无被调用函数无GPIO_PortSourceGPIO_PortSource用以选择用作事件输出的GPIO端口.Table 199. 给出了该参数可取的值Table 199. GPIO_PortSource值GPIO_PortSource描述GPIO_PortSourceGPIOC选择GPIOCGPIO_PortSourceGPIOD选择GPIOD/* Selects the GPIOE pin 5 for EVENT output */GPIO_EventOutputConfig(GPIO_PortSourceGPIOE, GPIO_PinSource5);10.2.15 函数GPIO_EventOutputCmdTable 200. 描述了GPIO_EventOutputCmdTable 200. 函数GPIO_EventOutputCmd函数名GPIO_EventOutputCmd输入参数1NewState: 事件输出的新形态这个参数可以取:ENABLE或者DISABLE输出参数无返回值无先决条件无例:/* Enable Event Ouput to the GPIOC pin 6 */GPIO_EventOutputConfig(GPIO_PortSourceGPIOC, GPIO_PinSource6);GPIO_EventOutputCmd(ENABLE);10.2.16 函数GPIO_PinRemapConfigTable 201. 描述了GPIO_ PinRemapConfigTable 201. 函数GPIO_ PinRemapConfig函数名GPIO_ PinRemapConfig函数本相void GPIO_PinRemapConfig(u32 GPIO_Remap, FunctionalStateNewState)功能描述改变指定管脚的映照输入参数1GPIO_Remap: 选择重映照的管脚参阅Section:GPIO_Remap查阅更多该参数答应取值范围输入参数2NewState: 管脚重映照的新形态这个参数可以取:ENABLE或者DISABLE输出参数无返回值无先决条件无被调用函数无GPIO_RemapGPIO_Remap用以选择用作事件输出的GPIO端口.Table 202. 给出了该参数可取的值Table 202. GPIO_Remap值GPIO_Remap描述GPIO_Remap_USART1USART1复用功能映照GPIO_PartialRemap_USART3USART2复用功能映照GPIO_FullRemap_USART3USART3复用功能完好映照GPIO_PartialRemap_TIM1USART3复用功能部分映照GPIO_FullRemap_TIM1TIM1复用功能完好映照GPIO_PartialRemap1_TIM2TIM2复用功能部分映照1GPIO_PartialRemap2_TIM2TIM2复用功能部分映照2GPIO_FullRemap_TIM2TIM2复用功能完好映照GPIO_PartialRemap_TIM3TIM3复用功能部分映照GPIO_FullRemap_TIM3TIM3复用功能完好映照GPIO_Remap_TIM4TIM4复用功能映照GPIO_Remap1_CAN CAN复用功能映照1GPIO_Remap2_CAN CAN复用功能映照2GPIO_Remap_PD01PD01复用功能映照GPIO_Remap_SWJ_NoJTRST除JTRST外SWJ完好使能(JTAG+SWDP)GPIO_Remap_SWJ_JTAGDisable JTAGDP失能 + SWDP使能例:/* I2C1_SCL on PB.08, I2C1_SDA on PB.09 */GPIO_PinRemapConfig(GPIO_Remap_I2C1, ENABLE);10.2.17 函数GPIO_EXTILineConfigTable 203. 描述了GPIO_EXTILineConfigTable 203. 函数GPIO_EXTILineConfig函数名GPIO_EXTILineConfig输入参数1GPIO_PortSource: 选择用作内部间断线源的GPIO端口参阅Section:GPIO_PortSource查阅更多该参数答应取值范围输入参数2GPIO_PinSource:待设置的内部间断线路该参数可以取GPIO_PinSourcex(x可所以015)输出参数无返回值无先决条件无被调用函数无例:/* Selects PB.08 as EXTI Line 8 */。

STM32固件库使用手册的中文翻译

UM0427用户手册之勘阻及广创作32位基于ARM微控制器STM32F101xx与STM32F103xx固件函数库介绍本手册介绍了32位基于ARM微控制器STM32F101xx与STM32F103xx的固件函数库。

该函数库是一个固件函数包,它由程序、数据结构和宏组成,包含了微控制器所有外设的性能特征。

该函数库还包含每一个外设的驱动描述和应用实例。

通过使用本固件函数库,无需深入掌握细节,用户也可以轻松应用每一个外设。

因此,使用本固态函数库可以大大减少用户的程序编写时间,进而降低开发成本。

每个外设驱动都由一组函数组成,这组函数覆盖了该外设所有功能。

每个器件的开发都由一个通用API (application programming interface 应用编程界面)驱动,API对该驱动程序的结构,函数和参数名称都进行了尺度化。

所有的驱动源代码都符合“Strict ANSIC”尺度(项目于范例文件符合扩充ANSIC尺度)。

我们已经把驱动源代码文档化,他们同时兼容MISRAC 尺度(根据需要,我们可以提供兼容矩阵)。

由于整个固态函数库依照“Strict ANSIC”尺度编写,它不受分歧开发环境的影响。

仅对话启动文件取决于开发环境。

该固态函数库通过校验所有库函数的输入值来实现实时错误检测。

该动态校验提高了软件的鲁棒性。

实时检测适合于用户应用程序的开发和调试。

但这会增加了成本,可以在最终应用程序代码中移去,以优化代码大小和执行速度。

想要了解更多细节,请参阅Section 2.5。

因为该固件库是通用的,而且包含了所有外设的功能,所以应用程序代码的大小和执行速度可能不是最优的。

对大多数应用程序来说,用户可以直接使用之,对于那些在代码大小和执行速度方面有严格要求的应用程序,该固件库驱动程序可以作为如何设置外设的一份参考资料,根据实际需求对其进行调整。

此份固件库用户手册的整体架构如下:⏹定义,文档约定和固态函数库规则。

STM32F405xx、STM32F407xx中文资料

1 带嵌入式闪存和静态随记存取存储器 SRAM(静态随记存取存储器)的 ARM®Cortex™-M4F 内核

ARM Cortex-M4F 处理器是最新一代用于嵌入式系统的 ARM 处理器。它的开发旨在提供 一个低成本平台,以满足 MCU 实现的需求,同时减少引脚数量和降低功耗,并提供卓越407xx

设备概述

目录

1 带嵌入式闪存和静态随记存取存储器 SRAM(静态随记存取存储器)的 ARM®Cortex™-M4F 内核 ..................................................................................................................................................1 2 自适应实时存储器加速器(ART Accelerator™) ........................................................................1 3 内存保护单元...............................................................................................................................1 4 嵌入式闪存...................................................................................................................................1 5 CRC(循环冗余校验)计算单元 ..............................

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1文档约定寄存器缩写列表下面的缩写用于描述寄存器Read/Write(rw)软件可读写Read-Only(r)软件只读Write-only(w)软件只写Read/clear(rc_w1)软件可读,写1清除,写0无作用Read/clear(rc_w0)软件可读,写0清除,写1无作用Read/clear by read软件可读,读后自动清零,写0无作用Read/set(rs)软件可读,可置位,写0无作用Read-only writeTrigger(rt_w)软件可读,写0或1翻转此位Toggle(t)写1翻转,写0无作用Reserved(Res.)保留位,必须保持复位值2存储器和总线架构2.1系统架构主系统包括32位多层互联AHB总线阵列,连接以下部件:Height masters—Cortex TM-M4F内核I-Bus(指令总线),D-bus(数据总线)和S-bus(系统总线)—DMA1存储器总线—DMA2存储器总线—DMA2外设总线—以太网DMA总线—USB OTG HS DMA总线Seven slaves—内置Flash存储器指令总线—内置Flash存储器数据总线—主内置SRAM1(112KB)—辅助内置SRAM2(16KB)—AHB1外设,包括AHB到APB的桥以及APB外设—AHB2外设—FSMC接口总线矩阵提供从主设备到从设备的访问,即使在有若干高速外设同时运行的情况下也能并行访问并高效运转。

这个架构如图1所示。

注意:64KB的CCM(内核耦合存储器core coupled memory)数据RAM并不是总线矩阵的一部分,它只能通过CPU来访问。

图1系统架构2.1.1S0:指令总线这条总线连接Cortex TM-M4F内核的指令总线到总线矩阵,用于内核取指。

总线的Target是存储有代码的存储器(包括内置Flash存储器/SRAM以及通过FSMC外扩的外部存储器)。

2.1.2S1:数据总线这条总线连接Cortex TM-M4F的数据总线和64KB的CCM数据RAM到总线矩阵,用于内核立即数的load以及调试访问。

总线的Target是存储有代码和数据的存储器(包括内置Flash存储器以及通过FSMC外扩的外部存储器)。

2.1.3S2:系统总线这条总线连接Cortex TM-M4F的系统总线到总线矩阵,用于访问位于外设或者SRAM 中的数据,指令也可通过这条总线取指(但是没有从ICode中取指效率高)。

总线的Target 是112KB和16KB内置SRAMs,AHB1外设,APB外设,AHB2外设以及通过FSMC外扩的外部存储器。

2.1.4S3、S4:DMA存储器总线这条总线连接DMA存储器总线主设备接口到总线矩阵,用于DMA在存储器中执行传送指令。

总线的Target是内置SRAM和通过FSMC外扩的外部存储器。

2.1.5S5:DMA外设总线这条总线连接DMA外设主总线接口到总线矩阵,用于DMA访问AHB外设或者执行存储器之间的传送指令。

总线的Target是AHB和APB外设加(plus)数据存储器:内部SRAM和通过FSMC外扩的外部存储器。

2.1.6S6:以太网DMA总线这条总线连接以太网DMA主设备接口到总线矩阵,用于以太网DMA加载或传送数据到一个存储器。

总线的Target是内置SRAM和外部通过FSMC外扩的存储器。

2.1.7S7:USB OTG HS DMA总线这条总线连接USB OTG HS DMA主设备接口到总线矩阵,用于USB OTG DMA加载或存储数据到一个存储器。

总线的Target是数据存储器:内置SRAM和外部通过FSMC 外扩的存储器。

2.1.8总线矩阵总线矩阵管理主设备之间的访问仲裁,仲裁用了一系列的算法。

2.1.9AHB/APB桥(APB)APB1和APB2两个AHB/APB桥提供AHB到两个APB之间的全速同步连接,允许外设频率的灵活选择。

设备复位以后,所有的外设时钟都是禁止的(除了SRAM和Flash存储器接口)。

在使用一个外设之前,必须在RCC_AHBxENR或者RCC_APBxENR寄存器中使能相应的时钟。

注意:当产生一个对APB寄存器16位或者8位的访问时,此次访问会被转换成一个32位的访问:桥会复制这个16或8位的数据来提供给32位的向量。

2.2存储器结构程存、数存、寄存器和IO端口被安排在一个线性的4G地址空间里。

字节在存储器中按照小端格式编码。

一个字中的最低字节被称为最低有效字节。

……可寻址的存储器空间被分为8个主要的块,每一个为512MB。

存储器中所有没有分配区域都被称为“保留”。

2.3存储器映射下图给出了在F40x和F41x中可用的外设的边界地址。

2.3.1内置SRAMSTM32F40x和STM32F41x内置了4K的备份SRAM和192K的系统SRAM。

系统SRAM可以按字节、半字、全字访问。

SRAM的起始地址是0x20000000.可以以CPU的速度并0等待地对SRAM进行读写操作。

系统SRAM被分成三个块,112KB,64KB和16KB。

有被AHB主机(比如以太网或者USB OTG HS)并行访问的能力:比如以太网可以在CPU读写112KSRAM的同时读写16KSRAM。

CPU可以通过系统总线访问系统SRAM或者在选择从SRAM中启动或者选择物理重映射时通过指令总线/数据总线访问。

为了达到SRAM执行的最大效率,应该选择物理重映射。

2.3.2位带Cortex-M4F存储器映射表中两个位带区。

这些区域把位带区的一个位映射到别名区的一个字。

对别名区的写操作会对位带区相应的位产生如同读-改-写操作。

在STM32F40x和STM32F41x中的外设寄存器和SRAM都映射到一个位带区,所以就可以对单个位进行读写操作。

这个操作只能Cortex-M4F来进行,而不是其他总线主机。

下面的计算公式给出了别名区的字和位带区的位之间的关系:bit_word_addr=bit_band_base+(byte_offset x32)+(bit_number×4)这里:bit_word_addr是位带区的位相应的别名区的字的地址bit_band_base是别名区的起始地址byte_offset是包含目标位的字节的数字Bit_number是目标位在包含它的字节中的位置(0-7)实例:下面的例子展示了怎样计算在位于SRAM地址0x20000300的字节的bit2对应别名区的字的地址:0x22006008=0x22000000+(0x300*32)+(2*4)写地址0x22006008和对位于SRAM地址0x20000300的字节的bit2进行读-改-写操作会产生同样的效果。

读地址0x22006008会返回位于SRAM地址0x20000300的字节的bit2的值(0x01:bit set,0x02:bit reset).2.3.3内置Flash存储器Flash存储器有以下特性:·1MB的容量·128位宽的数据读操作·字节、半字、字、双字的写操作·支持扇区和块擦除·存储器组织Flash存储器的结构如下:-整个存储区分为4个16KB、1块64KB和7块128KB-可在设备选择系统内存引导模式时作为系统内存-512字节的用户OTG(one-time programmable)空间.OTG区域包括额外的16字节用于锁定相应的OTG数据块。

-配有用于在设备处于等待或者停止模式时配置读写保护、BOR等级、软硬件看门狗以及复位的可选字节。

2.3.4Flash存储器读接口CPU时钟频率和Flash存储器读出时间的关系为了正确的从Flash存储器中读出数据,必须根据Cortex-M4TM内核时钟频率和设备的供电电压在Flash访问控制寄存器(Flash access control register FLASH_ACR)中正确配置等待状态的数目(等待时间)。

表三给出了等待状态和内核时钟频率之间的对应关系。

注意:当VOS=‘0’时,f HCLK的最大值为144MHz。

复位之后,CPU的时钟频率为16MHz,FLASH_ACR寄存器中配置的等待状态为0个。

强烈建议使用一下软件步骤根据CPU频率来调整访问Flash存储器的需要的等待状态数量。

提高CPU频率·在FLASH_ACR寄存器中配置新的等待状态的数目。

·通过读寄存器FLASH_ACR中的LATENCY来检查新的等待状态数目是否写入。

·通过写寄存器RCC_CFGR(RCC clock configuration register)中的SW位来修改CPU时钟源。

·如果需要,通过写寄存器RCC_CFGR的HPRE为来修改CPU时钟的分频系数。

·通过读时钟源状态位(SWS)和AHB预分频系数(HPRE)来检查设置的时钟源和预分频系数是否已经有效。

降低CPU频率·通过写寄存器RCC_CFGR(RCC clock configuration register)中的SW位来修改CPU时钟源。

·如果需要,通过写寄存器RCC_CFGR的HPRE为来修改CPU时钟的分频系数。

·通过读时钟源状态位(SWS)和AHB预分频系数来检查设置的时钟源和预分频系数是否已经有效。

·在FLASH_ACR寄存器中配置新的等待状态的数目。

·通过读寄存器FLASH_ACR中的LATENCY来检查新的等待状态数目是否写入。

注意:对时钟源或等待状态的配置并不一定会立即生效。

为了确保当前频率就是你所配置的频率,你可以去检查AHB分频系数和时钟源状态位。

要确保对等待状态的配置是否已经生鲜,你可以查看FLASH_ACR寄存器中的SW位。

FLASH_ACR寄存器用于开启或关断加速特性以及根据CPU频率来控制Flash存储器的访问时间。

下表提供了FLASH_ACR寄存器的详细描述。

Flash access control register(FLASH_ACR)FLASH_ACR寄存器用于开启或关断加速特性以及根据CPU频率来控制Flash存储器的访问时间。

偏移地址:0x00复位值:0x00000000访问:无等待状态,字,半字或字节访问Bits31:11保留位,必须保持清除(为0)。

Bit12DCRST:Data cache reset数据缓存复位0:数据缓存没有复位1:数据缓存复位当数据缓存(D cache)禁止时,此位只写。

Bit11ICRST:Instruction cache reset指令缓存复位0:指令缓存没有复位1:指令缓存复位Bit10DCEN:Data cache enable数据缓存使能0:数据缓存禁止1:数据缓存使能Bit9ICEN:Instruction cache enable指令缓存使能0:指令缓存禁止1:指令缓存使能Bit8PRFTEN:Prefetch enable预取指使能0:预取指禁止1:预取指使能Bits7:3保留,必须保持0Bits2:0LATENCY:Latency等待时间这些位描述了CPU时钟周期和Flash存储器访问时间的比率000:0等待状态001:1个等待状态010:2个等待状态011:3个等待状态100:4个等待状态101:5个等待状态110:6个等待状态111:7个等待状态2.3.5自适应实时存储器加速器(ART Accelerator TM)ART Accelerator TM是一个为STM32工业标准Cortex-M4TM内核优化的一个存储器加速器。