VHDL课程设计-PS2键盘

PS2接口键盘的输入识别电路设计

河海大学计算机与信息学院(常州)课程设计报告题目PS2接口键盘的输入识别电路设计专业、学号授课班号278605学生姓名指导教师完成时间2012年9月3日摘要本次HDL项目设计的主要目标是PS2接口键盘的输入识别电路设计。

PS/2 键盘是一种常用的计算机输入设备,稍加改动, 便可很方便的应用在各种嵌入式系统中。

本文提出了一种利用 FPGA 来设计 PS/2 接口的方法, 查阅了解资料PS/2 接口协议,运用verilog HDL语言编写程序,并用Quartus II编译,写入试验箱。

结果实现了0~9十个数字的识别并且按下Backspace能够清空四个数码管,表明此方法有容易实现模块化和移植性强的特点。

关键词: PS/2 接口嵌入式系统FPGAABSTRACTThe HDL project design goal is PS2 port keyboard input recognition circuit design.PS / 2 keyboard is a commonly used computer input devices, a little change can be very convenient application in a wide variety of embedded systems. This paperpresents a use of FPGA design PS / 2 interface, data access for PS / 2 interface protocol, using verilog HDL language programming and Quartus II compiler, write test chamber.0 to 9 ten numeric identification results and press the Backspace to clear the fourdigital tube,This method is easy to achieve modularity and portability. Keyword:PS / 2 interface Embedded Systems FPGA系统设计一、要求的设计目标1、设计要求:(1)以通用的PS2键盘为输入,设计一个能够识别PS2键盘输入编码的电路,并把键值通过数码管显示;(2)至少能够识别0~9的数字键。

FPGA基础设计_PS2键盘控制及短按、长按

FPGA基础设计_PS2键盘控制及短按、长按

PS2键盘也是一个经典的实验,可能很多人接触如何对通信协议、时序编程就是从这个实验开始学习的。

USB键盘已经很普及,现在市场上还是有一些USB转PS2的转接头,还有一些转换芯片。

这个实验虽然简单,不过不知道您有考虑过单按一次输出一个有效脉冲、短按、长按等这些是如何实现的么?这就涉及到一些时钟、边沿检测等设计问题。

PS2协议实现

我们见到的PS2的接口电路应该都是这样的:

一根时钟线、一根数据线完成通信,PS2通信的帧格式如下所示,时钟的下降沿数据有效:

按键在被按下时,会发送一个字节,这个码就是通码;按键在释放时,会发送两个字节,这个码就做断码(当然也有例外)。

每一个按键都有唯一的通码和断码,据此进行判断按下的是哪个键,从而执行对应的功能。

如一部分按键的通码和断码如下所示:

可以看出断码其实就是在通码前加了一个F0,比如A的通码是1C,则它的断码是F01C。

另外一些特殊功能的按键,在通码和断码前都会加个E0。

PS2解码的代码如下所示:

//-----------------ps2_clk下降沿捕获--------------------

//clk相当于中间采样点的作用,第一个下降沿到来说明起始位开始

reg ps2_clk0,ps2_clk1,ps2_clk2;//缓冲寄存器

wire ps2_clk_neg; //1表示检测到下降沿

reg ps2_state;

always @ (posedge clk or negedge rst_n)

if (!rst_n)

{ps2_clk0,ps2_clk1,ps2_clk2} 《= 3‘d0;

else。

基于VHDL的键盘扫描电路设计教材

毕业论文(设计)题目:基于VHDL的键盘扫描电路设计系:机电工程系学生姓名:专业:电子信息工程班级:指导教师:起止日期: 2012.10.15——2013.01.06 2013年1 月6 日基于VHDL的键盘扫描电路设计(东海科学技术学院机电工程系,浙江舟山 316000)摘要随着科技的发展,时代的进步,生活的需要,在我们生活的很多地方领域,都有键盘的应用,而且它的应用非常广,当然键盘扫描的方法也有很多种。

键盘是单片机系统设计中一种主要的信息输入接口,合理的设计,不仅可以节省系统的设计成本,更可以使仪器设备的操作变得更为简单、方便、快捷,很大程度上提高系统综合性能。

随着信息产业和微电子技术的发展,很多系统设计技术已经成为信息产业最热门的技术之一,在很多地方上都有应用,比如航空航天、医疗保健、通讯、广播、工业、测量测试等很多热门领域。

并且随着工艺的进步和技术的发展,向更广泛的应用领域扩展。

本次设计主要是运用VHDL硬件描述语言和图形设计综合方法,在MAX+PLUSⅡ软件平台的环境下建立波形文件,生成电路符号,设置输入端口,实现程序的模拟仿真,得到仿真波形图,才完成了键盘扫描电路的程序设计。

这个电路设计是一个关于小型的计算器的键盘按键电路的设计,主要由5个部分组成,它们分别为分频器电路、键盘扫描计数器电路、按键检测电路、按键抖动消除电路和键盘编码电路。

本次设计主要是设计一个4×4矩阵式的键盘扫描电路,它具有列扫描和行扫描的功能,有2个输入端口,分别为clk和col,同时也有2个输出端口,分别为row和bianma,按下按键的数据通过端口行、列线输入到FPGA芯片中去,FPGA芯片内部的扫描模块会将数据传送到编码器中进行编码,最终完成本次电路的设计。

在生活中是这种小型的计算器是非常常用的,虽然体型很小,但却被广泛的使用,很多其他的东西都是在这种小型的计算器的键盘的基础上设计的。

关键词:键盘扫描;VHDL;MAX+PLUSⅡ;仿真AbstractWith the development of science and technology, the progress of the times, the need of the life, we live in a lot of place fields, there are keyboard application, but its application is very wide, of course, the keyboard scanning method also has a lot of, the keyboard is the design of single-chip microcomputer system a main information input interface, a reasonable design, not only can save the design cost of system, it can make the equipment operation more simple, convenient, fast, greatly improve the overall system performance. With the development of information industry and the development of microelectronic technology, a lot of system design technology has become the information industry one of the hottest technologies, in many places have applications, such as aerospace, medical care, communication, broadcast, industrial, testing and many other hot areas. And with the technology progress and technology development, to the more widespread application domain expansion.The main design is the use of VHDL hardware description language and graphic design method in the MAX+PLUS software platform, established under the wave file, generating circuit symbols, set the input port, procedures to achieve the simulation, get the simulation waveform, to complete the keyboard scanning circuit design program. The circuit design is a small calculator keyboard circuit design, mainly is composed by 5 parts, which respectively as the divider circuit, keyboard scan counter circuit, key detection circuit, key jitter elimination circuit and keyboard coding circuit. The design is the design of a 4 x 4 matrix keyboard scanning circuit, it has a column scanning and scanning function, having 2 input ports, respectively CLK and col, but also has 2 output ports, respectively row and bianma, press the key data through the port line, line input to the FPGA chip, FPGA chip inside the scanning module can transmit data to the encoder for encoding, the final completion of the circuit design. In life is such a small calculator is very common, though very small in size, but it is widely used, many other things are in such a small calculator keyboard design based on.Key words:keyboard scan; VHDL ; MAX+PLUS Ⅱ;simulation目录第1章绪论 (1)1.1研究的意义和背景 (1)1.2键盘在国内外的发展状况 (1)1.3本课题研究的主要问题 (2)第2章键盘扫描电路总体设计 (3)2.1 设计工具的简介 (3)2.1.1VHDL硬件描述语言 (3)2.1.2MAX+PLUSⅡ的简介 (3)2.1.3FPGA芯片的介绍 (5)2.2键盘扫描电路的基本流程 (7)2.3键盘扫描电路的原理框图 (8)第3章键盘扫描电路的模块电路设计 (10)3.1分频器电路 (10)3.2键盘扫描计数器电路 (11)3.3按键检测电路 (12)3.4按键抖动消除电路 (13)3.5 键盘编码电路 (13)3.6 扫描电路总电路图 (14)第4章顶层设计 (16)4.1端口定义 (16)4.2仿真结果 (17)4.3电路符号 (17)第5章软件调试 (18)5.1 分频器电路中 (18)5.2键盘扫描计数器电路中 (19)5.3按键检测电路中 (20)5.4按键抖动消除电路中 (20)5.5键盘编码电路中 (21)总结 (23)致谢 (24)[参考文献] (25)附录 (26)第1章绪论1.1研究的意义和背景键盘与我们的生活息息相关,可以说是在我们的生活中是无处不在的,比如说手机键盘、电视机的键盘、电脑的键盘等等。

超完美VHDL数码管显示键值_PS2键盘控制实验

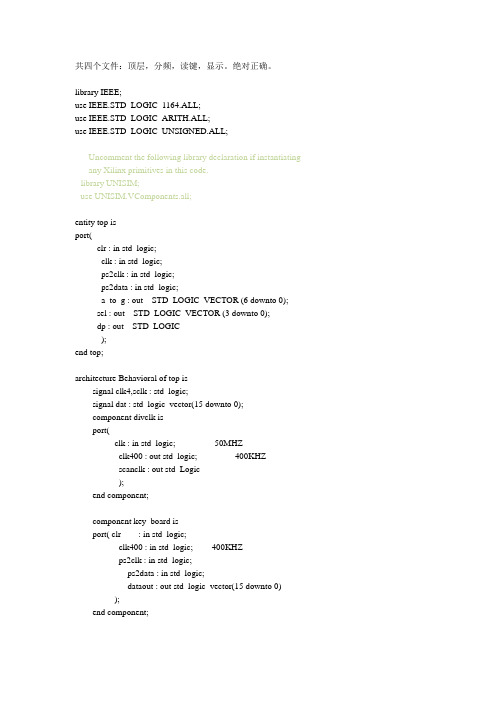

共四个文件:顶层,分频,读键,显示。

绝对正确。

library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;---- Uncomment the following library declaration if instantiating ---- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity top isport(clr : in std_logic;clk : in std_logic;ps2clk : in std_logic;ps2data : in std_logic;a_to_g : out STD_LOGIC_VECTOR (6 downto 0);sel : out STD_LOGIC_VECTOR (3 downto 0);dp : out STD_LOGIC);end top;architecture Behavioral of top issignal clk4,sclk : std_logic;signal dat : std_logic_vector(15 downto 0);component divclk isport(clk : in std_logic; ------50MHZclk400 : out std_logic; -------400KHZscanclk : out std_Logic);end component;component key_board isport( clr : in std_logic;clk400 : in std_logic; --400KHZps2clk : in std_logic;ps2data : in std_logic;dataout : out std_logic_vector(15 downto 0));end component;component disp isport(clr : in std_logic;scanclk : in std_logic;datain : in std_logic_vector(15 downto 0);a_to_g : out STD_LOGIC_VECTOR (6 downto 0);sel : out STD_LOGIC_VECTOR (3 downto 0);dp : out STD_LOGIC);end component;begininst1: divclk port map(clk,clk4,sclk);inst2: key_board port map(clr,clk4,ps2clk,ps2data,dat);inst3: disp port map(clr,sclk,dat,a_to_g,sel,dp);end Behavioral;library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;---- Uncomment the following library declaration if instantiating ---- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity divclk isport(clk : in std_logic; ------50MHZclk400 : out std_logic; -------400KHZscanclk : out std_Logic);end divclk;architecture Behavioral of divclk isbeginprocess(clk)variable count : std_logic_vector(19 downto 0):=X"00000"; beginif(rising_edge(clk))thencount:=count+1;end if;clk400<=count(2);scanclk<=count(12);end process;end Behavioral;library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;---- Uncomment the following library declaration if instantiating ---- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity key_board isport( clr : in std_logic;clk400 : in std_logic; --400KHZps2clk : in std_logic;ps2data : in std_logic;dataout : out std_logic_vector(15 downto 0));end key_board;architecture Behavioral of key_board issignal clk : std_logic:='0';signal data : std_logic:='0';signal shift1,shift2 : std_logic_vector(10 downto 0);signal ps2c,ps2d : std_logic;beginps2c<=ps2clk;ps2d<=ps2data;dataout<=shift1(8 downto 1) & shift2(8 downto 1);process(clk400,clr)variable tempclk : std_logic_vector(7 downto 0):=X"00"; variable tempdata: std_logic_vector(7 downto 0):=X"00"; beginif(clr='0') thentempclk:=X"00";tempdata:=X"00";clk<='0';data<='0';else if(clk400'event and clk400='1') thentempclk(0):=ps2c;tempclk(7 downto 1):=tempclk(6 downto 0);tempdata(0):=ps2d;tempdata(7 downto 1):=tempdata(6 downto 0); end if;end if;if(tempclk="11111111") thenclk<='1';elseif(tempclk="00000000") thenclk<='0';end if;end if;if(tempdata="11111111") thendata<='1';elseif(tempdata="00000000") thendata<='0';end if;end if;end process;process(clk,clr)beginif(clr='0')thenshift1<=(others => '0');shift2<=(others => '0');else if(clk'event and clk='0') thenshift1(10)<=data;shift1(9 downto 0)<=shift1(10 downto 1);shift2(10)<=shift1(0);shift2(9 downto 0)<=shift2(10 downto 1);-- shift1(0)<=data;-- shift1(10 downto 1)<=shift1(9 downto 0);-- shift2(0)<=shift1(10);-- shift2(10 downto 1)<=shift2(9 downto 0);end if;end if;end process;end Behavioral;library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;---- Uncomment the following library declaration if instantiating ---- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity disp isport(clr : in std_logic;scanclk : in std_logic;datain : in std_logic_vector(15 downto 0);a_to_g : out STD_LOGIC_VECTOR (6 downto 0);sel : out STD_LOGIC_VECTOR (3 downto 0);dp : out STD_LOGIC);end disp;architecture Behavioral of disp issignal S : std_logic_vector(1 downto 0);signal digit : std_logic_vector(3 downto 0);begindp<='1';process(scanclk)beginif rising_edge(scanclk) thenif(clr='0')thenS<="00";elseS<=S+1;end if;end if;end process;process(S)begincase S iswhen "00" =>digit<=datain(3 downto 0);sel<="0001";when "01" =>digit<=datain(7 downto 4);sel<="0010";when "10" =>digit<=datain(11 downto 8);sel<="0100";when others =>digit<=datain(15 downto 12);sel<="1000";end case;end process;process(digit)begin-- case digit is-- when X"0" => a_to_g<="0000001";-- when X"1" => a_to_g<="1001111";-- when X"2" => a_to_g<="0010010";-- when X"3" => a_to_g<="0000110";-- when X"4" => a_to_g<="1001100";-- when X"5" => a_to_g<="0100100";-- when X"6" => a_to_g<="0100000";-- when X"7" => a_to_g<="0001111";-- when X"8" => a_to_g<="0000000";-- when X"9" => a_to_g<="0000100";-- when X"A" => a_to_g<="0001000";-- when X"B" => a_to_g<="1100000";-- when X"C" => a_to_g<="0110001";-- when X"D" => a_to_g<="1000010";-- when X"E" => a_to_g<="0110000";-- when X"F" => a_to_g<="0111000";-- when others => a_to_g<="ZZZZZZZ";-- end case;case digit iswhen X"0" => a_to_g<="1111110";when X"1" => a_to_g<="0110000";when X"2" => a_to_g<="1101101";when X"3" => a_to_g<="1111001";when X"4" => a_to_g<="0110011";when X"5" => a_to_g<="1011011";when X"6" => a_to_g<="1011111";when X"7" => a_to_g<="1110000";when X"8" => a_to_g<="1111111";when X"9" => a_to_g<="1111011";when X"A" => a_to_g<="1110111";when X"B" => a_to_g<="0011111";when X"C" => a_to_g<="1001110";when X"D" => a_to_g<="0111101";when X"E" => a_to_g<="1001111";when X"F" => a_to_g<="1000111";when others => a_to_g<="ZZZZZZZ";end case;end process;end Behavioral;。

HDL-PS2接口键盘课程设计

课程设计报告题目HDL项目设计摘要:键盘是最常用人机接口设备之一,在嵌入式系统中有着相当广泛的应用。

一般自行设计的简易矩阵键盘仅仅是按行、列排列起来的矩阵开关。

当需要较多的按键时,则会占用较多的I/O 端口,在软件上则要进行上电复位按键扫描及通信处理,而且还要加上按键的去抖动处理,增大了软硬件开销。

而PS/2 键盘,内嵌自动去除按键抖动设计,自动地识别键的按下与释放,软硬件开发简便,价格便宜,稳定可靠,将PS/2 键盘作为嵌入式系统的输入设备已经成为可行的方案。

本设计是以现场可编程逻辑器件(FPGA)为核心的PS/2接口键盘的输入识别电路。

利用QuartusⅡ软件编写verilog HDL硬件描述语言程序以实现键盘部分简单键值的识别与输出。

本设计主要以程序为核心,硬件电路的搭建使用FPGA实验箱,将程序顶层文件里定义的输入输出端口与实验箱管脚进行相应的配置,除实验箱上的reset键以外,外设是一个与实验箱通过PS/2接口相连的键盘。

当系统上电后,实验箱上的数码管可以依次显示从键盘上输入的键值,并具有数码管清零功能。

关键词:Ps/2接口键盘、输入识别、FPGA 、Quartus Ⅱ、Verilog HDLAbstractThe keyboard, as one of the most commonly used man-machine interface equipment, has a wide application in embedded systems. General to design simple matrix keyboard is only per row, column arrangement up matrix switch. When need more button, will occupy more I/O port, in software, must carry on the power on the reset button scanning and communication processing, but also add buttons to jitter processing, increases the software and hardware cost. And PS / 2 keyboard, inline automatic remove key jitter design, automatically identify key press and release, software and hardware development is simple, cheap, stable and reliable, the PS / 2 keyboard as embedded system input device has become feasible scheme.This design based on field programmable logic devices (FPGA) is the core of the PS / 2 interface keyboard input identification circuit. Use verilog HDL Quartus Ⅱwriting software hardware description language program to realize the keyboard part simple key value of the recognition and output. This design mainly program as the core, the construction of the hardware circuit using FPGA experimental box, will be the top procedure defined in the file input/output port and experimental XiangGuan foot carries on the corresponding configuration, in addition to the experiment box on the reset button beyond, peripheral is a and experimental box through the PS / 2 interface connected keyboard. When the system is powered on, experiment box on the digital tube display can in turn from the keyboard input key value, and has the digital tube reset function.Keywords: Ps / 2 interface keyboard input identification FPGA,QuartusⅡVerilog HDL目录摘要2一.系统设计 51.1设计目标 51.2方案对比与确定 51.3总体设计框图及说明 61.3.1 总体设计框图 61.3.2总体设计端口说明 6 1.4模块电路设计及说明 7 1.4.1键盘数据接收部分 71.4.2数码管显示部分 8二.结果与讨论92.1调试步骤 9 2.2调试现象 92.3问题与分析 9三.软件设计103.1程序流程图 103.2程序设计 11四.心得体会17五.参考文献17六.附录18第一章系统设计1.1系统设计目标(1)以通用的PS2键盘为输入,设计一个能够识别PS2键盘输入编码的电路,并把键值通过数码管显示;(2)至少能够识别0~9的数字键。

一种基于VHDL的PS/2键盘接口设计

一种基于VHDL的PS/2键盘接口设计【摘要】介绍了一种基于VHDL的PS/2键盘接口设计方法,在EP2C5T144C8芯片上实现。

仿真和硬件测试表明,该设计具有可靠性高和可移植性强等优点,可方便地应用于各种基于FPGA/CPLD的嵌入式系统。

【关键词】PS/2接口;VHDL;FPGA1.引言随着社会的发展,嵌入式系统技术越来越多的应用到工业控制、汽车电子、航空航天、环境监测等领域中。

键盘作为嵌入式系统中的人机接口设备得到了广泛应用。

目前,嵌入式系统中采用的键盘有:独立按键式键盘、简易矩阵键盘。

独立按键式键盘有键盘个数少,可靠性低等缺点;而简易矩阵键盘的原理是行、列式的矩阵开关,需要单独设计制作,通用性和可移植性不强,且按键数较多时I/O利用率低,软件上为了提高可靠性还要进行延时去抖动、按键扫描以及与CPU 的通信处理等,一方面降低了系统的效率,另一方面增加了系统设计的成本。

微机系统中的PS/2键盘,具有内嵌式自动去除按键抖动设计,能自动地识别键的按下与释放,软硬件开发成本低且性能稳定;因此,将PS/2键盘作为嵌入式系统中的输入设备已成为业界研究的热点。

目前,关于PS/2键盘控制的应用大部分采用单片机或微机控制;与此相比,FPGA具有灵活性更强,集成度更高,容易移植等特点。

本文在分析PS/2协议、工作原理的基础上,给出了一种基于VHDL硬件描述语言的PS/2键盘接口的设计方法,并实现于Cyclone II EP2C5T144C8芯片上。

2.PS/2键盘接口协议2.1 物理特性PS/2设备接口用于许多现代的鼠标和键盘,常用为6脚mini-DIN,其引脚结构和外形如图1所示。

图1 PS/2硬件接口外形图PS/2设备分主从设备,其物理特性要求保证时钟、数据、电源和地线间的互相连接。

PS/2键盘靠PC的PS/2端口提供+5V电源,时钟和数据管脚为集电极开路形式,必须接大阻值的上拉电阻(一般设置在主设备中),主从设备间的数据通信采用双向同步方式传输,时钟信号一般由从设备产生。

基于FPGA的PS2键盘控制设计及仿真实现

本科毕业论文(设计)论文题目:基于FPGA的PS2键盘控制设计及仿真实现作者声明本毕业论文(设计)是在导师的指导下由本人独立撰写完成的,没有剽窃、抄袭、造假等违反道德、学术规范和其他侵权行为。

对本论文(设计)的研究做出重要贡献的个人和集体,均已在文中以明确方式标明。

因本毕业论文(设计)引起的法律结果完全由本人承担。

特此声明作者专业:通信工程作者学号:作者签名:年月日基于FPGA的PS2键盘控制设计及仿真实现The Design and Simulation Implementation of the PS2 Keyboard Control based on FPGA2013年5月10日摘要本文简述了PS2键盘的特点和工作原理,重点介绍了在FPGA 上实现PS2键盘的结构设计和VHDL代码设计。

PS2键盘具有价格低、通用可靠,且连接线少(仅使用2根信号线)的特点。

并可满足多种系统的要求。

FPGA(Field Programmable Gate Array)是一类高集成度的可编程逻辑器件,它结合EDA技术以硬件描述语言、电路原理图、状机等形式输入设计逻辑;并提供功能模拟、时序仿真等模拟手段,再经过一系列的变换,将输入逻辑转换成FPGA器件所需的编程文件,以实现专用集成电路ASIC。

应用FPGA设计PS2键盘控制器,不仅有硬件电路简单,更具灵活性,集成度高更容易移植等特点,更重要的是现代EDA(电子设计自动化)技术提供了一种很好的途径,利用VHDL硬件描述语言和FPGA器件可以很方便地构建键盘扫描模块。

设计使得使用VHDL语言基于FPGA芯片实现PS2键盘成为研究的方向。

本文对基于VHDL的PS2键盘实现进行了研究,并设计了PS2键盘。

所做的主要工作为:(1)以PS2键盘控制的基本理论为依据,对其进行了详细的讨论。

(2)本设计中采用了自上而下的层次化、模块化的设计思想,将整个接口划分为多个模块,同时利用VHDL语言的描述方法对各个功能模块进行了设计,最终完成了PS2键盘的系统设计。

基于VHDL利用PS_2键盘控制的密码锁设计_胡彩霞

《》2011年第5期在传统的数字电路设计实验中,如果要构建一个小型数字系统,通常要在数字电路试验箱中进行繁琐的搭线操作。

由于试验箱资源的限制使得所设计的数字系统功能会受到很大限制。

而FPGA 由于其集成度高和支持可在线编程的特点,修改电路设计变得如同修改程序一样方便[1]。

本文以电子密码锁的设计为实例,介绍了利用硬件编程语言VHDL 自顶向下地进行此系统的行为描述与结构设计,并介绍了PS/2键盘到主机的单向通信过程。

该设计中所用芯片的具体型号是XILINX 公司的具有40万门、208个管脚的SPARTAN XC3S400。

设计过程中下载模式采用主串模式,将程序下载到开发板上的EPROM 中,再由FPGA 将EPROM 中的程序读入片内编程RAM 中。

采用的EDA 开发工具为ISE 6,仿真工具是Modelsim 5.8a 。

1.数字密码锁的基本功能1.1功能描述:密码锁的设计主要达到以下四个功能:(1)密码锁加密:按下F1加密键,再按下0到9中的任四位数字作为密码。

(2)输入码激活:按下F2激活键,将已输入的四位数码作为密码或解锁码。

(3)解锁:按下F5解密键,输入的解锁码会与原密码会进行匹配。

如果成功,则开启密码锁;如果不成功,可继续解码,共有3次解密机会,当3次解密都不成功时,蜂鸣器产生报警信号宣告操作失败。

(4)数码输入:只有在按下F1加密键或F5解密键的前提下,按下0到9的数值才能显示到数码管上。

显示顺序是:随机按下的数码首先显示在四位数码管的最低位上,若确定此数码是想要的数码,再按下ENTER 键,便将此数码向左移动至左边第一个未显示的数码管上。

比如,初始时数码管显示为“XXXX ”(X 表示什么都不显示),按下一个9后,显示的是“XXX9”,再按下ENTER 键后,显示为“9XXX ”。

当输入的数码已达四位数时,按下F2激活键,便可将这四位数作为密码。

由于开发板上只有4个数码管,所以密码设定为4位,在实际中为了增加安全性,可以设置为更多位,还可将字母键扩展为密码。

基于单片机的PS2键盘设计

PS2键盘在单片机上的应用摘要:在嵌入式PC应用系统中,作为人机交互设备的键盘,往往采用结构简单按键少的矩阵键盘。

标准键盘虽然能直接与嵌入式PC机的PS/2接口相连,但是体积大,按键多,不能满足需求,本文提出用一种AT89C52单片机实现具有标准PS/2接口的矩阵键盘,具有便捷,实用的特点。

关键词:PS/2接口,PS/2键盘,拨号键,AT89C52,LCD1602Abstract:PS/2 interface is one of the most useful mouse interface.It was IBM’s patent named osulum before. It is the dedicate interface of mouse and keyboard. This text implied a plan using PS/2 to make a system. PS/2 tansmit the data which was pressed, and AT89C52 receive it ,disposed it and transmit it to Lcd1602. Lcd1602 discover it to make us know which key has been pressed. PS/2 simulate a phone’s dial keyboard. This system’s feature is the circuit is sample and useful.Keywords:PS/2 keyboard, AT89C52, LCD1602,PS/2 interface,dial keyboard目录1、前言 (1)2、整体方案设计 (2)2.1方案论证 (2)2.2方案比较 (3)3、单元模块设计 (4)3.1PS2键盘模块 (4)3.2单片机模块 (6)3.3LCD显示模块 (7)4、软件设计 (9)5、系统技术指标及精度和误差分析 (10)6、结论 (11)7、设计小结 (12)8、致谢 (14)9、参考文献 (14)附录1:电路总图 (15)附录2:仿真图 (16)附录3:软件代码 (17)1、前言单片机因其性价比高, 处理能力强, 且抗干扰能力好, 在医疗器械、机电液控制、数据传输等各类工控系统和设备仪器中得到广泛应用。

基于verilog的PS2键盘设计进阶

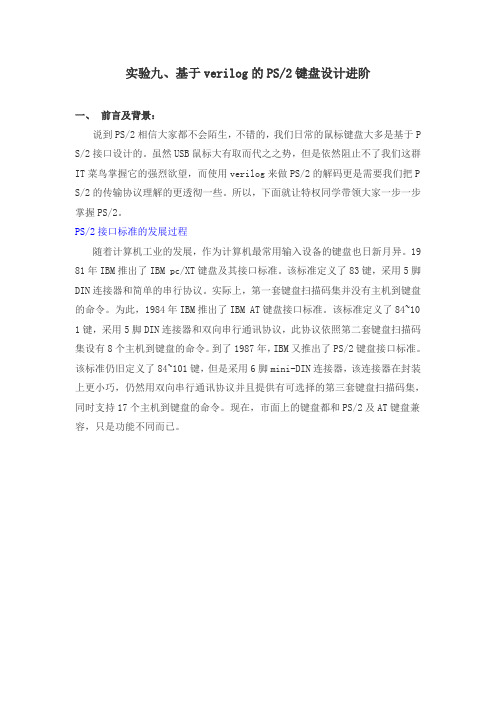

实验九、基于verilog的PS/2键盘设计进阶一、前言及背景:说到PS/2相信大家都不会陌生,不错的,我们日常的鼠标键盘大多是基于P S/2接口设计的。

虽然USB鼠标大有取而代之之势,但是依然阻止不了我们这群IT菜鸟掌握它的强烈欲望,而使用verilog来做PS/2的解码更是需要我们把P S/2的传输协议理解的更透彻一些。

所以,下面就让特权同学带领大家一步一步掌握PS/2。

PS/2接口标准的发展过程随着计算机工业的发展,作为计算机最常用输入设备的键盘也日新月异。

19 81年IBM推出了IBM pc/XT键盘及其接口标准。

该标准定义了83键,采用5脚DIN连接器和简单的串行协议。

实际上,第一套键盘扫描码集并没有主机到键盘的命令。

为此,1984年IBM推出了IBM AT键盘接口标准。

该标准定义了84~10 1键,采用5脚DIN连接器和双向串行通讯协议,此协议依照第二套键盘扫描码集设有8个主机到键盘的命令。

到了1987年,IBM又推出了PS/2键盘接口标准。

该标准仍旧定义了84~101键,但是采用6脚mini-DIN连接器,该连接器在封装上更小巧,仍然用双向串行通讯协议并且提供有可选择的第三套键盘扫描码集,同时支持17个主机到键盘的命令。

现在,市面上的键盘都和PS/2及AT键盘兼容,只是功能不同而已。

(4)延时20us(如果此时正在发送起始位,则应延时40us);(5)输出起始位(0)到数据线上。

这里要注意的是:在送出每一位后都要检测时钟线,以确保PC机没有抑制PS/2设备,如果有则中止发送;(6)输出8个数据位到数据线上;(7)输出校验位;(8)输出停止位(1);(9)延时30us(如果在发送停止位时释放时钟信号则应延时50us);通过以下步骤可发送单个位:(1)准备数据位(将需要发送的数据位放到数据线上);(2)延时20us;(3)把时钟线拉低;(4)延时40us;(5)释放时钟线;(6)延时20us。

用VHDL设计键盘输入显示方案

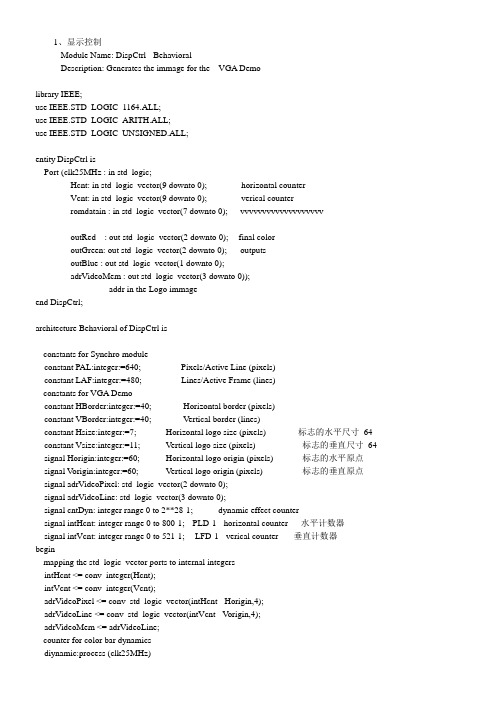

1、显示控制-- Module Name: DispCtrl - Behavioral-- Description: Generates the immage for the VGA Demo--------------------------------------------------------------------------------library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity DispCtrl isPort (clk25MHz : in std_logic;Hcnt: in std_logic_vector(9 downto 0); -- horizontal counterVcnt: in std_logic_vector(9 downto 0); -- verical counterromdatain : in std_logic_vector(7 downto 0); -- vvvvvvvvvvvvvvvvvvvoutRed : out std_logic_vector(2 downto 0); -- final coloroutGreen: out std_logic_vector(2 downto 0); -- outputsoutBlue : out std_logic_vector(1 downto 0);adrV ideoMem : out std_logic_vector(3 downto 0));-- addr in the Logo immageend DispCtrl;architecture Behavioral of DispCtrl is-- constants for Synchro moduleconstant PAL:integer:=640; --Pixels/Active Line (pixels)constant LAF:integer:=480; --Lines/Active Frame (lines)-- constants for VGA Democonstant HBorder:integer:=40; -- Horizontal border (pixels)constant VBorder:integer:=40; -- V ertical border (lines)constant Hsize:integer:=7; -- Horizontal logo size (pixels) 标志的水平尺寸64 constant Vsize:integer:=11; -- V ertical logo size (pixels) 标志的垂直尺寸64 signal Horigin:integer:=60; -- Horizontal logo origin (pixels) 标志的水平原点signal V origin:integer:=60; -- V ertical logo origin (pixels) 标志的垂直原点signal adrVideoPixel: std_logic_vector(2 downto 0);signal adrVideoLine: std_logic_vector(3 downto 0);signal cntDyn: integer range 0 to 2**28-1; -- dynamic effect countersignal intHcnt: integer range 0 to 800-1; --PLD-1 - horizontal counter--- 水平计数器signal intVcnt: integer range 0 to 521-1; -- LFD-1 - verical counter --- 垂直计数器begin-- mapping the std_logic_vector ports to internal integersintHcnt <= conv_integer(Hcnt);intVcnt <= conv_integer(Vcnt);adrV ideoPixel <= conv_std_logic_vector(intHcnt - Horigin,4);adrV ideoLine <= conv_std_logic_vector(intVcnt - V origin,4);adrV ideoMem <= adrVideoLine;-- counter for color bar dynamicsdiynamic:process (clk25MHz)beginif clk25MHz'event and clk25MHz = '1' thencntDyn <= cntDyn+1;end if;end process;mixer: process(clk25MHz,intHcnt, intVcnt)beginif intHcnt < PAL and intVcnt < LAF then -- 在激活的显示区域if intHcnt >= Horigin and intHcnt <= Horigin + Hsize andintVcnt >= V origin and intVcnt <= V origin + Vsizethen -- image --rom中的数据输出作为色差的信息;if romdatain(adrVideoPixel)='0' thenoutRed<="100";outGreen<="100";outBlue(1 downto 0) <="01";else -- the moving lines area-- redoutRed(2 downto 0) <="000";-- greenoutGreen(2 downto 0) <="000";-- blueoutBlue(1 downto 0) <="00";end if;elseoutRed <= (others => '0');outGreen <= (others => '0');outBlue <= (others => '0');end if;end if;end process;-- place the logo at the mouse pos, if left button pressedend Behavioral;2 、PS接口定义见附件中Keyctrl.vhd和Ps2keyboard.vhd3、状态灯指示字母输入见附件中SnakeledDemo.vhd。

北邮数电实验——PS2键盘

实验名称:PS2键盘接口设计姓名:金小敏学号:班级:一、实验任务设计制作一个PS/2 键盘接口控制器。

(a)基本功能按照PS/2 键盘接口标准设计一个控制器,接收PS/2 键盘发送的数据,用数码管和8×8 点阵显示接收到的键值。

其中0~9 用数码管显示,A~Z用8×8 点阵显示,接收到其他键值则不显示。

(b)拓展功能(i)实现显示汉字、符号:按F3显示汉字“中”、按F4显示汉字“国”、按F5显示心型符号;(ii)实现音乐播放控制:按F1开始播放音乐、按F2停止播放音乐。

二、系统设计(a)设计思路系统总的分为输入输出两大部分。

输入即为PS2键盘,输出有显示输出:8×8点阵、数码管,声音输出。

根据PS2的协议,PS2按键的输出包含扫描码和断码,本次实验只使用扫描码。

将扫描码解码出来后,即可作为不同的判断条件来控制输出。

输出包括数码管显示、点阵显示和声音输出。

将其设计为:0~9按键时只有数码管显示对应数字,点阵熄灭;A~Z时只有点阵显示,数码管熄灭;按F1时,开始播放音乐并且点阵显示音乐符号“♫”;按F2时,停止播放音乐并且点阵熄灭;按F3时显示汉字“中”;按F4显示汉字“国”;按F5显示“♡”。

程序设计为四大模块:解码模块、显示模块、分频模块、音乐模块。

(b)总体框图(i)系统模块键盘输入(ii )状态转移图(c)分块设计:(1)PS2解码模块 ①输入输出框图:位)ret:选择信号p_clk:PS2键盘时钟信号 p_dat:PS2键盘数据信号 ②原理及算法:从键盘/鼠标发送到主机的数据在时钟信号的下降沿当时钟从高变到低的时候被读取从主机发送到键盘/鼠标的数据在上升沿当时钟从低变到高的时候被读取不管通讯的方向怎样键盘/鼠标总是产生时钟信号。

一次数据组成为:1位起始位(总为0),8位数据位(低位在前),1位奇校验位,1位停止位(总为1)。

由于本次实验只用到扫描码,所以只要接收第一段数据即可。

可编程器件与硬件描述语言VHDL_PS2键盘

PS2键盘扫描总原理图:说明:总的原理图中共包含4个模块,分别是PS2键盘按键数据读取模块KEY_DATA、数据转换模块CONVERT、数码管显示模块LED、液晶显示模块LCD,以下就各个模块分别作进一步的说明:(1)PS2键盘按键数据读取模块KEY_DATA宏模块图:VHDL代码:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity KEY_DATA isport(sys_clk : in STD_LOGIC;k_data : in STD_LOGIC;k_clock : in STD_LOGIC;reset : in STD_LOGIC;data : out STD_LOGIC_VECTOR(7 DOWNTO 0);request : out STD_LOGIC);end KEY_DATA;architecture Behavioral of KEY_DATA issignal tmp : STD_LOGIC_VECTOR(11 downto 0) :="000000000000"; --记录一帧的信号signal now_kbclk,pre_kbclk : std_logic;signal scan : STD_LOGIC_VECTOR(10 DOWNTO 0);beginprocess(reset,k_clock,sys_clk)beginif reset='1' then tmp<="000000000000";elsif sys_clk'event and sys_clk='1' thenpre_kbclk <= now_kbclk;now_kbclk <= k_clock;if(pre_kbclk > now_kbclk) then --检测到ps2键盘时钟的下降沿if tmp(0)='0' thentmp <= k_data & "01111111111"; --开始存入数据,"01111111111"中的"0"用于之后判断一帧数据是否读取完毕elsetmp <= k_data & tmp(11 downto 1); --存数据end if;end if;end if;end process;process(tmp)beginif tmp(0) = '0' then --一帧数据读取完毕scan <= tmp(11 downto 1);data <= scan(8 downto 1);request<='1';elsedata <="00000000";request<='0';end if;end process;end Behavioral;管脚说明:reset为复位信号,高电平有效,使输出置0;sys_clk为系统时钟信号(25MHz);k_clock为键盘时钟信号;k_data为键盘数据信号;data(7:0)为输出信号,表示读取的键盘扫描码;request也为输出信号,该管脚为”1”表示一次按键的扫描码已读取完毕,用以通知后续转换电路将扫描码转换为ASCII码。

VHDL键盘心得体会

课程设计一开始,老师先让我们熟悉了实验指导书上的实验一到实验六这六个实验,目的旨在于让我们熟悉课程设计的步骤以及相关的软硬件知识。

这六个实验相对来说比较简单,我与同学们基本上实现了仿真,只是我拿到的数据线有问题,实验的先前阶段我又没有发现这问题,所以一直没有实现仿真,后来问了下同学,才知道是数据线的问题,找到了症结所在,接下来的事就水到渠成了。

课程设计不可能不碰到一些问题比如:硬件的问题,软件的问题,程序的问题。

我们这次课程设计使用的是新的设备,所以基本上没有出现硬件故障,只是有个别同学没有看设备的使用说明书,在做实验时碰到了一些操作问题,像什么数字信号模块的时钟没有选对啊,实验箱的电源没有插好啊等等。

仿真软件也由于我们先前做了六个基本实验,碰到的问题也不到,哦,记起来了,有个问题困扰了我们很多同学,就是把实验箱与电脑连接的时候,发现实验箱与电脑无法正常的进行数据交换,我们很多同学开始都在想是不是实验箱坏了,后来发现是电脑没有找到硬件,经过扫描让电脑找到新的硬件后,问题也随之解决了。

碰到问题最多的是在编程的时候,众所周知,编写程序是项很枯燥无味的事,幸好我们有些例子程序,这样我们也不需要完全把程序编出来,只要编某个模块就行了,这次使用的实验箱上的接口有很多是共用一个端口,这给我们造成了很大的麻烦,要不是老师告诉使用动态扫描的方法,我们也许还不能实现这次课程设计的仿真。

我们可以通过按下外接键盘的按键,使实验箱上除了显示键盘的扫描码外播放音乐的基准音符,也可以通过12位LED灯的点亮数目来记录你按下了多少次按键。

设计之初,我对EDA知识的掌握应该说是还没入门,随着设计的深入,碰到了一系列的问题,为了实现仿真,我们就不得不去解决这一系列的问题,这样在解决问题的过程中我们不知不觉的就对EDA知识有了更深的了解,同时也巩固了以前的知识。

通过编程,我发现VHDL语言跟C语言、汇编语言在某些方面是相通的,所以无形之中我也对计算机语言有了更深的认识。

最新vhdl课程设计_ps2键盘教学文案

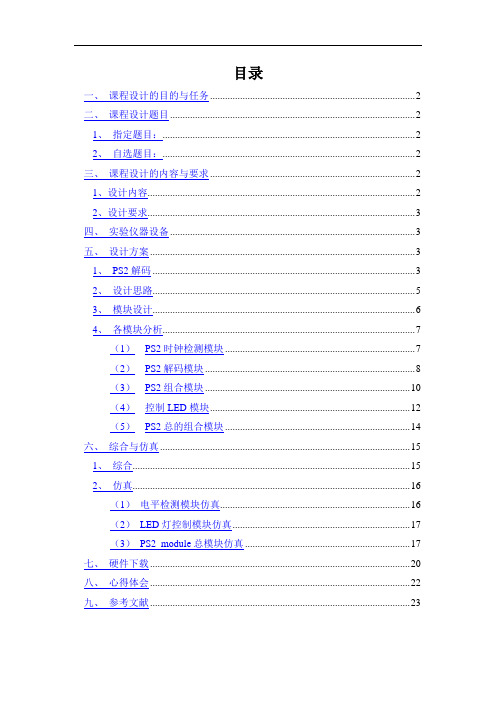

目录一、课程设计的目的与任务 (2)二、课程设计题目 (2)1、指定题目: (2)2、自选题目: (2)三、课程设计的内容与要求 (2)1、设计内容 (2)2、设计要求 (3)四、实验仪器设备 (3)五、设计方案 (3)1、PS2解码 (3)2、设计思路 (5)3、模块设计 (6)4、各模块分析 (7)(1)PS2时钟检测模块 (7)(2)PS2解码模块 (8)(3)PS2组合模块 (10)(4)控制LED模块 (12)(5)PS2总的组合模块 (14)六、综合与仿真 (15)1、综合 (15)2、仿真 (16)(1)电平检测模块仿真 (16)(2)LED灯控制模块仿真 (17)(3)PS2_module总模块仿真 (17)七、硬件下载 (20)八、心得体会 (22)九、参考文献 (23)一、课程设计的目的与任务(1)熟练掌握EDA工具软件QuartusII的使用;(2)熟练用VHDL硬件描述语言描述数字电路;(3)学会使用VHDL进行大规模集成电路设计;(4)学会用CPLD\FPGA使用系统硬件验证电路设计的正确性;(5)初步掌握EDA技术并具备一定的可编程逻辑芯片的开发能力;二、课程设计题目1、指定题目:0 :多功能计数器;1 :数字秒表;2 :简易数字钟;3 :简易频率计;4 :彩灯控制器;5 :交通灯控制器;6 :四路智力竞赛抢答器;7 :简易微波炉控制器;8 :表决器;9 :数字密码锁;我的的学号尾数是2,所以我要做的题目是简易数字钟。

由于我之前已经学过Verilog HDL和VHDL,所以简易数字钟相对于我比较简单,我完成了简易数字钟并验收后,再选择了另一个自选题目来完成。

简易数字钟:设计一个以“秒”为基准信号的简易数字钟,显示时、分、秒,同时可实现整点报时和清零(我已经完成,而且已经验收了)。

2、自选题目:在完成了数字钟的设计后,我选择了另一个设计的题目,那就是PS2键盘扫描。

所以这次课程设计我的报告主要详细写的是PS2键盘扫描的程序,而不是简易数字钟。

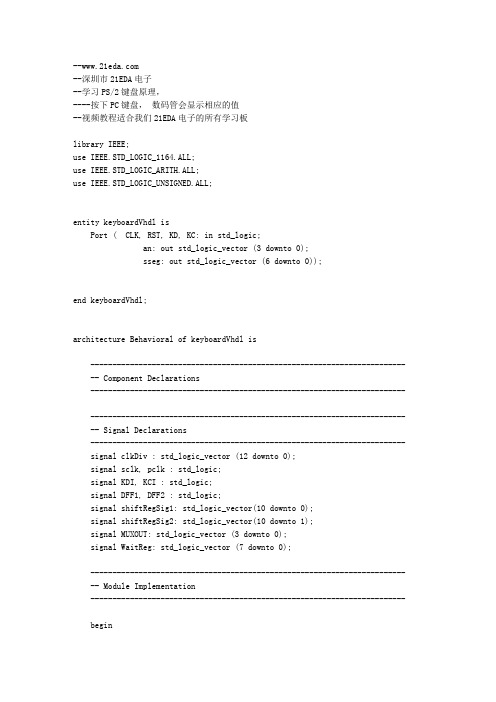

EDA_FPGA_VHDL_PS2键盘

--深圳市21EDA电子--学习PS/2键盘原理,----按下PC键盘,数码管会显示相应的值--视频教程适合我们21EDA电子的所有学习板library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity keyboardVhdl isPort ( CLK, RST, KD, KC: in std_logic;an: out std_logic_vector (3 downto 0);sseg: out std_logic_vector (6 downto 0));end keyboardVhdl;architecture Behavioral of keyboardVhdl is------------------------------------------------------------------------ -- Component Declarations------------------------------------------------------------------------------------------------------------------------------------------------ -- Signal Declarations------------------------------------------------------------------------ signal clkDiv : std_logic_vector (12 downto 0);signal sclk, pclk : std_logic;signal KDI, KCI : std_logic;signal DFF1, DFF2 : std_logic;signal shiftRegSig1: std_logic_vector(10 downto 0);signal shiftRegSig2: std_logic_vector(10 downto 1);signal MUXOUT: std_logic_vector (3 downto 0);signal WaitReg: std_logic_vector (7 downto 0);------------------------------------------------------------------------ -- Module Implementation------------------------------------------------------------------------ begin--Divide the master clock down to a lower frequency--CLKDivider: Process (CLK)beginif (CLK = '1' and CLK'Event) thenclkDiv <= clkDiv +1;end if;end Process;sclk <= clkDiv(12);pclk <= clkDiv(3);--Flip Flops used to condition siglans coming from PS2--Process (pclk, RST, KC, KD)beginif(RST = '0') thenDFF1 <= '0'; DFF2 <= '0'; KDI <= '0'; KCI <= '0';elseif (pclk = '1' and pclk'Event) thenDFF1 <= KD; KDI <= DFF1; DFF2 <= KC; KCI <= DFF2;end if;end if;end process;--Shift Registers used to clock in scan codes from PS2--Process(KDI, KCI, RST) --DFF2 carries KD and DFF4, and DFF4 carries KCbeginif (RST = '0') thenShiftRegSig1 <= "00000000000";ShiftRegSig2 <= "0000000000";elseif (KCI = '0' and KCI'Event) thenShiftRegSig1(10 downto 0) <= KDI & ShiftRegSig1(10 downto 1);ShiftRegSig2(10 downto 1) <= ShiftRegSig1(0) & ShiftRegSig2(10 downto 2);end if;end if;end process;--Wait Registerprocess(ShiftRegSig1, ShiftRegSig2, RST, KCI)beginif(RST = '0')thenWaitReg <= "00000000";elseif(KCI'event and KCI = '1' and ShiftRegSig2(8 downto 1) = "11110000")then WaitReg <= ShiftRegSig1(8 downto 1);end if;end if;end Process;--MultiplexerMUXOUT <= WaitReg(7 downto 4) when sclk = '1' elseWaitReg(3 downto 0);--Seven Segment Decoder--sseg <= "1000000" when MUXOUT = "0000" else"1111001" when MUXOUT = "0001" else"0100100" when MUXOUT = "0010" else"0110000" when MUXOUT = "0011" else"0011001" when MUXOUT = "0100" else"0010010" when MUXOUT = "0101" else"0000010" when MUXOUT = "0110" else"1111000" when MUXOUT = "0111" else"0000000" when MUXOUT = "1000" else"0010000" when MUXOUT = "1001" else"0001000" when MUXOUT = "1010" else"0000011" when MUXOUT = "1011" else"1000110" when MUXOUT = "1100" else"0100001" when MUXOUT = "1101" else"0000110" when MUXOUT = "1110" else"0001110" when MUXOUT = "1111" else"1111111";--Anode Driver--an(3) <= '1'; an(2) <= '1'; --disable first two seven-segment decoders.an(1 downto 0) <= "10" when sclk = '1' else "01";end Behavioral;。

基于verilog的PS2键盘设计进阶

实验九、基于verilog的PS/2键盘设计进阶一、前言及背景:说到PS/2相信大家都不会陌生,不错的,我们日常的鼠标键盘大多是基于P S/2接口设计的。

虽然USB鼠标大有取而代之之势,但是依然阻止不了我们这群IT菜鸟掌握它的强烈欲望,而使用verilog来做PS/2的解码更是需要我们把P S/2的传输协议理解的更透彻一些。

所以,下面就让特权同学带领大家一步一步掌握PS/2。

PS/2接口标准的发展过程随着计算机工业的发展,作为计算机最常用输入设备的键盘也日新月异。

19 81年IBM推出了IBM pc/XT键盘及其接口标准。

该标准定义了83键,采用5脚DIN连接器和简单的串行协议。

实际上,第一套键盘扫描码集并没有主机到键盘的命令。

为此,1984年IBM推出了IBM AT键盘接口标准。

该标准定义了84~10 1键,采用5脚DIN连接器和双向串行通讯协议,此协议依照第二套键盘扫描码集设有8个主机到键盘的命令。

到了1987年,IBM又推出了PS/2键盘接口标准。

该标准仍旧定义了84~101键,但是采用6脚mini-DIN连接器,该连接器在封装上更小巧,仍然用双向串行通讯协议并且提供有可选择的第三套键盘扫描码集,同时支持17个主机到键盘的命令。

现在,市面上的键盘都和PS/2及AT键盘兼容,只是功能不同而已。

表中,如果数据位中1的个数为偶数,校验位就为1;如果数据位中1的个数为奇数,校验位就为0;总之,数据位中1的个数加上校验位中1的个数总为奇数,因此总进行奇校验。

(是不是发现它的数据传输协议和串口很像呢!呵呵)PS/2 发送数据到PC的时序键盘接口时序:(a) 键盘发送时序(b) 键盘接收时序注:在时钟的下降沿读取数据。

以下可做具体写代码设计参考:从PS/2向PC机发送一个字节可按照下面的步骤进行:(1)检测时钟线电平,如果时钟线为低,则延时50us;(2)检测判断时钟信号是否为高,为高,则向下执行,为低,则转到(1);(3)检测数据线是否为高,如果为高则继续执行,如果为低,则放弃发送(此时PC机在向PS/2设备发送数据,所以PS/2设备要转移到接收程序处接收数据);(4)延时20us(如果此时正在发送起始位,则应延时40us);(5)输出起始位(0)到数据线上。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

VHDL课程设计-PS2键盘目录一、课程设计的目的与任务 (3)二、课程设计题目 (3)1、指定题目: (3)2、自选题目: (3)三、课程设计的内容与要求 (3)1、设计内容 (4)2、设计要求 (4)四、实验仪器设备 (4)五、设计方案 (4)1、PS2解码 (4)2、设计思路 (6)3、模块设计 (7)4、各模块分析 (8)(1)PS2时钟检测模块8(2)PS2解码模块10(3)PS2组合模块12(4)控制LED模块14(5)PS2总的组合模块16六、综合与仿真 (17)1、综合 (17)2、仿真 (18)(1)电平检测模块仿真 (18)(2)LED灯控制模块仿真 (18)(3)PS2_module总模块仿真 (19)七、硬件下载 (23)八、心得体会 (24)九、参考文献 (24)一、课程设计的目的与任务(1)熟练掌握EDA工具软件QuartusII的使用;(2)熟练用VHDL硬件描述语言描述数字电路;(3)学会使用VHDL进行大规模集成电路设计;(4)学会用CPLD\FPGA使用系统硬件验证电路设计的正确性;(5)初步掌握EDA技术并具备一定的可编程逻辑芯片的开发能力;二、课程设计题目1、指定题目:0 :多功能计数器;1 :数字秒表;2 :简易数字钟;3 :简易频率计;4 :彩灯控制器;5 :交通灯控制器;6 :四路智力竞赛抢答器;7 :简易微波炉控制器;8 :表决器;9 :数字密码锁;我的的学号尾数是2,所以我要做的题目是简易数字钟。

由于我之前已经学过Verilog HDL和VHDL,所以简易数字钟相对于我比较简单,我完成了简易数字钟并验收后,再选择了另一个自选题目来完成。

简易数字钟:设计一个以“秒”为基准信号的简易数字钟,显示时、分、秒,同时可实现整点报时和清零(我已经完成,而且已经验收了)。

2、自选题目:在完成了数字钟的设计后,我选择了另一个设计的题目,那就是PS2键盘扫描。

所以这次课程设计我的报告主要详细写的是PS2键盘扫描的程序,而不是简易数字钟。

PS键盘扫描:设计一个PS键盘扫描程序,能接受键盘的输入时钟和数据,区别哪一个键输入,同时解译通码和断码,使用LED灯来显示收到的数据。

三、课程设计的内容与要求1、设计内容(1)系统功能的分析;(2)实现系统功能的实际方案;(3)编写各功能模块的VHDL语言程序;(4)对各功能模块进行编译、综合、仿真、分析;(5)顶层文件设计(6)对整个系统进行编译、综合、仿真、分析;(7)在CPLD\FPGA实验开发系统试验箱上进行硬件验证;(8)写实验报告;2、设计要求(1)按所布置的题目要求,每一位学生独立完成全过程;(2)分模块层次化设计;(3)各功能模块的底层文件必须用VHDL语言设计,顶层文件可用VHDL语言设计,也可以用原理图设计。

四、实验仪器设备(1)PC机;(2)QuartusII软件;(3)黑金FPGA实验开发系统,芯片为Cyclone II的EP2C5Q208C8;五、设计方案1、PS2解码图1为PS2的接口图。

我使用的的右边的PS2接口,即1脚为数据脚,5脚为时钟脚,同时我编写的VHDL代码只对1脚和5脚操作。

图2 PS2协议时序图图2为PS2协议时序图。

由图可以解读出,PS2协议对数据的读取时“CLK 的下降沿”有效,而数据的放置时在“CLK的上升沿”。

PS2频率比较慢,大概为10KHz。

第N位属性0 开始位1~8 数据位9 校验位10 结束位表1 PS2数据说明PS2的一帧数据时11位。

对PS2进行解码,我们需要得到的是1~8位的数据位。

其他的位,可以使用取巧的方法编写。

键盘的编码有“通码(Make)”和“断码(Break)”之分。

通码相当于某个按键按下了,断码相当于某个按键释放了。

假设,我们按下了“Z”键不放,大约每秒有10个X“1A”的通码(10KHz),而当我们释放“Z”键,就会输出断码X“F0”和X“1A”。

同时,键盘编码一次只能有一个输出,即多个按键同时按下时,只有一个有效。

下表为第二套PC键盘扫描码。

键名通码断码-键名通码断码-键名通码断码A1C F0,1C946F0,46[54FO,54 B32F0,32`0E F0,0E INSERT E0,70E0,F0,70 C21F0,21-4E F0,4E HOME E0,6C E0,F0,6C D23F0,23=55FO,55PG UP E0,7D E0,F0,7D E24F0,24\5D F0,5D DELETE E0,71E0,F0,71 F2B F0,2B BKSP66F0,66END E0,69E0,F0,69表2 PC键盘第二套扫描码2、设计思路(1)PS2时钟的检测;(2)PS2数据的接受并提取需要的8位数据; (3)对PS2提取的8位数据进行解码,确定按键; (4)通过LED 灯显示按键的解码的结果; (5)设置多个按键,多种LED 显示方式;对于PS2键盘扫描程序,我的设计思路是一个模块一个功能,这样能清晰分辨模块,同时易于修改代码。

代码条理清晰,便于解读。

而对于多个模块则使用层次化的形式来编写,顶层文件并不包含功能的设定,只包含各个子功能模块。

3、模块设计PS2键盘扫描分为:电平检测,PS2解码,PS2组合,LED 控制和总PS 组合六个模块。

下面为各个模块的简易模块图。

(1)PS2时钟检测模块:图3 电平检测模块图(2)PS2解码模块:图4 PS2解码模块图(3)PS2组合模块:图5 PS2组合模块图(4)控制LED 模块:PS2解码模块PS2_Data PS2_Da H_L_SPS2_DoPS2_CLK_H_L_Sig电平检测模块PS2解码模块PS2_DataPS2_DaPS2_Done_SigPS2_CLK_Pin_InH_L电平检测模块图6 LED 控制模块图(5)PS2总的组合模块:图7 PS2模块图4、各模块分析(1) PS2时钟检测模块PS2电平检测模块主要的作用是检测PS2接口键盘的时钟信号,因为PS2的协议规定数据是在时钟的下降沿读取的。

所以电平检测模块要检测PS2时钟的下降沿,有下降沿来临时,要做相应的数据读取动作。

下面是代码的分析。

LIBRARY IEEE;--库USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL;------------------------------------------------------------------------------------------------------------------------------------------ ENTITY PS2_detect_module IS--实体声明PORT( CLK,RSTn : IN STD_LOGIC; PS2_CLK_Pin_In : IN STD_LOGIC; H_L_Sig : OUT STD_LOGIC; --电平由高变低,输出一个信号 L_H_Sig : OUT STD_LOGIC--电平由低变高,输出一个信号);END ENTITY PS2_detect_module;------------------------------------------------------------------------------------------------------------------------------------------ ARCHITECTURE PS2_detect OF PS2_detect_module IS --结构体声明SIGNAL H_L_F1 : STD_LOGIC :='1';--声明4个信号,用于电平输入的变PS2_Done_SigPS2PS2_Data_Pin_InPS2_CLK_Pin_In Data电平检测模块 电平检测模块 PS2_Data Data_O 电平检测模块PS2_Done化SIGNAL H_L_F2 : STD_LOGIC :='1'; --4个信号都赋了初值SIGNAL L_H_F1 : STD_LOGIC :='0';SIGNAL L_H_F2 : STD_LOGIC :='0';BEGINPROCESS(CLK,RSTn)BEGINIF (CLK'event AND CLK='1') THEN --同步进行IF (RSTn='0') THEN --同步复位动作H_L_F1 <= '1';H_L_F2 <= '1';L_H_F1 <= '0';L_H_F2 <= '0';ELSEH_L_F1 <= PS2_CLK_Pin_In;H_L_F2 <= H_L_F1;L_H_F1 <= PS2_CLK_Pin_In;L_H_F2 <= L_H_F1;END IF;END IF;END PROCESS;H_L_Sig <= H_L_F2 AND (NOT H_L_F1); --输出信号L_H_Sig <= L_H_F1 AND (NOT L_H_F2);END ARCHITECTURE PS2_detect; --结构体结束在结构体中声明了4个信号,用于电平的检测F2信号是接着F1信号的,如果F1信号变化了,F2信号还不会立即变化,F2还会保持F1的前一个状态,以两者的逻辑关系,可以判断输入的是上升沿还是下降沿。

结果如表格3。

表3 电平检测变化表(2)PS2解码模块LIBRARY IEEE; --库USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;------------------------------------------------------------------------------------------------------------------------------------------ ENTITY PS2_decode_module IS --实体声明PORT(CLK,RSTn : IN STD_LOGIC;H_L_Sig : IN STD_LOGIC;PS2_Data_Pin_In : IN STD_LOGIC;PS2_Done_Sig : OUT STD_LOGIC;PS2_Data : OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END ENTITY PS2_decode_module;------------------------------------------------------------------------------------------------------------------------------------------ ARCHITECTURE PS2_decode OF PS2_decode_module ISSIGNAL Done : STD_LOGIC :='0'; --声明一个完成信号SIGNAL i : STD_LOGIC_VECTOR(4 DOWNTO 0) :="00001"; --声明步骤iSIGNAL Data : STD_LOGIC_VECTOR(7 DOWNTO 0) :=X"32";BEGINPROCESS(CLK,RSTn,i)BEGINIF (CLK'event AND CLK='1') THENIF (RSTn='0') THENi <= "00001";Done <= '0';Data <= X"00";ELSECASE i ISWHEN "00000" => i <= "00001";WHEN "00001" => IF (H_L_Sig='1') THEN i <= "00010";Data(0) <= PS2_Data_Pin_In;END IF;WHEN "00010" => IF (H_L_Sig='1') THEN i <= "00011";Data(1) <= PS2_Data_Pin_In;END IF;WHEN "00011" => IF (H_L_Sig='1') THEN i <= "00100";Data(2) <= PS2_Data_Pin_In;END IF;WHEN "00100" => IF (H_L_Sig='1') THEN i <= "00101";Data(3) <= PS2_Data_Pin_In;END IF;WHEN "00101" => IF (H_L_Sig='1') THEN i <= "00110";Data(4) <= PS2_Data_Pin_In;END IF;WHEN "00110" => IF (H_L_Sig='1') THEN i <= "00111";Data(5) <= PS2_Data_Pin_In;END IF;WHEN "00111" => IF (H_L_Sig='1') THEN i <= "01000";Data(6) <= PS2_Data_Pin_In;END IF;WHEN "01000" => IF (H_L_Sig='1') THEN i <= "01001";Data(7) <= PS2_Data_Pin_In;END IF;WHEN "01001" => IF (H_L_Sig='1') THEN i <= "01010";END IF;WHEN "01010" => IF (H_L_Sig='1') THEN i <= "01011";END IF;WHEN "01011" => IF (Data=X"F0") THEN i <= "01100";ELSE i <= "10110";END IF;WHEN "01100" => IF (H_L_Sig='1') THEN i <= "01101";END IF;WHEN "01101" => IF (H_L_Sig='1') THEN i <= "01110";END IF;WHEN "01110" => IF (H_L_Sig='1') THEN i <= "01111";END IF;WHEN "01111" => IF (H_L_Sig='1') THEN i <= "10000";END IF;WHEN "10000" => IF (H_L_Sig='1') THEN i <= "10001";END IF;WHEN "10001" => IF (H_L_Sig='1') THEN i <= "10010";END IF;WHEN "10010" => IF (H_L_Sig='1') THEN i <= "10011";END IF;WHEN "10011" => IF (H_L_Sig='1') THEN i <= "10100";END IF;WHEN "10100" => IF (H_L_Sig='1') THEN i <= "10101";END IF;WHEN "10101" => IF (H_L_Sig='1') THEN i <= "10110";END IF;WHEN "10110" => IF (H_L_Sig='1') THEN i <= "10111";Done <= '1';END IF;WHEN "10111" => IF (H_L_Sig='1') THEN i <= "00001";Done <= '0';END IF;WHEN OTHERS => i <= "00001";END CASE;END IF;END IF;END PROCESS;PS2_Data <= Data;PS2_Done_Sig <= Done;END ARCHITECTURE PS2_decode;这个模块我有点偷懒,只对键盘输入的8位有效数据进行了提取,其他位基本是忽略了,第一位开始位忽略了,然后是读取8位有效数据,第9步和第10步跳过了检测位和结束位,然后是判断。