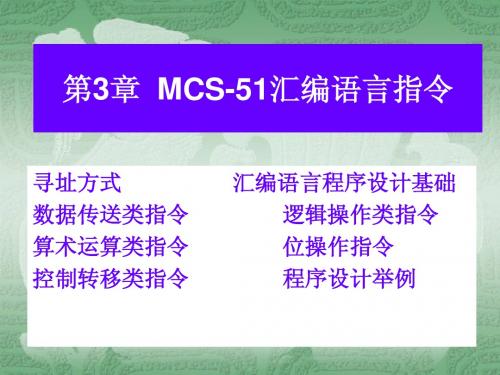

MCS-51汇编语言指令集

51单片机汇编语言指令集

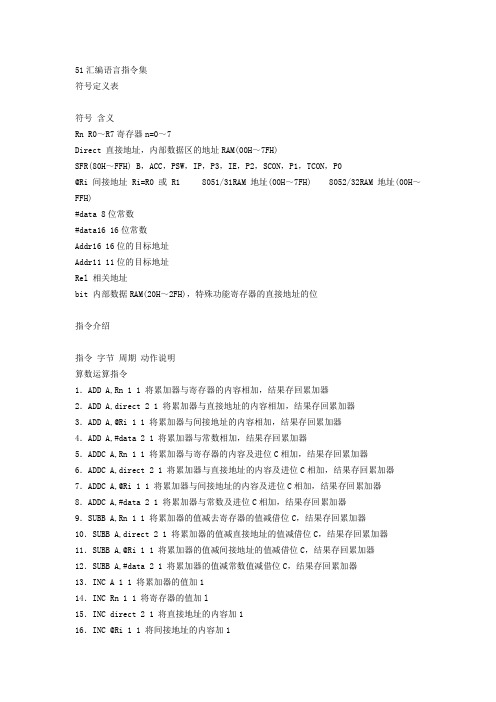

51汇编语言指令集符号定义表符号含义Rn R0~R7寄存器n=0~7Direct 直接地址,内部数据区的地址RAM(00H~7FH)SFR(80H~FFH) B,ACC,PSW,IP,P3,IE,P2,SCON,P1,TCON,P0@Ri 间接地址Ri=R0或R1 8051/31RAM地址(00H~7FH) 8052/32RAM地址(00H~FFH) #data 8位常数#data16 16位常数Addr16 16位的目标地址Addr11 11位的目标地址Rel 相关地址bit 内部数据RAM(20H~2FH),特殊功能寄存器的直接地址的位指令介绍指令字节周期动作说明算数运算指令1.ADD A,Rn 1 1 将累加器与寄存器的内容相加,结果存回累加器2.ADD A,direct 2 1 将累加器与直接地址的内容相加,结果存回累加器3.ADD A,@Ri 1 1 将累加器与间接地址的内容相加,结果存回累加器4.ADD A,#data 2 1 将累加器与常数相加,结果存回累加器5.ADDC A,Rn 1 1 将累加器与寄存器的内容及进位C相加,结果存回累加器6.ADDC A,direct 2 1 将累加器与直接地址的内容及进位C相加,结果存回累加器7.ADDC A,@Ri 1 1 将累加器与间接地址的内容及进位C相加,结果存回累加器8.ADDC A,#data 2 1 将累加器与常数及进位C相加,结果存回累加器9.SUBB A,Rn 1 1 将累加器的值减去寄存器的值减借位C,结果存回累加器10.SUBB A,direct 2 1 将累加器的值减直接地址的值减借位C,结果存回累加器11.SUBB A,@Ri 1 1 将累加器的值减间接地址的值减借位C,结果存回累加器12.SUBB A,#data 2 1 将累加器的值减常数值减借位C,结果存回累加器13.INC A 1 1 将累加器的值加114.INC Rn 1 1 将寄存器的值加l15.INC direct 2 1 将直接地址的内容加116.INC @Ri 1 1 将间接地址的内容加117.INC DPTR 1 1 数据指针寄存器值加1说明:将16位的DPTR加1,当DPTR的低字节(DPL)从FFH溢出至00H时,会使高字节(DPH)加1,不影响任何标志位18.DEC A 1 1 将累加器的值减119.DEC Rn 1 1 将寄存器的值减120.DEC direct 2 1 将直接地址的内容减121.DEC @Ri 1 1 将间接地址的内容减122.MUL AB 1 4 将累加器的值与B寄存器的值相乘,乘积的低位字节存回累加器,高位字节存回B寄存器说明:将累加器A和寄存器B内的无符号整数相乘,产生16位的积,低位字节存入A,高位字节存入B寄存器。

MCS51单片机指令系统

第一条指令为远查表指令,可以在64K的程序存储器空间寻 址。基地址寄存器为DPTR,其意思为,DPTR里面存放的是 程序存储器中数据表格的首地址,A为数据地址的偏移量。

这条指令执行以后,以 (A)+(DPTR)的数值为地址数 据就送进A里面来了,也就是从表格首地址开始以后的第(A) 个数据被送进A了。(举例子说明)

编写好的程序都放在程序存储器中,由于一个存储地址所 指示的存储单元只能存放一字节的数据。所以,在存放指令时, 必须将指令拆分成一个一个字节进行连续存放。

比如: 实现“累加器加10H”这条指令,其机器语言为 0111010000010000, 占用了两个字节,就必须拆成两个字节 进行连续存储。

但是,用二进制来表示比较麻烦,因此,也常用十六进制来 表示如:74H 10H来表示以上这条机器语言。可见,用十六进 制表示指令比较简单,但是,指令系统有上百条指令,不易记 住。所以,一般采用容易记住的一些缩写符号来表示机器语言,

2. 在指令中直接给出操作数的地址, 这种寻址方式就属

于直接寻址方式。在这种方式中, 指令的操作数部分直接 是操作数的地址。

比如:MOV A,30H;将30H里面的数送到A里面 MOV 21H,30H;将30H里面的数存放到21H里面 在MCS -51 单片机指令系统中, 直接寻址方式中可

以访问 3 种存储器空间: (1) 内部数据存储器的低 128 个字节单元(00H~

7. 位寻址 指按照位进行的寻址操作,(前面讲的都是按字节进

行的寻址操作)。该种寻址方式中, 操作数是内部RAM单元 中20H到2FH的128个位地址以及SFR中的11个可进行 位寻址的寄存器中的位地址寻址。

比如:MOV C,20H;就是将RAM中位寻址区中20H位地 址中的内容送给C。区别与MOV A,20H;这个是将内部 RAM中20H单元的内容送给A。

MCS-51汇编语言指令集

(A)→(Rn),n=0~7 Rn) direct) Rn) (direct)→(Rn),n=0~7 data→(Rn) data→(Rn),n=0~7 (A)→(direct) Rn) direct) (Rn)→(direct),n=0~7 (direct2)→(direct1) [(Ri)]→(direct),i=0,1 data→(direct) (A)→[(Ri)],i=0,1 (direct)→[(Ri)],i=0,1 data→[(Ri)],i=0,1

54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 7ห้องสมุดไป่ตู้ 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89

MOV Rn,A MOV Rn,direct MOV Rn,#data MOV direct,A MOV direct,Rn MOV direct1,direct2 MOV direct,@Ri MOV direct,#data MOV @Ri,A MOV @Ri,direct MOV @Ri,#data MOV DPTR,#data16 MOVC A,@A+DPTR MOVC A,@A+PC MOVX A,@Ri MOVX A,@DPTR MOVX @Ri,A MOVX @DPTR,A PUSH direct POP direct XCH A,Rn XCH A,direct XCH A,@Ri XCHD A,@Ri CLR C CLR bit SETB C SETB bit CPL C CPL bit ANL C,bit ANL C,/bit ORL C,bit ORL C,/bit MOV C,bit MOV bit,C

MCS51汇编指令

2

1

ADD A,direct

A)+(direct)→(A)累加器A中的数据与直接地址单元中的数据相加,结果存在A中

2

1

指令格式(助记符)

指令功能说明

字节

周期

ADD A,Rn

(A)+(Rn)→(A)累加器A中的数据与工作寄存器Rn中的数据相加,结果存在A中

如A的内容与直接地址内的数据不同,则短跳转

3

2

CJNE A,#data,rel

如A的内容与立即数不同,则短跳转

3

2

CJNE Rn,#data,rel

如Rn寄存器中的数据与立即数不同,则短跳转

3

2

CJNE @Ri,#data,rel

如间接地址的数据与立即数不同,则短跳转

3

2

DJNZ Rn,rel

Rn寄存器中的数据减1,若不为0,则短跳转,否则执行下条指令

3

2

MOV direct,#data

#data→(direct)立即数→直接地址单元direct

3

2

MOV direct,A

(A)→(direct)累加器A中的数据→直接地址单元direct

2

2

MOV direct,Rn

(Rn)→(direct)寄存器Rn中的数据→直接地址单元direct

2

2

MOV direct,@Ri

当进bit=1跳至rel,并且清除此bit为0,否则执行下一条指令

3

3

ACALL addr11

2K范围内子程序调用

2

2

LCALL addr16

大学课件MCS51单片机指令系统与汇编语言程序设计

ANL C, P ; (C)← (C)∧(P)

其中:P是PSW的第0位,C是PSW的第7位。

(4)字节符号地址(字节名称)加位序号的形式。对于部分特 殊功能寄存器(如状态标志寄存器PSW),还可以用其字节名 称加位序号形式来访问某一位。AC 如:

定义:操作数存放在MCS-51内部的某个工作寄存器Rn (R0~R7)或部分专用寄存器中,这种寻址方式称为 寄存器寻址。

特点:由指令指出某一个寄存器的内容作为操作数。 存放操作数的寄存器在指令代码中不占据单独的一个 字节,而是嵌入(隐含)到操作码字节中。

寻址范围:四组通用寄存器Rn(R0~R7)、部分专用 寄存器( A, B, DPTR, Cy )。

伪指令只出现在汇编前的源程序中,仅提供汇编用的某些控制 信息,不产生可执行的目标代码,是CPU不能执行的指令。

(1)定位伪指令ORG

格式:ORG n

其中:n通常为绝对地址,可以是十六进制数、标号或表达式。

功能:规定编译后的机器代码存放的起始位置。在一个汇编 语言源程序中允许存在多条定位伪指令,但每一个n值都应和前

2.2.2 直接寻址

定义:将操作数的地址直接存放在指令中,这种寻址方式称为 直接寻址。 特点:指令中含有操作数的地址。该地址指出了参与操作的数 据所在的字节单元地址或位地址。计算机执行它们时便可根据 直接地址找到所需要的操作数。

寻址范围:ROM、片内RAM区、SFR和位地址空间。P42

2.2.3 寄存器寻址

定义:指令中给出的操作数是一个可单独寻址的位地址,这种寻址 方式称为位寻址方式。

特点:位寻址是直接寻址方式的一种,其特点是对8位二进制数中 的某一位的地址进行操作。

寻址范围:片内RAM低128B中位寻址区、部分SFR(其中有83位 可以位寻址)。

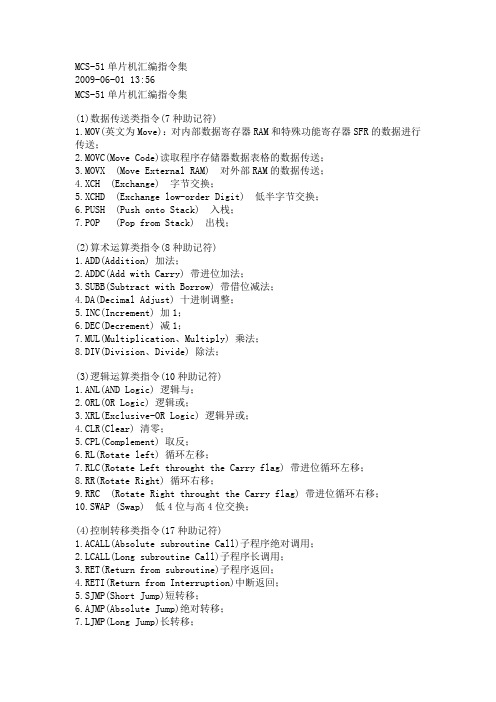

MCS-51单片机汇编指令集

MCS-51单片机汇编指令集2009-06-01 13:56MCS-51单片机汇编指令集(1)数据传送类指令(7种助记符)1.MOV(英文为Move):对内部数据寄存器RAM和特殊功能寄存器SFR的数据进行传送;2.MOVC(Move Code)读取程序存储器数据表格的数据传送;3.MOVX (Move External RAM) 对外部RAM的数据传送;4.XCH (Exchange) 字节交换;5.XCHD (Exchange low-order Digit) 低半字节交换;6.PUSH (Push onto Stack) 入栈;7.POP (Pop from Stack) 出栈;(2)算术运算类指令(8种助记符)1.ADD(Addition) 加法;2.ADDC(Add with Carry) 带进位加法;3.SUBB(Subtract with Borrow) 带借位减法;4.DA(Decimal Adjust) 十进制调整;5.INC(Increment) 加1;6.DEC(Decrement) 减1;7.MUL(Multiplication、Multiply) 乘法;8.DIV(Division、Divide) 除法;(3)逻辑运算类指令(10种助记符)1.ANL(AND Logic) 逻辑与;2.ORL(OR Logic) 逻辑或;3.XRL(Exclusive-OR Logic) 逻辑异或;4.CLR(Clear) 清零;5.CPL(Complement) 取反;6.RL(Rotate left) 循环左移;7.RLC(Rotate Left throught the Carry flag) 带进位循环左移;8.RR(Rotate Right) 循环右移;9.RRC (Rotate Right throught the Carry flag) 带进位循环右移;10.SWAP (Swap) 低4位与高4位交换;(4)控制转移类指令(17种助记符)1.ACALL(Absolute subroutine Call)子程序绝对调用;2.LCALL(Long subroutine Call)子程序长调用;3.RET(Return from subroutine)子程序返回;4.RETI(Return from Interruption)中断返回;5.SJMP(Short Jump)短转移;6.AJMP(Absolute Jump)绝对转移;7.LJMP(Long Jump)长转移;8C.JNE (Compare Jump if Not Equal)比较不相等则转移;9D.JNZ (Decrement Jump if Not Zero)减1后不为0则转移;10.JZ (Jump if Zero)结果为0则转移;11.JNZ (Jump if Not Zero) 结果不为0则转移;12.JC (Jump if the Carry flag is set)有进位则转移;13.JNC (Jump if Not Carry)无进位则转移;14.JB (Jump if the Bit is set)位为1则转移;15.JNB (Jump if the Bit is Not set) 位为0则转移;16.JBC(Jump if the Bit is set and Clear the bit) 位为1则转移,并清除该位;17.NOP (No Operation) 空操作;(5)位操作指令(1种助记符)1.SETB(Set Bit) 位置1。

MCS-51单片机汇编指令详解

MCS-51单片机汇编指令详解以累加器为目的操作数的指令MOV A,RnMOV A,directMOV A,@RiMOV A,#data第一条指令中,Rn代表的是R0-R7。

第二条指令中,direct就是指的直接地址,而第三条指令中,就是我们刚才讲过的。

第四条指令是将立即数data送到A中。

下面我们通过一些例子加以说明:MOV A,R1 ;将工作寄存器R1中的值送入A,R1中的值保持不变。

MOV A,30H ;将内存30H单元中的值送入A,30H单元中的值保持不变。

MOV A,@R1 ;先看R1中是什么值,把这个值作为地址,并将这个地址单元中的值送入A中。

如执行命令前R1中的值为20H,则是将20H单元中的值送入A中。

MOV A,#34H ;将立即数34H送入A中,执行完本条指令后,A中的值是3 4H。

以寄存器Rn为目的操作的指令MOV Rn,AMOV Rn,directMOV Rn,#data这组指令功能是把源地址单元中的内容送入工作寄存器,源操作数不变。

以直接地址为目的操作数的指令MOV direct,A 例: MOV 20H,AMOV direct,Rn MOV 20H,R1MOV direct1,direct2 MOV 20H,30HMOV direct,@Ri MOV 20H,@R1MOV direct,#data MOV 20H,#34H以间接地址为目的操作数的指令MOV @Ri,A 例:MOV @R0,AMOV @Ri,direct MOV @R1,20HMOV @Ri,#data MOV @R0,#34H十六位数的传递指令MOV DPTR,#data168051是一种8位机,这是唯一的一条16位立即数传递指令,其功能是将一个16位的立即数送入DPTR中去。

其中高8位送入 DPH(083H),低8位送入DPL(082H)。

例:MOV DPTR,#1234H,则执行完了之后DPH中的值为12H,DPL中的值为34H。

51单片机汇编语言7-指令系统-2

图3.8 数据传送指令分类

第3章

MCS-51指令系统

1. 内部 位数据传送指令 条) 内部8位数据传送指令 位数据传送指令(15条 内部8位数据传送指令共15条,主要用于MCS-51单片机内

部RAM与寄存器之间的数据传送。指令基本格式: MOV <目的操作数>,<源操作数> 1) 以累加器A为目的地址的传送指令(4条)

注意:以上传送指令的结果不影响程序状态字寄存器PSW标 志。

第3章

MCS-51指令系统

4) 以寄存器间接地址为目的地址的传送指令(3条)

助记符格式 MOV @Ri,A MOV @Ri,direct MOV @Ri,#data 机器码(B) 1111011i 1110011i direct 0111010i data 相应操作 (Ri)←A (Ri)←(direct) (Ri)←#data 指令说明 i=0,1 机器周期 1 2 1

2

第3章

MCS-51指令系统

注意:① 堆栈是用户自己设定的内部RAM中的一块专用存 储区,使用时一定先设堆栈指针,堆栈指针缺省为SP=07H。 ② 堆栈遵循后进先出的原则安排数据。 ③ 堆栈操作必须是字节操作,且只能直接寻址。将累加器 A入栈、出栈指令可以写成: PUSH/POP ACC 或 PUSH/POP 0E0H 而不能写成: PUSH/POP A ④ 堆栈通常用于临时保护数据及子程序调用时保护现场和 恢复现场。 ⑤ 以上指令结果不影响程序状态字寄存器PSW标志。

第3章

MCS-51指令系统

寄存器R0 寄存器R1 寄存器R6 内部 RAM 50 RAM:50H 内部 RAM:66H 内部 RAM:70H 50H 66H 30H 60H 60 45H 40H

MCS-51单片机的汇编语言

绝对地址段选择伪指令

CSEG

[AT

address]

DSEG

[AT

address]

ISEG

[AT

address]

BSEG

[AT

address]

XSEG

[AT

address]

分别为程序存储器、内部数据存储器、间接寻址的内部数据存 储器、位寻址区和外部数据存储器的使用指定绝对地址

1.5 通用的转移和调用语句

MCS-51汇编器允许程序员使用通用的转移和调用助记符JMP 与CALL

用来代替SJMP、AJMP、LJMP和ACALL、LCALL

汇编产生的未必是最优化的结果

1.6 条件汇编

将一个软件的多个版本保存在同一组源程序文件中 使用IF、ELSEIF、ELSE、ENDIF IF或ELSEIF后的表达式通常为关系表达式 当IF或ELSEIF后的数值表达式的值非零时,汇编其后的语句组;

1.4 伪指令语句

ORG伪指令

ORG

பைடு நூலகம்

expression

设置汇编计数器的值,指定其后语句的起始地址

伪指令语句

END伪指令

应当是源程序的最后一条语句 通知汇编程序汇编过程应在此结束 汇编器不理会END后面的文件内容

每个程序文件都应以END结束

伪指令语句

EQU和SET伪指令

symbol

单片机原理与应用

MCS-51单片机的汇编语言

INTS SET

IF ELSE ENDIF

INTS = 1 MAIN_START

MAIN_START

NUM1 DATA NUM2 DATA

DSEG AT

STACK: DS

20H

MCS51单片机指令系统与汇编语言程序设计

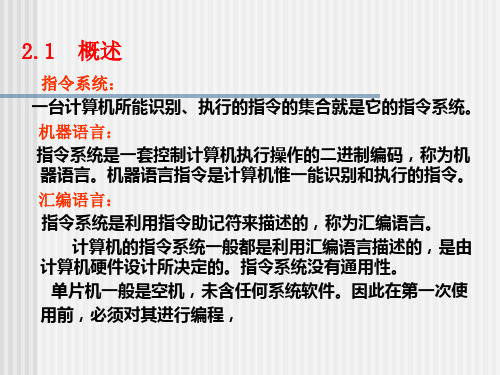

MCS51单片机指令系统与汇编语言程序设计MCS-51是一种非常常见的8位单片机系列,该系列包括了多种型号的单片机,如Intel 8051、8031、8052等。

MCS-51单片机指令系统是一组用于驱动该系列单片机的指令集,汇编语言程序设计是利用这些指令来编写程序。

MCS-51单片机指令系统包含了多种指令,可以执行诸如数据传输、算术逻辑运算、控制和数据访问等功能。

这些指令通过各种不同的寻址模式来操作数据,包括立即寻址、寄存器寻址、直接寻址、间接寻址和寄存器间接寻址等。

不同的寻址模式和指令组合可以实现不同的功能。

汇编语言程序设计通过将人类可读的汇编指令翻译成机器可执行的二进制指令来编写程序。

在MCS-51单片机中,汇编指令由操作码和操作数组成。

操作码指定了所执行的操作,如数据传输、算术运算或控制指令。

操作数则指定了指令要操作的数据。

下面以一个简单的例子来说明MCS-51单片机指令系统和汇编语言程序设计的基本原理。

假设我们要编写一个程序,将两个寄存器中的数据相加,并将结果存储到第三个寄存器中。

首先,我们需要将第一个寄存器的值加载到累加器A中,这可以通过MOV指令实现。

MOV指令的操作码为01,操作数为两个寄存器的地址。

例如,MOVA,R0将R0的值加载到A中。

接下来,我们需要将第二个寄存器的值加载到B寄存器中,同样可以使用MOV指令。

MOVB,R1将R1的值加载到B中。

然后,我们可以使用ADD指令将A和B中的值相加,并将结果存储到A中。

ADD指令的操作码为04,操作数为A的地址。

例如,ADDA将累加器中的值与A寄存器中的值相加,并将结果存储到A中。

最后,我们可以使用MOV指令将A中的结果移动到第三个寄存器中,例如,MOVR2,A将A的值移动到R2中。

通过组合使用这些指令,我们可以实现将两个寄存器中的值相加并存储到第三个寄存器中的功能。

总结来说,MCS-51单片机指令系统和汇编语言程序设计是一种用于编程控制该系列单片机的方式。

MCS-51单片机的指令集(分类)

子程序返回

1

24

RETI

中断返回

1

24

AJMP addr11

绝对短转移

2

24

LJMP addr16

长转移

3

24

SJMP rel

相对转移

2

24

JMP @A+DPTR

相对于DPTR的间接转移

1

24

JZ rel

累加器为零转移

2

24

JNZ rel

累加器非零转移

2

24

CJNE A,direct,rel

累加器与直接地址单元比较,不等则转移

2

12

MOV direct,Rn

寄存器内容送入直接地址单元

2

24

MOV direct,direct

直接地址单元中的数据送入直接地址单元

3

24

MOV direct,@Ri

间接RAM中的数据送入直接地址单元

2

24

MOV direct,#data8

8位立即数送入直接地址单元

3

24

MOV @Ri,A

累加器内容送入间接RAM单元

DEC @Ri

间接RAM内容减1

1

12

MUL A,B

A乘以B

1

48

DIV A,B

A除以B

1

48

DA A

累加器进行十进制转换

1

12

3、逻辑操作类指令

助记符

功能说明

字节数

振荡周期

ANL A,Rn

累加器与寄存器相“与”

1

12

ANL A,direct

累加器与直接地址单元相“与”

51单片机汇编语言指令教程汇集

51单片机汇编语言指令教程汇集1.MOV指令:MOV指令用于将一个值从一个寄存器或内存位置复制到另一个寄存器或内存位置。

例如,MOVA,将常数10复制到累加器A中。

2.ADD指令:ADD指令用于将两个操作数相加,并将结果保存在目标操作数中。

例如,ADDA,B将寄存器B的值与累加器A的值相加,并将结果保存在累加器A中。

3.SUB指令:SUB指令用于将源操作数减去目标操作数,并将结果保存在目标操作数中。

例如,SUBA,B将寄存器B的值减去累加器A的值,并将结果保存在累加器A中。

4.INC指令:INC指令用于将指定的操作数加1、例如,INCA将累加器A的值加15.DEC指令:DEC指令用于将指定的操作数减1、例如,DECA将累加器A的值减16.JMP指令:JMP指令用于无条件地跳转到指定的地址。

例如,JMP1000h将跳转到地址1000h处执行指令。

9. ACALL指令:ACALL指令用于调用一个子程序,其地址由指令给出,子程序结束后返回到调用指令的下一条指令。

例如,ACALL Subroutine将调用一个名为Subroutine的子程序。

10.RET指令:RET指令用于从子程序返回到调用指令的下一条指令。

例如,RET将从子程序返回。

11.NOP指令:NOP指令用于空操作,即不执行任何操作。

它通常用于延时或填充空白。

以上是一些常用的51单片机汇编语言指令,这些指令可以用于控制I/O口、进行算术运算、执行跳转和调用子程序等。

学习并熟练掌握这些指令,对于编写高效的51单片机汇编程序非常重要。

希望本文提供的51单片机汇编语言指令教程能够帮助你入门和掌握51单片机汇编语言的基本知识。

如果你想深入学习51单片机汇编语言,建议参考相关的教材或在线资源,进行更加系统和全面的学习。

51单片机汇编指令表

以下是一些常见的51单片机(如8051系列)的汇编指令:

1. 数据传送指令:

- MOV:将一个数据或寄存器的值移动到另一个寄存器或存储器位置。

- MOVC:将数据从外部代码存储器复制到累加器或寄存器。

2. 算术运算指令:

- ADD:将累加器与另一个寄存器或存储器中的值相加。

- SUB:从累加器中减去另一个寄存器或存储器中的值。

- INC:将累加器或寄存器的值加1。

- DEC:将累加器或寄存器的值减1。

3. 逻辑运算指令:

- ANL:对累加器和另一个寄存器或存储器中的值进行逻辑与操作。

- ORL:对累加器和另一个寄存器或存储器中的值进行逻辑或操作。

- XRL:对累加器和另一个寄存器或存储器中的值进行逻辑异或操作。

- CPL:对累加器或寄存器中的值进行按位取反操作。

4. 条件分支指令:

- CJNE:比较两个值,并在不相等时跳转到指定的地址。

- DJNZ:递减累加器或寄存器,并在结果不为零时跳转到指定的地址。

5. 跳转指令:

- JMP:无条件跳转到指定的地址。

- SJMP:短跳转,跳转到相对于当前地址的指定偏移量。

- AJMP:绝对跳转,跳转到指定的地址。

- LCALL:长调用,将当前地址入栈并跳转到指定的子程序地址。

6. 位操作指令:

- SETB:将某个位设置为1。

- CLR:将某个位清零。

- JB:如果某个位为1,则跳转到指定地址。

- JNB:如果某个位为0,则跳转到指定地址。

mcs51单片机指令集

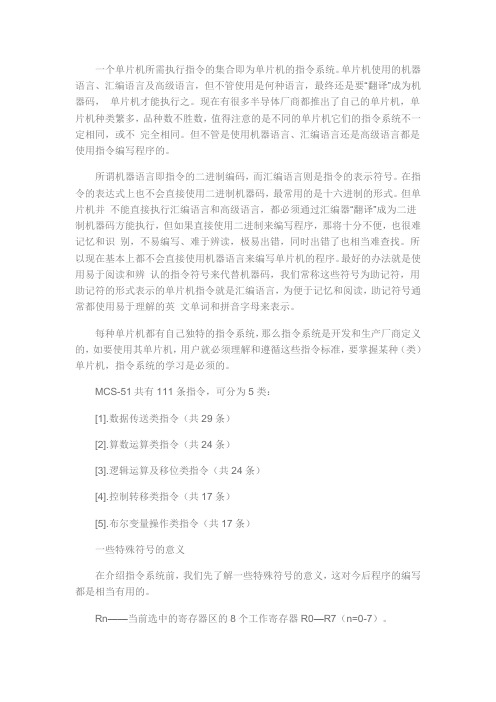

一个单片机所需执行指令的集合即为单片机的指令系统。

单片机使用的机器语言、汇编语言及高级语言,但不管使用是何种语言,最终还是要“翻译”成为机器码,单片机才能执行之。

现在有很多半导体厂商都推出了自己的单片机,单片机种类繁多,品种数不胜数,值得注意的是不同的单片机它们的指令系统不一定相同,或不完全相同。

但不管是使用机器语言、汇编语言还是高级语言都是使用指令编写程序的。

所谓机器语言即指令的二进制编码,而汇编语言则是指令的表示符号。

在指令的表达式上也不会直接使用二进制机器码,最常用的是十六进制的形式。

但单片机并不能直接执行汇编语言和高级语言,都必须通过汇编器“翻译”成为二进制机器码方能执行,但如果直接使用二进制来编写程序,那将十分不便,也很难记忆和识别,不易编写、难于辨读,极易出错,同时出错了也相当难查找。

所以现在基本上都不会直接使用机器语言来编写单片机的程序。

最好的办法就是使用易于阅读和辨认的指令符号来代替机器码,我们常称这些符号为助记符,用助记符的形式表示的单片机指令就是汇编语言,为便于记忆和阅读,助记符号通常都使用易于理解的英文单词和拼音字母来表示。

每种单片机都有自己独特的指令系统,那么指令系统是开发和生产厂商定义的,如要使用其单片机,用户就必须理解和遵循这些指令标准,要掌握某种(类)单片机,指令系统的学习是必须的。

MCS-51共有111条指令,可分为5类:[1].数据传送类指令(共29条)[2].算数运算类指令(共24条)[3].逻辑运算及移位类指令(共24条)[4].控制转移类指令(共17条)[5].布尔变量操作类指令(共17条)一些特殊符号的意义在介绍指令系统前,我们先了解一些特殊符号的意义,这对今后程序的编写都是相当有用的。

Rn——当前选中的寄存器区的8个工作寄存器R0—R7(n=0-7)。

Ri——当前选中的寄存器区中可作为地址寄存器的两个寄存器R0和R1(i=0,1)direct—内部数据存储单元的8位地址。

51单片机汇编指令详解

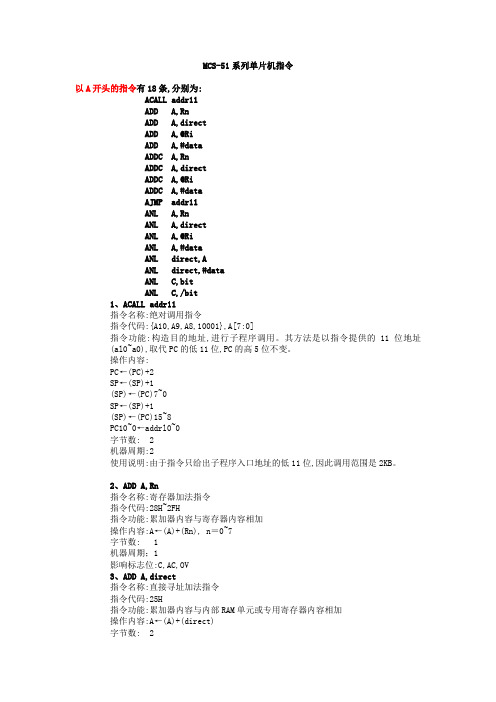

MCS-51系列单片机指令以A开头的指令有18条,分别为:ACALL addr11ADD A,RnADD A,directADD A,@RiADD A,#dataADDC A,RnADDC A,directADDC A,@RiADDC A,#dataAJMP addr11ANL A,RnANL A,directANL A,@RiANL A,#dataANL direct,AANL direct,#dataANL C,bitANL C,/bit1、ACALL addr11指令名称:绝对调用指令指令代码:{A10,A9,A8,10001},A[7:0]指令功能:构造目的地址,进行子程序调用。

其方法是以指令提供的11位地址(al0~a0),取代PC的低11位,PC的高5位不变。

操作内容:PC←(PC)+2SP←(SP)+1(SP)←(PC)7~0SP←(SP)+1(SP)←(PC)15~8PC10~0←addrl0~0字节数: 2机器周期:2使用说明:由于指令只给出子程序入口地址的低11位,因此调用范围是2KB。

2、ADD A,Rn指令名称:寄存器加法指令指令代码:28H~2FH指令功能:累加器内容与寄存器内容相加操作内容:A←(A)+(Rn), n=0~7字节数: 1机器周期;1影响标志位:C,AC,OV3、ADD A,direct指令名称:直接寻址加法指令指令代码:25H指令功能:累加器内容与内部RAM单元或专用寄存器内容相加操作内容:A←(A)+(direct)字节数: 2机器周期:1影响标志位:C,AC,OV4、ADD A,@Ri指令名称:间接寻址加法指令指令代码:26H~27H指令功能:累加器内容与内部RAM低128单元内容相加操作内容:A←(A)+((Ri)), i=0,1字节数: 1机器周期:1影响标志位:C,AC,OV5、ADD A,#data指令名称:立即数加法指令指令代码:24H指令功能:累加器内容与立即数相加操作内容:A←(A)+data字节数: 2机器周期:1影响标志位:C,AC,OV6、ADDC A,Rn指令名称:寄存器带进位加法指令指令代码:38H~3FH指令功能:累加器内容、寄存器内容和进位位相加操作内容:A←(A)+(Rn)+(C), n=0~7字节数: 1机器周期:1影响标志位:C,AC,OV7、ADDC A,direct指令名称:直接寻址带进位加法指令指令代码:35H指令功能:累加器内容、内部RAM低128单元或专用寄存器内容与进位位加操作内容:A←(A)+(direct)+(C)字节数: 2机器周期:1影响标志位:C,AC,OV8、ADDC A,@Ri指令名称:间接寻址带进位加法指令指令代码:36H~37H指令功能:累加器内容、内部RAM低128单元内容及进位位相加操作内容:A←(A)+((Ri))+(C), i=0,1字节数: 1机器周期:1影响标志位:C,AC,OV9、ADDC A,#data指令名称:立即数带进位加法指令指令代码:34H指令功能:累加器内容、立即数及进位位相加操作内容:A←(A)+data+(C)字节数: 2机器周期:1影响标志位:C,AC,OV10、AJMP addr11指令名称:绝对转移指令指令代码:{A10,A9,A8,00001},A[7:0]指令功能:构造目的地址,实现程序转移。

第二章 MCS-51指令系统及汇编语言程序设计

XCH A, direct 1 1 0 0 0 1 0 1

6.半字节交换指令

助记符 XCHD A, @Ri 机器码 1101011r 功能 ; (A3~0)((Ri)3~0), i=0,1

数据传送类指令

数据传送类指令的助记符有: MOV、MOVX、MOVC XCH、XCHD PUSH、POP

寄存器C MCS-51 传送指令 示意图 寄存器 R7~R0 直接地址 direct 直接地址 direct 寄存器 DPTR 立即数 #data

例:设外部数据存储器2097H单元中内容 为80H,在执行下列指令后,则A中的内容 为80H。 MOV P2, #20H MOV R0, #97H MOVX A, @R0

Ⅱ.由Ri内容指示外部数据存储器地址 (2)累加器内容送外部数据存储器

助记符 MOVX @Ri, A 目标 源 机器码 11110011 功能 ; ((Ri)+(P2))←A, i=0,1

二、直接寻址

紧跟在操作码后的是操作数的直接地址。 该方式中操作数存储的空间有三种:

1.内部数据存储器的低1 ; (70H)→A 2.位地址空间 例:MOV C, 00H ; 直接位00H内容→ 进位位 MOV 00H → 3.特殊功用功能寄存器 *只能用直接寻址方式进行访问。 例: MOV IE, #85 ; 立即数85H →中断允许寄存器

执行该指令时: 1.P3.6引脚上输出WR有效信号 2. Ri包含的低8位地址由P0口输出,高8位地址信息 由P2口输出。 3.累加器A的内容由P0口输出。 4.P0口作分时复用。

3.程序存储器内容送累加器

该类指令常用于查表。 (1)PC作基址寄存器

助记符 MOVC A, @A+PC 目标 源 机器码 10000011 功能 ; PC←PC+1 A ←((A)+(PC))

51单片机汇编指令集(附记忆方法)

51单片机汇编指令集一、数据传送类指令(7种助记符)MOV(英文为Move):对内部数据寄存器RAM和特殊功能寄存器SFR的数据进行传送;MOVC(Move Code)读取程序存储器数据表格的数据传送;MOVX (Move External RAM) 对外部RAM的数据传送;XCH (Exchange) 字节交换;XCHD (Exchange low-order Digit) 低半字节交换;PUSH (Push onto Stack) 入栈;POP (Pop from Stack) 出栈;二、算术运算类指令(8种助记符)ADD(Addition) 加法;ADDC(Add with Carry) 带进位加法;SUBB(Subtract with Borrow) 带借位减法;DA(Decimal Adjust) 十进制调整;INC(Increment) 加1;DEC(Decrement) 减1;MUL(Multiplication、Multiply) 乘法;DIV(Division、Divide) 除法;三、逻辑运算类指令(10种助记符)ANL(AND Logic) 逻辑与;ORL(OR Logic) 逻辑或;XRL(Exclusive-OR Logic) 逻辑异或;CLR(Clear) 清零;CPL(Complement) 取反;RL(Rotate left) 循环左移;RLC(Rotate Left throught the Carry flag) 带进位循环左移;RR(Rotate Right) 循环右移;RRC (Rotate Right throught the Carry flag) 带进位循环右移;SWAP (Swap) 低4位与高4位交换;四、控制转移类指令(17种助记符)ACALL(Absolute subroutine Call)子程序绝对调用;LCALL(Long subroutine Call)子程序长调用;RET(Return from subroutine)子程序返回;RETI(Return from Interruption)中断返回;SJMP(Short Jump)短转移;AJMP(Absolute Jump)绝对转移;LJMP(Long Jump)长转移;CJNE (Compare Jump if Not Equal)比较不相等则转移;DJNZ (Decrement Jump if Not Zero)减1后不为0则转移;JZ (Jump if Zero)结果为0则转移;JNZ (Jump if Not Zero) 结果不为0则转移;JC (Jump if the Carry flag is set)有进位则转移;JNC (Jump if Not Carry)无进位则转移;JB (Jump if the Bit is set)位为1则转移;JNB (Jump if the Bit is Not set) 位为0则转移;JBC(Jump if the Bit is set and Clear the bit) 位为1则转移,并清除该位;NOP (No Operation) 空操作;五、位操作指令(1种助记符)CLR 位清零;SETB(Set Bit) 位置1。

第三章 MCS-51汇编语言指令

RETN

JZ JNZ JC

ANL

ORL XRL RL

AND

OR XOR ROL

POP

ACALL LCALL AJMP LJMP SJMP RET

POP

CALL CALL JMP JMP JMP RET

JB

DJNZ ADD ADDC INC DA SUBB

RLC

RR RRC CPL CLR JNC JNB

标号是表示该指令所在的符号地址,一般是由字母 打头的字母数字串表示。 操作码助记符表示了指令的操作性质。

第一、第二操作数表示操作的对象。指令的操作码 部分必不可少,操作数部分有的指令没有,或只有一 个操作数。 注释部分是用户为了方便阅读程序所加的说明,可 有可无。

MCS-51单片机采用变字长存储机器指令的方式,指 令字长有单字节、双字节和三字节三种。其格式如下:

MOV A,#20H执行示意图

3.1.2 寄存器寻址 把指定的某一可寻址的工作寄存器R0~R7的内容 作为操作数。指令操作码的低3位指示所用寄存器。 如:INC R3;(R3)←(R3)+1 … RS1 RS0 …

0 0 0 * * 0 1 1

片内RAM …… 0100 0010 01000001 …… 1 ALU

编译即将源代码进行汇编,形成可执行的代码。调试 即将编译通过的可执行代码进行模拟运行,输入给定的 数据,检查运行结果是否正确。

3.2.6 MCS-51伪指令 伪指令是供汇编用的特殊指令,只是在汇编过程中产 生某种控制,或者对标号进行赋值。 伪指令在汇编时不产生机器语言指令,仅提供汇编控 制信息。 ⒈设置起始地址伪指令ORG(Origin) 格式:ORG NNNN 功能:指定目标程序或数据块在存储器中存放的起始 地址。其中NNNN为十进制或十六进制地址。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MCS-51汇编语言指令集符号定义表符号含义RnR0~R7寄存器n=0~7Direct直接地址,内部数据区的地址RAM(00H~7FH)SFR(80H~FFH) B,ACC,PSW,IP,P3,IE,P2,SCON,P1,TCON,P0@Ri间接地址Ri=R0或R1 8051/31RAM地址(00H~7FH) 8052/32RAM地址(00H~FFH)#data8位常数#data1616位常数Addr1616位的目标地址Addr1111位的目标地址Rel相关地址bit内部数据RAM(20H~2FH),特殊功能寄存器的直接地址的位²指令介绍指令字节周期动作说明算数运算指令1.ADD A,Rn11将累加器与寄存器的内容相加,结果存回累加器2.ADD A,direct21将累加器与直接地址的内容相加,结果存回累加器3.ADD A,@Ri1将累加器与间接地址的内容相加,结果存回累加器4.ADD A,#data21将累加器与常数相加,结果存回累加器5.ADDC A,Rn11将累加器与寄存器的内容及进位C相加,结果存回累加器6.ADDC A,direct21将累加器与直接地址的内容及进位C相加,结果存回累加器7.ADDC A,@Ri11将累加器与间接地址的内容及进位C相加,结果存回累加器8.ADDC A,#data21将累加器与常数及进位C相加,结果存回累加器9.SUBB A,Rn11将累加器的值减去寄存器的值减借位C,结果存回累加器10.SUBB A,direct21将累加器的值减直接地址的值减借位C,结果存回累加器11.SUBB A,@Ri11将累加器的值减间接地址的值减借位C,结果存回累加器12.SUBB A,0data21将累加器的值减常数值减借位C,结果存回累加器13.INC A11将累加器的值加114.INC Rn1将寄存器的值加l15.INC direct21将直接地址的内容加116.INC @Ri11将间接地址的内容加117.INC DPTR11数据指针寄存器值加1说明:将16位的DPTR加1,当DPTR的低字节(DPL)从FFH溢出至00H时,会使高字节(DPH)加1,不影响任何标志位18.DEC A11将累加器的值减119.DEC Rn11将寄存器的值减120.DEC direct21将直接地址的内容减121.DEC @Ri11将间接地址的内容减122.MUL AB14将累加器的值与B寄存器的值相乘,乘积的低位字节存回累加器,高位字节存回B寄存器说明:将累加器A和寄存器B内的无符号整数相乘,产生16位的积,低位字节存入A,高位字节存入B寄存器。

如果积大于FFH,则溢出标志位(OV)被设定为1,而进位标志位为023.DIV AB14将累加器的值除以B寄存器的值,结果的商存回累加器,余数存回B寄存器说明:无符号的除法运算,将累加器A除以B寄存器的值,商存入A,余数存入B。

执行本指令后,进位位(C)及溢出位(OV)被清除为024.DA A11将累加器A作十进制调整,若(A) 3-0>9或(AC)=1,则(A) 3-0←(A)3-0+6若(A) 7-4>9或 (C)=1,则(A) 7-4←(A)7-4+6逻辑运算指令25.ANL A,Rn11将累加器的值与寄存器的值做AND的逻辑判断,结果存回累加器26.ANL A,direct21将累加器的值与直接地址的内容做AND的逻辑判断,结果存回累加器27.ANL A,@Ri11将累加器的值与间接地址的内容做AND的逻辑判断,结果存回累加器28.ANL A,#data21将累加器的值与常数做AND的逻辑判断,结果存回累加器29.ANL direct,A21将直接地址的内容与累加器的值做AND的逻辑判断,结果存回该直接地址30.ANL direct,#data32将直接地址的内容与常数值做AND的逻辑判断,结果存回该直接地址31.ORL A,Rn11将累加器的值与寄存器的值做OR的逻辑判断,结果存回累加器32.ORL A,direct21将累加器的值与直接地址的内容做OR的逻辑判断,结果存回累加器33.ORL A,@Ri11将累加器的值与间接地址的内容做OR的逻辑判断,结果存回累加器34.ORL A,#data21将累加器的值与常数做OR的逻辑判断,结果存回累加器35.ORL direct,A21将直接地址的内容与累加器的值做OR的逻辑判断,结果存回该直接地址36.ORL direct,#data32将直接地址的内容与常数值做OR的逻辑判断,结果存回该直接地址37.XRL A,Rn11将累加器的值与寄存器的值做XOR的逻辑判断,结果存回累加器38.XRL A,direct21将累加器的值与直接地址的内容做XOR的逻辑判断,结果存回累加器39.XRL A,@Ri11将累加器的值与间接地扯的内容做XOR的逻辑判断,结果存回累加器40.XRL A,#data21将累加器的值与常数作XOR的逻辑判断,结果存回累加器41.XRL direct,A21将直接地址的内容与累加器的值做XOR的逻辑判断,结果存回该直接地址42.XRL direct,#data32将直接地址的内容与常数的值做XOR的逻辑判断,结果存回该直接地址43.CLR A11清除累加器的值为044.CPL A11将累加器的值反相45.RL A11将累加器的值左移一位46.RLC A11将累加器含进位C左移一位47.RR A11将累加器的值右移一位48.RRC A11将累加器含进位C右移一位49.SWAP A11将累加器的高4位与低4位的内容交换。

(A)3-0←(A)7-4 数据转移指令50.MOV A,Rn11将寄存器的内容载入累加器51.MOV A,direct21将直接地址的内容载入累加器52.MOV A,@Ri11将间接地址的内容载入累加器53.MOV A,#data21将常数载入累加器54.MOV Rn,A11将累加器的内容载入寄存器55.MOV Rn,direct2将直接地址的内容载入寄存器56.MOV Rn,gdata21将常数载入寄存器57.MOV direct,A21将累加器的内容存入直接地址58.MOV direct,Rn22将寄存器的内容存入直接地址59.MOV direct1, direct232将直接地址2的内容存入直接地址1 60.MOV direct,@Ri22将间接地址的内容存入直接地址61.MOV direct,#data32将常数存入直接地址62.MOV @Ri,A11将累加器的内容存入某间接地址63.MOV @Ri,direct22将直接地址的内容存入某间接地址64.MOV @Ri,#data21将常数存入某间接地址65.MOV DPTR,#data1632将16位的常数存入数据指针寄存器66.MOVC A,@A+DPTR1(A) ←((A)+(DPTR))累加器的值再加数据指针寄存器的值为其所指定地址,将该地址的内容读入累加器67.MOVC A,@A+PC12(PC)←(PC)+1;(A)←((A)+(PC))累加器的值加程序计数器的值作为其所指定地址,将该地址的内容读入累加器68.MOVX A,@Ri12将间接地址所指定外部存储器的内容读入累加器(8位地址)69.MOVX A,@DPTR12将数据指针所指定外部存储器的内容读入累加器(16位地址)70.MOVX @Ri,A12将累加器的内容写入间接地址所指定的外部存储器(8位地址)71.MOVX @DPTR,A12将累加器的内容写入数据指针所指定的外部存储器(16位地址)72.PUSH direct22将直接地址的内容压入堆栈区73.POP direct22从堆栈弹出该直接地址的内容74.XCH A,Rn11将累加器的内容与寄存器的内容互换75.XCH A,direct21将累加器的值与直接地址的内容互换76.XCH A,@Ri11将累加器的值与间接地址的内容互换77.XCHD A,@Ri11将累加器的低4位与间接地址的低4位互换布尔代数运算78.CLR C11清除进位C为079.CLR bit21清除直接地址的某位为080.SETB C11设定进位C为181.SETB bit21设定直接地址的某位为182.CPL C11将进位C的值反相83.CPL bit21将直接地址的某位值反相84.ANL C,bit22将进位C与直接地址的某位做AND的逻辑判断,结果存回进位C 85.ANL C,/bit22将进位C与直接地址的某位的反相值做AND的逻辑判断,结果存回进位C 86.ORL C,bit22将进位C与直接地址的某位做OR的逻辑判断,结果存回进位C 87.ORL C,/bit22将进位C与直接地址的某位的反相值做OR的逻辑判断,结果存回进位C 88.MOV C,bit21将直接地址的某位值存入进位C89.MOV bit,C22将进位C的值存入直接地址的某位90.JC rel22若进位C=1则跳至rel的相关地址91.JNC rel22若进位C=0则跳至rel的相关地址92.JB bit,rel32若直接地址的某位为1,则跳至rel的相关地址93.JNB bit,rel32若直接地址的某位为0,则跳至rel的相关地址94.JBC bit,rel32若直接地址的某位为1,则跳至rel的相关地址,并将该位值清除为0 程序跳跃95.ACALL addr1122调用2K程序存储器范围内的子程序96.LCALL addr1632调用64K程序存储器范围内的子程序97.RET12从子程序返回98.RETI2从中断子程序返回99.AJMP addr1122绝对跳跃(2K内)100.LJMP addr1632长跳跃(64K内)101.SJMP rel22短跳跃(2K内)-128~+127字节102.JMP @A+DPTR12跳至累加器的内容加数据指针所指的相关地址103.JZ rel22累加器的内容为0,则跳至rel所指相关地址104.JNZ rel22累加器的内容不为0,则跳至rel所指相关地址105.CJNE A,direct,rel32将累加器的内容与直接地址的内容比较,不相等则跳至rel所指的相关地址106.CJNE A,#data,rel32将累加器的内容与常数比较,若不相等则跳至rel所指的相关地址107.CJNE @Rn,#data,rel32将寄存器的内容与常数比较,若不相等则跳至rel所指的相关地址108.CJNE @Ri,#data,rel32将间接地址的内容与常数比较,若不相等则跳至rel所指的相关地址109.DJNZ Rn,rel2将寄存器的内容减1,不等于0则跳至rel所指的相关地址110.DJNZ direct,rel32将直接地址的内容减1,不等于0则跳至rel所指的相关地址111.NOP11无动作。