LPC总线介绍

LPC(low_pin_count)

DMA传输流程 1. 当LFRAME#选择LAD[3:0]上的信号为“0000b”,主机开始传输信号 。 2.主机选择传输类型为DMA,传输方向为DMA方向。 3.主机选择通道数目,如果合适,由终端计数。 4.主机指明传输的大小:8,16或32位。 5.如果DMA读状态:主机转向总线并驱动第一个8位数据;在一个有效的 同步信号中,外设承认这8位数据;如果传输的是16或32位数据,则会 重复处理接下来的每8位数据。 6.如果DMA写状态:主机转向总线并等待数据;外设由同步信号指示数 据准备,并传输第一个8位数据;如果传输的是16或32位数据,则会重 复发送同步信号并处理接下来的每8位数据。 7.外设转向总线。

LPC I/F Enables Register用于控制各个Device的Enable

在DOS下读取LPC的相关寄存器信息

End Thank you

Reset Policy

Reset 时LPC Interface HOST 与外设的状态 • 当Reset 为有效(低电平) 时 HOST: LFRAME#为高电平 LAD[3:0]为高阻态 LDRQ# 为无效状态 外 设: LFRAME#为无效 LAD[3:0]为高阻态 LDRQ# 为高电平 • 当Reset 为无效(高电平)时,LCLK开始RUN

• I/O Cycles 在这种情况下,I/O的读写周期被用于外设。这些通常用于寄存器或 FIFO通道,而且通常有最少的同步次数。 • Firmware Memory Cycles Firmware memory 读写周期为PC系统引导Firmware。同步时间将取 决于设备的速度。其ADDR字段是28位。

LPC 的访问

查阅Intel Q77系列南桥资料。通过搜索PCI Bus Device找到LPC,由 表可知LPC Controller是BUS0:Device 31:Function 0。

lpc协议内容

lpc协议内容【原创版】目录1.LPC 协议简介2.LPC 协议的工作原理3.LPC 协议的优点与不足4.LPC 协议的应用领域正文一、LPC 协议简介LPC(Low Power Converter)协议,即低功耗转换器协议,是一种用于电子设备低功耗管理的通信协议。

它主要应用于计算机硬件设备,如CPU、内存、硬盘等,以实现设备的自动功耗管理。

LPC 协议能够使硬件设备在与其他设备通信时自动调整功耗,从而降低系统的整体能耗。

二、LPC 协议的工作原理LPC 协议的工作原理主要基于设备间的通信与协作。

设备通过发送特定的 LPC 命令和响应,来实现对设备功耗的控制。

具体来说,LPC 协议的工作流程如下:1.设备 A 向设备 B 发送 LPC 命令,请求其进入低功耗状态。

2.设备 B 收到命令后,根据自身状态和系统需求,判断是否需要进入低功耗状态。

3.如果设备 B 需要进入低功耗状态,它会向设备 A 发送确认响应,表示已开始执行低功耗操作。

4.设备 A 收到响应后,可以继续发送其他 LPC 命令,或者等待设备B 完成低功耗操作后恢复通信。

三、LPC 协议的优点与不足1.优点(1)降低系统能耗:LPC 协议能够使设备自动调整功耗,从而降低系统的整体能耗,提高续航表现。

(2)简化硬件设计:LPC 协议使得设备能够通过软件控制功耗,减少了硬件设计的复杂性。

(3)提高系统稳定性:LPC 协议能够实时监测设备功耗,有助于防止设备过热等安全问题。

2.不足(1)兼容性问题:LPC 协议可能会遇到不同厂商、不同设备之间的兼容性问题,导致功耗控制效果不佳。

(2)通信开销:LPC 协议需要设备间进行通信与协作,会增加一定的通信开销。

四、LPC 协议的应用领域LPC 协议广泛应用于计算机硬件设备,如 CPU、内存、硬盘等,以实现设备的自动功耗管理。

此外,LPC 协议也被用于其他电子设备领域,如手机、平板、物联网设备等,以满足低功耗、高性能的需求。

硬件基础系列之七-LPC

硬件基础系列之七LPC目录目录 (ii)1. 概述...................................................................................................................... - 1 -2. 发展来历............................................................................................................... - 1 -2.1. LPC发展目的 .............................................................................................. - 1 -2.2. LPC发展过程 .............................................................................................. - 1 -2.3. LPC应用 ..................................................................................................... - 3 -3. 接口信号............................................................................................................... - 3 -4. 传输协议............................................................................................................... - 4 -4.1. LPC信号电平及时序.................................................................................... - 4 -4.2. LPC协议 ..................................................................................................... - 6 -4.3. Memory访问 .............................................................................................. - 9 -4.4. I/O访问.....................................................................................................- 10 -4.5. DMA访问 ..................................................................................................- 11 -4.6. FWH访问 ..................................................................................................- 13 -5. 典型应用..............................................................................................................- 14 -6. 总结.....................................................................................................................- 14 -6.1. DMA ..........................................................................................................- 14 -1.概述LPC是由Intel 提出,为了在PC 上把ISA 取消而制定的一个新总线规格。

LPC214x系列微控制器中的I 2C总线接口实现

I 接 口完 全 符 合 整 个 I 规 范 .它 能 支 持 断 开 到 2 C C L C 1 X系列 的连接 而不 影 响 同一 I 总线 上 的其 P 24 C

它 器件 。

地址寄存器 IA DR I 2

2 0 . W . d,n 0 88 W We ac c

维普资讯

第 2 8 8 1o 第 8 O 年月 卷 期 0

姆霹缔瘗

V1 o o1N. . 8 O

Au . 2 8 g 00

2 工 作 流 程 与 操 作

在 主发送 器 模 式 中 ,系统 中 的仲 裁逻 辑 会 检

输出

部 分

I CON S 2 ET

串行时钟 I l 发生器 l l

中断

I CONCLR 2 I CL 2S H

控制寄存器&S L C 占空比 周期寄存器

位 ,以产 生 中断请求 。

IS L 2 CL

8 移 位 寄存 器 ( D T 位 I A )用来 存 放要 发送 的 2

一

个 字 节 的 串行 数 据 或 刚 接 收 到 的 一 个 字 Байду номын сангаас 。

。 蕊 {

状寄器 态存

ID T 2 A 的数 据 总 是 从 右 向左 移 动 :最先 发 送 MS B

收 稿 日期 : 0 7 1 — 4 20—20

图1 I 2 行 接 口 方 框 图 c串

l 电子元 器 件 主 硐 O

2 0 年8 0 8 月

LC 1 X P 24 系列微 控制器 中的 I 总线接 口实现 2 C

景 志 .冯 小平

LPC总线介绍

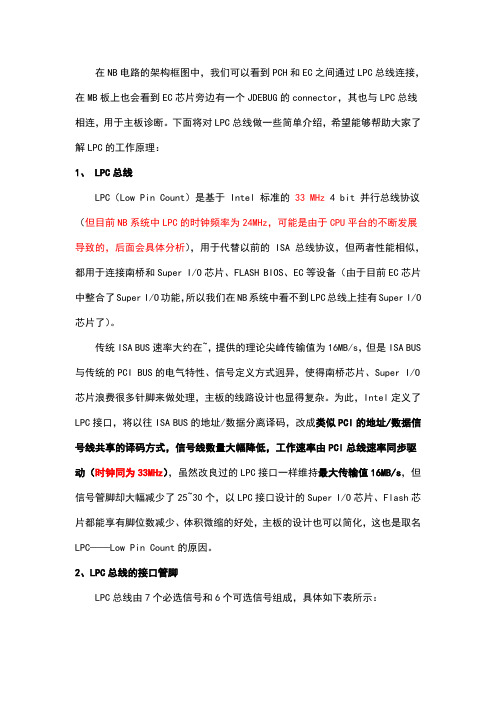

在NB电路的架构框图中,我们可以看到PCH和EC之间通过LPC总线连接,在MB板上也会看到EC芯片旁边有一个JDEBUG的connector,其也与LPC总线相连,用于主板诊断。

下面将对LPC总线做一些简单介绍,希望能够帮助大家了解LPC的工作原理:1、LPC总线LPC(Low Pin Count)是基于 Intel 标准的33 MHz 4 bit 并行总线协议(但目前NB系统中LPC的时钟频率为24MHz,可能是由于CPU平台的不断发展导致的,后面会具体分析),用于代替以前的 ISA 总线协议,但两者性能相似,都用于连接南桥和Super I/O芯片、FLASH BIOS、EC等设备(由于目前EC芯片中整合了Super I/O功能,所以我们在NB系统中看不到LPC总线上挂有Super I/O 芯片了)。

传统ISA BUS速率大约在~,提供的理论尖峰传输值为16MB/s,但是ISA BUS 与传统的PCI BUS的电气特性、信号定义方式迥异,使得南桥芯片、Super I/O 芯片浪费很多针脚来做处理,主板的线路设计也显得复杂。

为此,Intel定义了LPC接口,将以往ISA BUS的地址/数据分离译码,改成类似PCI的地址/数据信号线共享的译码方式,信号线数量大幅降低,工作速率由PCI总线速率同步驱动(时钟同为33MHz),虽然改良过的LPC接口一样维持最大传输值16MB/s,但信号管脚却大幅减少了25~30个,以LPC接口设计的Super I/O芯片、Flash芯片都能享有脚位数减少、体积微缩的好处,主板的设计也可以简化,这也是取名LPC——Low Pin Count的原因。

2、LPC总线的接口管脚LPC总线由7个必选信号和6个可选信号组成,具体如下表所示:表 3-2 LPC总线可选信号列表信号外设Host设备信号描述LDRQ#O I外设进行DMA or bus mastering操作的总线请求信号,一对一,外设之间不能共享同一个LDRQ#SERIRQ I/O I/O中断请求信号CLKRUN#OD I/OD外设进行DMA or bus mastering操作才会需要该信号,用于停止PIC bus,同PCI CLKRUN信号LPME#OD I/OD电源管理唤醒,与PCI PME相似LPCPD#I O Power DownLSMI#OD I SMI信号系统管理中断MB板上的JDEBUG connector有12pin,没有连接LRESET#信号,只连接了其余的6个必选信号,为主板诊断提供接口,其中CLK_DEBUG由PCH提供,24MHZ:EC与PCH连接的LPC总线中除了包含7个必选信号,还包含SEEIRQ和CLKRUN#信号。

lpc 常用指令

LPC(Low Pin Count)是一种用于实现嵌入式系统低成本、低功耗、小体积设计的总线,它使用较少的引脚数以减少芯片的封装尺寸。

LPC总线的指令集是建立在并行总线基础上的,它包括以下一些常用指令:

MPS(进栈指令):将运算结果送入栈存储器的第一段,同时将先前送入的数据依次移到栈的下一段。

MRD(读栈指令):将栈存储器的第一段数据(最后进栈的数据)读出且该数据继续保存在栈存储器的第一段,栈内的数据不发生移动。

MPP(出栈指令):将栈存储器的第一段数据(最后进栈的数据)读出且该数据从栈中消失,同时将栈中其它数据依次上移。

INV(反指令):执行该指令后将原来的运算结果取反。

NOP(空操作指令):不执行操作,但占一个程序步。

基于LPC总线的POST卡设计与实现

P S O T卡( o r nslts cr) p we o e t ad 即主板诊断 卡 , fe 用

源稳定后 , 即发出 p w r o d o e o 信号 , 片组撤 去 rst g 芯 ee 信

号 ,P 便 从 F F 0 或 者 F F F F H 开始 执 行 指 CU F FH FFFO 令, 这个地址放置 的是一 条跳转指 令 , 跳转 至系统 BO IS 真正 的启 动代 码 处 引。BO I S首 先做 的 就是 P S O T加 电 自检 , 对计算 机 的硬件设 备进 行检 测 , 每一个 设备 对 应一个检测代码 。

I S 1 0 4 5 S N 0 2 9 6

实

验

技

术

与

管

理

第 2卷 7

第 8期

21 0 0年 8月

订 二

彳 -

Ex e i n a c n l g n p rme t l Te h o o y a d Ma a e n n g me t

V o . 7 No 8 A u . 2 0 12 . g 01

Tin Yi e ,Zha ng i a nl i o Do lng

( i u n Vo a in l n c n c lC l g ,Jy a 5 6 0,Ch n ) J y a c t a d Te h i o l e i u n 4 4 5 o a a e ia

Ab ta t sr c :The ni r al pp ia in f om p e a s u ve s a lc to o c ut r m ke POST c r be om ig n ndip ns bl bu t o1 ad c n a i s e a e De g o . Ba e n t e s u s d o h t dy ofLPC s p o o ola d is sg l e i ton, hetm ig o bu r t c n t i nas d fnii t i n fIPC usi e e r he oc ly. b sr s a c d f a l M e nwhie, ih t om bna in H DI a l w t he c i to ofV ha dwa ed s rp i a ua e, h r r e c i ton lng g t e POST a d b s d on LPC c r a e busi s

lpc 控制算法

lpc 控制算法

LPC(Longitudinal Predictive Control,纵向预测控制)算法是一种先进

的控制算法,主要用于预测和控制纵向的运动过程。

在车辆控制、自动驾驶等领域中,LPC算法被广泛应用于预测和控制车辆的纵向运动,如制动、加速和巡航控制等。

LPC算法基于车辆的动力学模型和运动学模型,通过预测未来的车辆状态和运动轨迹,实现对车辆的纵向控制。

在LPC算法中,需要建立车辆的动力

学模型和运动学模型,并确定模型的参数和状态变量。

然后,通过预测未来的车辆状态和运动轨迹,计算出最优的控制输入,如制动压力、加速踏板位置等,以实现最优的纵向控制。

LPC算法的优点在于能够主动预测和控制纵向运动过程,可以提前进行控制,避免了常规控制方法的滞后。

同时,LPC算法还可以根据不同的工况和场景,自适应地调整控制参数和策略,以提高控制的准确性和稳定性。

总的来说,LPC算法是一种有效的纵向预测控制方法,在车辆控制和自动驾驶等领域中具有广泛的应用前景。

lpc协议内容

lpc协议内容【实用版】目录1.LPC 协议简介2.LPC 协议的内容3.LPC 协议的应用4.LPC 协议的优缺点正文【LPC 协议简介】LPC 协议,全称为 Low Pin Count,即低引脚数协议,是一种串行通信协议,主要用于在微控制器(MCU)和周边设备(如 EEPROM、LCD 显示器等)之间进行通信。

相较于并行通信,LPC 协议在减少引脚数量、降低成本、提高系统稳定性等方面具有显著优势。

【LPC 协议的内容】LPC 协议的内容主要包括以下几个方面:1.通信方式:LPC 协议采用串行通信方式,即数据是逐个位按顺序进行传输。

发送方将数据字符从并行转换为串行,按位发送给接收方。

接收方收到串行数据后,再将其转换为并行数据。

2.通信时序:LPC 协议的通信时序包括三个主要阶段,即数据传输阶段、时钟信号阶段和片选信号阶段。

数据传输阶段用于发送数据,时钟信号阶段用于同步数据传输,片选信号阶段用于选择要通信的设备。

3.数据格式:LPC 协议的数据格式分为数据包和数据帧。

数据包是数据的组织单位,包含起始符、地址、数据、校验和、结束符等部分。

数据帧是数据包的传输单位,包含一个起始符、多个数据包和一个结束符。

4.校验方式:LPC 协议采用 CRC(循环冗余校验)进行数据校验,以确保数据传输的正确性。

【LPC 协议的应用】LPC 协议广泛应用于各种微控制器和周边设备的通信,如:1.MCU 与 EEPROM 之间的通信:LPC 协议可用于实现 MCU 对EEPROM 的读写操作。

2.MCU 与 LCD 显示器之间的通信:LPC 协议可用于实现 MCU 对LCD 显示器的控制,如显示文字、图片等。

3.MCU 与其他周边设备之间的通信:LPC 协议还可应用于其他各类周边设备的通信,如传感器、存储器等。

【LPC 协议的优缺点】1.优点:(1)引脚数量少:LPC 协议采用串行通信,相较于并行通信可减少大量引脚数量,降低成本。

基于LPC总线的POST卡设计

二.总体框图

其中232是串口通信芯片,通过MAX232与电脑进行串口 通信; 4245是一个双向电平转换芯片,它能够实现电平的从 3.3V到5V的双向转换。因为FPGA I/O管脚需要3.3V供 电。

4

设计思路

一.设计思路 在LPC总线上对80H端口进行解码,并在2个七段LED上显示。解码器 实际上完成的是对LPC总线的控制功能,采用FPGA实现,用Verilog HDL语言对FPGA进行编程,完成对地址的译码,串行数据到并行数 据类型的转换,发送总线反转信号,并完成到LED的译码,根据LPC 控制功能,可以把它描述为一种状态机。下图为LPC控制功能的状态 转移图。

论文题目:基于LPC总线的POST卡设计 学生姓名:*** 指导教师:***

Contents

1

2 3

设计内容

设计指标

应用价值

4

设计思路

1

设计内容

一.主板诊断卡: power on self test card,简称POST卡,主要用于诊断主板故障的原 因与部位。计算机在开机检测的前期,对关键性部位(如CPU、内存 等)的检测不能输出在显示屏上,这些核心故障的诊断难以处理,但计 算机在检测过程中,BIOS会将检测代码送至80H端口,通过对80H端 口进行解码并用LED显示,结合故障代码含义速查表就能判断出计算机 故障所在。FPGA(现场可编程门阵列)具有速度快、保密性强、体积 小、可靠性高等优点,用途广泛,并且设计开发周期短,用FPGA实现 POST诊断码的解码和输出逻辑,效果事半功倍。 二.LPC总线: LPC(low pin count)是一种连接南桥和Suer IO,BIOS以及EC等设备 的总线。 LPC总线跟传统的ISA总线相比,信号比ISA少很多,但传输速率依然 可达 16MB/s。由于这些特点,在连接外设时,用来代替ISA总线。 其框架图如下:

丢包补偿的lpc方法

丢包补偿的lpc方法丢包补偿的LPC方法随着互联网的普及和网络应用的快速发展,网络丢包问题成为了影响用户体验的重要因素之一。

网络丢包是指在数据传输过程中,由于各种原因导致数据包丢失的现象。

这种现象会导致网络传输的不稳定性和延迟增加,影响用户的网络体验。

为了解决这一问题,丢包补偿的LPC(Lost Packet Compensation)方法应运而生。

LPC方法是一种通过补偿丢失的数据包来提高网络传输质量的技术。

它通过在网络传输的两端进行丢包检测和补偿操作,使得用户在接收端能够获得更加稳定和完整的数据。

LPC方法主要包括丢包检测、丢包补偿和网络传输优化三个步骤。

丢包检测是LPC方法的第一步。

在数据传输过程中,发送端会标记每个数据包,并在接收端进行检测。

如果接收端发现某个数据包丢失,就会向发送端发送请求,要求重新发送丢失的数据包。

通过这种方式,发送端和接收端可以实时地监测数据包的丢失情况,并采取相应的措施。

丢包补偿是LPC方法的核心步骤。

当接收端检测到某个数据包丢失后,它会向发送端发送请求,要求重新发送该数据包。

发送端收到请求后,会根据接收端的要求,重新发送丢失的数据包。

为了保证数据传输的效率,LPC方法还可以采用差错校正码等技术,对数据包进行纠错,提高数据传输的可靠性。

网络传输优化是LPC方法的关键一环。

为了减少丢包的发生,LPC 方法可以通过优化网络传输路径、增加网络带宽、改善网络设备等方式,提高网络传输的质量和稳定性。

此外,LPC方法还可以利用数据压缩和分段传输等技术,减少数据包的大小和传输时间,进一步提高网络传输的效率。

总结起来,丢包补偿的LPC方法通过丢包检测、丢包补偿和网络传输优化三个步骤,可以有效提高网络传输质量,降低丢包率,提高用户的网络体验。

在实际应用中,LPC方法已经被广泛应用于在线游戏、视频直播、实时通信等领域。

通过采用LPC方法,网络应用可以更加稳定和可靠地运行,为用户提供更好的服务。

LPC简介

Chapter1:LPC17xx Introductory information 第一章:lpc17xx入门资料文档信息信息内容关键词lpc1769,lpc1768,lpc1767,lpc1766,lpc1765,lpc1764,lpc1759,lpc1758,lpc1756,lpc1754,lpc1752,lpc1751,手臂,微,32位,通用串行总线,以太网接口,微控制器,可以,摘要lpc17xx用户手册译结果(英> 中)复制结果双语对照查看恩智浦半导体um10360lpc17xx用户手册修订历史修订日期的描述120100104lpc17xx用户手动修改。

修改:•“草案”状态删除。

•编辑更新和印刷更正各地用户手册。

•lpc1758,lpc1767,和lpc1768已被添加到列表的前盖,订货信息,在1节和4节–,部分的识别号码表32部分–7.11。

•操作的注意在睡眠模式被删除从第4–8.1。

•表8–81,clkout的功能是从描述p1.25。

在部分•以太网章,10节和10节的–16.1–17.2,有人指出在外部物理层必须初始化和物理时钟收到的以太网块前进一步的以太网初始化块。

此外,在10节–17.1,标题下“所有的描述”的句子,-仲裁被删除。

一般的更正确的讨论的主题中添加了2节–5。

•收发器分数波特率发生器是残疾人在波特率的自动模式(参见14节和15节的–14.4.10.1–4.14)。

在第14节•–4.12节和15–4.16,说明价值的动态链接库已登记的更正阅读”价值的动态链接库登记必须大于2”。

•* * * * * * ** * * * * * *运动控制•描述计算的qei章(见26节–4.3),定义为公式的值相加,并说明改进。

描述的位置和指数比较寄存器错误表明,小于,等于,大于比较可以选择。

它变为只显示“等于”。

•说明闪光签名生成已被添加在32节–10。

联系信息更多信息,请访问:销售办公地址,请发送电子邮件到:salesaddresses@ 1。

LPC总线信号描述

• HOLD#:暂时停止和SPI存储器的通信

SST25LF040A

பைடு நூலகம்

SST25LF040A的PIN定义

• SCK:提供SPI接口的时钟信号.地址、命令、输入 数据将在上升沿被锁存。数据输出将在下降沿被 移出。 • SI:串行数据输入,连续地传输数据、地址、命 令。在SCK的上升沿被锁存。 • SO:从设备移出数据脚。在SCK的下降沿移出。 • CE#:片选信号,当电位从高电位变为低电位时 芯片被选择,当芯片工作时该脚应保持低电位。 • WP#:写保护脚。和内部BPL寄存器结合形成写 保护功能。如下图:

可选信号

• LDRQ#:仅仅用于客户端需要作DMA总线控制时 发出该信号,每个客户端须一单独的信号不可共 享。 • SERIRQ:仅用于客户端需中断支持时使用,如 果主机没包含ISA IRQ时则须该信号. • CLKRUN#:和PCI CLKRUN#信号相同.仅用于客 户端在DMA总线控制时可以停止PCI总线. • LPME#:近似于PCI PME#.用于LPC客户端去请求 从休眠中换醒. • LPCPD#:用于指示客户端做好准备,电源将从客户 端移走. • LSMI#:如果客户端想使用SMI#信号时使用该信号.

lpc总线信号描述lpc总线lpc总线协议总线寂静信号信号二总线can总线sm总线控制器现场总线通用串行总线控制器i2c总线

LPC总线信号分为必须信号和 可选信号

必须信号如下

• LAD(3:0):多功能管脚(命令、地址、数据) • LFRAME#:指示一个新的周期的开始、旧的周期 结束。 • LRESET#:和PCIRST#相同。对于主机来如果 有PCIRST就不需要该信号。该信号用于初始化 各LPC设备的内部寄存器。 • LCLK:和PCICLK相同。如果主机有PCICLK将 不需要该信号,为LPC设备提供工作时钟。

基于LPC2106的IIC总线E2PROM的应用

基于LPC2106的IIC总线E2PROM的应用作者:袁易君来源:《中小企业管理与科技·中旬版》2008年第12期摘要:本文利用Proteus软件仿真的特点,提出在此平台上仿真设计IIC总线E2PROM芯片AT24C02在Arm7内核LPC2106中的应用,用实例说明了LPC21XX系列单片机的标准IIC 接口的使用。

关键词:Proteus 软件仿真 Arm7内核0 引言Proteus软件是一款主要面向8位及32位单片机软硬件设计的仿真平台,能实时仿真多种单片机芯片,如51单片机系列、AVR单片机系列、PIC单片机系列及Arm单片机系列等,可减少学习单片机的成本,又可达到良好的学习效果。

LPC2106是一款基于Arm7内核的32位单片机,具有非常小的尺寸和极低的功耗,片内具有128KB的Flash ROM,64KB的静态RAM,芯片本身具有标准的IIC串行接口,不需要像51单片机一样进行软件模拟,同时还具有其他一些8位单片机所不具备的功能,其应用前景将会越来越广泛。

1 LPC2106 I2C接口及24C E2PROM介绍LPC2106 I2C接口可配置为主机或从机,总线时钟频率可调整,最高支持400KHz总线频率,LPC2106在使用I2C总线的时候,要将P0.2、P0.3功能设置选择为SCL、SDA,并且总线上要接两个上拉电阻,阻值大小为几K左右,同时需要设置一些相关寄存器的内容选择工作方式。

24C系列串行EEPROM具有体积小、功耗低、工作电压允许范围宽等特点外,还具有型号多、容量大、二总线协议、占用I/O口线少、容量扩展配置极其灵活方便、读写操作相对简单等特点。

本系统中使用的是24C02(2kb),采用CMOS工艺,工作电压在1.8~5.5V之间,24C系列采用最多的封装形式是8脚PDIP封装,8 脚封装中A0、A1、A2为器件地址选择位,这3个引脚配置成不同的编码值,在同一串行总线上最多可扩展8片同一容量或不同容量的24C系列串行EEPROM芯片。

lpc协议内容

lpc协议内容

【原创版】

目录

1.LPC 协议简介

2.LPC 协议的工作原理

3.LPC 协议的优点

4.LPC 协议的应用领域

5.LPC 协议的发展前景

正文

一、LPC 协议简介

LPC(Low Pin Count)协议,即低引脚数协议,是一种串行通信协议,主要用于低速通信和低引脚数设备之间的通信。

它的主要特点是通信速度快、硬件引脚数量少,因此在电子设备中得到了广泛的应用。

二、LPC 协议的工作原理

LPC 协议的工作原理是通过发送方将数据字节发送到接收方,接收方在接收到数据后进行解码,并将解码后的数据传递给主机。

发送方和接收方通过特定的时钟信号进行同步,以确保数据传输的准确性。

三、LPC 协议的优点

LPC 协议具有以下几个优点:

1.通信速度快:LPC 协议采用串行通信,其通信速度比并行通信要快,可以有效地提高数据传输的效率。

2.硬件引脚数量少:LPC 协议只需要两根引脚即可完成通信,因此可以节省大量的硬件资源。

3.成本低:由于 LPC 协议所需的硬件资源少,因此其成本相对较低。

四、LPC 协议的应用领域

LPC 协议广泛应用于电子设备中,如存储器、输入输出设备、传感器等。

同时,LPC 协议也得到了许多行业标准的支持,如 I2C

(Inter-Integrated Circuit)协议、SPI(Serial Peripheral Interface)协议等。

五、LPC 协议的发展前景

随着电子设备越来越小型化、集成化,LPC 协议在未来的发展前景十分广阔。

常见总线简介CAN、USART、SPI、SCI等

任何一个微处理器都要与一定数量的部件和外围设备连接,但如果将各部件和每一种外围设备都分别用一组线路与CPU直接连接,那么连线将会错综复杂,甚至难以实现。

为了简化硬件电路设计、简化系统结构,常用一组线路,配置以适当的接口电路,与各部件和外围设备连接,这组共用的连接线路被称为总线。

采用总线结构便于部件和设备的扩充,尤其制定了统一的总线标准则容易使不同设备问实现互连。

微机中总线一般有内部总线、系统总线和外部总线。

内部总线是微机内部各外围芯片与处理器之间的总线,用于芯片一级的互连;而系统总线是微机中各插件板与系统板之间的总线,用于插件板一级的互连;外部总线则是微机和外部设备之间的总线,微机作为一种设备,通过该总线和其他设备进行信息与数据交换,它用于设备一级的互连。

另外,从广义上说,计算机通信方式可以分为并行通信和串行通信,相应的通信总线被称为并行总线和申行总线。

并行通信速度快、实时性好,但由于占用的口线多,不适于小型化产品;而串行通信速率虽低,但在数据通信吞吐量不是很大的微处理电路中则显得更加简易、方便、灵活。

串行通信一般可分为异步模式和同步模式。

随着微电子技术和计算机技术的发展,总线技术也在不断地发展和完善,而使计算机总线技术种类繁多,各具特色。

下面仅对微机各类总线中目前比较流行的总线技术分别加以介绍。

一、内部总线1.I2C总线I2C(Inter-IC)总线10多年前由Philips公司推出,是近年来在微电子通信控制领域广泛采用的一种新型总线标准。

它是同步通信的一种特殊形式,具有接口线少,控制方式简化,器件封装形式小,通信速率较高等优点。

在主从通信中,可以有多个I2C总线器件同时接到I2C总线上,通过地址来识别通信对象。

2.SPI总线串行外围设备接口SPI(serialperipheralinterface;)总线技术是Motorola公司推出的一种同步串行接口。

Motorola公司生产的绝大多数MCU(微控制器)都配有SPI硬件接口,如68系列MCU。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

在NB电路的架构框图中,我们可以看到PCH和EC之间通过LPC总线连接,在MB板上也会看到EC芯片旁边有一个JDEBUG的connector,其也与LPC总线相连,用于主板诊断。

下面将对LPC总线做一些简单介绍,希望能够帮助大家了解LPC的工作原理:1、LPC总线LPC(Low Pin Count)是基于Intel 标准的33 MHz 4 bit 并行总线协议(但目前NB系统中LPC的时钟频率为24MHz,可能是由于CPU平台的不断发展导致的,后面会具体分析),用于代替以前的ISA 总线协议,但两者性能相似,都用于连接南桥和Super I/O芯片、FLASH BIOS、EC等设备(由于目前EC芯片中整合了Super I/O功能,所以我们在NB系统中看不到LPC总线上挂有Super I/O芯片了)。

传统ISA BUS速率大约在7.159~8.33MHz,提供的理论尖峰传输值为16MB/s,但是ISA BUS与传统的PCI BUS的电气特性、信号定义方式迥异,使得南桥芯片、Super I/O芯片浪费很多针脚来做处理,主板的线路设计也显得复杂。

为此,Intel 定义了LPC接口,将以往ISA BUS的地址/数据分离译码,改成类似PCI的地址/数据信号线共享的译码方式,信号线数量大幅降低,工作速率由PCI总线速率同步驱动(时钟同为33MHz),虽然改良过的LPC接口一样维持最大传输值16MB/s,但信号管脚却大幅减少了25~30个,以LPC接口设计的Super I/O芯片、Flash芯片都能享有脚位数减少、体积微缩的好处,主板的设计也可以简化,这也是取名LPC——Low Pin Count的原因。

2、LPC总线的接口管脚LPC总线由7个必选信号和6个可选信号组成,具体如下表所示:MB板上的JDEBUG connector有12pin,没有连接LRESET#信号,只连接了其余的6个必选信号,为主板诊断提供接口,其中CLK_DEBUG由PCH提供,24MHZ:EC与PCH连接的LPC总线中除了包含7个必选信号,还包含SEEIRQ和CLKRUN#信号。

这里需要注意的是JDEBUG的CLK信号与连接EC和PCH的LPC 总线中CLK信号并非同一个信号。

PCH提供了2个输出24MHz时钟的管脚,但每个时钟只能驱动一个LPC设备,故EC和JDEBUG各连接一个。

3.LPC总线的通信协议LPC总线支持多种事务类型的操作,例如IO读写、内存读写、DMA读写、Firmware memory读写等。

一个cycle通常一下流程:●总线host拉低LFRAME#信号,指示cycle开始,同时将相关信息输出到LAD[3:0]上●主机Host根据Cycle类型驱动相应的信息到LAD[3:0]上,比如当前操作的事务类型、数据传输方向及size大小、访问地址等。

●host根据Cycle类型的不同选择进行驱动数据或者是移交总线控制权。

●外设获取总线控制权后,将相应的数据驱动到LAD[3:0]上。

表示该Cycle完成。

●外设释放总线控制权。

至此该Cycle结束。

一个典型cycle通常由Start、Cyctype+Dir、ADDR 、Size(DMA only)、Channel(DMA only)、TAR、Sync、DATA状态组成,下图是一个典型的cycle示例流程,该cycle类似于IO读或内存读操作中的cycle,DATA字段由外设驱动发送给host.图4.1 cycle示意流程图3.1 StartStart用于指示一个传输的开始或者结束。

当FRAME#信号有效时,所有的外设都要监视LAD[3:0]信号,并在FRAME#信号有效的最后一个时钟进入START状态。

LAD[3:0]的值编码如下表表4.1 Start状态LAD[3:0]定义3.2 Cycle Type/Direction(CYCTYPE+DIR)该状态由Host驱动,对Cycle的传输类型(Memory、IO、DMA)以及传输方向进行说明。

LAD[0]在该场中被保留,作为外设应该忽略。

具体定义值见下表表4.2 Cyctype+DIR状态LAD[3:0]定义3.3 Size该状态表示传输数据DATA字段的大小,由host驱动,当数数据为16或32bits,将分成多个DATA转态发送,Size只存在于DMA类型cycle中。

而在IO和内存类型cycle中,每个cycle只能传输8bits数据。

Size状态LAD[1:0]有效,LAD[3:2]被忽略,LAD[3:0]具体定义如下表4.3 Size状态LAD[3:0]定义3.4 ADDR/ChannelADDR状态表示地址信息,由host驱动。

在IO cycle中,地址信息为16bits (4个时钟周期);在内存cycle中,地址信息为32bits(8个时钟);而在DMA cycle 中,则没有ADDR状态,取代的则是Channel状态(1个时钟)。

LAD[2:0]表示channel 的序号,其中channel 0~3为8bit channels, channel 5~7为16 bit channels, channel4一般被保留作为bus master 的请求信号。

ADDR的地址信息先从高位发送。

3.5 TAR(Turn-around)TAR用于交换总线的控制权(2个时钟),当host要将总线转交给外设时,TAR 由host驱动;当外设要将总线交还给host时,TAR由外设驱动。

TAR两个时钟周期的第一个时钟周期有host或外设驱动,LAD[3:0]=1111;第二时钟周期host或外设则将LAD[3:0]置为三态,但由于LAD[3:0]管脚内部有弱上拉,LAD[3:0]还都是处于高逻辑电平,所以TAR的两个时钟LAD[3:0]都为1111.3.6 SyncSync用来加入等待状态,持续时间为1~N个时钟周期。

在target或者DMA传输操作时,Sync由外设驱动;在bus master操作时,Sync由Host驱动。

可能的组合见表表4.4 Sync状态LAD[3:0]定义当外设还没准备好时,可以插入一些等待周期0101(短等待)或0110(长等待),等到Ready状态来到时,可以选择驱动为“0000"(准备好),“1010”(错误)或者“1001"(Ready More)。

4.6.1 Sync Timeout总线上通常可能发生以下几种潜在的错误:1.当Host发起一个Cycle(Memory、IO、DMA)后,但是,总线上没有设备驱动SYNC场,当Host检测到3个连续的时钟内都没有响应时,便可以认为总线上没有外设响应此次Cycle操作。

2.Host驱动一个Cycle(Memory,IO,DMA),一个设备驱动了一个有效的SYNC 场来插入等待(LAD[3:0]=’0101b’或者’0110b’),但是却不能完成该Cycle,这种情况在外设锁定的时候就发生了。

此时,Host应采取以下措施以解除总线死锁:●假如SYNC是’0101b’,那么SYNC时钟周期最多为8个。

当Host检测到有多于8个时钟周期的SYNC场,那么Host将取消这个Cycle。

●假如SYNC是’0110b’,那么这里将没有最大SYNC长度的限制。

外设必须设计有保护机制来完成这个Cycle。

当由Host来驱动SYNC时,因为延迟的原因,它可能不得不插入大量的等待周期,但外设不应该认为有time out发生。

下图为SYNC的周期过长引起timeout,此时LFRAME#会拉低4个LCLK周期,进入start状态,来终止这个Cycle.图4.2 LFRAME终止cycle4.7 DATADATA状态占用两个时钟周期,用于传送一个字节数据。

当数据流向外设时,该场由Host驱动;反之,当数据流向Host时,则该场由外设驱动。

在传输过程的时候,低4位最先被驱动到总线上,在第一个时钟,Data[3:0]被驱动,第二个时钟,Data[7:4]被驱动。

4.8 各事务类型操作举例图4.3 memory read/write图4.4 I/O read/write图4.5 DMA read/write(16bits)4、L PC总线的测量(逻辑分析仪)用逻辑分析仪TLA5202测得LPC总线中LCLK、LFRAME#、LAD[3:0]信号,下面为测量的几组数据波形:下面是测的是两个cycle的总体波形图,由于我在测试时外接的测试线过长,在cycle结束后的末期引入了串扰,图中的黄色框图中便为串扰信号波形,理想状态应该是LAD[3:0]统一保持高逻辑,后面再统一变为低逻辑。

这里我们可以看到时钟信号LCLK并不是一直输出的,只有当cycle开始时,PCH才会输出LCLK 信号,cycle结束后,若一段时间内不再有cycle传输,LCLK便不再输出。

图5.1 Cycle总体波形图下图测试的是一组I/O read cycle,host要读取IO地址为0064H的数据,外设接管总线后,经过11个时钟周期的长等待SYNC状态(0110)后,变为ready 状态(sync为0000),然后外设将数据1CH发送给host,驱动TAR状态(FF),将总线控制权交还给host,这个cycle结束。

图5.2 I/O read cycle下图测试的是一组I/O write cycle,host向IO地址025AH写入数据93H,外设接管总线后,经过8个时钟周期的长等待SYNC状态(0110)后,变为ready 状态(sync为0000),表明外设接收到数据,之后外设驱动TAR状态(FF),将总线控制权交还给host,这个cycle结束。

图5.3 I/O write cycle下图测试的是time out情况,host向IO地址0080H写入数据01H,然后host 驱动TAR状态来移交纵向,但无外设驱动sync状态来接管总线,LAD一直处于弱上拉的高状态,经过5个时钟周期的无响应后,host拉低LFRAME#,保持4个LCLK,进入start状态,LAD[3:0]=1111,则host将该cycle终结。

图5.4 time out。