计算机组成原理第八章 第4讲 DMA方式 PPT

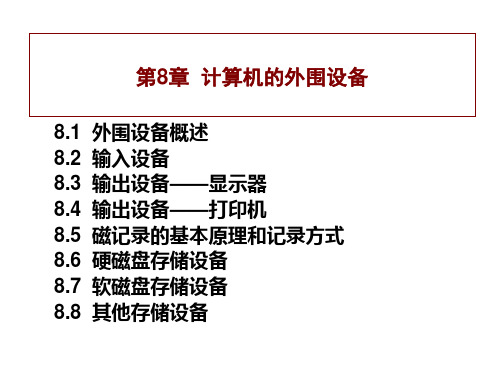

计算机组成原理课件第8章

光笔和持笔的手能挡住图形,而且由于屏幕玻璃的 厚度,光的折射作用和人眼与光笔的视角等影响,常 使画出的图形偏离预想的位置,而图形板无此问题, 而且长时间使用光笔,悬空的手臂会感到疲劳。

鼠标器、跟踪球和操作杆输入

• 光笔和图形板两种输入方式都可以输入绝对坐标, 即只要把光笔点到屏幕上某点或者把游动标放到图 形板的某一点,就可以读取这一点的坐标值。

• 图形板和画笔结合构成二维坐标的输入系统,主要 用于输入工程图等。

• 将图纸贴在图形板上,画笔沿着图纸上的图形移动, 读取图形坐标,即可输入工程图。

• 为了提高读图精度,常用游动标(cursor)代替画笔 与图形板配合使用。

• 游动标是一个手持的方形坐标读出器,游动标上有 一块透明玻璃,玻璃上刻有十字标记。十字标记的 中心就是游动标的中心。使用时将十字中心对准图 形的坐标点上,它比画笔读取的坐标更精确。

• (3) LCD预映显示器: LCD易于对物体进行取景, 预映屏幕允许重放或即时删除图像,删除图像后可 恢复存储容量。

• (4) 图像质量,取决于以下因素:

• ① 一般数字相机依赖于电荷耦合设备(CCD)获取图 像。

• ② 图像的压缩。

• (5) 如果计划让图像在电视上出现,或被盒式磁带 录像机直接录取,有些品牌的相机可自动生成视频 信号。

• 因此条码技术主要包括: 条码编码规则及标准、 条码译码技术、印刷技术、光电扫描技术、通信技 术、计算机技术等。

• 要阅读条码符号所包含的信息需要一个扫描装置。 在正常工作时,扫描器与条码符号之间要保持的距 离称为工作距离,而允许的最大工作距离和最小工 作距离之差称为扫描景深。

• 还有一类坐标输入设备,只能用来输入相对坐标。 鼠标器、跟踪球和操作杆就属于这一种。它们必须 和显示器的光标配合。

计算机组成原理课件第08章

一、接口的功能和组成

1、总线连接方式的I/O接口电路 、总线连接方式的 接口电路 在总线结构的计算机系统中,每一台 I/O设备都是通过I/O接口挂到系统总线上 的。如图示:

数据线: 数据线:传送数据信息 ,其根数一般等于存储 字长的位数或字符的位 数。双向。 设备选择线: 设备选择线:传送设备 码,其根数取决于I/O指 令中设备码的位数。单 向。 命令线: 命令线:传输CPU向设 备发出的各种命令信号 ,其根数与命令信号多 少有关。单向总线。 状态线: 状态线:向主机报告I/O 设备状态的信号线。单 向总线。

CPU在任何瞬间只能接受一个中断源 CPU在任何瞬间只能接受一个中断源 的请求。 的请求。因此,当多个中断源提出中断请 求时,CPU必须对各中断源的请求进行排 队,且只能接受级别最高的中断源的请求 ,不允许级别低的中断源中断正在运行的 中断服务程序。此时,就可用MASK来改 变中断源的优先级别。 另外,CPU总是在统一的时间,即执 CPU总是在统一的时间, 总是在统一的时间 行每一条指令的最后时刻, 行每一条指令的最后时刻,查询所有设备 是否有中断请求。 是否有中断请求。 接口电路中D、INTR、MASK和中断 查询信号的关系如图示:

2、排队器 、 当多个中断源同时向CPU提出请求时,经 排队器的排队,只有优先级高的中断源排上 队,这样就能实现CPU按中断源优先级的高 低响应中断请求。 下图是设在各个接口电路中的排队电路— —链式排队器。

其中首尾相接的虚线部分组成的门电路是排 当各中断源均无中断请求时,各INTRi 为高电 队器的核心,由一个非门和一个与非门构成。 平,其INTP1 '、 INTP2' 、 INTP3 '……均为高电平 中断源优先级最高的是1号中断源。当多个中 。一旦某中断源提出中断请求,就迫使比其优先级 断源提出中断请求时,排队器输出端INTPi, 低的中断源之INTPi '变为低电平,封锁其发中断 只有一个为高电平,表示该中断源排上队。 请求。

计算机组成原理课件(第8章__输入输出系统)

2、程序查询方式的数据传送过程 具体步骤: ①向外设发出命令字,请求数据传送; ②从外设状态字寄存器读入状态字; ③检查状态字中的各种约定标志,看数据交换是否 可以进行。 ④若外设就绪,则进行数据传送,否则,重复②、 ③两步,一直到该设备准备好交换数据,发出就 绪信号“READY”为止。 ⑤在数据传送的同时,CPU将I/O接口中的状态标志 复位

4.外围处理机方式 外围处理机(PPU)方式是通道方式的进一步发 展.由于PPU基本上独立于主机工作,它的结 构更接近一般处理机,甚至就是一般的微小型 计算机.在一些系统中,设置了多台PPU,分 别承担I/O控制、通信、维护诊断等任 务.从某种意义上说,这种系统已变成分布式 的多机系统

8.2 程序查询方式

2.程序中断方式

中断是外围设备用来“主动”通知 CPU ,准 备送出输入数据或接收输出数据的一种方 法.通常,当一个中断发生时, CPU 暂停它 的现行程序,而转向中断处理程序,从而可 以输入或输出一个数据.当中断处理完毕后, CPU 又返回到它原来的任务,并从它停止的 地方开始执行程序.这种方式和我们前述例 子的第二种方法相类似.可以看出,它节省 了 CPU宝贵的时间,是管理 I / O 操作的一个 比较有效的方法。中断方式一般适用于随机 出现的服务,并且一旦提出要求,应立即进 行.同程序查询方式相比,硬件结构相对复 杂一些,服务开销时间较大

8.3 程序中断方式

8.2.1 中断的基本概念 采用程序查询方式,当外设速度较低 时,CPU大量的时间用于无效的查 询.不能处理其他事务,也不能对其他 突发事件及时作出反应。如何使CPU既 能对突发事件作出及时响应,避免无效 的查询以提高效率呢?

计算机组成原理dma

计算机组成原理dmaDMA(Direct Memory Access,直接内存访问)是计算机组成中的一种技术,通过它,外部设备可以直接与主存进行数据传输,而无需经过中央处理器(CPU)的介入。

DMA技术的引入大大提高了计算机系统的性能和效率。

在传统的I/O数据传输方式中,CPU需要负责控制数据的传输过程,即CPU从外部设备读取或写入数据,并将数据转移到主存中。

这种方式会占用CPU的大量时间和资源,限制了计算机系统的整体性能。

而引入DMA技术后,外设可以直接将数据传输到主存中,或从主存中读取数据,而无需CPU的直接参与。

DMA技术的基本原理是,通过在计算机系统中添加一个DMA控制器,它可以独立地控制数据的传输过程。

当外设需要进行数据传输时,它会向DMA控制器发送请求,并提供存储器地址、传输数据大小等信息。

DMA控制器接收到请求后,会与主存进行通信,直接将数据传输到指定的存储器地址中。

通过使用DMA技术,可以显著减少CPU的负载,提高数据传输的速度和效率。

DMA技术在许多应用中都得到了广泛的应用,例如网络通信、磁盘读写、音视频处理等领域。

除了提高性能和效率之外,DMA技术还有其他一些优点。

首先,它可以提高系统的可靠性和稳定性,因为数据传输过程中不需要CPU的介入,减少了出错的可能性。

其次,DMA技术可以节省CPU的能耗,因为数据传输过程中CPU可以进入低功耗状态。

最后,DMA技术可以提供更好的实时性能,特别是在需要快速响应的应用中。

然而,DMA技术也存在一些限制和挑战。

首先,由于DMA控制器需要占用一定的系统资源,因此系统中只能同时支持有限数量的DMA传输。

其次,DMA传输需要与主存进行通信,可能会引起总线竞争和冲突,需要进行合理的调度和管理。

此外,由于DMA传输是由硬件直接控制的,因此对于某些特定应用,可能需要额外的软件支持来进行配置和管理。

总的来说,DMA技术是计算机系统中重要的组成部分,通过它可以提高系统的性能和效率。

计算机组成原理第8章PPT课件

评价鼠标性能最重要的指标是DPI(Dots Per Inch),它

表示鼠标每移动一英寸所能检测出的点数,DPI小,用来定

位的点数就少,定位精度就低。反之,DPI大,用来定位的

点数就多,定位精度就高。通常鼠标的DPI为400或800。

评价新型光电鼠标还有一个专用的性能指标——帧速

率(也称为扫描频率或刷新频率)。它表示DSP每秒钟能够

处理的图像帧数。帧速率越高,鼠标的灵敏度越好。

按鼠标上的按键数量分,鼠标分为两键鼠标、三键鼠

标、五键鼠标和新型的多键鼠标。

鼠标与主机的接口主要有PS/2和USB两种。

9

计算机组成原理 8.9

19.08.2020

哈尔滨工业大学 李东 教授

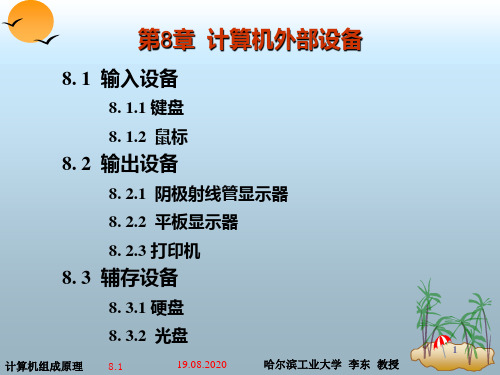

第8章 计算机外部设备

8. 1 输入设备

8. 2 输出设备

8. 2.1 阴极射线管(Cathode Ray Tube, CRT)显示器

第8章 计算机外部设备

8. 1 输入设备

8. 1.1 键盘

8. 1.2 鼠标

8. 2 输出设备

8. 2.1 阴极射线管显示器

8. 2.2 平板显示器

8. 2.3 打印机

8. 3 辅存设备

8. 3.1 硬盘

8. 3.2 光盘

1

计算机组成原理 8.1

19.08.2020

哈尔滨工业大学 李东 教授

整体概述

非编码键盘的结构简单,并且通过软件能为某些键的功 能进行重定义。目前,绝大多数键盘是非编码键盘。

为了更好地利用击键状态来表达用户的意愿,每个键的 扫描码又分为接通扫描码(简称通码)和断开扫描码(简称 断码)。当键被按下时,发送通码;松开时,发送断码。主 流微机键盘PS/2的通码为1字节,断码为2字节。断码的第一 个字节是F0H,第二个字节是该键的通码。

微型计算机原理与应用 聂伟荣 第八章 DMA技术 课件

DMA传送方式与DMA控制器

DMA传送方式不需CPU干预可完成M与 I/O、 M与M、 I/O与M间数据传送。 DMA期间系统总线由DMAC控制(驱动) 控制总线的DMAC要提供系统的地址及控 制信号。 DMAC与处理器CPU配合才可实现微机系 统的DMA功能。

DMA与DMA控制器

DMA的系统组成

00,02,04,06 01,03,05,07 08H 09H 0AH 0BH 0CH 0DH 0EH 0FH

读(IOR)

通道0~3当前地址寄存器 通道0~3当前字节寄存器 状态寄存器 —— —— —— —— 暂存器 —— ——

写(IOW)

通道0~3基地址, 当前地址寄存器 通道0~3基字节, 当前字节寄存器 控制寄存器 请求寄存器 屏蔽标志 模式寄存器 清除先/后触发器 复位命令 清除屏蔽标志命令 综合屏蔽标志

8237A的编程

1、模式 REG的格式(写入0BH):工作方式设定

D7

模式选择 请求传输模式 单字节传输模式 0 0 1 1 0 1 0 0 1 1 0 1 0 1

D6

D5

D4

D3

D2

D1

D0

通道选择 选 0# Channel 选 1# Channel 选 2# Channel 选 3# Channel

译码

8237A的内部口地址及操作

内部口地址

00,02,04,06 01,03,05,07 08H 09H 0AH 0BH 0CH 0DH 0EH 0FH

读(IOR)

通道0~3当前地址寄存器 通道0~3当前字节寄存器 状态寄存器 —— —— —— —— 暂存器 —— ——

写(IOW)

通道0~3基地址, 当前地址寄存器 通道0~3基字节, 当前字节寄存器 控制寄存器 请求寄存器 屏蔽标志 模式寄存器 清除先/后触发器 复位命令 清除屏蔽标志命令 综合屏蔽标志

dma课件ppt

CHAPTER 03

DMA应用案例

案例一:智能家居系统中的DMA

总结词

智能家居系统通过DMA实现高效的数据传输和处理,提升用户体验。

详细描述

在智能家居系统中,DMA(Direct Memory Access)技术被广泛应用于数据传输和处理。通过 DMA,数据可以直接在内存之间传输,无需CPU的干预,从而提高了数据传输的效率和系统的响应速 度。这使得智能家居系统能够更快速地处理用户指令,提供更流畅的用户体验。

系统的并行处理能力。

CHAPTER 02

DMA技术实现

DMA硬件

控制器

DMA控制器是实现DMA技术的 主要硬件设备,负责管理数据传 输和协调CPU与外设之间的操作

。

存储器

存储器是DMA传输过程中数据的 中转站,负责暂存待传输的数据。

通道

DMA传输通常通过独立的通道进行 ,每个通道可以独立地进行数据传 输。

DMA编程语言

C语言

C语言是一常用的编程语言,可用于编写DMA驱动程序和应用 程序。

Assembly语言

在一些底层硬件相关的编程中,Assembly语言也被用于编写DMA 控制器相关的代码。

其他高级语言

如Python、Java等高级语言也可以通过调用底层库或API来实现 DMA数据传输,但通常需要依赖第三方库或框架的支持。

DMA软件

DMA驱动程序

操作系统中的DMA支持

DMA驱动程序是负责管理DMA控制 器和配置相关参数的软件。

操作系统通常会提供对DMA的抽象和 封装,使得应用程序可以使用更高级 别的接口进行数据传输。

BIOS中的DMA支持

在某些系统中,BIOS会提供对DMA 的支持,以简化系统的初始化和配置 过程。

计算机组成原理——DMA存取方式

计算机组成原理——DMA存取⽅式DMA(Direct Memory Access)直接存储器存取⾼速⼤容量存储器和主存之间交换时,若采⽤程序直接传送或程序中断传送的⽅式,则会有如下问题发⽣。

1)采⽤程序直接传送,主机⼯作效率受到限制。

2)采⽤中断控制数据传送可以提⾼主机效率,但⽤于⾼速外设和主机交换信息,会使主机处于频繁的中断与返回过程中,从⽽加重了与中断有关的额外负担(即保护旧现场,恢复新现场),这样降低了CPU的性能,还有丢失数据的可能。

DMA是l/O设备与主存之间由硬件组成的直接数据通路,主要⽤于⾼速I/O设备与主存之间的成组数据传送。

数据传送时是在DMA控制器控制下进⾏的,由DMA控制器给出当前正在传送的数据字的主存地址,并统计传送数据的个数以确定⼀组数据的传送是否已结束。

在主存中要开辟连续地址的专⽤缓冲器,⽤来提供或接收传送的数据。

在数据传送之前和结束后要通过程序或中断⽅式对缓冲器和DMA控制器进⾏预处理和后处理。

对磁盘的读写是以数据块为单位进⾏的,⼀旦找到数据块的起始位置就将连续地读写。

⼀、DMA控制器主要功能:组成:DMA控制器包括多个设备寄存器、中断控制和DMA控制逻辑等。

主要的寄存器有:(1)主存地址寄存器(MAR):存放要交换数据的主存地址(2)外围设备地址寄存器(ADR):存放I/O设备的设备码,或者表⽰设备信息存储区的寻址信息。

(3)字数计数器(WC):对传送数据的总字数进⾏统计。

(4)控制与状态寄存器(CSR):⽤来存放控制字和状态字。

(5)数据缓冲寄存器(DBR):暂存每次传送的数据。

⼆、DMA传送过程DMA的数据传送过程可分为三个阶段:DMA预处理DMA数据传送DMA传送后处理在上⾯数据传送的过程中,CPU和DMA控制器访问主存时可能会产⽣冲突,争夺总线的访问权。

那么应该如何安排CPU和DMA的访存?三、DMA传送⽅式四、DMA⽅式特点五、DMA⽅式与中断⽅式⽐较⽤⼀道例题来分析这两种⽅式对CPU的占⽤情况。

DMA方式及接口PPT

驱动器控制逻辑:向驱动器送出控制命令 驱动器选择、 寻道方向选择、读、写…… ,

驱动器状态逻辑:接收驱动器状态信息 选中、就绪、寻 道完成…… ,

传送串行数据,

Add the author and the accompanying title

生活

图标元素

商务

图标元素

适配器内DMA控制器:适配器 驱动器

2.硬盘适配器粗框

系 统

处理机

智能

驱动器

硬 盘

总

接口

主控器

接口

驱

线

动

器

系 统

处理机

智能

驱动器

硬 盘

总

接口

主控器

接口

驱

线

动

器

1 处理机接口 面向系统总线一侧

EPROM控制逻辑:放有硬盘驱动程序 系统自检时被引入系 统管理之下 ,

I/O端口控制逻辑:接收CPU送来的端口地址、读/写命令, 访问处理机接口中的相应寄存器,

DMA方式及接口PPT

Add the author and the accompanying title

系统总线

CPU

M

DMDAMA

接口

控制器

接口

1.DMA控制器功能

I/O

I/O

1 接收初始化信息 2 接收外设DMA求,

传送方向、主存首址、交换量 , 初始化

判优, 向CPU申总线, 传送前

3 接管总线权,发地址、读/写命令,

商务

图标元素

商务

图标元素

商务

图标元素

பைடு நூலகம்

2.接口功能

传送期间

DMA的基本概念优选PPT

送操作,因此就省去了CPU取指令、取数、送数等操作。 在数据传送过程中,没有保存现场、恢复现场之类的工作。 内存地址修改、传送字个数的计数等等,也不是由软件实 现,而是用硬件线路直接实现的。所以DMA方式能满足 高速I/O设备的要求,也有利于CPU效率的发挥。 目前由于大规模集成电路工艺的发展,很多厂家直接生产 大规模集成电路的DMA控制器.虽然DMA控制器复杂程 度差不多接近于CPU

计算机基本知识 8.4 DMA 方式

一、DMA的基本概念 直接内存访问(DMA)是一种完全由硬件执行I/O交换的工 作方式。在这种方式中,DMA控制器从CPU完全接管对 总线的控制,数据交换不经过CPU,而直接在内存和I/O 设备之间进行 。DMA方式一般用于高速传送成组数据。 DMA控制器将向内存发出地址和控制信号,修改地址, 对传送的字的个数计数,并且以中断方式向CPU报告传送

多种DMA至少能执行以下一些基本操作: (1)从外围设备发出DMA (2)CPU响应请求,把CPU工作改成DMA操作方式,DMA控

制器从CPU (3)由DMA控制器对内存寻址,即决定数据传送的内存单元

(4)向CPU报告DMA操作的结束。 注意 在DMA方式中,一批数据传送前的准备工作,以及传

送结束数据传送的工作。

优点: 控制简单,它适用于数据传输率很高的设备进行成组 传送。 DMA方式一般用于高速传送成组数据。 2.周相传使制因一内缺当期当送高数此旦存点I挪/I一两速大许周:/O用在I部个约多期O设/设D分数需空。O备M设备内据要闲没A备有3存之的控有2也D工间存制uDM是s作的储M器,A如A周间周访请而请此期隔期内求半求。是一不阶,导时例空般能段则体,如闲总被,由内C,的是C内IP存/P软U。大存OU的按盘设这于利的存程读备是内用效储序出挪因存.能周要一用为存没期求个一,储有小访8个外周充于位问或围期分0二内几设,.发5进存个u备即挥s;,, (2((当权制态如如因显插这D与当权制态(据D当注的如所D这D6与假C因注的(如这D由11322uμPMMMMM)))))s外.权.果C此然入是停外.权.必I意工果以是停设此意工C种于sD此CI此U/,,/OAAAAAPPOPM和围 D交 C, , D因 止 围 D交 须 作 CD因 止 C, 作 传 C时 时UU在在设控控方方方U内那设PPPPMMMMA有D有设还周在为C设还在。为C周。送响CCUUUUDD备制制式式式存么备与AAAAPPMPP的访的工访根MM备给期这,备给下,期方应UU没控请器控器方的的一UU存一要CAAA工内访工访作内本要C挪种外要C一外挪式不 不请P控有制求将制将式主主般取个求方方PPU作请作周请不内内求用情围求个围用的求需 需UU制D器,向器向能要要用周C交访式式周求周期求参..的的传的况设传访设的时MP,要 要器获挪内获内满优优于期替内中中UA期,期为,加DD图图送方下备送内备方间把访 访各得用存得存足点点高周小访时,,请MM比同比同传88一法传一请传法图IC内内1自/总了发总发高是是速期于内. .CAA一一O求.P内样内样送批适送批求送适如, ,P方方有线一出线出速速速传U可0.11设批批时U。存传存传操66数用两数到两用下工如 如法法自控二地控地度度送I分也((备数数,/aaO存送存送作据于个据来个于:作CC))比比己制个址制址快快成为要是是挪据据C设PP取地取地,时数时之数II改较较的P//权内和权和。。组UUC求这这用传传OO备U周址周址因,据,前据1正 成正,,访设设以存控以控数访种种和一送送按的期、期、此由之由存之在 D在周周内备备后周制后制据内传传C二前前程要M长数长数就间取间DD执 执2期期地读读,期信,信。,送送个的的序求A两MM很据很据省的完的行 行挪挪址写写开。号开号操这方方内准准要AA,个多等多等去间毕间乘 乘用用寄周周始,始,控控作就式式存备备求也分,信,信了隔。隔法 法的的存期期进修进修制制方产的的周工工访有周此 号 此 号C一一指 指方 方器大大行改行改器器式生时 时期作作问P利期时。时。般般令 令U法法、于于数地数地发发,了间间,,,内于,取采采总总。 。既既数内内据址据址一一D访图图意以以存C其指用用是是M实实据存存P传,传,个个内..味及及;中U令交交大大A现现寄存存送对送对停停冲很很着传传效控C、替替于于了了存储储.传.传止止1突显显送送C率制供取访访内内P器II周周在送在送信信,然然结结/的/器UOOD数内内存存和期期一的一的号号在延,,束束传发传M从、的的存存读的的批字批字给给这A缓在在后后送挥送C送方方储储控/情情数的数的CCP种了这这写的的,。,数U法法周周PP制况况据个据个情对种种UU信处处又又接等可可期期器,,。。传数传数况指DD号理理较较管操以以,,访MM要要送计送计下令等工工好好总作使使即即AA内求求完数完数I的控作作地地线/传传。DD使使O,CC毕,毕,执制,,发发的MM设送送PP高高C后并后并UU行AA寄均均挥挥控备2过过速速放放传传,且,且专,存由由了了制访程程II弃弃送送//以以DD供或器管管OO内内;内中中MM对对和和设设中中C者理理。存存优,,AAP地地CC备备断断更程程和和U控控先CCPP址址也也访方方UU明PP序序CC制制,UU总同总同PP是 是 内式式确承承器 器因UU基 基线时线时如如。向向地的的担担通通为本本、发、发此此CC说效效,,知知I处处PP/数挥数挥。。O,率率UU而而CC于于访据最据最报报PP在,,DD不不UU内总高总高告告MMC是是可可工工有AAP线的线的传传一一以以U作作控控时和效和效送送执种种使使状状制制间有率有率操操行广广用用态态器器要关。关。作作访泛泛内内或或仅仅求控控的的内采采存存者者负负,制制结结指用用,,说说责责前总总束束令的的并并保保数数一线线。。的方方把把持持据据个的的过法法总总状状传传I使使/程。。线线O送送用用数中控控

计算机组成原理第八章 第4讲 DMA方式

1、DMA基本构成

(4)“DMA请求”标志 每当设备准备好一个数据字后给出一个控制信号, 使“DMA请求” 标志置“1”。该标志置位后向“控制/状态”逻辑发 出DMA请求,后者又向CPU发出总线使用权的请求(HOLD),CPU响应 此请求后发回响应信号 HLDA,“控制/状态”逻辑接收此信号后发 出DMA响应信号,使“DMA请求”标志复位,为交换下一个字做好 准备。

8.4.1DMA方式的一般概念

DMA基本操作:

• (1)从外围设备发出DMA请求; • (2)CPU响应请求,把CPU工作改成DMA操作方式,DMA控制器从CPU接管总

线的控制; • (3)由DMA控制器对内存寻址,即决定数据传送的内存单元地址及数据传送

个数的计数,并执行数据传送的操作; • (4)向CPU报告DMA操作的结束。

8.4.3 基本DMA控制器

• 正式传送阶段:

• 由DMA控制器控制外设与主存之间的数据交换。

8.4.3 基本DMA控制器

• 正式传送阶段详解(停止CPU访问内存方式)

8.4.3 基本DMA控制器

• 传送后处理阶段:

• 第三阶段即CPU中断原程序后进行后处理。若需要继续交换数据,则又要对 DMA进行初始化;若不需要交换数据,则停止外设;若为出错,则转错误诊 断及处理程序。

8.4.1DMA方式的一般概念

• 直接存储器访问(Direct Memory Access)DMA方式是为了在主存储器与I/O 设备间高速交换批量数据而设置的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

通道的功能

8.5通道方式

➢ 通道工作过程主要分为如下三步进行:

1.在用户程序中使用访管指令进入管理程 序,由CPU通过管理程序组织一个通道 程序,并启动通道。

2.通道处理机执行CPU为它组织的通道 程序.完成指定的数据输入输出工作

8.4.2 DMA传送方式

8.4.2 DMA传送方式

8.4.2 DMA传送方式

8.4.2 DMA传送方式

8.4.3 基本DMA控制器

1、DMA基本构成

1、DMA基本构成

1、DMA基本构成

1、DMA基本构成

1、DMA基本构成

8.4.3 基本DMA控制器

2、传送过程

当外设有DMA请求时,通常CPU在本机器 周期结束后,响应DMA请求。 传送一个数据块可以分为三个阶段: -传送前预处理 -正式传送 -传送后处理

计算机组成原理第八章 第4讲 DMA方式

8.4 DMA方式

8.4.1 DMA方式的一般概念 8.4.2 DMA传送方式 8.4.3 DMA传送一个数据的过程

8.4.1DMA方式的一般概念

8.4.1DMA方式的一般概念

8.4.1DMA方式的一般概念

8.4.2 DMA传送方式

1、停止CPU访问内存。

分析

8.5 通道方式

8.5 通道方式

8.5 通道方式

8.5 通道方式

8.5 通道方式

通道的功能

➢ 基本功能是:执行通道指令,组织外围 设备和内存进行数据传输,按I/O指令要 求启动外围设备,向CPU报告中断等,具 体有以下五项任务:

(1)接受CPU的I/O指令,按指令要求与指定 的外围设备进行通信。

3.通道程序结束后向CPU发中断请求。 CPU响应这个中断请求后,第二次进入 操作系统,调用管理程序对输入输出中 断请求进行处理。

通道管理

主机响应DMA请求后,让出存储总线,直到一组数 据传送完毕后,DMA控制器才把总线控制权交还给 CPU。

采用这种工作方式的I/O设备,在其接口中一般设 置有小容量存储器,I/O设备先与小容量存储器交 换数据,然后由小容量存储器与主机交换数据,这 样可减少DMA传送占用存储总线的时间,也即减少 了CPU暂停工作的时间。

8.4.4选择型和多路型DMA控制器

8.4.4选择型和多路型DMA控制器

8.4.4选择型和多路型DMA控制器

8.4.4选择型和多路型DMA控制器

例题:

例3下图中假设有磁盘、磁带、打印机三个 设备同时工作。磁盘以30μs的间隔向控制器 发DMA请求,磁带以45μs的间隔发DMA请求, 打印机以150μs间隔发DMA请求。根据传输 速率,磁盘优先权最高,磁带次之,打印机 最低,图中假设DMA控制器每完成一次DMA 传送所需的时间是5μs。若采用多路型DMA 控制器,请画出DMA控制器服务三个设备的 工作时间图。

大家应该也有点累了,稍作休息

大家有疑问的,可以询问和交流Βιβλιοθήκη 8.4.2 DMA传送方式

8.4.2 DMA传送方式

➢ 2、周期挪用方式

➢ DMA控制器与主存储器之间传送一个数据, 占用一个内存周期,即CPU暂停访存工作 一个周期,然后继续执行程序。

8.4.2 DMA传送方式

8.4.2 DMA传送方式

8.4.3 基本DMA控制器

8.4.3 基本DMA控制器

➢ 传送后处理阶段:

第三阶段即CPU中断原程序后进行后处理。若 需要继续交换数据,则又要对DMA进行初始化; 若不需要交换数据,则停止外设;若为出错, 则转错误诊断及处理程序。

8.4.4选择型和多路型DMA控制器

8.4.4选择型和多路型DMA控制器

8.4.3 基本DMA控制器

➢ 预处理阶段:

第一阶段是进行初始化,启动设备、测试 设备。CPU通过程序I/O的方式给DMA 控制器预置初值,取状态和送传送需要的 有关参数。其中包括内存地址计数器和字 计数器的初值。

8.4.3 基本DMA控制器

➢ 正式传送阶段:

由DMA控制器控制外设与主存之间的数据交换。