计算机组成原理第2版-唐朔飞配套PPT

合集下载

计算机组成原理课后答案(第二版)唐朔飞公开课获奖课件

系统总线

第三章

第1页

1. 什么是总线? 总线传播有何特点? 为了减轻总线负载,总线上部件都应具有 什么特点?

解:总线是多种部件共享传播部件; 总线传播特点是:某一时刻只能有一 路信息在总线上传播,即分时使用; 为了减轻总线负载,总线上部件应通 过三态驱动缓冲电路与总线连通。

第2页

4. 为何要设置总线判优控制? 常见集中式总线控制有几种? 各有 何特点? 哪种方式响应时间最快?→A、D→B和D→C寄存 器间传送; (2) 设计一种电路,实现如下 操作:

T0时刻完毕D→总线; T1时刻完毕总线→A; T2时刻完毕A→总线; T3时刻完毕总线→B。

第11页

解: (1)采用三态输出D型寄存器74LS374 做A、B、C.D四个寄存器,其输出可直 接挂总线。A、B、C三个寄存器输入采 用同一脉冲打入。注意-OE为电平控制, 与打入脉冲间时间配合关系为:

16. 在异步串行传送系统中,字符 格式为: 1个起始位、8个数据位、1个 校验位、2个终止位。若规定每秒传送 120个字符,试求传送波特率和比特率。

解: 一帧 =1+8+1+2 =12位 波特率 =120帧/秒×12位

=1440波特 比特率 = 1440波特×(8/12)

=960bps 或: 比特率 = 120帧/秒×8 =960bps

解: 总线宽度 = 16位/8 =2B 总线带宽 = 8MHz×2B =16MB/s

第18页

15. 在一种32位总线系统中,总线 时钟频率为66MHz,假设总线最短传 播周期为4个时钟周期,试计算总线最 大数据传播率。若想提高数据传播率, 可采用什么措施?

解法1: 总线宽度 =32位/8 =4B 时钟周期 =1/ 66MHz =0.015µs 总线最短传播周期 =0.015µs×4

第三章

第1页

1. 什么是总线? 总线传播有何特点? 为了减轻总线负载,总线上部件都应具有 什么特点?

解:总线是多种部件共享传播部件; 总线传播特点是:某一时刻只能有一 路信息在总线上传播,即分时使用; 为了减轻总线负载,总线上部件应通 过三态驱动缓冲电路与总线连通。

第2页

4. 为何要设置总线判优控制? 常见集中式总线控制有几种? 各有 何特点? 哪种方式响应时间最快?→A、D→B和D→C寄存 器间传送; (2) 设计一种电路,实现如下 操作:

T0时刻完毕D→总线; T1时刻完毕总线→A; T2时刻完毕A→总线; T3时刻完毕总线→B。

第11页

解: (1)采用三态输出D型寄存器74LS374 做A、B、C.D四个寄存器,其输出可直 接挂总线。A、B、C三个寄存器输入采 用同一脉冲打入。注意-OE为电平控制, 与打入脉冲间时间配合关系为:

16. 在异步串行传送系统中,字符 格式为: 1个起始位、8个数据位、1个 校验位、2个终止位。若规定每秒传送 120个字符,试求传送波特率和比特率。

解: 一帧 =1+8+1+2 =12位 波特率 =120帧/秒×12位

=1440波特 比特率 = 1440波特×(8/12)

=960bps 或: 比特率 = 120帧/秒×8 =960bps

解: 总线宽度 = 16位/8 =2B 总线带宽 = 8MHz×2B =16MB/s

第18页

15. 在一种32位总线系统中,总线 时钟频率为66MHz,假设总线最短传 播周期为4个时钟周期,试计算总线最 大数据传播率。若想提高数据传播率, 可采用什么措施?

解法1: 总线宽度 =32位/8 =4B 时钟周期 =1/ 66MHz =0.015µs 总线最短传播周期 =0.015µs×4

计算机组成原理-唐朔飞(完整版)

为配合由高等教育出版社出版的面向21世纪课程教材《计算机组成原理》 教学和自学的需要,随书出版了《计算机组成原理》配套课件。为了配合该教 材的第2版,本课件在保留原课件特色的基础上,做了相应的补充和修改。

该课件与《计算机组成原理》第2版教材在体系上完全一致,它以课堂 教学为依托,帮助读者边阅读边思考,通过点击鼠标,逐行显示精练的文字和 简明的图表,既可从文稿中对教材的重点和难点加深理解,又可从视图中看到 动画演示效果,形象地理解各种电路的工作原理和设计思路。

(4)主机完成一条指令的过程

1.2

以取数指令为例

CPU

…5

存储体

ACC MQ

6

ALU

CU

IR

控制

27 3 8

I/O 设

单元 PC 1 MAR MDR

备

X

4

运算器

控制器

主存储器 9

(4)主机完成一条指令的过程

1.2

以存数指令为例

CPU

…5

存储体

ACC MQ

6

ALU

CU

IR

控制

27 Байду номын сангаас 9

I/O 设

3.SGI: SGI Altix ICE 8200

14 336个 CPU 最大平均速度 126 900 GFLOPS

最快的五台超级计算机(截止到 2007.11)2.1

4. HP : EKA - Cluster Platform 3000 BL460c

14 240个 CPU 最大平均速度 117 900 GFLOPS

MAR MDR

主存储器

存储字 存储单元中二进制代码的组合 存储字长 存储单元中二进制代码的位数

每个存储单元赋予一个地址号

该课件与《计算机组成原理》第2版教材在体系上完全一致,它以课堂 教学为依托,帮助读者边阅读边思考,通过点击鼠标,逐行显示精练的文字和 简明的图表,既可从文稿中对教材的重点和难点加深理解,又可从视图中看到 动画演示效果,形象地理解各种电路的工作原理和设计思路。

(4)主机完成一条指令的过程

1.2

以取数指令为例

CPU

…5

存储体

ACC MQ

6

ALU

CU

IR

控制

27 3 8

I/O 设

单元 PC 1 MAR MDR

备

X

4

运算器

控制器

主存储器 9

(4)主机完成一条指令的过程

1.2

以存数指令为例

CPU

…5

存储体

ACC MQ

6

ALU

CU

IR

控制

27 Байду номын сангаас 9

I/O 设

3.SGI: SGI Altix ICE 8200

14 336个 CPU 最大平均速度 126 900 GFLOPS

最快的五台超级计算机(截止到 2007.11)2.1

4. HP : EKA - Cluster Platform 3000 BL460c

14 240个 CPU 最大平均速度 117 900 GFLOPS

MAR MDR

主存储器

存储字 存储单元中二进制代码的组合 存储字长 存储单元中二进制代码的位数

每个存储单元赋予一个地址号

计算机组成原理课后习题及答案-唐朔飞(完整版)ppt课件

控制器组成。 • PC:Program Counter,程序计数器,其功能是存放当前欲执行指令的地址,并可自动计数形成下

一条指令地址。 • IR:Instruction Register,指令寄存器,其功能是存放当前正在执行的指令。 • CU:Control Unit,控制单元(部件),为控制器的核心部件,其功能是产生微操作命令序列。 • ALU:Arithmetic Logic Unit,算术逻辑运算单元,为运算器的核心部件,其功能是进行算术、逻辑

CLK: T0: T1: T2: T3: P0: P1: P2: P3:

编辑版pppt

24

返回目录

以8位总线为例,电路设计如下: (图中,A、B、C、D四个寄存器与数据总线 的连接方法同上。)

数据总线(D7~D0)

ABUS

BBUS

CBUS

DBUS

1Q OE

374 8Q

1D A 8D

1Q 374 8Q

编辑版pppt

14

8. 为什么说半同步通信 同时保留了同步通信和异步 通信的特点?

解: 半同步通信既能像同步

通信那样由统一时钟控制, 又能像异步通信那样允许传 输时间不一致,因此工作效 率介于两者之间。

编辑版pppt

15

10. 什么是总线标准?为什么要设

置总线标准?目前流行的总线标准有哪些? 什么是即插即用?哪些总线有这一特点?

• 解:P9-10 • 主机:是计算机硬件的主体部分,由CPU和主存储器MM合成为主机。 • CPU:中央处理器,是计算机硬件的核心部件,由运算器和控制器组成;(早期的运

算器和控制器不在同一芯片上,现在的CPU内除含有运算器和控制器外还集成了 CACHE)。 • 主存:计算机中存放正在运行的程序和数据的存储器,为计算机的主要工作存储器, 可随机存取;由存储体、各种逻辑部件及控制电路组成。

一条指令地址。 • IR:Instruction Register,指令寄存器,其功能是存放当前正在执行的指令。 • CU:Control Unit,控制单元(部件),为控制器的核心部件,其功能是产生微操作命令序列。 • ALU:Arithmetic Logic Unit,算术逻辑运算单元,为运算器的核心部件,其功能是进行算术、逻辑

CLK: T0: T1: T2: T3: P0: P1: P2: P3:

编辑版pppt

24

返回目录

以8位总线为例,电路设计如下: (图中,A、B、C、D四个寄存器与数据总线 的连接方法同上。)

数据总线(D7~D0)

ABUS

BBUS

CBUS

DBUS

1Q OE

374 8Q

1D A 8D

1Q 374 8Q

编辑版pppt

14

8. 为什么说半同步通信 同时保留了同步通信和异步 通信的特点?

解: 半同步通信既能像同步

通信那样由统一时钟控制, 又能像异步通信那样允许传 输时间不一致,因此工作效 率介于两者之间。

编辑版pppt

15

10. 什么是总线标准?为什么要设

置总线标准?目前流行的总线标准有哪些? 什么是即插即用?哪些总线有这一特点?

• 解:P9-10 • 主机:是计算机硬件的主体部分,由CPU和主存储器MM合成为主机。 • CPU:中央处理器,是计算机硬件的核心部件,由运算器和控制器组成;(早期的运

算器和控制器不在同一芯片上,现在的CPU内除含有运算器和控制器外还集成了 CACHE)。 • 主存:计算机中存放正在运行的程序和数据的存储器,为计算机的主要工作存储器, 可随机存取;由存储体、各种逻辑部件及控制电路组成。

《计算机组成原理》唐朔飞 重点、难点课件

如 16 MB (227位)的存储器

寻址范围

按 字节 寻址 按 字(16位)寻址 按 字 (32位)寻址

224= 16 M 223 = 8 M 222 = 4 M

字节 寻址 字(16位)寻址

24 位 23 位

22 位

字 (32位)寻址

容量 224 × 23 = 227位 223 × 24 = 227位 222 × 25 = 227位

字块2m-1

某一主存块 j 按模 Q 映射到 缓存 的第 i 组中的 任一块

例 假设主存容量为 512 KB,Cache 容量为 4KB,每个字块为

16 个字,每个字 32 位。 (1)Cache 地址有多少位?可容纳多少块?

根据 Cache 容量为 4KB 得 Cache 地址 12 位 4KB/4B = 1K字 1K/16 = 64 块 (2)主存地址有多少位?可容纳多少块? 根据 512KB 得主存地址 19 位 512KB/4B = 128K字 128K/16 = 8192 块。 (3)在直接映射方式下,主存的第几块映射到 Cache 中的第 5 块(设起始字块为第 1 块)? 主存的第 5,64 + 5,2×64 + 5, … , 8192 – 64 + 5 块 能映射到 Cache 的第 5 块

第1章 计算机系统概论

计算机

第1篇 概论

第1章 计算机系统概论

计算机

存储器 I/O

系统总线

第2篇 计算机系统的硬件结构

CPU

第1章 计算机系统概论

计算机

存储器 I/O

第3篇 CPU

系统总线

CPU

中央处理器

ALU CU

CPU 内部互连

计算机组成原理课后答案第二版唐朔飞第九章省公共课一等奖全国赛课获奖课件

第12页

11. 设CPU内部结构如图9.4所表 示,另外还设有B、C、D、E、H、L 六个存放器,它们各自输入和输出端 都与内部总线相通,并分别受控制信 号控制(如Bi为存放器B输入控制;Bo 为存放器B输出控制)。要求从取指 令开始,写出完成以下指令所需全部 微操作和控制信号。 (1)ADD B,C;((B)+(C) B) (2)SUB A,H;((AC)-(H) AC)

第27页

14. 设单总线计算机结构如图9.5所表示,其中 M为主存,XR为变址存放器,EAR为有效地址 存放器,LATCH为锁存器。假设指令地址已存 于PC中,画出“LDA * D”和“SUB D(XR)”指 令周期信息流程图,并列出对应控制信号序列。

说明:

(1) “LDA * D”指令字中*表示相对寻址, D为相对位移量。

(AC)–(H)Z

ZAC

Ho,Yi ACo,ALUi,– Zo,ACi

第18页

12. CPU结构同上题,写出完成 以下指令所需全部微操作和控制信号 (包含取指令)。

(1)存放器间接寻址无条件转移 指令“JMP @ B”。

(2)间接寻址存数指令“STA @ X”。

解:解题方法步骤同上题。 (1) “JMP @ B”指令流程图和 全部微操作控制信号以下:

第2页

4. 能不能说CPU主频越快,计算 机运行速度就越快?为何?

解:不能说机器主频越快,机器 速度就越快。因为机器速度不但与主 频相关,还与数据通路结构、时序分 配方案、ALU运算能力、指令功效强 弱等各种原因相关,要看综合效果。

第3页

5. 设机器ACPU主频为8MHz,机 器周期含4个时钟周期,且该机平均指 令执行速度是0.4MIPS,试求该机平均 指令周期和机器周期,每个指令周期 中含几个机器周期?假如机器BCPU主 频为12MHz,且机器周期也含4个时钟 周期,试问B机平均指令执行速度为多 少MIPS?

11. 设CPU内部结构如图9.4所表 示,另外还设有B、C、D、E、H、L 六个存放器,它们各自输入和输出端 都与内部总线相通,并分别受控制信 号控制(如Bi为存放器B输入控制;Bo 为存放器B输出控制)。要求从取指 令开始,写出完成以下指令所需全部 微操作和控制信号。 (1)ADD B,C;((B)+(C) B) (2)SUB A,H;((AC)-(H) AC)

第27页

14. 设单总线计算机结构如图9.5所表示,其中 M为主存,XR为变址存放器,EAR为有效地址 存放器,LATCH为锁存器。假设指令地址已存 于PC中,画出“LDA * D”和“SUB D(XR)”指 令周期信息流程图,并列出对应控制信号序列。

说明:

(1) “LDA * D”指令字中*表示相对寻址, D为相对位移量。

(AC)–(H)Z

ZAC

Ho,Yi ACo,ALUi,– Zo,ACi

第18页

12. CPU结构同上题,写出完成 以下指令所需全部微操作和控制信号 (包含取指令)。

(1)存放器间接寻址无条件转移 指令“JMP @ B”。

(2)间接寻址存数指令“STA @ X”。

解:解题方法步骤同上题。 (1) “JMP @ B”指令流程图和 全部微操作控制信号以下:

第2页

4. 能不能说CPU主频越快,计算 机运行速度就越快?为何?

解:不能说机器主频越快,机器 速度就越快。因为机器速度不但与主 频相关,还与数据通路结构、时序分 配方案、ALU运算能力、指令功效强 弱等各种原因相关,要看综合效果。

第3页

5. 设机器ACPU主频为8MHz,机 器周期含4个时钟周期,且该机平均指 令执行速度是0.4MIPS,试求该机平均 指令周期和机器周期,每个指令周期 中含几个机器周期?假如机器BCPU主 频为12MHz,且机器周期也含4个时钟 周期,试问B机平均指令执行速度为多 少MIPS?

计算机组成原理唐朔飞PPT 第4章 存储器

三、随机存取存储器

(2) 静态 RAM 芯片举例

CS I/O 1 I/O 2 I/O 3 I/O 4 存储容量 1K×4 位

Intel 2114

A0

…

VCC

GND

② Intel 2114 RAM 矩阵 (64 × 64) 读

A8

A7 A6 行 地 第一组

0

第二组 16

第三组 32

第四组 48

0

… 15

0 0 行 第一组

0

第二组 16

第三组 32

第四组 48

0 地 1 0 址

0

… 15

…

… 31

…

… 47

…

… 63

…

…

0 译 0 码 63

0 列 0 0 地 0 址 15 0 译 码

… …

WE

…

…

0

…

16

15

31

32

47

48

63

读写电路

I/O1

读写电路

I/O2

读写电路

I/O3

读写电路

I/O4

CS

② Intel 2114 RAM 矩阵 (64 × 64) 读

址 15 译 码

WE

… …

CS

…

…

…

读写电路

I/O1

读写电路

I/O2

读写电路

I/O3

读写电路

I/O4

③ Intel 2114 RAM 矩阵 (64 × 64) 写

0 0 行 第一组

0

第二组 16

第三组 32

第四组 48

0 地 1 0 址

0

… 15

计算机组成原理(唐朔飞)系统总线68页PPT

谢谢!

68

计算机组成原理(唐朔飞)系统总线

16、云无心以出岫,鸟倦飞而知还。 17、童孺纵行歌,斑白欢游诣。 18、福不虚至,祸不易来。 19、久在樊笼里,复得返自然。 20、羁鸟恋旧林,池鱼思故渊。

▪

26、要使整个人生都过得舒适、愉快,这是不可能的,因为人类必须具备一种能应付逆境的态度。——卢梭

▪

27、只有把抱怨环境的心情,化为上进的力量,才是成功的保证。——罗曼·罗兰

▪

28、知之者不如好之者,好之者不如乐之者。——孔子

▪

29、勇猛、大胆和坚定的决心能够抵得上武器的精良。——达·芬奇

▪

30、意志是一个强壮的盲人,倚靠在明眼的跛子肩上。——叔本华

计算机组成原理(唐朔飞)CPU结构和功能 PPT

指令1、指令3、 指令 1 与指令 指令存储器和数据存储器分开 6 冲突 指令 、指令 、指令 解决办法 4• 冲突 …… 指令 2 与指令 5 冲突

• 指令预取技术 (适用于访存周期短的情况) 适用于访存周期短的情况)

《计算机组成原理》 计算机组成原理》

2、 控制相关 程序的相近指令之间出现某种关联 、

解决办法 ?

4. 指令的六级流水

t 1

指令 1 指令 2 指令 3 指令 4 指令 5 指令 6 指令 7 指令 8 指令 9 FI

《计算机组成原理》 计算机组成原理》

取指、指令译码、算操作数地址、取操作数、执行指令、 取指、指令译码、算操作数地址、取操作数、执行指令、写操作数

2

DI FI

3

CO DI FI

IF ID EX WR

流水线速度是原来速度的 3 倍

0

1

2

3

4

5

6

7

8

9

10 11

12 13

t

3. 超长指令字

《计算机组成原理》 计算机组成原理》

并行性, 由编译程序 挖掘 出指令间 潜在 的 并行性,将 多条 一条具有 能 并行操作 的指令组合成 一条具有 多个操作码字段 的 超长指令字(可达几百位) 超长指令字(可达几百位) 多个处理部件(EX部件 部件) 采用 多个处理部件 部件

组合逻辑设计 微程序设计 硬连线逻辑

参见 第四篇

存储逻辑

参见 8.4 参见 第六章

2. 中断系统

五、ALU

《计算机组成原理》 计算机组成原理》

8.2 指 令 周 期

一、 指令周期的基本概念

1 . 指令周期 取出并执行一条指令所需的全部时间 指令周期:

最新计算机组成原理课后答案(第二版)-唐朔飞-第六章PPT课件

解:(1)阶码基值不论取何值, 在浮点数中均为隐含表示,即:2和 16不出现在浮点格式中,仅为人为的 约定。

(2)当基值不同时,对数的表示范围和精度 都有影响。即:在浮点格式不变的情况下,基越 大,可表示的浮点数范围越大,但精度越下降。

(3)r=2时,最大正数的浮点格式为: 0,1111;0.111 111 111 1 其真值为:N+max=215×(1-2-10) 非零最小规格化正数浮点格式为:

=23 (0.111 011)2 x4= -86.5=(-1 010 110.1)2

=27 (-0.101 011 01)2 则以上各数的浮点规格化数为: (1)[x1]浮=1,0001;0.110 011 000 0 (2)[x1]浮=1,1111;0.110 011 000 0 (3)[x1]浮=0,1111;0.110 011 000 0

解:[x]补与[x]原、x的对应关系如下:

[x]补 1.1100

[x]原 1.0100

x(二进制) x(十进制)

-0.0100

-1/4

1.1001

1.0111

-0.0111

-7/16

0.1110

0.1110

+0.1110

+7/8

1.0000

无

-1.0000

-1

1,0101

1,1011

-1011

-11

号位为1,则[x]补<[y]补。同样,当x<0、 y >0时,有x < y,但[x]补>[y]补。

注意: 1)绝对值小的负数其值反而大,且负

数的绝对值越小,其补码值越大。因此, 当x<0、y<0时,若[x]补>[y]补,必有 x>y。

(2)当基值不同时,对数的表示范围和精度 都有影响。即:在浮点格式不变的情况下,基越 大,可表示的浮点数范围越大,但精度越下降。

(3)r=2时,最大正数的浮点格式为: 0,1111;0.111 111 111 1 其真值为:N+max=215×(1-2-10) 非零最小规格化正数浮点格式为:

=23 (0.111 011)2 x4= -86.5=(-1 010 110.1)2

=27 (-0.101 011 01)2 则以上各数的浮点规格化数为: (1)[x1]浮=1,0001;0.110 011 000 0 (2)[x1]浮=1,1111;0.110 011 000 0 (3)[x1]浮=0,1111;0.110 011 000 0

解:[x]补与[x]原、x的对应关系如下:

[x]补 1.1100

[x]原 1.0100

x(二进制) x(十进制)

-0.0100

-1/4

1.1001

1.0111

-0.0111

-7/16

0.1110

0.1110

+0.1110

+7/8

1.0000

无

-1.0000

-1

1,0101

1,1011

-1011

-11

号位为1,则[x]补<[y]补。同样,当x<0、 y >0时,有x < y,但[x]补>[y]补。

注意: 1)绝对值小的负数其值反而大,且负

数的绝对值越小,其补码值越大。因此, 当x<0、y<0时,若[x]补>[y]补,必有 x>y。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2. 计算机的解题过程

1.1

高级语 言程序

翻译

目标

程序

运行

结果

计算机

二、计算机系统的层次结构

高级语言

汇编语言 操作系统 机器语言

虚拟机器 M3

虚拟机器 M2 虚拟机器 实际机器 M1

1.1

微指令系统

微程序机器 M0

虚拟机器 M4 虚拟机器 M3

用编译程序翻译 成汇编语言程序

1.1

软 件

用汇编程序翻译 成机器语言程序

3.SGI: SGI Altix ICE 8200

14 336个 CPU

最大平均速度 126 900 GFLOPS

最快的五台超级计算机(截止到 2007.11) 2.1

4. HP : EKA - Cluster Platform 3000 BL460c

14 240个 CPU

最大平均速度 117 900 GFLOPS

X MQ

[ACC]÷[X]

余数在ACC中

(3)控制器的基本组成

完成 一条 指令

PC

1.2

PC

IR

取指令

分析指令

取指 访存

CU

执行指令

CU

执行 访存

IR

PC 存放当前欲执行指令的地址, 具有计数功能(PC)+ 1 PC IR 存放当前欲执行的指令

(4)主机完成一条指令的过程

以取数指令为例 CPU

…

MQ

初态 ACC [M] [ACC]-[X]

被减数

X ACC

③ 乘法操作过程

0 ACC ALU ALU X

运算器

1.2

指令

初态 乘 M

MQ

ACC

[M] [ACC]

被乘数

MQ X

0

[X]×[MQ]

ACC

ACC∥MQ

④ 除法操作过程

ACC ALU X

运算器

1.2

指令

初态 除 M

MQ

ACC

[M]

被除数

1.2

加b得ax+b ,存于ACC中 乘x得(ax+b)x,存于ACC中

4

5 6

000011

000010 000101

0000001011

0000001100 0000001100 x a b c

加c得ax2 + bx + c ,存于ACC

将ax2 + bx +c ,存于主存单元 打印

7

8 9 10 11 12

212 992 个 CPU

最大平均速度 478 200 GFLOPS

最快的五台超级计算机(截止到 2007.11) 2.1

2.IBM: JUGENE - Blue Gene/P Solution

65 536个 CPU

最大平均速度 167 300 GFLOPS

最快的五台超级计算机(截止到 2007.11) 2.1

200 000 1 000 000

四

五

10 000 000 100 000 000

1978-现在

2.1 第一台von Neumann 系统结构的计算机

IBM System/360

2.1

最快的五台超级计算机(截止到 2007.11) 2.1

1. IBM: BlueGene/L - eServer Blue Gene Solution

由于时间仓促,难免有不妥之处,敬请读者和专家批评指正。

唐朔飞

2007年12月

参考资料

白中英 《计算机组成原理》 立体化教 材 第四版 唐朔飞 《计算机组成原理:学习指导与 习题解答》 高教出版社 王诚 《计算机组成原理考研辅导》,清 华出版社

第1章 计算机系统概论 第1篇 概论

第2章 计算机的发展及应用

1.4 本书结构

1.1 计算机系统简介

一、 计算机的软硬件概念

1. 计算机系统

计 算 机 系 统 硬件 计算机的实体, 如主机、外设等 软件 由具有各类特殊功能 的信息(程序)组成

1.1

系统软件 用来管理整个计算机系统

语言处理程序

操作系统 服务性程序

软 件

数据库管理系统

网络软件

应用软件 按任务需要编制成的各种程序

1.机器字长 CPU 一次能处理数据的位数

主频 吉普森法 TM = fi ti

i =1

与 CPU 中的 寄存器位数 有关

n

2.运算速度

MIPS CPI

每秒执行百万条指令

执行一条指令所需时钟周期数

FLOPS 每秒浮点运算次数

3.存储容量

存放二进制信息的总位数 存储单元个数 ×存储字长 如

1.3

主存容量

ACC

ALU

MQ

加法 被加数 和 被减数 减法 差 乘数 乘法 乘积高位 乘积低位 被除数 除法 余数 商

X

运算器

被乘数

除数

① 加法操作过程

ACC ALU X

运算器

1.2

指令

加 M

MQ

初态 ACC [M] [ACC]+[X]

被加数

X ACC

② 减法操作过程

ACC ALU X

运算器

1.2

指令

减 M

字节数 如 字节数

MAR MDR 容量 10 8 1 K × 8位 16 32 64 K × 32位

1K = 210

2 = 1 KB 221 = 256 KB 80 GB

13

1B = 23b

辅存容量

1GB = 230b

1.4 本书结构

计算机

第1篇 概论

1.4 本书结构

计算机

存储器

I/O

第2篇 计算机系统的硬件结构

ACC MQ

Байду номын сангаас

1.2

5

存储体

6

IR 27 3 8

MDR

I/O 设 备

CU

ALU

控制 单元

PC

1

4

MAR

X

运算器

控制器

9

主存储器

(4)主机完成一条指令的过程

以存数指令为例 CPU

…

ACC MQ

1.2

5

存储体

6

IR 27 3 9

MDR

I/O 设 备

CU

ALU

控制 单元

PC

1

4

MAR

X

运算器

控制器

8

主存储器

计算机组成原理

第2版

唐朔飞

高 等 教 育 出 版 社 高等教育电子音像出版社

为配合由高等教育出版社出版的面向21世纪课程教材《计算机组成原理》 教学和自学的需要,随书出版了《计算机组成原理》配套课件。为了配合该教 材的第2版,本课件在保留原课件特色的基础上,做了相应的补充和修改。 该课件与《计算机组成原理》第2版教材在体系上完全一致,它以课堂教 学为依托,帮助读者边阅读边思考,通过点击鼠标,逐行显示精练的文字和简 明的图表,既可从文稿中对教材的重点和难点加深理解,又可从视图中看到动 画演示效果,形象地理解各种电路的工作原理和设计思路。

第3章 系统总线 第4章 存储器

第2篇 硬件结构

第5章 输入输出系统

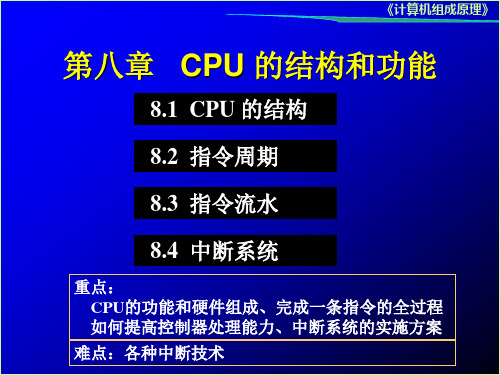

第6章 计算机的运算方法 第3篇 中央处理器 第7章 指令系统 第8章 CPU 的结构和功能

第9章 控制单元的功能

第4篇 控制单元 第10章 控制单元的设计

第1章 计算机系统概论

1.1 计算机系统简介 1.2 计算机的基本组成

1.3 计算机硬件的主要技术指标

最快的五台超级计算机(截止到 2007.11) 2.1

5. HP : Cluster Platform 3000 BL460c

13 728个 CPU

最大平均速度 102 800 GFLOPS

2.1

最权威的超级计算机排名的参考网址

Rank

1

Site

Top 10

乘以a 在运算器中 乘以x 在运算器中

指令格式举例

操作码 取数 000001 存数 加 α 0000001000 β γ [ACC] [ACC]+[γ] β 地址码 [α]

1.2

ACC

ACC

乘

打印

δ

[ACC]×[δ]

[ ]

ACC

打印机

停机

计算 ax2 + bx + c 程序清单

指令和数据存于 主存单元的地址 0 1 2 3 指令 操作码 000001 000100 000011 000100 地址码 0000001000 0000001001 0000001010 0000001000 注释 取数x至ACC 乘a得ax ,存于ACC中

2.1 计算机的发展史 2.2 计算机的应用 2.3 计算机的展望

2.1 计算机的发展史

一、计算机的产生和发展

1946年 美国 ENIAC

十进制运算

1955年退役

18 000

1 500 150 30 1 500 5 000

多个电子管

多个继电器

千瓦 吨

平方英尺

次加法/秒

用手工搬动开关和拔插电缆来编程

新版课件提供了章目录和节目录。操作上除了顺序播放外,还可任选一章、

任选一节播放,并可从任意一页幻灯片返回到上一级目录。具体功能如下。

1. 进入章目录后,可点击任一章播放。

2. 进入节目录后,可点击任一节播放。

3. 每一节播放结束时,可继续播放,也可点击本节最后一页幻灯片右下 角的按钮,回到上一级目录,再点击节目录幻灯片右下角的按钮,即可回到 章目录。 4. 点击任一页幻灯片右下角的按钮,均可回到上一级目录。 在修改课件过程中,哈尔滨工业大学计算机科学与技术学院张丽杰、罗 丹彦为课件的录入、排版、绘图、动画演示做了大量工作,在此表示衷心感 谢。