轨对轨运放的含义

什么是运放它的作用是什么

什么是运放它的作用是什么运放,即运算放大器(Operational Amplifier),是一种基础的电子器件,具备高度放大和线性特性。

它通常被广泛应用于模拟电路中,具有多种功能和作用。

一、什么是运放运放是一种电子增益器,其内部由大量的晶体管及其他电子元件构成。

它具有两个输入端(非反馈输入端和反馈输入端)和一个输出端。

运放的主要功能是将输入信号经过放大处理,并在输出端输出增大的信号。

二、运放的作用1. 放大器功能:运放作为电压放大器,它能够将输入信号放大到需要的幅度,使得输入信号能够适应后续电路的工作要求。

2. 比较器功能:运放可以将输入信号与参考电平进行比较,判断输入信号是大于还是小于参考电平,并在输出端产生一个高或低电平,用于开关电路的驱动。

3. 滤波器功能:运放通过设置合适的电路结构,可以实现对输入信号的滤波功能,将特定频率范围的信号通过,同时将其他频率的信号削弱或抑制。

4. 电压源功能:运放可以将电源电压通过稳压电路转化为一定稳定的直流电压,在电子电路中起到供电的作用,保证电路的正常工作。

5. 多种数学运算:运放可以通过负反馈电路实现加法、减法、乘法和除法等数学运算,常被应用于模拟计算器和信号处理等领域。

6. 模拟信号处理功能:运放可以将模拟信号加以处理,如放大、多路切换、调节增益、相移等操作,从而满足不同应用中的信号要求。

7. 模拟电平转换:运放可以将信号由低电平转换为高电平或由高电平转换为低电平,实现信号的匹配和适配。

8. 反馈控制功能:运放通过反馈电路来控制放大倍数和频率响应,保证整个电路的稳定性和可靠性。

总之,运放作为一种重要的电子器件,具有广泛的应用范围。

在各种电子电路中,运放能够实现信号的放大、滤波、开关、数学运算和模拟处理等多种功能,为电路的正常工作和信号处理提供了便利。

在日常生活和科技发展中,我们经常能够见到运放的身影,例如音频放大器、仪器测量设备、通信设备等。

随着技术的不断进步,运放的应用也将变得越来越广泛。

运算放大器工作原理是什么?

运算放大器工作原理是什么?运算放大器简称运放,由于早期应用于模拟计算机中,用以实现数学运算,故得名“运算放大器”。

主要是用在模拟电路中,比如放大器、比较器、模拟运算器,是电子工程师经常要用到的器件。

运算放大器是具有很高放大倍数的电路单元。

在实际电路中,通常结合反馈网络共同组成某种功能模块。

它是一种带有特殊耦合电路及反馈的放大器。

其输出信号可以是输入信号加、减或微分、积分等数学运算的结果。

运放是一个从功能的角度命名的电路单元,可以由分立的器件实现,也可以实现在半导体芯片当中。

而随着半导体技术的发展,大部分的运放是以单芯片的形式存在。

运放的种类繁多,广泛应用于电子行业当中。

要想更好用好运放,透彻地了解运算放大器工作原理是必须的。

一、运算放大器工作原理是什么?运算放大器(OperaTIonal Amplifier,简称OP、OPA、OPAMP)是一种直流耦合﹐差模(差动模式)输入、通常为单端输出(DifferenTIal-in, single-ended output)的高增益(gain)电压放大器,因为刚开始主要用于加法,乘法等运算电路中,因而得名。

一个理想的运算放大器必须具备下列特性:无限大的输入阻抗、等于零的输出阻抗、无限大的开回路增益、无限大的共模排斥比的部分、无限大的频宽。

最基本的运算放大器如图1-1。

一个运算放大器模组一般包括一个正输入端(OP_P)、一个负输入端(OP_N)和一个输出端(OP_O)。

最基本的运算放大器通常使用运算放大器时,会将其输出端与其反相输入端(inverTIng input node)连接,形成一负反馈(negaTIve feedback)组态。

原因是运算放大器的电压增益非常大,范围从数百至数万倍不等,使用负反馈方可保证电路的稳定运作。

但是这并不代表运算放大器不能连接成正回馈(positive feedback),相反地,在很多需要产生震荡讯号的系统中,正回馈组态的运算放大器是很常见的组成元件。

轨至轨运放的介绍

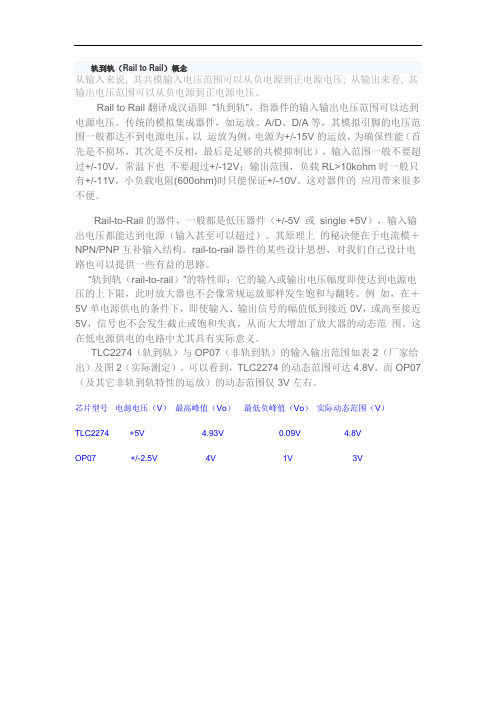

轨至轨(rail to rail)概念(2009-11-25 09:14:28)转载▼分类:电子标签:杂谈从输入来说, 其共模输入电压范围可以从负电源到正电源电压; 从输出来看, 其输出电压范围可以从负电源到正电源电压。

Rail to Rail翻译成汉语即“轨到轨”,指器件的输入输出电压范围可以达到电源电压。

传统的模拟集成器件,如运放、A/D、D/A等,其模拟引脚的电压范围一般都达不到电源电压,以运放为例,电源为+/-15V的运放,为确保性能(首先是不损坏,其次是不反相,最后是足够的共模抑制比),输入范围一般不要超过+/-10V,常温下也不要超过+/-12V;输出范围,负载RL>10kohm时一般只有+/-11V,小负载电阻(600ohm)时只能保证+/-10V。

这对器件的应用带来很多不便。

Rail-to-Rail的器件,一般都是低压器件(+/-5V 或 single +5V),输入输出电压都能达到电源(输入甚至可以超过)。

其原理上的秘诀便在于电流模+NPN/PNP互补输入结构。

rail-to-rail器件的某些设计思想,对我们自己设计电路也可以提供一些有益的思路。

“轨到轨(rail-to-rail)”的特性即:它的输入或输出电压幅度即使达到电源电压的上下限,此时放大器也不会像常规运放那样发生饱和与翻转。

例如,在+5V单电源供电的条件下,即使输入、输出信号的幅值低到接近0V,或高至接近5V,信号也不会发生截止或饱和失真,从而大大增加了放大器的动态范围。

这在低电源供电的电路中尤其具有实际意义。

TLC2274(轨到轨)与OP07(非轨到轨)的输入输出范围如表2(厂家给出)及图2(实际测定)。

可以看到,TLC2274的动态范围可达4.8V,而OP07(及其它非轨到轨特性的运放)的动态范围仅3V左右。

轨至轨(rail to rail) 运放有一类特殊的放大器具有非常低的端边占用电压(headroom)要求,称之谓输出摆幅与供电电压相同(轨至轨rail to rail)放大器。

轨对轨运放的含义

随着单电源运放的广泛的运用,运放的轨至轨输入rail to rail input成为一个时髦的词;现在大部分低电压单电源供电的运放都是轨至轨输入的;TI在轨至轨输入的运放产品方面具有十分领先的优势;本文介绍运放的rail to rail输入的实现以及TI在实现运放的rail to rail 输入方面的领先技术;先说两句废话,解释一下轨至轨,这里的轨指的是电源轨,运放的两个电源供电电压如+/-15V;这两个电源电压就像两条平行的距离为30V的“轨道”一样限制了运放的输入输出信号;运放的轨至轨输入是指运放的输入端信号电压能够达到电源的两个轨,并保持不失真,如上例输入信号电压可达到+/-15V;运放的输入电压范围可在运放的datasheet中找到;就是共模电压范围VcmCommon-Mode Voltage Range;如下表即为OPA365的输入电压范围,可见它是典型的轨至轨输入运放;一般的BJT和JFET是非轨至轨输入的运放;如下表所示为OPA827共模输入电压范围为V-+3V至V+-3V,典型的非轨至轨运放;单电源我们暂且称之为“单电源”运放的输入级通常有三种结构,第一种是采用PMOS 做差分输入级;这样的运入输入级电压可以低于负电源轨甚至,但达不到正电源轨,如OPA336;下表是datasheet中标出的OPA336输入电压范围;它的输入级原理框图如下图,典型的PMOS差分输入级;既然PMOS差分输入级输入电压不能达到正电源轨,那NMOS呢,对头,NMOS差分输入级的输入电压可以达到正电源轨,但是达不到负电源轨,一般会在负电源轨的之上;此时有人想到了,把PMOS和NMOS差分输入级并联起来;在接近电源负电压轨时使PMOS 差分输入级工作,在接近电源正电源轨时使NMOS差分输入级工作;这样不就可以实现运放的轨至轨输入了嘛;太巧妙了;的确早先的轨至轨输入运放就是这样设计的;并且现在也在大量使用这种技术;如下图是OPA703的输入级,就是典型的PMOS与NMOS相并联的运放输入级;当输入共模电压在Vss-<Vcm<Vss+-2V时PMOS处于工作状态,NMOS处于关闭状态;当输入共模电压在Vss--2V<Vcm<Vss++时NMOS处于工作状态,PMOS处于关闭状态;下表是OPA703的datasheet中给出的共模电压输入范围V-至V++.Bipolar输入级运入同样也有这样的结构,如下图是典型PNP与NPN型三级管并联形成的差分输入级;。

轨到轨CMOS运算放大器的研究与设计

重废邮虫盍堂亟±论塞簋三童熟到魍£MQS运簋趑太墨的县佳遮让第三章轨到轨CMOS运算放大器的具体设计运放的输入电位通常要求高于负电源某一数值,而低于正电源某一数值。

经过特殊设计的运放可以允许输入电位在从负电源到正电源的整个区间变化,甚至稍微高于正电源或稍微低于负电源也可以。

这种运放称为轨到轨(Rail—to—Rail)输入运算放大器。

3.1轨到轨运放的输入级设计3.1.1传统的输入级设计通过对差分放大器的直流性质研究我们发现,NMOS差分对管的输入共模电压可以达到电源电压%仃,同时可得PMOS差分对管的共模输入电压可以无限制的接近地电压,上面的直流工作点都可以通过对管子的器件特性的选择来选定。

但是无论如何我们不可能让NMOS差分对管的共模电压接近于地电压,同理,我们也不能让PMOS差分对管的共模电压接近于电源电压%D,这些是因为器件本身的性质决定的。

于是我们不可能通过只选择其中的任何一个类型的管子而实现共模输入电压达到轨到轨的要求。

然而我们通过上面的分析可以发现,假如两种类型的管子配合着相互使用,于是问题则可以迎刃而解。

如此输入级的共模输入电压范围就可达到运放对输入级电路轨到轨的要求。

通过上面的分析我们得到互补式运算放大器的差分输入电路结构如图3.1所示。

从下图中我们得出:当只有N/dOS差分对导通的时候,N/dOS差分对管Ml,M2的输入共模范围为‰一%+‰;当只有PMOS差分对管处于导通状态的时候,M3,M4作为输入级其共模的输入范围为‰一K,。

+‰;通过上面的分析我们知道两种差分对管实现了优缺点的互补,我们就完成了共模输入电压范围扩大的目的,此时为坎。

~%。

,如此一来轨到轨输入级结构的大体思路已经成行,我们同时可以计算出可以使这对差分对管正常工作的最小的电源电压,其电压值大小是:‰nlin=‰+‰+2‰。

上面的式子中‰,%分别是PMOS晶体管和NMos晶体管的栅源电压;‰是16尾电流管的饱和电压,这里尾电流管子是采用电流镜技术。

常见问答-轨到轨输出运算放大器具备哪些优势

常见问答轨到轨输出运算放大器具备哪些优势?John ArdizzoniAnalog Devices Inc.在低电源电压应用中,无论是使用单电源,或是低电压双极性电源,放大器的输入范围和输出摆幅都有一定的限制,有限的输入范围和受限的输出摆幅都会减小放大器的动态范围。

轨到轨放大器不仅有助于扩展这个动态范围,而且还能提高性能。

放大器通常采用射极跟随器(源跟随器)或共发射极(共源极)输出级电路。

射极跟随器可提供较低的失真,但输出摆幅也较小,这是因为输出级晶体管需要在线性区域工作,这样会使输出摆幅减小约1V。

轨到轨输出放大器一般采用共射极或共源极输出电路,虽然这种输出电路无法提供像射极跟随器那么好的性能,但它能提供更宽的摆幅。

轨到轨输出的摆幅能够非常接近电源轨,但由于晶体管上有一定的压降,所以也不能完全达到轨电压,不过两者的差值在几毫伏之内。

场效应管(FET)输入运算放大器能带来什么好处?FET输入的运算放大器具备几个优势。

由于它具有极低的输入偏置电流,通常在pA范围内,因而对输入电路产生的负载也极低,这样就可使用大的源电阻,而不会引入明显的失调电压误差(大小为输入偏置电流与源电阻的乘积)。

由于输入偏置电流如此之低,因此将运算放大器用于反相配置时,就没有必要补偿输入失调电压误差。

在这种配置中,补偿放大器的一种常用方法是采用一个电阻将同相输入端连接到地,该电阻的阻值是反馈和增益设置电阻的并联组合,但现在由于电流很低,这里也不再需要此电阻,因此简化了电路。

FET输入运算放大器的一种常见应用就是在光电二极管检测器应用中作为电流-电压转换器(I-V转换器)。

在这些应用中,光电二极管的电流非常小,因此强制要求所用运算放大器必须具备极低的输入偏置电流,这样才能确保所有的光电二极管电流都通过反馈电阻(产生输出电压),而不是进入运算放大器中,否则将会在运算放大器电流-电压转换器的预期输出电压中引入误差。

放大器输出阻抗和输出驱动能力如何影响系统性能?低输出阻抗之所以重要是有多方面的原因。

轨对轨运放 cascode补偿

轨对轨运放cascode补偿

轨对轨运放(Rail-to-Rail Operational Amplifier,RR-OPAMP)是一种运放,其输入和输出的电压范围可以覆盖整个供电电压范围。

传统的运放,输入和输出电压范围受限于供电电压范围,因此在输入和输出靠近供电电压边界时,会造成截断失真。

轨对轨运放采用了一种特殊的电路结构,使得其输入和输出能够达到供电电压边界。

它通常使用增加电源轨极的技术,将两个差分输入级放置在输入信号的正负两侧,以确保输入信号可以驱动差分放大器。

而cascode补偿则是一种用于减小RR-OPAMP中的晶体管工作点漂移和增加增益带宽积的技术。

它通过在RR-OPAMP的输入级和差分对输出级之间插入一个额外的cascode级,将cascode晶体管的基极电压稳定在一个固定的值上。

这样可以大大减小晶体管工作点电流对工作状态和增益的影响,并提高运放的线性度和带宽。

总的来说,轨对轨运放结合cascode补偿技术,能够提供更大的输入和输出电压范围,并减小非线性失真和频率响应损失。

这使得它在需要处理接近供电边界的信号时,具有优势。

轨到轨运放知识介绍

普通运放和轨到轨运放区别

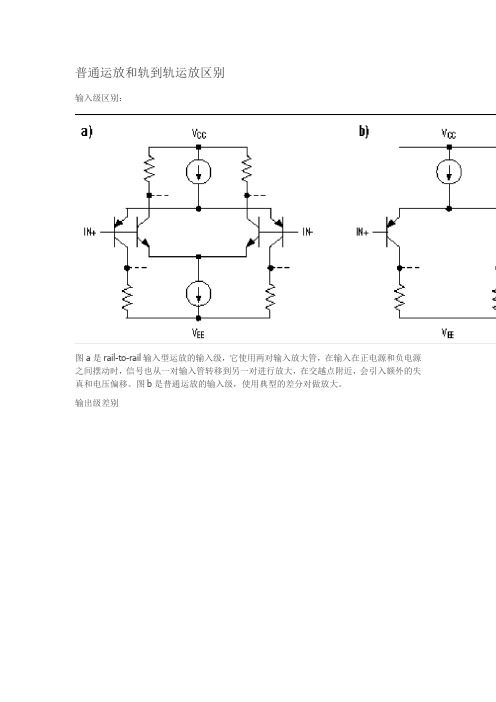

输入级区别:

图a是rail-to-rail输入型运放的输入级,它使用两对输入放大管,在输入在正电源和负电源之间摆动时,信号也从一对输入管转移到另一对进行放大,在交越点附近,会引入额外的失真和电压偏移。

图b是普通运放的输入级,使用典型的差分对做放大。

输出级差别

图a是具备rail-to-rail输出能力的运放的输出级,使用共射组态,将输出提升到Vss+Vce(sat)到VCC-Vce(sat),图b是普通运放的输出级,使用射级跟随器,饱和压降为Vbe+Vce(sat),Vce(sat)来源于恒流源,Vbe为输出级的射级压降。

从零学运放—01运算放大器的参数

从零学运放—01运算放大器的参数运放常用基本参数,如下:※输入失调电压(InputOffset Voltage)Vos※输入失调电压的温漂(OffsetVoltage Drift)Drift※输入偏执电流(InputBias Current)Ib※输入失调电流(InputOffset Current)Ios※共模电压输入范围(InputCommon-Mode Voltage Range)Vcm※输出动态范围特性(OutputCharacteristics)※压摆率(SlewRate)SR※增益带宽积(GainBandwidth Product)GBP※开环增益(Open-LoopVoltage Gain)Aol※共模信号抑制比(CommonMode Rejection)※电源纹波抑制比(SupplyVoltage Rejection)※噪声密度(NoiseDensity)实际运放参数有很多种,这里只是列出来我们通常普遍用到的参数。

下面是输入特性1.1、输入失调电压(InputOffset Voltage)Vos将运放的两个输入端接地,理想运放输出为零,但实际运放输出不为零。

将输出电压除以增益得到的等效输入电压称为输入失调电压。

一般定义为运放输出为零时,两个输入端之间所加的补偿电压。

该值反映了运放内部电路的对称性,对称性越好,输入失调电压越小。

高精度运放,内部补偿电路做的好,对称性好,相对来说就贵。

Vos(输入失调电压)越小,芯片价格就越贵。

那么我们是根据我们信号的特性来选择我们的运放,不一定所有的使用运放的地方都用高精度运放,要考虑到我们产品性价比,成本需要廉价。

下图是,运放的Vos参数图表:一般给出一个典型值(常温下25℃),然后给出一个全温度的范围值。

一般来说我们做设计时我们要考虑的都是最大值(Max),并且是全温度的最大值,因为我们不能保证我们的产品工作在什么温度下并且全温度下已经考虑了温漂的影响。

对轨对轨运算放大器的理解

对轨对轨运算放大器的理解Document serial number【UU89WT-UU98YT-UU8CB-UUUT-UUT108】轨对轨(rail-to-rail)1.所谓轨对轨(rail-to-rail)运算放大器,指的是放大器输入和输出电压摆幅非常接近或几乎等于电源电压值。

2.不是所有的rail to rail 运放输入和输出都接近电源,有的只是输入有的只是输出,当然也有的输入输出都是rail to rail 的,该类运放的最大特点就是可以扩展信号的电压范围,但一般输出电流较小,在大电流的情况下并不能保证rail to rail。

3.在低电源电压和单电源电压下可以有宽的输入共模电压范围和输出摆幅。

4.轨至轨输入,有的称之为满电源摆幅(R-R)性能,可以获得零交越失真,适合驱动ADC,而不会造成差动线性衰减,实现高精密度应用,有轨至轨运放和轨至轨比较器。

,只是一个概念,其实就是正负电源(±V)供电运算放大器。

☆运算放大器供电方式:1.±V;2.+V和GND。

这两种供电方式,各有各的特点。

1.±V:用三极管的截止失真来说,这种方式输入,不要加入直流输入成分,它的“静态工作点”电压是0V,所以动态范围非常大,接近电源。

优点:失真小,态范围非常大(振幅接近V);缺点:双电源输入,电路变得复杂。

2.+V和GND:还拿三极管的截止失真来说,这种方式输入,如果在输入端不加入直流成分(1/2V),那么在输入信号电压很大时,信号的负半周期,就是出现截止失真。

(设计方案:在输入端加入直流成分(稍稍大于1/2V),它的“静态工作点”电压是1/2V左右,这样所以动态范围也可以非常大,接近电源1/2V左右。

)优点:单电源输入,电路简单;缺点:不接入直流成分,失真大,如果作为高音质声音放大,会引起左右分离度降低等情况。

综上情况,在高性能运算放大器电路中,采用rail-to-rail设计方案比较好。

Rail-to-Rail CMOS运算放大器设 Rail-to-Rail特点

一、恒定增益、Rail-to-Rail CMOS运算放大器设计摘要:本文设计了一种低电压、恒定增益、Rail-to-Rail的CMOS运算放大器,整个电路采用标准的0.6um CMOS工艺参数进行设计,并经过HSPICE工具仿真,在3V的单电源工作电压情况下,静态功耗约为9.1mW,当电路同时驱动20pF电容和500Ω电阻的负载时,电路的直流增益达到62dB,单位增益带宽达到18MHz,相位裕度为50o。

关键词:模拟集成电路;CMOS;运算放大器 .随着信息技术和微电子制作工艺技术的高速发展,器件的特征尺寸越来越小,由此构成的集成电路的电源电压也越来越低。

1997年,半导体工业协会曾对未来十年CMOS电路的电源电压发展趋势作了预测,如图1所示。

预计未来十年集成电路的电源电压将降至1.5V,甚至更低。

形成这种发展趋势的原因很多。

其中主要有以下三方面原因:1、随着集成制作工艺的发展,器件的特征尺寸将逐渐减小,相同工作电压下小尺寸器件所承受的电场将逐渐增高,器件工作的安全性要求迫使工作电压必须相应降低,而电路集成规模或集成密度逐步增大的事实,导致大功耗、大发热量的芯片出现,同样要求采用降低电源电压来降低功耗。

2、便携式电子装置的迅速发展及其呈现出的广阔市场,可植入人体的微功耗医疗电子部件的广泛应用等市场需求是对低电压电路的有力牵引。

3、全球兴起的绿色环保——低能耗要求亦是发展低电压电路的重要动力。

虽然数字化处理技术已经广泛应用于电子设备中,然而电子设备的原始信号均来自现实世界,如电磁记录、扬声器、麦克风、CCD、LCD、无线调制器和解调器等,它们所产生的信号都为模拟信号,这些信号实现数字处理前必然要先经过模拟信号处理(比如放大、A/D 转换等),同时数字化处理后的信号作用于现实世界时仍需还原为模拟信号(比如D/A转换、功率放大等)。

因而即使在数字技术十分成熟的今天,模拟信号处理技术仍是无法回避,不能忽视的。

Rail-to-Rail CMOS运算放大器设 Rail-to-Rail特点

一、恒定增益、Rail-to-Rail CMOS运算放大器设计摘要:本文设计了一种低电压、恒定增益、Rail-to-Rail的CMOS运算放大器,整个电路采用标准的0.6um CMOS工艺参数进行设计,并经过HSPICE工具仿真,在3V的单电源工作电压情况下,静态功耗约为9.1mW,当电路同时驱动20pF电容和500Ω电阻的负载时,电路的直流增益达到62dB,单位增益带宽达到18MHz,相位裕度为50o。

关键词:模拟集成电路;CMOS;运算放大器 .随着信息技术和微电子制作工艺技术的高速发展,器件的特征尺寸越来越小,由此构成的集成电路的电源电压也越来越低。

1997年,半导体工业协会曾对未来十年CMOS电路的电源电压发展趋势作了预测,如图1所示。

预计未来十年集成电路的电源电压将降至1.5V,甚至更低。

形成这种发展趋势的原因很多。

其中主要有以下三方面原因:1、随着集成制作工艺的发展,器件的特征尺寸将逐渐减小,相同工作电压下小尺寸器件所承受的电场将逐渐增高,器件工作的安全性要求迫使工作电压必须相应降低,而电路集成规模或集成密度逐步增大的事实,导致大功耗、大发热量的芯片出现,同样要求采用降低电源电压来降低功耗。

2、便携式电子装置的迅速发展及其呈现出的广阔市场,可植入人体的微功耗医疗电子部件的广泛应用等市场需求是对低电压电路的有力牵引。

3、全球兴起的绿色环保——低能耗要求亦是发展低电压电路的重要动力。

虽然数字化处理技术已经广泛应用于电子设备中,然而电子设备的原始信号均来自现实世界,如电磁记录、扬声器、麦克风、CCD、LCD、无线调制器和解调器等,它们所产生的信号都为模拟信号,这些信号实现数字处理前必然要先经过模拟信号处理(比如放大、A/D 转换等),同时数字化处理后的信号作用于现实世界时仍需还原为模拟信号(比如D/A转换、功率放大等)。

因而即使在数字技术十分成熟的今天,模拟信号处理技术仍是无法回避,不能忽视的。

几种常用运算放大器举例

运算放大器分类总结报告1、通用型运算放大器通用型运算放大器就是以通用为目的而设计的。

这类器件的主要特点是价格低廉、产品量大面广,其性能指标能适合于一般性使用。

例μA741(单运放)、LM358(双运放)、LM324(四运放)及以场效应管为输入级的LF356都属于此种。

它们是目前应用最为广泛的集成运算放大器。

下面就实验室里也常用的LM358来做一下介绍:LM358 内部包括有两个独立的、高增益、内部频率补偿的双运算放大器,适合于电源电压范围很宽的单电源使用,也适用于双电源工作模式,在推荐的工作条件下,电源电流与电源电压无关。

它的使用范围包括传感放大器、直流增益模块和其他所有可用单电源供电的使用运算放大器的场合。

:外观管脚图它的特点如下:·内部频率补偿·直流电压增益高(约100dB)·单位增益频带宽(约1MHz)·电源电压范围宽:单电源(3—30V)双电源(±1.5 一±15V)·低功耗电流,适合于电池供电·低输入偏流·低输入失调电压和失调电流·共模输入电压范围宽,包括接地·差模输入电压范围宽,等于电源电压范围·输出电压摆幅大(0 至Vcc-1.5V)常用性能指标:性能图表:大信号频率响应 大信号电压开环增益电压跟随器对小信号脉冲的响应常用电路: (1)、正向放大器根据虚短路,虚开路,易知:1(1)2R Vo Vi R =+ (2)、高阻抗差分放大器电路左半部分可以看作两个同向放大器,分别对e1,e2放大(a+b+1)倍,右半部分为一个差分放大器放大系数为C ,因此得到结果:0(21)(1)e C e e a b =-++(3)、迟滞比较器将输入电平与参考电平作比较,根据虚短路,虚开路有:121()()O REF IN R R V V V R +=- ,则: 112112()()inL OL REF REFinHOH REF REFR V V V V R R R V V V V R R =-++=-++2、高精度运算放大器所谓高精度运放是一类受温度影响小,即温漂小,噪声低,灵敏度高,适合微小信号放大用的运算放大器。

轨到轨

轨到轨(Rail to Rail)概念从输入来说, 其共模输入电压范围可以从负电源到正电源电压; 从输出来看, 其输出电压范围可以从负电源到正电源电压。

Rail to Rail翻译成汉语即“轨到轨”,指器件的输入输出电压范围可以达到电源电压。

传统的模拟集成器件,如运放、A/D、D/A等,其模拟引脚的电压范围一般都达不到电源电压,以运放为例,电源为+/-15V的运放,为确保性能(首先是不损坏,其次是不反相,最后是足够的共模抑制比),输入范围一般不要超过+/-10V,常温下也不要超过+/-12V;输出范围,负载RL>10kohm时一般只有+/-11V,小负载电阻(600ohm)时只能保证+/-10V。

这对器件的应用带来很多不便。

Rail-to-Rail的器件,一般都是低压器件(+/-5V 或single +5V),输入输出电压都能达到电源(输入甚至可以超过)。

其原理上的秘诀便在于电流模+NPN/PNP互补输入结构。

rail-to-rail器件的某些设计思想,对我们自己设计电路也可以提供一些有益的思路。

“轨到轨(rail-to-rail)”的特性即:它的输入或输出电压幅度即使达到电源电压的上下限,此时放大器也不会像常规运放那样发生饱和与翻转。

例如,在+5V单电源供电的条件下,即使输入、输出信号的幅值低到接近0V,或高至接近5V,信号也不会发生截止或饱和失真,从而大大增加了放大器的动态范围。

这在低电源供电的电路中尤其具有实际意义。

TLC2274(轨到轨)与OP07(非轨到轨)的输入输出范围如表2(厂家给出)及图2(实际测定)。

可以看到,TLC2274的动态范围可达4.8V,而OP07(及其它非轨到轨特性的运放)的动态范围仅3V左右。

芯片型号电源电压(V)最高峰值(Vo)最低负峰值(Vo)实际动态范围(V)TLC2274 +5V 4.93V 0.09V 4.8VOP07 +/-2.5V 4V 1V 3V。

放大器 , 轨到轨放大器

放大器, 轨到轨放大器我为应用选择的放大器的数据手册同时规定了小信号带宽和大信号带宽,它们是相当不同的规格。

我如何确定信号是小信号还是大信号?当谈到放大器的带宽时,我们讨论的其实是使用小信号模型的放大器频率响应。

该模型的导出前提是电路在偏置点周围是线性的;换言之,其增益保持恒定,与施加的信号无关。

如果信号足够小,该模型会非常有效,其与实际情况的偏差几乎难以检测。

所有人都喜欢使用这个模型,因为它简化了设计和分析过程。

如果使用大信号模型——即包括所有非线性方程——电路将变得复杂无比,至少对我这样的凡人是如此。

1因此,小信号模型和正弦信号将复杂性降低到一个可处理的水平。

但严格说来,即便最小的实际信号也会稍稍改变晶体管电路(例如运算放大器)的偏置点。

信号越大,就越难以忽略非线性效应,其最明显的表现是失真。

在某一点,由于信号过快且过大,使得放大器达到其压摆率限值——相当于放大器输出的最大变化率,通常用V/µs表示。

压摆率达到限值之后,放大器就会落后,当信号开始斜坡下降时,放大器尚未达到信号峰值,最后的结果便是信号幅度比预期要小。

在该点时,放大器大致达到了大信号带宽。

一般来说,这发生在低于小信号带宽的频率,信号确定无疑地发生了最大的失真。

但信号不会突然发生彻底失真,而是逐渐增加失真的幅度和频率。

当失真超过系统的容限时,我们可以说信号过大。

那么,我们如何知道放大器足够快,能够处理某个信号呢?首先,像平常一样,确保小信号带宽对于所需增益是足够的。

然后,查看数据手册中的大信号带宽规格(或SR[V/µs]=Peak_Amplitude×6.28×Frequency[MHz]。

轨对轨运放

1.所谓轨对轨(rail-to-rail)运算放大器轨对轨放大器,指的是放大器输入和输出电压摆幅非常接近或几乎等于电源电压值。

2.不是所有的rail to rail 运放输入和输出都接近电源,有的只是输入有的只是输出,当然也有的输入输出都是rail to rail 的,该类运放的最大特点就是可以扩展信号的电压范围,但一般输出电流较小,在大电流的情况下并不能保证rail to rail3.在低电源电压和单电源电压下可以有宽的输入共模电压范围和输出摆幅.4.轨至轨输入,有的称之为满电源摆幅(R-R)性能,可以获得零交越失真,适合驱动ADC,而不会造成差动线性衰减。

实现高精密度应用。

有轨至轨运放和轨至轨比较器。

5.rail-to-rail,只是一个概念,其实就是正负电源(±V)供电运算放大器。

2.?所说,我不能苟同。

其实一切高深的复杂的电路,追根朔源,都可以看作由简单的分离元件组成。

运算放大器供电方式:1,±V2,+V和GND。

这两种供电方式,各有各的特点。

1,±V用三极管的截止失真来说,这种方式输入,不要加入直流输入成分,它的“静态工作点”电压是0V,所以动态范围非常大,接近电源。

优点:失真小,态范围非常大(振幅接近V)。

缺点:双电源输入,电路变得复杂。

2,+V和GND。

还拿用三极管的截止失真来说,这种方式输入,如果在输入端不加入直流成分(1/2V),那么在输入信号电压很大时,信号的负半周期,就是出现截止失真。

设计方案,在输入端加入直流成分(稍稍大于1/2V),它的“静态工作点”电压是1/2V左右。

这样所以动态范围也可以非常大,接近电源1/2V左右。

优点:单电源输入,电路简单。

缺点:不接入直流成分,失真大;如果作为高音质声音放大,会引起左右分离度降低等情况。

综上情况,在高性能运算放大器电路中,采用rail-to-rail设计方案比较好。

6.再补充一下:轨至轨输入/输出功能扩大了动态范围,最大限度地提高了放大器的整体性能。

CMOS轨对轨运算放大器电路

6. 成绩评定

1. “重庆大学本科课程设计管理办法(试行)(重大校 [2005]111号)”摘录:

第十六条 课程设计的成绩分为:优秀、良好、中等、及格,不及格五个等 级。课程所在学院应针对不同性质的课程制定评分标准。 第十七条 课程设计成绩为优秀者一般不超过完成课程设计人数的20%~ 25%,优良总比例不超过完成课程设计人数的70%。 第十八条 课程设计属下列情况之一的应评为不及格: (一)设计(论文)工作态度不认真、纪律松懈,缺勤累计超过三分 之一以上; (二)设计(论文)过程中有作弊行为,如抄袭别人成果等; (三)设计(论文)有原则性错误; (四)设计说明书(论文)达不到基本要求。 第二十条 课程设计不及格的学生,必须重修课程设计,并按学生学籍管理 规定的相关条款进行处理。

3. 课程设计的工作计划

(1)2011.6.13~2011.6.14:对设计的电路进行版图设计,并 从版图中提取T-Spice文件; (2)2011.6.15~2011.6.16:根据从版图中提取的参数,用 T-Spice软件进行仿真。将仿真结果与设计参数进行比较, 如不满足设计指标要求,则修改版图,再提取参数、仿真 比对,直到满足需要为止。 (3)2011.6.17~2011.6.18:撰写设计报告,提交符合规范的 设计报告。

4. 设计报告书写要求

用标准格式的纸书写(重大实践网上下载); 语言通顺,层次清楚,符合规范(见附录); 字数要求不得少于2000字; 给出设计的版图; 给出从版图中提取T-Spice文件; 给出后仿真的相关波形,标出相关数据点;

5. 设计报告装订要求

课程设计装订顺序为: (1)封面(学校统一规定) (2)任务书(由指导教师填写) (3)摘要及关键词(可选) (4)正文 (5)结论 (6)注解(尾注或夹注)(可选项) (7)参考文献

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

•随着单电源运放的广泛的运用,运放的轨至轨输入(rail to rail input)成为一个时髦的词。

现在大部分低电压单电源供电的运放都是轨至轨输入的。

TI 在轨至轨输入的运放产品方面具有十分领先的优势。

本文介绍运放的rail to rail 输入的实现以及TI在实现运放的rail to rail 输入方面的领先技术。

先说两句废话,解释一下轨至轨,这里的轨指的是电源轨,运放的两个电源供电电压如+/-15V。

这两个电源电压就像两条平行的距离为30V的“轨道”

一样限制了运放的输入输出信号。

运放的轨至轨输入是指运放的输入端信号电压能够达到电源的两个轨,并保持不失真,如上例输入信号电压可达到+/-15V。

运放的输入电压范围可在运放的datasheet中找到。

就是共模电压范围Vcm

(Common-Mode Voltage Range)。

如下表即为OPA365的输入电压范围,可见它是典型的轨至轨输入运放。

一般的BJT和JFET是非轨至轨输入的运放。

如下表所示为OPA827共模输入电压范围为(V-)+3V至(V+)-3V,典型的非轨至轨运放。

单电源(我们暂且称之为“单电源”)运放的输入级通常有三种结构,第一种是采用PMOS做差分输入级。

这样的运入输入级电压可以低于负电源轨0.2甚至0.3V,但达不到正电源轨,如OPA336。

下表是datasheet中标出的OPA336输入电压范围。

它的输入级原理框图如下图,典型的PMOS差分输入级。

既然PMOS差分输入级输入电压不能达到正电源轨,那NMOS呢,对头,NMOS差分输入级的输入电压可以达到正电源轨,但是达不到负电源轨,一般会在负电源轨的1.2V之上。

此时有人想到了,把PMOS和NMOS差分输入级并联起来。

在接近电源负电压轨时使PMOS差分输入级工作,在接近电源正电源轨时使NMOS差分输入级工作。

这样不就可以实现运放的轨至轨输入了嘛。

太巧妙了。

的确早先的轨至轨输入运放就是这样设计的。

并且现在也在大量使用这种技术。

如下图是OPA703的输入级,就是典型的PMOS与NMOS相并联的运放输入级。

当输入共模电压在(Vss-)-0.3V<Vcm<(Vss+)-2V时PMOS处于工作状态,NMOS处于关闭状态。

当输入共模电压在(Vss-)-2V<Vcm<(Vss+)+0.3V时NMOS处于工作状态,PMOS处于关闭状态。

下表是OPA703的datasheet中给出的共模电压输入范围(V-)-0.3V至(V+)+0.3V.

Bipolar输入级运入同样也有这样的结构,如下图是典型PNP 与NPN型三级管并联形成的差分输入级。