第五章_IO系统

io设备课程设计

io设备课程设计一、教学目标本课程的教学目标是使学生掌握io设备的基本原理、分类、工作方式和主要性能指标,能够正确选用和使用io设备,提高计算机系统的运行效率。

具体分解为以下三个层面:1.知识目标:学生需要了解io设备的硬件结构和软件接口,掌握各种io设备的工作原理、性能指标及应用场景。

2.技能目标:学生能够根据实际需求选择合适的io设备,进行基本的安装、调试和优化。

3.情感态度价值观目标:培养学生对io设备的正确使用和维护意识,提高学生对计算机系统的整体性能的重视。

二、教学内容本课程的教学内容主要包括io设备的基本原理、分类、工作方式和主要性能指标。

具体安排如下:1.第一章:io设备概述,介绍io设备的概念、分类和性能指标。

2.第二章:io设备的工作方式,讲解io设备的数据传输方式、中断处理和直接内存访问(DMA)。

3.第三章:io设备的硬件结构,包括io接口、总线和存储器等方面的知识。

4.第四章:io设备的软件接口,介绍io设备的驱动程序和应用程序的编写方法。

5.第五章:常见io设备,分析硬盘、显示器、键盘、鼠标等常见io设备的工作原理和性能。

6.第六章:io设备的选购与维护,讲解如何选择合适的io设备以及如何进行维护和优化。

三、教学方法为了提高学生的学习兴趣和主动性,本课程将采用多种教学方法相结合的方式:1.讲授法:教师通过讲解io设备的基本原理、分类和工作方式,使学生掌握相关知识。

2.案例分析法:分析实际案例,使学生更好地理解io设备的工作原理和应用场景。

3.实验法:安排实验室实践环节,让学生亲自动手操作io设备,提高实际操作能力。

4.讨论法:学生进行小组讨论,分享彼此的学习心得和经验,促进互动交流。

四、教学资源为了支持本课程的教学内容和教学方法的实施,我们将准备以下教学资源:1.教材:《io设备教程》,为学生提供系统、全面的io设备知识。

2.参考书:推荐一些有关io设备的经典著作,供学生深入研究。

精选设备管理IO设备

第五章 设 备 管 理

3) 这种分类方式可将I/O (1) 独占设备。 (2) (2) 共享设备。 (3) (3) 虚拟设备。

第五章 设 备 管 理

2. 设备与控制器之间的接口

至设备 控制器

数据信号线 状态信号线

控制信号线

I/O设 备 缓冲 转换器

控制逻辑

信号 数据

图 5-1 设备与控制器间的接口

第五章 设 备 管 理

5.1.2 设备控制器

1. 设备控制器的基本功能 1) 接收和识别命令 2) 2) 数据交换 3) 3) 标识和报告设备的状态 4) 4) 地址识别 5) 5) 数据缓冲 6) 6) 差错控制

第五章 设 备 管 理

2. 设备控制器的组成

CPU与 控 制 器 接 口

数据线

地址线 控制线

T3(缓 冲 3)

T4(缓 冲 4)

(b)

M1

M2

M3

M4

C1

C2

C3

C4

(2) 内存地址寄存器MAR。在输入时,它存放把数据从 设备传送到内存的起始目标地址;在输出时,它存放由内存 到设备的内存源地址。

(3) 数据寄存器DR。用于暂存从设备到内存,或从内存 到设备的数据。

(4) 数据计数器DC。 存放本次CPU要读或写的字(节)数。

第五章 设 备 管 理

3. DMA工作过程 设置AR和DC初值

一是其指令类型单一,这是由于通道硬件比较简单, 其所能执行的命令,主要局限于与I/O操作有关的指令; 再 就是通道没有自己的内存,通道所执行的通道程序是放在主 机的内存中的, 换言之,是通道与CPU共享内存。

第五章 设 备 管 理

2. 通道类型 1) 字节多路通道(Byte Multiplexor Channel)

第五章 IO端口、输入捕捉

• 图5-2: 共用的端口结构框图

• 5.3.1 I/O 与多个外设复用

• 对于有些dsPIC30F 器件,尤其是那些带有少量 I/O 引脚数较少的器件,其每个I/O 引脚可能要 复用多种外设功能。图5-2 所示为两个外设与同 一个I/O 引脚复用的示例。

• 和TRISx 寄存器以及该端口引脚将读作0

5.3 外设复用

• 当某个外设使能时,与其相关的引脚将被禁止作为通 用I/O 引脚使用。可以通过输入数据路径读该I/O 引脚, 但该I/O 端口位的输出驱动器将被禁止。

• 与另一个外设共用一个引脚的I/O 端口总是服从于该外 设。外设的输出缓冲器数据和控制信号提供给一对多 路开关。该多路开关选择是外设还是相关的端口拥有 输出数据的所有权以及I/O 引脚的控制信号。图11-2 显示了端口如何与其他外设共用,以及与外设连接的 相关I/O 引脚。

• 参照图5-2,外设多路开关的结构将决定外设输 入引脚是否可以通过使用PORT 寄存器用软件控 制。

• 当图中所示的概念化的外设在功能被使能时,会断开 I/O 引脚与端口数据的连接。一般而言,下列外设允许 通过PORT 寄存器手动控制它们的输入引脚:

• 外部中断引脚 • 定时器时钟输入引脚 • 输入捕捉引脚 • PWM 故障引脚 • 大多数串行通信外设在使能时,将完全控作0 • bit 13 ICSIDL:输入捕捉模块在空闲时停止控制位 • 1 = 输入捕捉模块在CPU 空闲模式将停止 • 0 = 输入捕捉模块在CPU 空闲模式将继续工作 • bit 12-8 未用:读作0 • bit 7 ICTMR:输入捕捉定时器选择位 • 1 = 捕捉事件时捕捉TMR2 的内容 • 0 = 捕捉事件时捕捉TMR3 的内容 • 注: 可供选择的定时器可能会和上述不同。 更多详细

CXServer手册五(44-53)

OMRON 第五章-IO表组件第五章IO表组件本章叙述适用于C系列PLC、CV系列PLC和CS1系列PLC的IO表组件,及其创建、恢复和编辑经过配置的PLC机架和地址数据的能力。

IO表组件允许使用适用的硬件作为参考,在PLC内配置机架、槽和单元。

一个PLC具有三个版本的IO表,这些表在理论上应该具有相同的内容。

IO表组件的编辑允许操作表的内部版本和修改PLC硬件如何配置的视图。

这三个版本是:♦实际IO表。

上电时PLC单元和槽的实际硬件配置。

♦注册IO表。

内部PLC表:这是PLC运行时使用的表,不管实际硬件的状态如何它可以由CX-Server软件读出,并且对于C2000 PLC、CV系列PLC和CS系列PLC,它还可由CX-Server软件写入。

♦CX-Server IO 表。

CX-Server 理解的IO配置。

它可直接创建和修改,与PLC无关,并且可用程序传送(对于CV系列和CS1系列PLC)。

可以通过PC改变注册表和CX-Server表,但实际配置需要对PLC硬件的直接操作。

只能把C2000、CV和CS1系列PLC的注册IO表传送到PLC。

对注册IO表中的各个IO单元的编辑只在C1000H、C2000H、CS1系列和CV系列PLC上有效。

IO表组件显示为一个分层结构。

IO表视图可扩大以显示所有远程终端(RT)和IO的条目。

可显示活动的PLC的所有机架和单元,尽管它们未必全部在使用中。

可显示对应于每个机架、槽或单元的地址和IO字串,用于表示单元的输入和输出特性。

状态栏显示所选的PLC和CPU型号,以及PLC的当前操作方式。

当增加一个远程终端(RT)时,它可被扩展以提供终端视图,显示该远程机架上的所有条目。

机架左边的图标表示安装在扩展机架的单元、SYSBUS/SYSBUS2远程机架或IO终端。

为查看IO表的内容,双击某机架。

每个槽的单元地址将显示在括号中。

44OMRON 第五章-IO 表组件45此图标代表一个空机架。

计算机控制(第五章开关IO电机控制步进电机)

(七)电磁阀接口技术 电磁阀对气体、液体管道的开关进行控制。广泛应用于液 压机械、空调系统、热水器、自动机床等系统中。 电磁阀可分为交流和直流两类,根据其阀位和通道数目有 两位三通、两位四通、三位四通等。 下图为电磁阀的结构原理图。

交流电电磁阀常要使用双向可控硅驱动或用一个直流继 电器作为中间继电器控制。

下图为交流电磁阀的接口电路。MOC3041为光电耦合 器,用于触发双向晶闸管KS,以及隔离单片机和电磁阀系统。

(八)报警程序的设计

常用的报警方式有: 1、 声语言报警:电铃,电笛,频率可调的蜂鸣震 荡音响,集成电子音乐芯片,语音芯片等。 2、 显示报警:LED指示灯,闪烁的白炽电灯, LED、LCD数码管,LED、LCD图形显示器,CRT 显示器等。 3、 图形、声音的混合报警。

三、电机控制接口技术

电动机的应用非常广泛。电机分为动力电机和控制电机。 现代化生产对电机的性能要求越来越高:精度、速度、带 负载能力、灵活性、智能化等。 电机的控制用自动化控制设备,朝向集成化、微型化、智 能化方向发展。微机和单片机使电机控制产生革命性的飞跃。目 前已研制出了许多微机或单片机控制电机的系统及专用控制板。 不远的将来,智能化调速系统、电机一体化等会广泛应用。 (一)小功率直流电机调速原理 小功率直流电机的调速可通过控制电枢平均电压来实现。 用微机或单片机控制,通过改变电枢电压接通时间与通电周期的 比值(即占空比)来控制电机速度——此即脉冲宽度调制PWM。 电机转速由电枢电压Ua决定, Ua越大,电机转速越高。 电机通电时速度增加,断电时速度逐渐减小,控制通、断时间比 即可控制电机转速。 设电机全通电时的转速为Vmax,占空比为D=t1/T,则电机的 平均速度为:Vd=Vmax×D (近似的线性关系)

第5章 IO接口电路的设计

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0 0 0 0 0

0 1 1 1 0 0

1 0 1 1 1 0 1 1 1

x x x x x x

x x x x x x x x x

C018~C01F C020~C027

C028~C02F C030~C037 C038~C03F

1 1 1

1 1 1

0 0 0

0 0 0

0 0 0 0 0 0

0 0 0 0 0 0 0 0 0 0 0 0

0 0 0 0 0 1 0 1 0

x x x x x x x x x

C000~C007 C008~C00F C010~C017

1 1

1 1 1

1 1

1 1 1

0 0

0 0 0

0 0

0 0 0

0 0 0 0

开始 初始化 读入状态

N

数据准备好

Y

输入数→CPU

数→内存缓冲区

N Y

传送完? 结束

9

例5-4

查询式输出方式的接口电路

输出 /ACK 设备

数 据 锁存器 (8位) R C

选通 信号 +5V

D7~D0 /WR(写数据) 2 /CS2 /CS1 1

I/O 译码

M//IO A15~A0

Q

D

D触发器

/RD(读状态) D1(数据总线)

10

设:状态口的地址为P_S2,输出口地址 为P_OUT,传送数据的总字节为C_2, 则查询方式输出数据的程序段为: MOV CX,C_2 READ_S2:IN AL,P_S2 TEST AL,02H JZ READ_S2 MOV AL,输出数据 OUT P_OUT,AL LOOP READ_S2 ……

第五章测试

1.下列选项中,能引起外部中断的事件是( )A.键盘输入B.除数为0C.浮点运算下溢D.访存缺页2.单级中断系统中,中断服务程序内的执行顺序是( )I.保护现场II.开中断Ⅲ,关中断Ⅳ.保存断点v.中断事件处理Ⅵ.恢复现场Ⅶ.中断返回A.I—V一Ⅵ一II一ⅦB.Ⅲ一I—V一ⅦC.ⅡI一Ⅳ一V一Ⅵ一ⅦD.Ⅳ一I—V一Ⅵ一Ⅶ3.某计算机有五级中断L4~L0,中断屏蔽字为M4M3M2MIM。

,Mi=l(。

≤i≤4)表示对L级中断进行屏蔽。

若中断响应优先级从高到低的顺序是L4- L0-L2-L1-L3,则L1的中断处理程序中设置的中断屏蔽字是( ).A. 1 1 1 1 0B.0 1 1 0 1C.00011D.0 1 0 1 0 4.某计算机处理器主频为50MHz,采用定时查询方式控制设备A的I/。

,查询程序运行一次所用的时钟周期数至少为500.在设备A工作期间,为保证数据不丢失,每秒需对其查询至少200次,则CPU用于设备A的I/。

的时间占整个CPU时间的百分比至少是( ).A.0.02%B.0.05070C.0.20070D.0.50%5. 响应外部中断的过程中,中断隐指令完成的操作,除保护断点外,还包括( ).I.关中断II.保存通用寄存器的内容Ⅲ,形成中断服务程序入口地址并送PCA.仅I、ⅡB.仅I、Ⅲc.仅II、Ⅲ D. I、II、Ⅲ6.设置中断排队判优逻辑的目的是( ).A.产生中断源编码B.使同时提出的请求中的优先级别最高者得到及时响应C.使CPU能方便地转入中断服务子程序D.提高中断响应速度7.中断判优逻辑和总线仲裁方式相类似,下列说法正确的是( ).I.在总线仲裁方式中,独立请求方式响应时间最快,是以增加控制线数为代价的II.在总线仲裁方式中,计数器定时查询方式有一根总线请求(BR)和一根设备地址线,若每次计数都从0开始,则设备号小的优先级高Ⅲ.总线仲裁方式一般是指I/。

设备争用总线的判优方式,而中断判优方式~般是指I/。

第5章 字符串和文件IO

String Subset函数应用

• 参见第5章 例3-2

Scan From String函数

•用于扫描字符串,并将有效的数值(0到9,正负,e, E和分号)转换成数值。如果连接了一个格式字符串, 它将根据字符串指定的格式进行转换,否则将进行默 第一个字符的偏移地址是0。

认格式的转换。该函数从偏移地址的string处开始扫描。

• Write To Spreadsheet File VI——用于将单精度 数值组成的一维或者二维数组转换成文本字符串 (LABVIEW自动转换),再写入一个新建文件 或者已有文件。该VI先打开或者新建文件,再写 入,之后再关闭文件(自动完成)。可以用于创 建能够被大多数电子表格(文本编辑)软件读取 的文本文件。 • Read From Spreadsheet File VI——用于从某 个文件的特定位置开始读取指定n行的内容,再 将数据转换成二维或者一维单精度数组 (LABVIEW自动转换)。该VI先打开文件,再读 数据,之后再关闭文件(自动完成)。可以用于 读取用文本格式存储的电子表格文件。

第5章例9保存datalog

注意

• refnum:标识号,用以代表已经打开的文 件。 • 此处涉及文件的低级操作,先打开,再写 入(读出)数据,最后关闭文件,释放 refnum。

第5章例10打开 datalog

第5章例11保存datalog(数组), 然后再打开datalog (数组)

思考题

• Write Characters To File VI——用于将一个字 符串写入一个新建文件或者已有文件。该VI打开 该文件、写入数据,再关闭文件(自动完成) 。 • Read Characters From File VI——用于从某个 文件的特定位置开始读取指定个数的字符。该VI 先打开文件,读取数据,之后再关闭文件(自动 完成) 。 • Read Lines From File VI——用于从某个文件的 特定位置开始读取指定n行的内容。该VI先打开文 件,读取指定的行,之后再关闭文件(自动完 成) 。

单片机原理及接口技术第5章 IO口应用-显示与开关键盘输入

图5-1

发光二极管与单片机并行口的连接

5

如果端口引脚为低电平,能使灌电流Id从单片机的外部流入内部,则将

大大增加流过的灌电流值,如图5-1(b)所示。所以,AT89S51单片机任 何一个端口要想获得较大的驱动能力,要采用低电平输出。 如果一定要高电平驱动,可在单片机与发光二极管之间加驱动电路,如 74LS04、74LS244等。 5.1.2 单片机I/O端口控制发光二极管的编程 发光二极管与单片机的I/O端口的连接,如图5-1(b)所示。如要点亮 某发光二极管,只需该I/O端口位写入“0”即可。下面通过一个例子介绍如

21

图5-6 4位LED静态显示的示意图

示字符。这样在同一时间,每一位显示的字符可以各不相同。但是,静态

显示方式占用I/O口线较多。 对于图5-6所示电路,要占用4个8位I/O口(或锁存器)。如果数码管 数目增多,则还需要增加I/O口的数目。在实际的系统设计中,如果显示位 数较少,可采用静态显示方式。但显示位数较多时,为了降低成本,一般 采用动态显示方式。 2. 动态扫描显示方式 显示位数较多时,静态显示所占用的I/O口多,为节省I/O口与驱动电路

单片机控制的8位I/O口锁存器输出相连。如果送往各个LED数码管所显示字 符的段码一经确定,则相应I/O口锁存器锁存的段码输出将维持不变,直到

送入下一个显示字符的段码。因此,静态显示方式的显示无闪烁,亮度较

高,软件控制比较容易。 图5-6所示为4位LED数码管静态显示电路,各个数码管可独立显示,

只要向控制各位I/O口锁存器写入相应的显示段码,该位就能保持相应的显

闭合时,P3.0引脚为低电平。单片机对开关状态的检测是由程序检测

10

图5-3

开关、LED发光二极管与P1口的连接

《计算机系统结构》第六章IO系统

Left Symmetric Distribution

• Parity disk = (block number/4) mod 5 • Eliminate the parity disk bottleneck of RAID 4 • Best of large read and large write performance • Can correct any single self-identifying failure • Small logical writes take two physical reads and two physical writes. • Recovering needs reading all nonfailed disks

1. RAID0

– 数据分块,即把数据分布在多个盘上。 – 非冗余阵列、无冗余信息。 – 严格地说,它不属于RAID系列。

A

B

C

D

E

I

F

J

G

K

H

L

M

N

O

etc...

RAID0中的数据映射

逻辑盘 物理盘 0 物理盘 1 物理盘 2 物理盘 3

条带0

条带 1 条带 2 条带 3 条带 4 条带 5 条带 6 条带 7 阵列管理

实时性:在I/O设备提出中断、DMA等请求时,CPU 要及时响应,完成必要的I/O操作或控制。例如: Keyboard、Printer、COM、Mouse、定时器等。 与设备无关性:通过制定统一的接口标准(物理接口、 软件接口),使得应用程序依据这一接口可以访问或 支持各种I/O设备。

I/O系统的层次结构

独立的地址和 1. 总线的设计 数据总线

数据总线 宽度

过程控制系统第五章

续缓慢上升, 同时乙塔的进料量也缓慢增加, 当液位上 升到某一数值时, 甲塔采出量等于在干扰作用下的入料 量, 液位不再上升而暂处某一高度. 从而使液位和流量 都处于缓慢变化中, 达到均匀协调的控制目的.

如干扰来自乙塔塔压变化而使其入料量发生变化, 则先由流量副回路控制, 当这一控制作用使甲塔液位受 到影响时, 再由液位控制器改变流量控制器的设定值, 让流量控制器作进一步的调整, 缓慢改变控制阀的开度 两控制器互相配合, 使液位和流量都在允许的范围内缓 慢地均匀变化.

0

t0

t

作用下, 液位和流量均在各自允许的范围内缓慢变化,

如上右图所示. 通常, 简单均匀方案中的控制器采用纯

比例控制, 且比例度较大, 一般大于100%, 当需采用PI 控制时, 应使积分弱些, 即积分时间常数整定的大些.

简单均匀控制系统的最大优点是结构简单, 投运方 便, 成本低廉. 但当前后设备的压力变化较大时, 尽管 控制阀的开度不变, 输出流量也会发生变化, 所以它适 用于干扰不大, 要求不高的场合. 此外, 在液位对象的 自衡能力较强时, 均匀控制的效果也较差.

先说明主控制器Wc1(s) 前负号的由来. D1(s)

1

H

R

(

s)

E1

(

s)

Wc1

(

s

)

QR

(s)

E2 (s)

Wc2 (s)

Q(s) Wo2 (s)

Z1(s)

Z2(s)

H m2 (s)

H (s) Wo1 ( s )

H m1 ( s)

前已选择主控制器为正作用方式, 则: E1(s) Z1(s) HR (s) 主控制器正作用方式如下图所示. 等效变换得, 设:

IO系统调用原理介绍

IO系统调用原理介绍

下面是IO系统调用的原理和流程介绍。

1. 用户程序发起IO请求:应用程序通过系统提供的IO相关函数发起IO请求。

例如,如果要读取文件,应用程序会调用read(函数,如果要写入文件,应用程序会调用write(函数。

2.系统调用进入内核态:当应用程序发起IO请求时,CPU会从用户态切换到内核态,将控制权交给操作系统内核。

3.内核处理IO请求:操作系统接收到IO请求后,会根据请求的类型和参数进行相应的处理。

4.硬件设备访问:操作系统根据IO请求的类型,调用相应的设备驱动程序,将IO请求传递给硬件设备进行处理。

例如,如果是读取文件的IO请求,操作系统会调用磁盘驱动程序将数据从硬盘读取到内存中。

5.等待IO操作完成:在进行IO操作时,可能需要等待硬件设备的响应。

例如,如果是网络IO请求,操作系统可能需要等待网络数据包的传输完成才能继续执行。

6.返回结果给应用程序:当IO操作完成后,操作系统将结果返回给应用程序。

如果是读取文件的请求,操作系统会将读取到的数据拷贝到应用程序指定的缓冲区。

7.应用程序继续执行:一旦IO操作完成并且结果返回给应用程序,操作系统会将控制权重新切换回用户态,应用程序可以继续执行后续的操作。

IO系统调用的原理可以简单总结为:应用程序通过系统调用将IO请求交给操作系统内核,内核根据IO请求类型和参数进行相应的处理,并将请求传递给硬件设备进行实际的IO操作。

当IO操作完成后,操作系统将结果返回给应用程序,应用程序可以根据结果继续执行后续的操作。

io设备课程设计

io设备课程设计一、课程目标知识目标:1. 让学生掌握IO设备的基本概念,包括输入设备和输出设备的功能和分类。

2. 使学生了解计算机系统中IO设备的硬件组成及其与CPU的交互原理。

3. 引导学生掌握IO设备的编程控制方法,理解中断、直接内存访问(DMA)等技术的应用。

技能目标:1. 培养学生运用所学知识分析、解决实际IO设备问题的能力。

2. 培养学生通过编程实现对IO设备的控制,提高实践操作技能。

3. 培养学生团队协作能力,通过分组讨论、实践,共同完成IO设备课程项目。

情感态度价值观目标:1. 激发学生对计算机硬件和IO设备的兴趣,培养其探索精神。

2. 培养学生养成良好的学习习惯,严谨的科学态度,敢于面对和解决实际问题。

3. 增强学生的信息安全意识,使其明白IO设备在计算机系统安全中的作用。

本课程针对高年级学生,结合学科特点和教学要求,将课程目标分解为具体的学习成果。

通过本课程的学习,使学生既掌握了IO设备的基本理论知识,又具备了一定的实践操作技能,为今后进一步学习计算机硬件和系统编程打下坚实基础。

同时,培养学生团队协作、自主学习的能力,提高其综合素质。

二、教学内容1. IO设备基本概念:介绍输入设备、输出设备的定义及分类,分析各类IO设备的性能特点。

参考教材章节:第一章 IO设备概述2. IO设备的硬件组成:讲解IO设备与CPU的交互原理,介绍接口电路、数据传输方式等硬件组成。

参考教材章节:第二章 IO设备的硬件组成3. IO设备的编程控制:学习IO端口编址、中断处理、直接内存访问(DMA)等编程控制方法。

参考教材章节:第三章 IO设备的编程控制4. IO设备应用实例:分析实际应用中的IO设备,如USB、串口、并行口等,了解其工作原理和编程实现。

参考教材章节:第四章 常用IO设备及其应用5. 课程项目:分组进行IO设备控制实践,通过项目实施,巩固所学知识,提高动手能力。

参考教材章节:第五章 IO设备课程项目实践教学内容安排和进度:第1周:IO设备基本概念第2周:IO设备的硬件组成第3周:IO设备的编程控制第4周:IO设备应用实例第5-6周:课程项目实践本教学内容结合课程目标,确保科学性和系统性,按照教学大纲安排,使学生能够循序渐进地掌握IO设备相关知识。

微机原理 第五章 IO接口

控 制 逻 辑

8 8

IOR IOW

I/O 端口 (256个) 个

(3)使用专用I/O指令和 (3)使用专用I/O指令和 使用专用I/O 存储器访问指令有明显 区别, 区别,可使编制的程序 清晰易懂,便于检查. 清晰易懂,便于检查.

隔离I/O I/O方式 5.2.2 隔离I/O方式

5-16

2.缺点: 2.缺点: 缺点

AB 存储器 存 储 空 间 DB MPU

读 /写 I/O 端口 RD 源自R 控制 逻辑控制5.2.1 存储器映象方式

5-12

1.优点: 1.优点: 优点

AB 存储器 存 储 空 间 DB MPU

读 /写 I/O 端口 RD WR 控制 逻辑

控制

I/O操作与存储器操作完 (1) I/O操作与存储器操作完 全相同,无需使用专用I/O指 全相同,无需使用专用I/O指 I/O 令,而存储器操作指令及其寻 址方式非常丰富,从而使I/O 址方式非常丰富,从而使I/O 功能增强,编程方便,灵活. 功能增强,编程方便,灵活. I/O端口数目 端口数目( (2) I/O端口数目(即外设数 只受总存储容量的限制, 目)只受总存储容量的限制,大 大增加了系统的吞吐率. 大增加了系统的吞吐率. (3) 使微机系统的读写控制 逻辑简单. 逻辑简单.

存储器 (1MB)

控制

MEMR MEMW

控 制 逻 辑

8 8

IOR IOW

有两个地址空间, 有两个地址空间, 使用不同的读写 MPU 使用不同的读写 控制信号访问存储器 I/O端口 端口. 和I/O端口. MPU访问I/O端口必 访问I/O MPU访问I/O端口必 须采用专用I/O指令. 须采用专用I/O指令. I/O指令

第06章-IO系统设计ppt课件(全)

A1 A2 …

B1 B2 …

通道 A1 A2 … B1 B2 … C1 C2 …

C1 C2 …

图6.16 选择通道传送方式示意图

(3)数组多路通道

◦ 综合前两种通道的优点,可连接多台高速设备,允许几 台设备并行工作,以成组交叉方式传送。每个外设都有 数据缓冲区。

硬件中断(硬中断):是一个异步信号,表明需要注意、 或需要改变执行一个同步事件。

软件中断(软中断):是利用硬件中断的概念,用软件方 式进行模拟,实现宏观上的异步执行效果。

外部中断:一般是指由计算机外设发出的中断请求,如: 键盘中断、打印机中断、定时器中断等。外部中断是可以 屏蔽的中断。

内部中断:是指因硬件出错(如突然掉电、奇偶校验错等) 或运算出错(除数为零、运算溢出、单步中断等)所引起 的中断。内部中断是不可屏蔽的中断。

主存

…

12H JMP 200 向量地址 13H JMP 300

14H JMP 400

入口地址 200 打印机服务程序

入口地址 300 显示器服务程序

… ……

图6.10 通过向量地址寻找入口地址

图6.12 链式排队线路和设备编码器

直接存储器访问方式(Direct Memory Access,DMA), 是一种直接依靠硬件在主存与I/O设备间进行数据传送,且 在 数 据 传 送 过 程 中 不 需 CPU 干 预 的 I/O 数 据 传 送 控 制 方 式 。 CPU与接口的数据传送的具体过程由硬件(DMA Controller, DMAC,DMA控制器)完成,传送速度比通过CPU快。 (1)CPU暂停方式 (2)周期挪用方式(周期窃取方式) (3)交替访问内存方式

第五章通用和复用功能IO口

第五章通用和复用功能IO口1.引言通用和复用功能IO口是现代数字电路设计中的重要组成部分。

它们允许电路与外部设备进行通信和控制,实现数据的输入、输出和处理。

在本章中,我们将介绍通用和复用功能IO口的基本原理和应用。

通用功能IO口是一种通用的输入/输出接口,可以通过软件来配置不同的功能。

它可以被用作输入口,用来读取外部设备的状态;也可以被用作输出口,用来控制外部设备的运行。

通用功能IO口通常由一组引脚组成,每个引脚都可以配置为不同的功能。

通过编程的方式,我们可以根据需要来选择引脚的功能,并进行相应的输入和输出操作。

复用功能IO口是一种多功能的输入/输出接口,可以通过硬件设置来选择不同的功能。

它通常由一个多路器和多个外设模块组成。

多路器的作用是选择不同的外设模块进行连接,从而实现不同的输入和输出功能。

使用复用功能IO口,可以有效地减少芯片上的引脚数量,提高系统的可扩展性和灵活性。

4.通用功能IO口的应用通用功能IO口广泛应用于各种数字电路设计中。

它可以连接各种外设设备,如按钮、开关、传感器、LED灯等。

通过编程的方式,我们可以读取外设的状态,并根据需要来控制外设的运行。

通用功能IO口还可以连接到其他数字电路中,实现数据的输入、输出和处理。

例如,它可以与存储器、处理器、通信接口等进行连接,实现数据的存储、处理和传输。

5.复用功能IO口的应用复用功能IO口广泛应用于嵌入式系统和通信系统中。

它可以连接各种外设设备,如显示器、触摸屏、以太网接口、USB接口等。

通过硬件设置,我们可以选择不同的外设模块进行连接,并根据需要来实现不同的输入和输出功能。

复用功能IO口还可以连接到其他模块中,实现数据的传输和处理。

例如,它可以与显示模块、通信模块等进行连接,实现图形的显示、数据的传输等。

6.小结通用和复用功能IO口是现代数字电路设计中的重要组成部分。

它们允许电路与外部设备进行通信和控制,实现数据的输入、输出和处理。

通过软件和硬件的配置,我们可以选择引脚的功能,并进行相应的输入和输出操作。

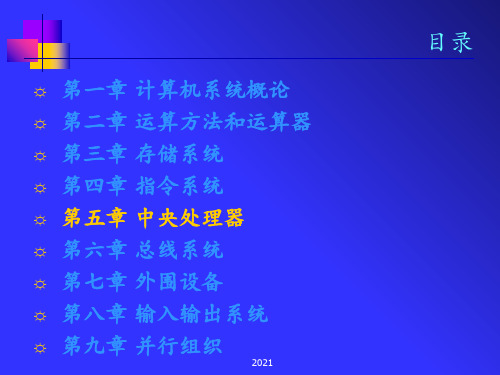

计算机组成原理第五章(白中英版)PPT课件

CPU周期 : 又称机器周期(总线周期),CPU访问 内存所花的时间较长,因此用CPU从内存读取一条指 令字的所需的最短时间来定义

时钟周期 : 通常称为节拍脉冲或T周期。一个CPU 周期包含若干个时钟周期T

相互关系: 1个指令周期 = 若干个CPU周期 1个CPU周期 = 若20干21 T周期

2021

时序产生器 (3/4)

三、3级时序信号的关系 1、一台计算机机内的控制信号一般均由若干个周期

状态,若干个节拍电位及若干个时标脉冲这样3级 控制时序信号定时完成。 2、3级控制时序信号的宽度均成正整数倍同步关系。 周期状态之间,节拍电位之间,时标脉冲之间既 不容许有重叠交叉,又不容许有空白间隙,应该 是能一个接一个地准确连接,一个降落另一个升 起而准确切换的同步信号。

(2) 对指令进行译码,并产生相应的操作控制信号, 送往相应的部件,启动规定的动作;

(3) 指挥并控制CPU、内存与输入/输出(I/O)设 备之间数据流动的方向

• 运算器是数据加工处理部件,所进行的全部操作由 控制器发出的控制信号指挥

(1) (2)执行所有的逻辑运算,并进行逻辑测试

2021

CPU的基本模型

2021

5.1.1 CPU的功能

★ 指令控制

★ 操作控制 CPU产生每条指令所对应的操作信号,并把各种

操作信号送往相应的部件,从而控制这些部件按指令 的要求进行动作

★ 时间控制 对各种操作的实施时间进行定时

★ 数据加工 对数据进行算术运算和逻辑运算处理

2021

5.1.2 CPU的基本组成

• 控制器完成对整个计算机系统操作的协调与指挥。 (1) 控制机器从内存中取出一条指令,并指出下一条 指令在内存中的位置;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(3)异步应答信号:与总线控制权信号共同实现现应答

选择回答(STACK):主设备获得总线控制权后发出,表明它已获得 总线控制权。 主同步(MSYNC):主设备获总线控制权后发出以启动一次总线传送 操作。 从同步(SSYNC):从设备对主同步的回答,表明数据传送结束

13

同步控制信号

(4)总线控制权信号

(6)优先权

排队链输入(PCI)、排队链输出(PCO):用于构成链式判优结构

(7)数据传送控制信号

存储器读(MEMR)、存储器写(MEMW)、I/O读(IOR)、I/O写(IOW)、 高字节允许(BHEN)(用以选择高、低字节)

14

总线的设计要素

(二)总线的时序 1、同步控制总线操作

以上的时序状态图描述了同步方式下的总线操作过程 (DMAC)

23

5.3 直接程序传送方式及接口

一、基本思想 CPU直接利用I/O指令编程实现数据的输入输出。 二、接口模型

接口占用二个端口地址:即命令/状态寄存器和数据缓冲寄存器各占一个 端口。 命令字:CPU通过I/O指令设置,体现对外设的具体控制命令。 状态字:反映外设的工作状态,也可由CPU初始化。现设二位:“忙 (B)”及“完成(D)”。若BD为00则外设处于空闲状态,该状态可 由CPU编程设置,称为“接口清0”。

19

总线的设计要素

(三)总线的仲裁

当多个设备竞争总线时,由总线仲裁器进行仲裁,在微 机中就是南北桥芯片组。 仲裁方式分集中和竞争二种方式。

1、集中式仲裁:

分配原则是:优先级高的设备可以剥夺优先级低的设备 的总线使用权。 当仲裁器接收到总线请求时,就发出总线授权信号。 设备的优先级由设备和仲裁器的逻辑距离决定。 当设备较多时,可采用分级仲裁方式。

28

中断系统的软、硬件组织

(2)内部硬件中断 掉电中断(8); 溢出中断(9); 校验错中断(10); (3)软中断 INT 11~n,根据需要进行扩充,作为系统调用命令。 2、针对各种中断源,分别编制对应的中断服务程序。 3、对中断服务程序的入口地址进行组织,形成中断向量 表。

29

中断系统的软、硬件组织

(2)按时序划分

同步接口:与同步总线连接的接口,接口与系统总线 间的数据传送由统一的时序信号(由CPU或专门的系统 总线时序信号)控制。 异步接口:与异步总线连接的接口,接口与系统总线 间的传送采用异步应答的工作方式。

(3)按信息的传送控制方式划分

中断接口、DMA接口、磁盘存储接口等。

11

5.2 系统总线

16

总线的时序

2、异步控制方式的总线操作 异步方式无统一的时钟周期划分,采用应答工作方式。各信号间的关 系有如下三种:

(1)不互锁:设备1的请求信号触发设备2的回答信号,但请求及回答 信号的撤消均由设备本身定时决定。 (2)半互锁:设备1请求信号的撤消是当接收到设备2的回答信号后;而 设备2的回答信号的撤消由设备2定时决定。 (3)全互锁:由回答信号撤消请求信号;由请求信号的撤消信号撤消回 答信号。 采用互锁方式:时间安排紧凑;但控制复杂。 采用非互锁方式:较易实现,可靠性较高;但总线效率低。

9

接口的功能与分类

3、I/O接口的分类 (1)按数据传送格式划分 并行接口:接口与系统总线及I/O间均以并行方式传送 数据。 串行接口:接口与I/O间以串行方式,而与系统总线间 以并行方式传送数据。

…

I/O接口

系统总线

…

I/O接口 I/O设备 串行接口

…

I/O设备

同步控制信号

(1)复位信号(RESET) (2)同步定时信号:

处理器时钟(CLOCK):CPU产生,系统的定时信号及基本时钟。 附加同步(ASCLOCK):多处理机间的同步或外部输入到CPU的定时 信号。 刷新同步(REFRESH):动态存储器刷新的同步信号。 CPU机器周期同步(MCSYNC):表示一个机器周期的开始,I/O据 此与CPU同步。 状态信号(S0、S1):系统总线的周期状态,供有关的I/O作为辅助定 时。

25

5.4 程序中断方式及接口

一、二个基本问题 1、中断的本质是程序切换 2、中断的特点是随机性: (1)随机出现的事件; (2)主观上有意调用外设,但以随机提出请求方式 实现处理; (3)随机插入的软中断。

26

5.4 程序中断方式及接口

二、中断方式的典型应用 1、以中断方式管理中低速的外设,使CPU与外 设并行工作; 2、软中断,如INT n,n为中断号; 3、故障处理,如:

5

5.1 概述

二、总线类型与总线标准 1、从系统组成角度的分类 常见的术语有: 单总线、系统总线、 I/O扩展总 线、局部总线、高速存储总线、内总线、外总线等。 2、按据传送格式分

串行总线:如USB(通用串行总线)、FC(光纤通道); 并行总线:SCSI(小型机系统接口)

3、按时序控制方式分类

硬件故障:掉电、校验错、运算错; 软件故障:溢出、地址越界、使用非法指令等。

4、实时处理,如时钟、实时监控对象异常; 5、多机通信 6、人机对话

27

程序中断方式及接口

三、中断系统的软、硬件组织 中断系统:与中断功能有关的软件、硬件。 1、模型机中的各种中断请求 (1)外部硬件中断源 IREQ0:系统时钟; IREQ1:实时时钟,供实时处理; IREQ2:通信中断; IREQ3:键盘; IREQ4:CRT显示器; IREQ5:硬盘; IREQ6:软盘; IREQ7:打印机。

系统总线的功能是连接系统内所有的功能部件。其设计主 要涉及到总线宽度、时序控制、仲裁等几个方面。 一、总线的设计要素 (一)总线宽度: 关系到系统的数据传输率、可管理内存的大小、集成度和 硬件成本等。 地址线(AB):确定内存的字数 如8086提供20根;80386提供32根地址线。 数据线(DB):确定内存的宽度 如8086提供16根;80386提供32根数据线。在现代计 算机中一般地址线和数据线分时复用以降低硬件成本。 控制线(CB):确定CPU控制功能的强弱 用于传送包含状态在内的有关的控制信号,主要包括如 下信号:

5.1 概述

三、接口的功能与分类 1、接口: 泛指设备部件(软、硬)间的交接部分。主机的系统 总线与I/O或其它外部系统间的接口逻辑,称为I/O接 口或外围接口

软件接口:软件模块间的交接部分。 软硬接口:软、硬件相互作用,所涉及的硬件逻辑与软件 ,如硬件信号引发相应软件模块的调用,如中断系统及中 断服务程序。 接口技术:硬件接口及相应的控制软件。

2

主机与外设间的连接模式

2、多总线结构:

3

主机与外设间的连接模式

3、高性能的多总结构

4

主机与外设间的连接模式

4、I/O通道和I/O处理机 通道是一个弹性较大的概念。 I/O处理机是由通道发展而来的,IOP比通道具有 更强的功能,类似于CPU,只是更为专业化,主 要面向输入输出管理及处理。

总线请求(BREQ):要求总线控制权的设备发出(如DMAC) 总线批准(BACK):总线请求的批准,由CPU或总线控制器发出 总线忙(BUSY):主设备获得总线控制权后发出,持续到释放总线 控制权

(5)中断请求与中断批准信号

中断请求线(IREQ0 ~IREQ7) :外设中断请求 系统的中断请求(INT):中断控制器发出 中断响应(INTA):CPU响应INT后发出

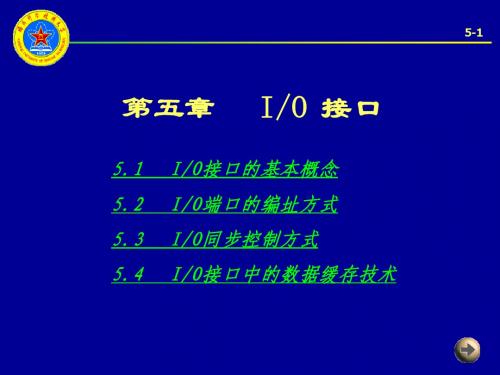

第五章 输入/输出系统

基本要求:掌握总线的功能及分类、接口的功能 及分类、直接程序传送方式接口的工作原理、程 序中断方式接口的工作原理 重 点:接口的功能、程序中断方式接口的工作 原理 难 点:程序中断方式接口的工作原理

1

5.1 概述

I/O系统包括I/O设备、接口及系统总线。 一、主机与外设间的连接模式 1、单总线 总线型也是其它连接模式的基础。

20

集中式仲裁器

21

总线的仲裁

2、竞争式仲裁 分配原则: 优先级不同的设备同时申请总线,则分配给高优先级的 设备; 先来先占用:谁先抢占总线,只要该设备没有释放总线, 则其它优先级高的设备不能强行占用总线。

22

总线的设计要素

(四)PCI总线

器件周边互连总线,可作为中间层或直接连接I/O设备; 早期:主频33MHZ,32位,带宽大133MHZ 发展:主频66MHZ(最高达133MHZ),64位 同步时序总线 地址线和数据线复用,支持64位地址和数据 集中式仲裁 支持32位和64位扩展卡 支持单个和多个处理器 支持突发数据传输

24

直接程序传送方式及接口

三、接口的工作过程 1、CPU通过启动命令启动外设; 2、启动后:D=0、B=1,此时,外设开始工作; 3、CPU查询外设状态字,查询结果是:DB=01,说明未准备 好,CPU就继续查询等待; 4、外设准备好,则置位状态字DB=10: (1)若是输入设备,则外设将数据送到数据缓冲寄存器后,使 DB=10,CPU经查询判断得知数据准备好,便通过输入指令 取走数据,同时设置DB=01; (2)若是输出设备,则当接口中的数据缓冲寄存器为空是,使 DB=10,CPU经查询判断得知外设准备好接收数据,便通过 输出指令送出数据,同时设置DB=01;

17

异步控制方式

异步总线的操作过程:

18

异步控制方式

以DMAC为例说明工作过程如下: (1)DMAC发出总线请求BREQ; (2)前一个主设备降下总线忙BUSY信号,表示前一个总线 周期的结束,CPU经判断发出总线批准信号BACK; (3)DMAC接收到BACK信号后,撤消总线请求,并发出选 择回答STACK信号,表示已接收到批准信号BACK,于是 CPU结束批准信号,放弃总线控制权。 (4)DMAC接管总线,升起总线忙BUSY信号,同时,向总 线送出地址码和传送命令; (5)DMAC向从设务发出主同步信号MSYNC,启动总线传 送操作; (6)传送结束时,从设备发出从同步信号SSYNC,DMAC 接收后,发出撤消选择回答信号STACK、总线忙信号BUSY 及主同步信号MSYNC。 至此,一个总线周期结束。